Received July 8, 2020, accepted July 24, 2020, date of publication July 29, 2020, date of current version August 10, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.3012699

# A 5 GS/s 29 mW Interleaved SAR ADC With 48.5 dB SNDR Using Digital-Mixing Background Timing-Skew Calibration for Direct Sampling Applications

MINGQIANG GUO<sup>®1,2</sup>, (Member, IEEE), JIAJI MAO<sup>1,2</sup>, (Graduate Student Member, IEEE), SAI-WENG SIN<sup>®1,2</sup>, (Senior Member, IEEE), HEGONG WEI<sup>3</sup>, (Member, IEEE), AND RUI P. MARTINS<sup>®1,2,4</sup>, (Fellow, IEEE)

<sup>1</sup> State-Key Laboratory of Analog and Mixed-Signal VLSI, Institute of Microelectronics, University of Macau, Macau 999078, China

Corresponding author: Sai-Weng Sin (terryssw@um.edu.mo)

This work was supported in part by the National Key Research and Development Program of China under Grant 2019YFB1310000; in part by The Science and Technology Development Fund, Macau, under Grant SKL-AMSV(UM)-2020-2022(DP); and in part by the University of Macau under Grant MYRG2017-00192-FST and Grant MYRG2018-00204-AMSV.

**ABSTRACT** This article presents a 16-channel 5 GS/s time-interleaved (TI) SAR ADC for a direct-sampling receiver that employs a digital-mixing background timing mismatch calibration to compensate for timing-skew errors. It uses a first-order approximation to obtain the derivative of the autocorrelation of the input signal, subsequently used to evaluate the explicit amount of the timing-skew. Therefore, this allows a digital background calibration of the timing-skew, avoiding extra analog circuits. The proposed 16-channel TI ADC uses a splitting-combined monotonic DAC switching method for the individual SAR channel to achieve a trade-off of simple switching and small common-mode voltage variation of the comparator. The prototype, implemented in 28 nm CMOS, reaches a 48.5/47.8 dB SNDR with an input signal of 2.38/4.0 GHz after the proposed background timing mismatch calibration, respectively. Furthermore, the ADC core's power consumption is 29 mW sampling at 5 GS/s, with a Walden FoM of 26.7 fJ/conv.-step and a Schreier FoM of 157.9 dB.

**INDEX TERMS** Analog-to-digital converter (ADC), time-interleaved (TI) ADC, timing mismatch, digital background calibration, digital-mixing.

#### I. INTRODUCTION

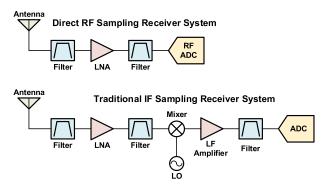

The direct RF sampling receiver architecture is much simpler than the traditional IF sampling one. As shown in Fig. 1, it only consists of a low-noise amplifier (LNA), the appropriate filters, and the RF ADC. Unlike its IF version, the direct RF sampling receiver does not use the analog mixers and local oscillators (LOs). The ADC digitizes the RF signal directly and sends it to a DSP. However, direct sampling architecture cannot be practically implemented in the past ten years. The main limitation is the ultra-high requirements of the converter

The associate editor coordinating the review of this manuscript and approving it for publication was Venkata Rajesh Pamula.

sample rates [1]. In nowadays broadband cable and satellite communications, the input spectrum ranges from tens of MHz to multi-GHz [2]. Therefore, a Nyquist rate converter in the GS/s range is required to sample the input signal in full bandwidth.

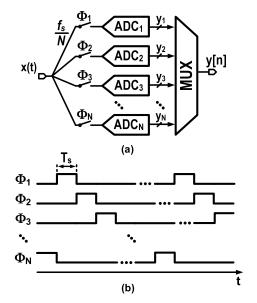

A time-interleaved (TI) ADC architecture is a power-efficient candidate for these wideband applications because it can increase the overall converter's effective sampling rate by multiplexing several ADC channels in parallel. The effective conversion rate ( $f_s$ ) of an N-channel TI ADC becomes N times the rate of each sub-converter, as shown in Fig. 2. Nevertheless, the architecture suffers from inter-channel mismatches among the sub-ADC channels, which includes

<sup>&</sup>lt;sup>2</sup>Department of ECE, Faculty of Science and Technology, University of Macau, Macau 999078, China

<sup>&</sup>lt;sup>3</sup>Electrical and Computer Engineering Department, The University of Texas at Austin, Austin, TX 78712, USA

<sup>&</sup>lt;sup>4</sup>Instituto Superior Técnico, Universidade de Lisboa, 1649-004 Lisbon, Portugal

FIGURE 1. Direct RF sampling vs. traditional IF sampling.

FIGURE 2. a) N-channel TI ADC, and (b) its clock phases.

offset, gain and timing mismatches [3]. Compared to the offset and gain mismatches, timing mismatch induces a dynamic error proportional to both input frequency and amplitude.

Compared to foreground calibration, the background calibration can actively track the supply and temperature changes without interrupting the normal operation although it has higher complexity. Adding a reference converter is an effective way to perform background calibration for timing mismatch [4]–[9]. However, the addition of this reference converter will bring additional area and power consumption.

Some recent works [3], [10]–[16] develop timing-skew mismatch calibration without the use of an additional reference channel. Some of them use digital-mixing based on the difference of the autocorrelation function between channels. [3], [11], and [13] estimate the polarity of the timing skew with fewer samples. [3] and [11] need a feedback loop from digital to analog for calibrating the timing-skew by tuning the delay line of individual sub-channel. In [13] they correct the timing mismatch error in the digital domain without a tunable delay line, but an auxiliary delta-sampling ADC is necessary to estimate the skew error.

This article presents a fully digital background timingskew calibration without any additional analog circuits. Different from the previous works [3], [11] which only use digital-mixing to detect the polarity of the timing-skew, this method divides the derivative of the autocorrelation function of the input signal by the difference between channels' digital mixing [16]. Moreover, the article improves the accuracy over [16] with a more accurate bilateral estimation of the derivative of the autocorrelation function. We implement a 5 GS/s 16-channel TI-SAR ADC in 28 nm CMOS with a splitting-combined monotonic DAC switching method for a single-channel SAR ADC. After the proposed timing-skew calibration, the ADC obtains an SNDR of 48.5/47.8 dB with an input frequency of 2.38 /4.0 GHz, respectively. The ADC core consumes 29.0 mW (inter-channel mismatch calibration off-chip), while leading to a Walden FOM of 26.7 fJ/conv.step and a Schreier FOM of 157.9 dB.

In addition to this introductory section, Section II describes the review for the timing-skew detection techniques in TI-ADCs with digital-mixing. Section III describes the proposed digital-mixing timing-skew calibration technique. Section IV demonstrates the circuit details of the 16-channel 5 GS/s TI-SAR ADC. Section V summarizes the measured performance, and Section VI concludes the article.

# II. REVIEW OF TIMING-SKEW CALIBRATION WITH DIGITAL-MIXING

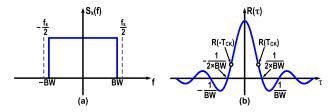

The following discussion of modeling of the TI ADC neglects the effect of quantization noise, as this permits us to fully investigate the effect of mismatches on the system. From Fig. 2, the input and output of the TI ADC are x(t) and y[n], respectively, and ideally  $y[n] = x(nT_s)$ , with  $T_s$  representing the sampling period. From [17], we can generally assume the input signal x(t) is a wide-sense stationary (WSS) signal. For example, for a bandlimited signal with a white spectrum in the  $1^{\rm st}$  Nyquist band, the autocorrelation follows a *sinc* function, as depicted in Fig. 3. Therefore, the autocorrelation function of the input signal  $R(\tau) = E\left[x_k(t)x_k(t+\tau)\right]$  is independent of the time t.

FIGURE 3. The waveform of (a) a low-pass wide-band random signal and (b) the autocorrelation function of this signal.

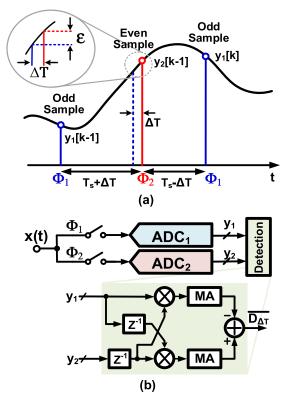

We first describe the timing mismatch analysis for a two-channel TI ADC. From Fig. 4, ADC<sub>1</sub> samples the input x(t) at  $\Phi_1$  with the digital output of  $y_1$ (odd sample) and ADC<sub>2</sub> samples at  $\Phi_2$  with  $y_2$  (even sample), with  $\Phi_2$  skewed from the ideal value by  $\Delta T$ . This indicates a time difference between samples  $y_1[k-1]$  and  $y_2[k-1]$  of  $2\Delta T$  seconds

FIGURE 4. (a) TI-ADC sampling to illustrate the effect of the timing mismatch for two-channel TI ADC, and (b) the timing-skew detection topology based on digital-mixing.

larger than that between  $y_2[k-1]$  and  $y_1[k]$ , as illustrated in Fig. 4(a).

The digital mixing technique evaluates both of the autocorrelation functions [3], one from the moving average (MA) of the product of  $y_1[k-1]$  and  $y_2[k-1]$  and the other from  $y_2[k-1]$  and  $y_1[k]$ , as shown in Fig. 4(b), and expressed by:

$$R(T_s + \Delta T) = \frac{1}{n} \sum_{k=1}^{n} y_1 [k-1] y_2 [k-1]$$

(1)

$$R(T_s - \Delta T) = \frac{1}{n} \sum_{k=1}^{n} y_1 [k] y_2 [k-1]$$

(2)

$$R(T_s - \Delta T) = \frac{1}{n} \sum_{k=1}^{n} y_1[k] y_2[k-1]$$

(2)

Therefore, for a small value of timing-skew  $\Delta T$ , we derive the difference between (1) and (2) as follows [3], [11]:

$$\overline{D_{\Delta T}} = R (T_s + \Delta T) - R (T_s - \Delta T)$$

$$\approx 2\Delta T \cdot \frac{dR(\tau)}{d\tau}|_{\tau = T_s}$$

(3)

Thus, the evaluated timing-skew information  $\overline{D_{\Delta T}}$  is proportional to the timing-skew  $\Delta T$  and to the derivative of its autocorrelation function  $R(\tau)$  at  $\tau = T_s$ .

With the information of the polarity for timing-skew  $\Delta T$ in (3), [3] and [11] use a tunable delay line in the sampling clock generator to adjust earlier or later the sampling clocks until the value of  $\overline{D_{\Delta T}}$  is negligible. The tunable delay line will increase the jitter noise of the sampling clock. In [13] the circuit presents a digital correction to eliminate the timing-skew error by adding extra auxiliary channels,

also based on the above detection topology. Both approaches need modification/addition of analog circuits. In this article, we demonstrate a digital calibration method that avoids extra analog circuits.

# **III. DIGITAL TIMING-SKEW CALIBRATION USING DIGITAL-MIXING**

The timing-skew in each sub-converter can induce a dynamic error, depending on both the amplitude and frequency of the input signal. As shown in Fig. 4(a), when we choose ADC<sub>1</sub> as the reference, the timing-skew  $\Delta T$  of ADC<sub>2</sub> produces a skew-induced sampling error  $\varepsilon$ . Without the loss of generality, we assume the timing-skew  $\Delta T$  to be much smaller than the sampling period  $T_s$ . Thus, for the input signal x(t), the ideal (or calibrated) samples  $y_{2,cal}$  can be approximated by a 1<sup>st</sup>-order Taylor series as:

$$y_{2,cal}[k] \approx y_2[k] - y_2'[k] \cdot \Delta T$$

(4)

where  $y_2'[k]$  is the first-order derivative of even samples, which can be obtained by a derivative filter.

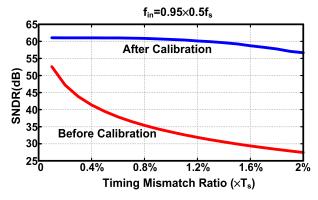

As expressed in (4), the skew-induced error correction assumes only first-order sampling errors, and we do not take into consideration the higher-order Taylor series terms. Moreover, the accuracy of the correction will decrease when the timing-skew becomes large. Fig. 5 plots the behavior study of a 16-channel TI ADC before and after the ideal linear approximation correction. The plot depicts the trends of SNDR with the input frequency of  $f_{in} = 0.95 \times 0.5 f_s$ versus the timing mismatch ratio (RMS value). From these curves, the accuracy of the digital correction degrades with the increase of the timing mismatch level. To guarantee excellent performance at high frequency, we use a retiming technique in the multi-phase clock generator to reduce both initial values of timing-skew and clock jitter (discussed in detail in the next section).

FIGURE 5. The SNDR of a 16 channel 10 bit ADC before and after an ideal linear approximation correction versus the timing-mismatch ratio.

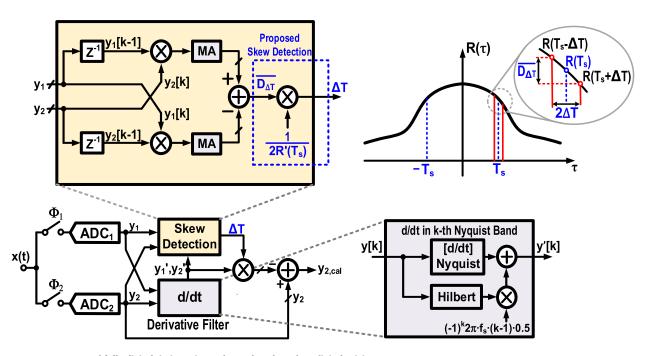

This section presents the proposed fully digital timing mismatch calibration method. First, we use a two-channel TI ADC as an example to explain the basic principle and calibration algorithm. Furthermore, different from [16], here

FIGURE 6. Proposed fully digital timing mismatch topology based on digital-mixing.

we use a bilateral linear approximation to obtain a more accurate derivative of the autocorrelation to improve the mismatch correction.

# A. FORMULATION OF THE PROPOSED FULLY DIGITAL TIMING-SKEW CALIBRATION

Fig. 6 exhibits the principle of the proposed background calibration technique for timing mismatch. We use a digital differentiator to obtain  $y_2'[k]$ , and with a Hilbert transform filter, the derivative of the input at around 90% frequency range (0.05–0.95) can be obtained within any Nyquist band [15]. Then, from (3), the amount of the timing-skew  $\Delta T$  can be calculated by

$$\Delta T \approx \frac{\overline{D_{\Delta T}}}{2 \cdot \frac{dR(\tau)}{d\tau}|_{\tau = T_s}} \tag{5}$$

The derivative of the autocorrelation function should be [11]:

$$\frac{dR(\tau)}{d\tau}|_{\tau=T_s} = \frac{dE\left[y(t)\cdot y(t+\tau)\right]}{d\tau}|_{\tau=T_s}$$

$$= E\left[y(t)\cdot \frac{dy(t+\tau)}{d\tau}|_{\tau=T_s}\right] \tag{6}$$

In previous work [16], we use the moving average of the product of  $y_1[k-1]$  and  $y_2'[k-1]$  to approximate  $\frac{dR(\tau)}{d\tau}|_{\tau=T_s}$ :

$$\frac{dR(\tau)}{d\tau}|_{\tau=T_s} \approx \frac{1}{n} \sum_{k=1}^{n} y_1 [k-1] y_2' [k-1] = \frac{dR(\tau)}{d\tau}|_{\tau=T_s + \Delta T}$$

(7)

However, due to the existence of timing-skew  $\Delta T$ , the terms on the right-hand side of (7) are not an accurate value of  $\frac{dR(\tau)}{d\tau}|_{\tau=T_s}$ , but instead it is  $\frac{dR(\tau)}{d\tau}|_{\tau=T_s+\Delta T}$ . This induces an

approximation error in our previous estimation of  $\frac{dR(\tau)}{d\tau}|_{\tau=T_s}$  presented in [16].

Alternatively, for the small value of  $\Delta T$ , the first-order derivative of the autocorrelation function at  $\tau = T_s$  can be a bilateral approximation:

$$\frac{dR(\tau)}{d\tau}|_{\tau=T_s} = \frac{1}{2} \left[ \frac{dR(\tau)}{d\tau} |_{\tau=T_s+\Delta T} + \frac{dR(\tau)}{d\tau} |_{\tau=T_s-\Delta T} \right] \quad (8)$$

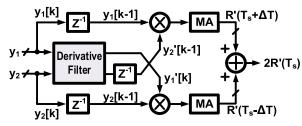

By taking the moving averages for the product of  $y_1[k-1]$  to  $y_2'[k-1]$  and the other from  $y_2[k-1]$  to  $y_1'[k]$ , as shown in Fig. 7,  $\frac{dR(\tau)}{d\tau}|_{\tau=T_s+\Delta T}$  and  $\frac{dR(\tau)}{d\tau}|_{\tau=T_s-\Delta T}$  can be obtained:

$$\frac{dR(\tau)}{d\tau}|_{\tau=T_s+\Delta T} = R'(T_s + \Delta T)

= \frac{1}{n} \sum_{k=1}^{n} (y_1 [k-1] y_2' [k-1]) \qquad (9)

\frac{dR(\tau)}{d\tau}|_{\tau=T_s-\Delta T} = R'(T_s - \Delta T)

= \frac{1}{n} \sum_{k=1}^{n} (y_2 [k-1] y_1' [k]) \qquad (10)$$

Then, by averaging (9) and (10), we determine the  $dR/d\tau$  at  $\tau = T_S$  as presented in Fig. 7, with the estimated amount of the timing-skew  $\Delta T$  evaluated by (5) (as in Fig. 6).

FIGURE 7. Proposed block diagram to obtain the first-order derivative of the autocorrelation function based on digital-mixing.

#### **B. SIMULATION RESULTS**

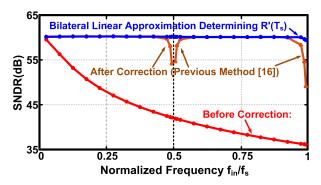

Fig. 8 illustrates the comparison of the SNDR vs. the input frequency after timing mismatch digital correction by two different detection methods ((a) used in [16] and (b) proposed here). We use the same 25 tap differentiation filter for a two-channel TI ADC during the comparison with an injected timing-skew of  $0.5\% \times T_s$ . When compared with the previous method [16], the new approximation for  $\frac{dR(\tau)}{d\tau}|_{\tau=T_s}$ has an obvious advantage when the input is near Nyquist frequencies. It demonstrates that the decrease of SNDR after calibration with the detection method in [16] happens at the frequencies near  $m \times 0.5 f_s$ . This happens because we implement the differentiation filter using a finite number of taps (Fig. 6) which limits the accuracy of the filter's frequency response near  $m \times 0.5 f_s$  [15]. Moreover, the inaccuracy of the predicted derivative of the input will also affect the required number of convergence samples during the detection of the timing-skew [15].

FIGURE 8. The SNDR of two channel TI ADC before and after correction (with two different method) as a function of input frequency.

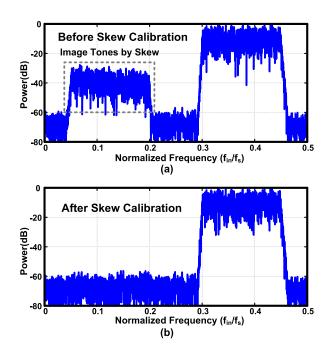

Fig. 9 (a) and (b) shows the simulated ADC spectrum of a wide-band random signal before and after performing the proposed timing mismatch calibration. We did not observe any image pattern of the skew after the proposed calibration.

## C. EXTENSION TO MULTIPLE CHANNELS

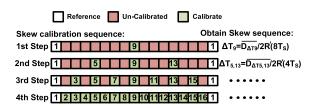

We now extend the above concepts to additional channels (16 channels chosen as an example). To this end, we define the sampling times of the first channel as the reference [13] (highlighted in Fig. 10). We then compute the timing of channels 2, 3, ..., 13, 14 and 15 with respect to channel 1, which can be divided into four steps. First, we can detect and correct the mismatch between channels 9 and 1 by evaluating  $\overline{D_{\Delta T9}}$  and R' (8 $T_s$ ). Second, we can correct the timing skews in channels 5 and 13 by  $\overline{D_{\Delta T5,13}}$  and R' (4 $T_s$ ), relying on the corrected channel 9 as reference. The 3<sup>rd</sup> and 4<sup>th</sup> steps continue in a similar way until all the channels are calibrated.

### IV. ADC IMPLEMENTATION

## A. ADC ARCHITECTURE

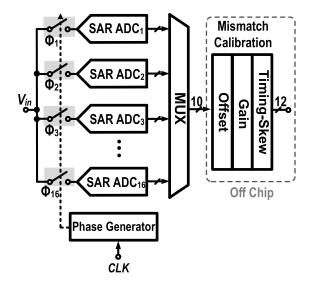

Fig. 11 presents the 5 GS/s TI ADC prototype consisting of 16-channel time-interleaved 312.5 MS/s SAR sub-ADCs. The inter-channel mismatch, including offset, gain,

FIGURE 9. The simulated two channel TI ADC output spectrum (a) before and (b) after timing-skew calibration for a randomized input.

FIGURE 10. The sequence of calibration in a 16-channel TI ADC.

FIGURE 11. ADC Architecture.

and timing-skew, are all calibrated in the digital domain in the background off-chip. Besides, we use a bilateral digital-mixing background timing-skew calibration, as discussed previously. With this method, extra analog circuits

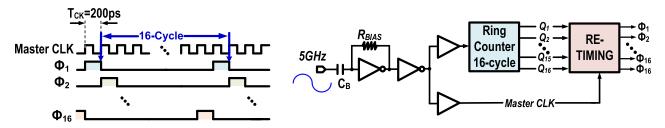

FIGURE 12. The timing diagram of the sampling for each sub-converter and block diagram of the clock generator.

FIGURE 13. The block diagram of the single-channel ADC.

are not necessary (Fig. 11). From the measurements, 16 k samples are enough to achieve a good SNDR for the timing-skew calibration.

The 16-channel interleaved ADC needs sixteen clock phases with 6.25% duty cycle. Fig. 12 displays the clock generator with a master clock of 5 GHz, divided by the 16-cycle ring counter, produces the outputs  $Q_1$ - $Q_{16}$ . The ring counter is constructed with D-type Flip-Flops (DFFs) forming a shift register. This can be considered as a cascade of logic gates, which accumulate a substantial amount of jitter. We reuse the master clock to retime  $Q_1$ - $Q_{16}$  from the ring counter to impose that the falling edges of the final sample clock  $\Phi_1$ - $\Phi_{16}$  depend only on the rising edges of the master clock [15]. Besides, to ensure an equal distance to each channel, we also use an H-tree routing paths for input signals and clocks in the layout. Benefitting from the combination of the retiming technique and the H-tree routing, we not only reduce the jitter produced by clock-division but also guarantee that the initial un-calibrated timing-skew of each channel is small enough.

#### B. SINGLE-CHANNEL SAR ADC

For the sub-channel implementation, the V<sub>CM</sub>-based switching procedure [18] has an excellent power efficiency. However, the low power supply of the advanced process turns this structure not attractive in high-speed applications. The multi-bit per cycle SAR ADC [19], [20] is suitable for such applications, but this topology needs complex DAC and control logic. The capacitor DAC splitting structure is a popular choice for the high-speed SAR ADC [2], [13]. Still, this architecture imposes that both switches and the

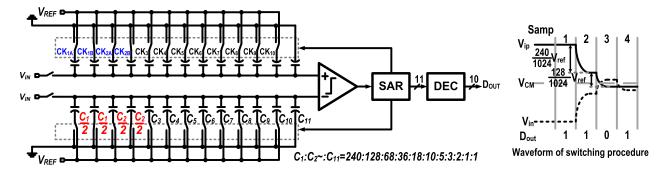

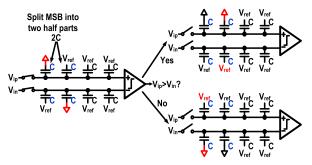

SAR decision logic have higher complexity than the solely monotonic switching structure [21]. In this work, we use the single-channel ADC with a splitting-combined monotonic switching method [22]. Fig. 13 shows the circuit diagram of the single-channel converter. Each SAR channel includes a two-stage dynamic comparator, bootstrap switches, custom DAC capacitor arrays, SAR decision logic, and digital error correction (DEC) to convert non-binary data to binary [23]. The ADC samples the input signal on the top plates of the capacitor arrays, determining the first MSB by the signal polarity on the top plates before the DAC conversion. As a result, the 10 bit ADC requires 29 capacitor DAC only. One extra redundant bit cycle is added to address the DAC settling issue in high-speed conversion [23]. Therefore, the 29 capacitor cells arrange into ten capacitor groups C<sub>1</sub>-C<sub>10</sub> with binary-scaled recombination as shown in Fig. 13.

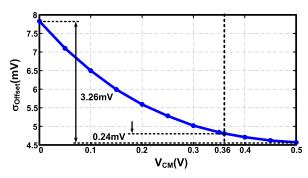

Unlike [22], there are only two MSB DAC capacitors split into two halves, as Fig. 14 displays, thus the variation of the comparator input common-mode voltage ( $V_{CM}$ ) is reduced from 0.5 V to 0.14 V ( $\sim$ 72% reduction), compared with the solely monotonic switching. The nine remaining LSBs are still in the traditional monotonic switching method. As a result, the splitting-combined monotonic switching method not only preserves the benefit of relatively-simple switches and SAR decision logic, like solely monotonic method, but also largely alleviates the variation of common-mode voltage that may lead to the dynamic offset of the comparator. Fig. 14 demonstrates a plot of the common-mode voltage ( $V_{CM}$ ) vs. the RMS value of the offset ( $\sigma_{Offset}$ ) for the comparator from 200 times Monte Carlo simulations. The  $V_{CM}$ -dependent variation of  $\sigma_{Offset}$  reduces from a solely

FIGURE 14. The simulated comparator offset versus common mode voltage.

FIGURE 15. Conversion of splitting combined monotonic switching procedure for an example 3-bit ADC.

monotonic switching of around 3.26 mV (0.5V  $V_{CM}$  variation) to the splitting-combined monotonic values of 0.24 mV (0.14V  $V_{CM}$  variation) now. Fig. 15 illustrates an example of the conversion of a split-combined monotonic switching procedure for a 3 bit ADC, with only MSB divided into two halves.

# **V. EXPERIMENTAL RESULTS**

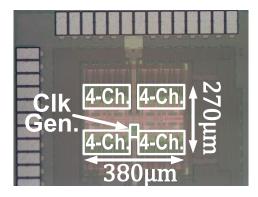

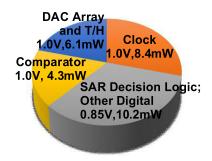

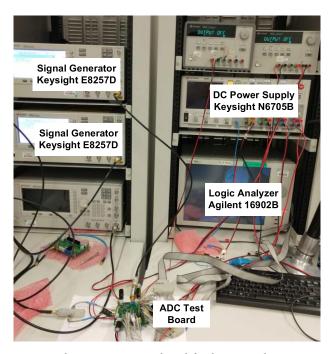

The proposed 16-channel TI ADC is fabricated in a 28 nm CMOS with a core area of  $380 \times 270 \ \mu \text{m}^2$  (Fig. 16). The DVDD digital supply, including the SAR logic and other control digital circuits, is 0.85 V. On the other hand, the AVDD analog supply, like comparators, track and hold (T&H) circuits, capacitor DAC switches, and the clock division circuit are 1.0 V for high sampling linearity and low-jitter noise. The total power consumption of the ADC core is 29mW (T&H and DAC array 21%, comparator 15%, SAR decision logic and other digital 35%, and clock generator 29%), as summarized in Fig. 17. The reference of the ADC are driven from AVDD, as no reference buffer is required. The inter-channel mismatch calibration algorithm is off-chip. The estimated number of gates for the proposed calibration algorithm are around 170 k. The estimated power consumption for the algorithm is 12.8 mW (DVDD = 0.85 V) and an estimated area of 0.11 mm<sup>2</sup>. The measurement test-branch for the proposed TI ADC prototype is shown in Fig. 18.

Fig. 19 plots the measured output spectrum over the Nyquist rate with an input of 2.86 GHz before and after timing mismatch calibration. The 2.86 GHz input is over

FIGURE 16. Chip micrograph.

FIGURE 17. Power breakdown.

FIGURE 18. The measurement test-branch for the proposed TI ADC prototype.

the Nyquist rate, thus the measurement includes the effectiveness of the Hilbert Transform Filter of the differentiator [15]. From Fig. 19(b), the highest image tone generated by timing-mismatch improves from -69.7 dB with our previous

ADC specially designed for output decimated by a factor of 625x

FIGURE 19. Measured output spectrum with an input frequency of 2.86 GHz (a) before and (b) after timing-skew calibration.

FIGURE 20. The measured largest image tone after timing-skew calibration with an input of 2.86 GHz versus the number of samples.

method [16] to -77.6 dB with the new, as discussed in Section V.

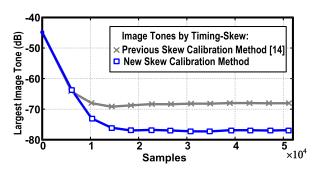

Fig. 20 shows the measured largest image tone by timing-skew with a 2.86 GHz input at 5 GS/s versus the number of timing-skew detection samples. Both the new method and the previous one [16] only need about 16 k samples convergence to achieve satisfactory dynamic performance. Compared to the method in [16], the new skew calibration method has a significant improvement in the largest image tone when the samples over 10 k.

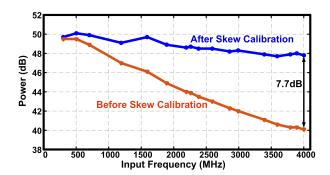

Fig. 21 displays the SNDR vs. the input frequency at 5 GS/s. The SNDR peaks at 50.3 dB at the low input frequency. Benefiting from the proposed timing-skew calibration and retiming techniques, the SNDR only drop 1.8 dB and 2.5 dB at the frequency near the Nyquist rate and the

FIGURE 21. The measured SNDR versus input frequency before and after timing-skew calibration.

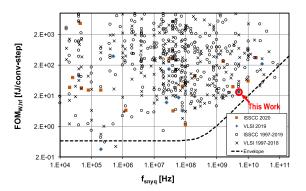

FIGURE 22. Compared to state-of-the-art for the Walden FOM [27].

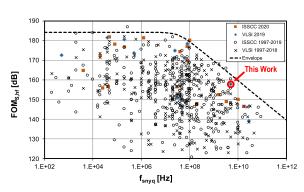

FIGURE 23. Compared to state-of-the-art for the Schreier FOM [27].

frequency of 4 GHz, respectively. Therefore, thermal noise and distortion of the sampling switch are the main limiting factors for dynamic performance.

Table 1 illustrates the performance summary and a comparison with several state-of-the-art TI ADCs. These works include the recently published 10 bit TI ADC with similar sampling rates. The total power consumption of the ADC presented in this article achieves 48.5 dB SNDR near the Nyquist rate at 5 GS/s and only consumes 29 mW, with a Walden FOM of 26.7 fJ/conv.-step and a Schreier FOM of 157.9 dB. It makes this ADC having competitive power efficiency in the comparison.

Fig. 22, and Fig. 23 compares this ADC with all works published at ISSCC 1997-2020 and VLSI 1997-2019 [27]

| TABLE 1. Tal | ble of compa | arison with s | state-of-the-arts. |

|--------------|--------------|---------------|--------------------|

|--------------|--------------|---------------|--------------------|

|                                  | This Work |                      | JSSC-15[2]    | TCASI-17[24] | ISSCC-17[25] | JSSC-18[13] |                      | JSSC-20[26] |

|----------------------------------|-----------|----------------------|---------------|--------------|--------------|-------------|----------------------|-------------|

|                                  |           |                      | M. Brandolini | J. Fang      | J. P. Keane  | C. Lin      |                      | M. Baert    |

| Architecture                     | TI-SAR    |                      | TI-Pipe-SAR   | TI-SAR       | TI-SAR       | TI-SAR      |                      | TI-VCO      |

| Technology                       | 28nm      |                      | 28nm          | 28nm         | 28nm FDSOI   | 40nm        |                      | 28nm        |

| Supply(V)                        | 1.0/0.85  |                      | 1.8/1.0       | 1.0          | 1.9/1.1/0.9  | 1.1         |                      | 1.0/0.85    |

| Resolution(bit)                  | _         | 10                   | 10            | 10           | 10           | 10          |                      | 10          |

| Speed(GS/s)                      | 5         | .0                   | 5.0           | 5.0          | 8.0          | 2.6         |                      | 5.0         |

| Skew Correction                  | Dig       | gital                | Analog        | Analog       | Analog       | Digital     |                      | Analog      |

| SFDR@Nyq.(dB)                    | 59.6      |                      | 58            | 54.4         | 60.3         | 57.8        |                      | 57.1        |

| SNDR@Nyq.(dB)                    | 48.5      |                      | 46.1          | 41.7         | 49.0         | 50.6        |                      | 45.2        |

| SNDR>Nyq.(dB)                    | 47.8@     | 04GHz                | N/A           | N/A          | N/A          | N/A         |                      | N/A         |

| Power(mw)                        | 29.0      | 41.8 <sup>(1)</sup>  | 150           | 76           | 300          | 18.4        | 39.2 <sup>(1)</sup>  | 22.7        |

| Area(mm²)                        | 0.103     | 0.21 <sup>(1)</sup>  | 0.45          | 0.57         | 0.184        | 0.825       | 0.92(1)              | 0.023       |

| FOM <sub>w</sub> @Nyq.(fJ/cStep) | 26.7      | 38.5 <sup>(1)</sup>  | 192.5         | 165          | 162.9        | 25.6        | 54.5 <sup>(1)</sup>  | 30.5        |

| FOM <sub>w</sub> @Nyq.(dB)       | 157.9     | 156.3 <sup>(1)</sup> | 148.1         | 147.2        | 150.2        | 159.1       | 155.8 <sup>(1)</sup> | 155.6       |

(1) With estimated mismatch calibration power and area.

with the Nyquist sampling rate (equal to the sampling rate  $(f_s)$  divided by the oversampling ratio (OSR)), vs. the Walden FoM and Schreier FoM at high frequency, respectively. Both two figures demonstrating this work have competitive positions in the state-of-the-art high-speed ADC.

#### VI. CONCLUSION

This article presented a digital background timing-skew calibration for a TI ADC based on digital-mixing. With such method we can correct the timing mismatch of the TI ADC without additional analog circuits. Besides, there is no clock jitter noise from the supplementary tuning circuits. Moreover, we use the bilateral linear approximation to obtain the accurate derivative of the autocorrelation to enhance further the timing-skew mismatch detection. A prototype 16-channel 5 GS/s time-interleaved SAR ADC with a splitting-combined monotonic switching method, implemented in 28 nm CMOS, obtained a SNDR of 48.5 dB/ 47.8dB at 2.38 GHz/ 4.00 GHz, respectively.

#### **REFERENCES**

- [1] J. Wu, C.-Y. Chen, T. Li, L. He, W. Liu, W.-T. Shih, S. S. Tsai, B. Chen, C.-S. Huang, B. J.-J. Hung, H. T. Hung, S. Jaffe, L. Kun Tan, and H. Vu, "A 240-mW 2.1-GS/s 52-dB SNDR pipeline ADC using MDAC equalization," *IEEE J. Solid-State Circuits*, vol. 48, no. 8, pp. 1818–1828, Aug. 2013.

- [2] M. Brandolini et al., "A 5 GS/s 150 mW 10 b SHA-less pipelined/SAR hybrid ADC for direct-sampling systems in 28 nm CMOS," IEEE J. Solid-State Circuits, vol. 50, no. 12, pp. 2922–2934, Dec. 2015.

- [3] B. Razavi, "Design considerations for interleaved ADCs," *IEEE J. Solid-State Circuits*, vol. 48, no. 8, pp. 1806–1817, Aug. 2013.

- [4] M. El-Chammas and B. Murmann, "A 12-GS/s 81-mW 5-bit time-interleaved flash ADC with background timing skew calibration," *IEEE J. Solid-State Circuits*, vol. 46, no. 4, pp. 838–847, Apr. 2011.

- [5] D. Stepanovic and B. Nikolic, "A 2.8 GS/s 44.6 mW time-interleaved ADC achieving 50.9 dB SNDR and 3 dB effective resolution bandwidth of 1.5 GHz in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 48, no. 4, pp. 971–982, Apr. 2013.

- [6] Y.-Z. Lin, C.-H. Tsai, S.-C. Tsou, and C.-H. Lu, "A 8.2-mW 10-b 1.6-GS/s 4× TI SAR ADC with fast reference charge neutralization and background timing-skew calibration in 16-nm CMOS," in *Proc. IEEE Symp. VLSI Circuits (VLSI-Circuits)*, Jun. 2016, pp. 1–2.

- [7] H.-W. Kang, H.-K. Hong, W. Kim, and S.-T. Ryu, "A time-interleaved 12-b 270-MS/s SAR ADC with virtual-timing-reference timing-skew calibration scheme," *IEEE J. Solid-State Circuits*, vol. 53, no. 9, pp. 2584–2594, Sep. 2018.

- [8] J. Song, K. Ragab, X. Tang, and N. Sun, "A 10-b 800-MS/s time-interleaved SAR ADC with fast variance-based timing-skew calibration," IEEE J. Solid-State Circuits, vol. 52, no. 10, pp. 2563–2575, Oct. 2017.

- [9] J. Song, K. Ragab, X. Tang, and N. Sun, "A 10-b 600-MS/s 2-way time-interleaved SAR ADC with mean absolute deviation-based background timing-skew calibration," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 8, pp. 2876–2887, Aug. 2019.

- [10] N. Le Dortz, J.-P. Blanc, T. Simon, S. Verhaeren, E. Rouat, P. Urard, S. Le Tual, D. Goguet, C. Lelandais-Perrault, and P. Benabes, "A 1.62GS/s time-interleaved SAR ADC with digital background mismatch calibration achieving interleaving spurs below 70dBFS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 386–388.

- [11] H. Wei, P. Zhang, B. D. Sahoo, and B. Razavi, "An 8 bit 4 GS/s 120 mW CMOS ADC," *IEEE J. Solid-State Circuits*, vol. 49, no. 8, pp. 1751–1761, Aug. 2014.

- [12] H. Le Duc, D. M. Nguyen, C. Jabbour, P. Desgreys, O. Jamin, and V. T. Nguyen, "Fully digital feedforward background calibration of clock skews for sub-sampling TIADCs using the polyphase decomposition," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 6, pp. 1515–1528, Jun. 2017.

- [13] C.-Y. Lin, Y.-H. Wei, and T.-C. Lee, "A 10-bit 2.6-GS/s time-interleaved SAR ADC with a digital-mixing timing-skew calibration technique," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1508–1517, May 2018.

- [14] D. Li, Z. Zhu, R. Ding, M. Liu, Y. Yang, and N. Sun, "A 10-bit 600-MS/s time-interleaved SAR ADC with interpolation-based timing skew calibration," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 1, pp. 16–20, Jan. 2019.

- [15] M. Guo, J. Mao, S.-W. Sin, H. Wei, and R. P. Martins, "A 1.6-GS/s 12.2-mW seven-/eight-way split time-interleaved SAR ADC achieving 54.2-dB SNDR with digital background timing mismatch calibration," *IEEE J. Solid-State Circuits*, vol. 55, no. 3, pp. 693–705, Mar. 2020.

- [16] M. Guo, J. Mao, S.-W. Sin, H. Wei, and R. P. Martins, "A 29 mW 5GS/s time-interleaved SAR ADC achieving 48.5dB SNDR with fully-digital timing-skew calibration based on digital-mixing," in *Proc. Symp. VLSI Circuits*, Jun. 2019, pp. 76–77.

- [17] M. El-Chammas and B. Murmann, "General analysis on the impact of phase-skew in time-interleaved ADCs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 5, pp. 902–910, May 2009.

- [18] Y. Zhu, C.-H. Chan, U.-F. Chio, S.-W. Sin, S.-P. U, R. P. Martins, and F. Maloberti, "A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 45, no. 6, pp. 1111–1121, Jun. 2010.

- [19] H. Wei, C.-H. Chan, U.-F. Chio, S.-W. Sin, S.-P. U, R. P. Martins, and F. Maloberti, "An 8-b 400-MS/s 2-b-per-cycle SAR ADC with resistive DAC," *IEEE J. Solid-State Circuits*, vol. 47, no. 11, pp. 2763–2772, Nov. 2012.

- [20] C.-H. Chan, Y. Zhu, S.-W. Sin, S.-P. Ben U, and R. Paulo Martins, "A 6 b 5 GS/s 4 interleaved 3 b/Cycle SAR ADC," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 365–377, Feb. 2016.

- [21] C.-C. Liu, S.-J. Chang, G.-Y. Huang, and Y.-Z. Lin, "A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure," *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 731–740, Apr. 2010.

- [22] C.-C. Liu, S.-J. Chang, G.-Y. Huang, Y.-Z. Lin, and C.-M. Huang, "A 1 V 11fJ/conversion-step 10bit 10MS/s asynchronous SAR ADC in 0.18  $\mu$ m CMOS," in *Proc. Symp. VLSI Circuits*, Jun. 2010, pp. 241–242.

- [23] C.-C. Liu, C.-H. Kuo, and Y.-Z. Lin, "A 10 bit 320 MS/s low-cost SAR ADC for IEEE 802.11ac applications in 20 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 50, no. 11, pp. 2645–2654, Nov. 2015.

- [24] J. Fang, S. Thirunakkarasu, X. Yu, F. Silva-Rivas, C. Zhang, F. Singor, and J. Abraham, "A 5-GS/s 10-b 76-mW time-interleaved SAR ADC in 28 nm CMOS," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 7, pp. 1673–1683, Jul. 2017.

- [25] J. P. Keane, N. J. Guilar, D. Stepanovic, B. Wuppermann, C. Wu, C. W. Tsang, R. Neff, and K. Nishimura, "An 8GS/s time-interleaved SAR ADC with unresolved decision detection achieving -58dBFS noise and 4 GHz bandwidth in 28 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 284–285.

- [26] M. Baert and W. Dehaene, "A 5-GS/s 7.2-ENOB time-interleaved VCO-based ADC achieving 30.5 fJ/cs," *IEEE J. Solid-State Circuits*, vol. 55, no. 6, pp. 1577–1587, Jun. 2020.

- [27] B. Murmann. (Apr. 1, 2020). ADC Performance Survey 1997-2020. [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html

**SAI-WENG SIN** (Senior Member, IEEE) received the B.Sc., M.Sc., and Ph.D. degrees in electrical and electronics engineering from the University of Macau, Macau, China, in 2001, 2003, and 2008, respectively. He is currently an Associate Professor with the Department of ECE, Faculty of Science and Technology, also the Deputy Director of academic with the Institute of Microelectronics, and also the Academic Coordinator of the State-Key Laboratory of Analog and Mixed-Signal

VLSI, University of Macau. He has published one book *Generalized Low-Voltage Circuit Techniques for Very High-Speed Time-Interleaved Analog-to-Digital Converters* (Springer), hold seven U.S., three Taiwan patents, and 150 technical journals and conference articles in the field of high-performance data converters and analog mixed-signal integrated circuits.

Dr. Sin is/has been the member of the Technical Program Committee/Review Committee Member of the IEEE Asian Solid-State Circuits Conference (A-SSCC), the International Symposium on Circuits and Systems (ISCAS), the International Conference on Integrated Circuits, Technologies and Applications (ICTA), the International Wireless Symposium, the IEEE SENSORS, and the IEEE RFIT Conference. He was the Secretary of the IEEE Solid-State Circuit Society (SSCS) Macau Chapter (with 2012 IEEE SSCS Outstanding Chapter Award) and the IEEE Macau CAS/COM Joint Chapter (with 2009 IEEE CAS Chapter of the Year Award). He is/has been a Track Chair in TPC of the IEEE TENCON, a Review Committee Member of PrimeAsia, Technical Program and Organization Committee of the 2004 IEEJ AVLSI Workshop, and the Special Session Co-Chair and a Technical Program Committee Member of 2008 IEEE APCCAS Conference. He was a co-recipient of the 2011 ISSCC Silk Road Award, the Student Design Contest Award in A-SSCC 2011, and the 2011 State Science and Technology Progress Award (second-class), China. His co-supervised student received the 2015 SSCS Pre-Doctoral Achievement Award. He served as an Associate Editor for IEEE Access and the IEEE Transaction on Circuits AND SYSTEMS II—EXPRESS BRIEFS.

MINGQIANG GUO (Member, IEEE) received the B. S. degree from Xidian University, Xi'an, China, in 2011, the M.S. degree from Fudan University, Shanghai, China, in 2014, and the Ph.D. degree from the University of Macau, Macau, China, in 2020. His current research interests include analog and mixed-signal integrated circuits design with an emphasis on high-speed data converters.

Dr. Guo was a recipient of the IEEE Circuits and Systems Society (CAS) Scholarship for the

PRIME 2017 Conference, the IEEE Solid-State Circuits Society (SSCS) Student Travel Grant Award for the ISSCC 2019, and the IEEE 2019 Symposia on VLSI Technology and Circuits (VLSI) Travel Grant.

**JIAJI MAO** (Graduate Student Member, IEEE) received the B.S. degree from Xidian University, Xi'an, China, in 2013, and the M.S. degree (Hons.) in electrical and electronics engineering from the University of Macau, Macau, China, in 2018.

His main research interests include analog and mixed-signal integrated circuits design and calibration techniques for high-performance data converters.

**HEGONG WEI** (Member, IEEE) received the B.Sc., M.Sc., and Ph.D. degrees (Hons.) in electrical and electronics engineering from the University of Macau, Macau, China, in 2006, 2008, and 2011, respectively.

He was a Project Leader with the State-Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau. From October 2011 to April 2014, he was a Postdoctoral Fellow with the Circuit Communication Laboratory, University

of California at Los Angeles, Los Angeles. He is currently with Silicon Laboratories, Inc., Austin, TX, USA. He is also a Senior Research Fellow with the Electrical and Computer Engineering Department, The University of Texas at Austin, Austin. His research interests include high speed and high performance data converters and mixed-signal circuits design. He published more than 20 technical journals and conference articles in this field.

Dr. Wei received the Silk-Road Award at ISSCC 2011.

**RUI P. MARTINS** (Fellow, IEEE) was born in April 1957. He received the bachelor's, master's, and Ph.D. degrees, and the Habilitation for Full-Professor in electrical engineering and computers from the Department of Electrical and Computer Engineering (DECE), Instituto Superior Técnico (IST), University of Lisbon, Portugal, in 1980, 1985, 1992, and 2001, respectively. Since October 1980, he has been with the DECE/IST, Universidade de

Lishoa

Since 1992, has been on leave from the Universidade de Lisboa and has also been with the DECE, Faculty of Science and Technology (FST), University of Macau (UM), Macau, China, where he has also been a Chair-Professor, since August 2013. In FST, was the Dean of the Faculty from 1994 to 1997. He has been a Vice-Rector of UM, since 1997. He was also a Co-Founder of Chipidea Microelectronics [now Synopsys-Macao], Macau, from 2001 to 2002. From September 2008 to August 2018, he was a Vice-Rector of research. From September 2018 to August 2023, he was also a Vice-Rector of global affairs. Within the scope of his teaching and research activities, he has taught 21 bachelor's and master's courses and, in UM, has supervised (or co-supervised) 47 theses, Ph.D. (26) and master's (21). He has coauthored books and 12 book chapters; 36 patents, USA (32), Taiwan (three) and China (one); 537 articles, in scientific journals (217), and in conference proceedings (320); and other 64 academic works, in a total of 656 publications. He created in 2003 the Analog and Mixed-Signal VLSI Research Laboratory, UM, elevated in January 2011 to the State Key Laboratory (SKLAB) of China (the 1st in Engineering in Macau), being its Founding Director. He was the Founding Chair of UMTEC (UM company), from January 2009 to March 2019, supporting the incubation and creation in 2018 of Digifluidic, the first UM Spin-Off, whose CEO is a SKLAB Ph.D. graduate.

Prof. Rui Martins was a member of the IEEE CASS Fellow Evaluation Committee, in 2013, 2014, and 2018. In July 2010 was elected, unanimously, as a Corresponding Member of the Lisbon Academy of Sciences, being the only Portuguese Academician living in Asia. He was a Founding Chair of the IEEE Macau Section, from 2003 to 2005, and the IEEE Macau Joint-Chapter on Circuits And Systems (CAS)/Communications (COM), from 2005 to 2008 [2009 World Chapter of the Year of IEEE CAS Society (CASS)], a General Chair of the IEEE Asia-Pacific Conference on CAS-APCCAS'2008, the Vice President (VP) Region ten (Asia, Australia, and Pacific) from 2009 to 2011, and a VP-World Regional Activities and Membership of IEEE CASS, from 2012 to 2013. He was a Chair of the IEEE CASS Fellow Evaluation Committee, in 2019 and 2021. He was the IEEE Nominating Committee of Division I Director (CASS/EDS/SSCS), in 2014, and the IEEE CASS Nominations Committee, from 2016 to 2017. He was the General Chair of the ACM/IEEE Asia South Pacific Design Automation Conference (ASP-DAC), in 2016, receiving the IEEE Council on Electronic Design Automation (CEDA) Outstanding Service Award, in 2016, and also the General Chair of the IEEE Asian Solid-State Circuits Conference-A-SSCC 2019. He was also the Vice President from 2005 to 2014 and the President from 2014 to 2017 of the Association of Portuguese Speaking Universities (AULP), and received two Macao Government decorations: the Medal of Professional Merit (Portuguese-1999); and the Honorary Title of Value (Chinese-2001). He was an Associate Editor of the IEEE Transactions ON CAS II: Express Briefs, from 2010 to 2013, nominated as a Best Associate Editor, from 2012 to 2013.

. . .