Received June 30, 2020, accepted July 12, 2020, date of publication July 14, 2020, date of current version July 24, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.3009286

# Innovative Theory of Low-Pass NGD via-Hole-Ground Circuit

BLAISE RAVELO<sup>®1</sup>, (Member, IEEE), FAYU WAN<sup>®1</sup>, (Member, IEEE), SÉBASTIEN LALLÉCHÈRE<sup>2</sup>, (Member, IEEE), WENCESLAS RAHAJANDRAIBE<sup>®3</sup>, (Member, IEEE), PREETI THAKUR<sup>®4</sup>, AND ATUL THAKUR<sup>®5</sup>

Corresponding author: Fayu Wan (fayu.wan@nuist.edu.cn)

This work was supported in part by the NSFC under Grant 61971230 and Grant 61601233, in part by the Jiangsu Distinguished Professor Program and Six Major Talents Summit of Jiangsu Province under Grant 2019-DZXX-022, in part by the Postgraduate Research and Practice Innovation Program of Jiangsu Province under Grant SJKY19\_0974, and in part by the Priority Academic Program Development of Jiangsu Higher Education Institutions (PAPD) Fund.

**ABSTRACT** The via ground (GND) structure constitutes one of the most useful elements for designing high performance printed circuit boards (PCBs). The electrical interconnections with vias become key regular solutions for the implementation of various electronic functions. However, so far, the vias are never being used for designing negative group delay (NGD) circuit. To answer this curious question, an original study on the design feasibility of low-pass NGD function with via ground is introduced in the present paper. After the topological description, the NGD analysis in function of the via parameters is established. The design equations allowing to synthesize the via in function of NGD function specifications are formulated. The developed NGD theory is verified with comparisons between calculations and simulations with a commercial tool. As expected, NGD value in order of hundred-picoseconds over hundred-megahertz cut-off frequencies is obtained with good agreement between the theoretical model and simulation. Furthermore, time domain analyses confirm that the via NGD structure enables to generate output signals in time-advance of arbitrary waveform input signals presenting limited bandwidth.

**INDEX TERMS** Analytical modelling, cylindrical via, low-pass negative group delay (NGD), microstrip circuit, via-hole ground.

#### I. INTRODUCTION

To increase the performance of modern analog and digital communication devices, innovative and diverse electronic functions were developed. Nowadays, these electronic functions tend to be designed and integrated in high density (HD) printed circuit boards (PCBs) [1]–[3]. However, the design of HD PCBs requires complex electrical interconnections. In order to predict these PCB performances, effective models of their constituting elements as interconnections are necessary.

# A. STATE OF THE ART ON THE USE OF VIA ELEMENT FOR PCB DESIGN

Among the key elements constituting the PCBs, the via-holes are playing an important role to design high-performance

The associate editor coordinating the review of this manuscript and approving it for publication was Poki Chen .

packaged components and PCBs [4]–[15]. The via enables to simplify and to shorten the connections between different components at optimized position of PCBs. The modelling and characterization of vias are one of attractive research topics of electronic research engineers.

In early 1990s, a pioneer equivalent circuit of microstrip via hole ground (GND) was proposed [4]. Further improvement has been made to extend the model to higher frequencies [5]. As the equivalent model is limited to certain cases of elementary structures, alternative full-wave numerical models have been developed with the boom of computer aided designs [6]–[8]. Behind the development of the modelling and computation methods, characterization techniques are needed especially in function of design complexity [9]–[13]. A via modelling approach for via-hole characterization on Silicon substrate in *K*-band is developed in [13].

<sup>&</sup>lt;sup>1</sup>School of Electronic and Information Engineering, Nanjing University of Information Science and Technology (NUIST), Nanjing 210044, China

<sup>&</sup>lt;sup>2</sup>CNRS, Institut Pascal, SIGMA Clermont, Université Clermont Auvergne (UCA), 63000 Clermont-Ferrand, France

<sup>&</sup>lt;sup>3</sup>CNRS, Aix-Marseille University, University of Toulon, IM2NP UMR7334, 13013 Marseille, France

<sup>&</sup>lt;sup>4</sup>Physics Department, Amity University Haryana, Gurgaon 122413, India

<sup>&</sup>lt;sup>5</sup> Amity Centre of Nanotechnology, Amity University Haryana, Gurgaon 122413, India

The via models were exploited to improve the performance and to optimize design PCBs especially in multilayer technology [10], [11]. The vias are useful to miniaturize high-frequency circuits to realize certain microwave functions as filters [14], [15]. However, the utilities of via for classical RF and microwave functions are well-known topics in the area of packaging engineering, electromagnetic compatibility (EMC), signal integrity (SI) [16], [17] and in integrated circuit design [18]–[20].

However, so far, an emerging research topic is progressively evolving for the study of an unfamiliar electronic function with negative group delay (NGD) phenomenon [21]–[27].

#### B. STATE OF THE ART ON NGD FUNCTIONS

The meaning of NGD function was illustrated theoretically and experimentally with the observation of time-advanced output signals [28]–[33]. It is noteworthy that this NGD function signature does not contradict the causality [30], [31]. Tentative applications of NGD function for the corrections of group delay (GD) [34], [35] and undesirable parasitic effects [36] have been proposed. Nevertheless, the NGD function remains one of the most unfamiliar functions for electronic design and fabrication engineers because of its counterintuitive effects compared to natural and classical signal propagations. In fact, the NGD function is often misunderstood and even somehow hard to believe for many electronic, RF and microwave circuit designers.

To face up this technical misunderstanding, more pedagogical researches have been conducted by demonstrating the analogy between NGD and classical filter electronic functions [37], [38]. By referring with the frequency band and the negative sign of the GD, the concept of low-pass (LP) and bandpass (BP) NGD functions have been introduced [37], [38]. In the area of RF and microwave engineering, most of existing NGD circuits were implemented in microstrip technology to work as BP NGD functions [21]-[27]. Regarding electromagnetic compatibility expectations, the existence of NGD functions was demonstrated when dealing with microstrip crosstalk [28]. Similar to all electronic functions, the physical sizes constitute one of major criteria for the qualification of NGD circuit performances. In this optic, research works have been made to design compact NGD circuits [21], [22], [25].

#### C. NOVELTY OF NGD CIRCUIT CONSTITUTING ELEMENTS

The democratization of NGD functions in the area of electronic and RF/microwave engineering depends on the understandability, theorization and design feasibility with their constituting components. Despite the encouraging research performed by few NGD research teams around the world, and because of its counterintuitive aspect, the NGD function is not considered as normal classical electronic functions as filters, antennas, phase shifters, amplifiers, coupler, power dividers/combiners and so on...So far, the NGD topologies available in the literature are essentially implemented with

• lumped R, L and C components,

TABLE 1. State of the art on components constituting NGD topologies.

|   | Elements                               | NGD function               | Theory        | References    |

|---|----------------------------------------|----------------------------|---------------|---------------|

| • | R, L and C<br>lumped<br>components     | Low-pass and bandpass NGDs | Available     | [30-33,37-38] |

| • | Distributed microstrip lines           | Bandpass NGD               | Available     | [21-27]       |

|   | Transistor and RLC-networks            | Low-pass and bandpass NGDs | Available     | [37-38]       |

| • | Operational amplifier and RLC-elements | Low-pass and bandpass NGDs | Available     | [30-33]       |

| _ | Via ground structure                   | Low-pass                   | Not available | Present work  |

- microstrip transmission lines,

- and active elements as operational amplifiers and transistors.

However, as illustrated in Table 1, no study on NGD topology based on via elements is available. The novelty of the present study is answering to this typical research curiosity for understanding how a via element is susceptible to behave as a low-pass NGD function.

Despite the popularity of via integration in HD PCBs [4]–[15]–[17], curious questions were legitimately wondered by research engineers considering emerging circuit topologies as electronic NGD functions. In the best of the author's knowledge, nowadays, the design of NGD circuit based on via-hole is not available in the literature. This reason of originality is the main motivation of the present research paper.

### D. OUTLINE OF THE PAPER

For the better organization, the paper is presented mainly in four sections:

- Section II describes the novel via structure design and physical parameters. Based on the electrical equivalent circuit, the S-matrix model of the via circuit will be established in function of the physical parameters.

- Section III is focused on the innovative theory of via-hole ground. The theoretical investigation is based on the low-pass (LP) NGD analysis. The group delay (GD) will be innovatively expressed in function of the assumed via parameters. The NGD synthesis design equations will be established in function of the desired low-pass NGD function specifications.

- Section IV examines the feasibility of the via-NGD theory with a proof-of-concept (PoC). The design issue will be described. Comparisons between frequency and time domain analysis, never being achieved before, will be discussed.

- Then, Section V is the final conclusion.

# II. DESCRIPTION OF THE VIA-HOLE GROUND STRUCTURE UNDER STUDY

The present section will explore the new NGD structure constituted by a via GND. The design and physical

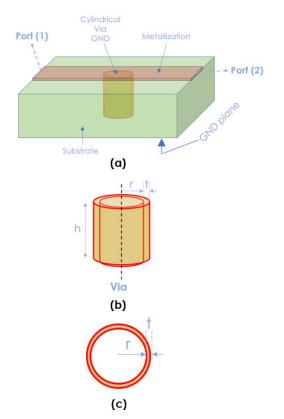

FIGURE 1. 3-D design of (a) the via-hole ground integrated in microstrip structure, and (b) profile and (c) top views of the cylindrical via-hole.

parameters will be defined. Then, the novel representation of equivalent S-matrix general model will be expressed analytically.

### A. 3-D DESIGN GEOMETRY

This description of the via-hole structure 3-D geometry will be explored in this subsection. The description includes the definition of the physical representation. The main originality of the structure can be understood compared to the existing NGD circuits [20]–[36]. In the present subsection, the proposed via structure is used to generate the NGD function with outstanding simplicity. To generate the unfamiliar NGD function, a PCB design constituted by a dielectric substrate integrating via structure is introduced.

Fig. 1(a) represents the perspective view of 3-D design of the via GND. This innovative NGD circuit is implemented as a microstrip structure. The substrate is a dielectric material. The top plane side is constituted by the metallized conductor strip line serves for the access port connections. The bottom side is represented by metallized GND plane. Fig. 1(b) shows the perspective view of the cylindrical via constituted by metallic holed with circular cylindrical shape. Fig. 1(c) presents the top view of the via. The physical parameters of the constituting metallic cylindrical holed via are defined by internal radius, r, metal thickness, t, and height, h.

## B. ELECTRICAL EQUIVALENT CIRCUIT

The innovative way to developed the innovative NGD theory of the via-hole is established from equivalence principle.

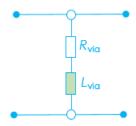

FIGURE 2. Equivalent circuit of via-hole ground.

The main idea consists in considered the electrical equivalent circuit of the 3-D designed via introduced in the previous subsection.

According to the equivalence concept, we can start with the fact that the via hole introduced in Fig. 1(b) is equivalent to series RL-network as depicted in Fig. 2 [4].

At lower frequencies, by denoting the metal conductivity  $\sigma$ , relative permeability  $\mu_r$ , and vacuum absolute permeability  $\mu_0 = 4\pi 10^{-7}$  SI, the cylindrical via is equivalent to a shunt impedance of series RL-network with electrical parameters:

$$R_{via} = \frac{h}{\pi \sigma \left[r^2 - (r - t)^2\right]} \tag{1}$$

$$L_{via} = \frac{\mu_r \mu_0 \left[ 2h \ln(x) + 3y \right]}{\pi}$$

(2)

where:

$$x = \frac{h + \sqrt{r^2 + h^2}}{r} \tag{3}$$

$$y = r - \sqrt{r^2 + h^2}. (4)$$

Before the exploration of the novel NGD analysis of the via, the analytical modelling of the equivalent S-matrix model will be described in the next subsection.

#### C. S-MATRIX MODELLING

Along the paper, the angular frequency variable is denoted by:

$$\omega = 2\pi f. \tag{5}$$

Based on the via GND equivalent circuit shown in Fig. 2, the shunt-impedance analytical model is expressed as:

$$Z_{via}(j\omega) = R_{via} + j\omega L_{via}.$$

(6)

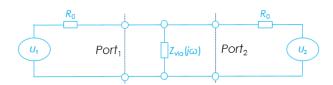

To model the via structure S-matrix, we can consider the two-port equivalent circuit of Fig. 3 with terminal reference impedance,  $R_0 = 50 \Omega$ .

The voltage sources, named,  $U_1(j\omega)$  and  $U_2(j\omega)$ , serve to excite the circuit. Acting as a symmetric and passive network, the S-matrix model of the circuit established in Fig. 2 is written as:

$$[S(j\omega)] = \begin{bmatrix} S_{11}(j\omega) & S_{21}(j\omega) \\ S_{21}(j\omega) & S_{11}(j\omega) \end{bmatrix}.$$

(7)

It can be demonstrated analytically that the S-matrix coefficients are expressed as:

$$S_{11}(j\omega) = \frac{R_0}{R_0 + 2Z_{via}(j\omega)} \tag{8}$$

$$S_{11}(j\omega) = \frac{R_0}{R_0 + 2Z_{via}(j\omega)}$$

(8)

$$S_{21}(j\omega) = \frac{2Z_{via}(j\omega)}{R_0 + 2Z_{via}(j\omega)}.$$

(9)

FIGURE 3. S-matrix modeling diagram with the via equivalent model.

The innovative LP NGD theory based on the structure of via-ground hole will be based on this expression of the transmission coefficient. The following section will develop in details the proposed NGD theory.

# III. INNOVATIVE NGD THEORY OF THE VIA-GROUND HOLE CIRCUIT

This section introduces the novel theory of LP NGD function design with a via NGD circuit. After the recall on the LP NGD specifications, the new NGD modelling methodology based on the S-matrix frequency response model is introduced. Then, the NGD analysis and synthesis equations will be elaborated.

#### A. RECALL ON LOW-PASS NGD FUNCTION DEFINITION

Similar to the classical microwave filter, the LP NGD circuit must be designed with ideal parameters calculated from the expected reflection and transmission coefficients, and NGD specifications. We can denote the specifications as follows:

- the minimal and maximal reflection coefficients,  $(S_{11\min}, S_{11\max})$ ,

- the minimal and maximal transmission coefficients,  $(S_{21\min}, S_{21\max})$ ,

- and the design value of NGD,  $\tau_n$ .

With low-pass NGD angular cut-off frequency:

$$\omega_n = 2\pi f_n \tag{10}$$

we have:

$$\begin{cases} GD(\omega) \le 0 & \text{if } \omega \le \omega_n \\ GD(\omega) > 0 & \text{if } \omega > \omega_n. \end{cases}$$

(11)

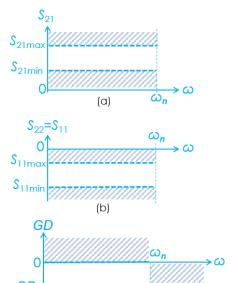

In general, based on graphical representation, the ideal specifications of NGD function can be represented by the three diagrams of Figs. 4.

### **B. S-PARAMETER FREQUENCY RESPONSES**

Before the NGD analysis, it is worth to elaborate the frequency responses of the via structure S-parameter model.

# 1) MAGNITUDE AND PHASE RESPONSES

The magnitudes of the reflection and transmission coefficients expressed in equations (8) and (9) can be written as:

$$S_{11}(\omega) = |S_{11}(j\omega)| = \frac{R_0}{\sqrt{(R_0 + 2R_{via})^2 + 4L_{via}^2 \omega^2}}$$

(12)

$$S_{21}(\omega) = |S_{21}(j\omega)| = \frac{2\sqrt{R_{via}^2 + L_{via}^2 \omega^2}}{\sqrt{(R_0 + 2R_{via})^2 + 4L_{via}^2 \omega^2}}.$$

(13)

FIGURE 4. Typical specifications of low-pass NGD function:

(a) transmission, (b) reflection coefficient and (c) GD responses.

The transmission phase frequency response corresponding to the quantity given previously defined by:

$$\varphi(\omega) = \arg\left[S_{21}(j\omega)\right] \tag{14}$$

is expressed as:

$$\varphi(\omega) = \arctan\left(\frac{L_{via}\omega}{R_{via}}\right) - \arctan\left(\frac{2L_{via}\omega}{R_0 + 2R_{via}}\right).$$

(15)

#### 2) GD RESPONSES

The main novelty of the NGD theory present study concerns the analytical demonstration of LP design feasibility of via-GND hole structure introduced in Section II. The NGD theory is substantially developed from the transmission parameter via GD expression.

Accordingly, the analytical approach is based on the GD associated to the transmission phase expressed previously via the relation:

$$GD(\omega) = \frac{-\partial \varphi(\omega)}{\partial \omega}.$$

(16)

Substituting equation (15) into the previous analytical definition, we can establish the innovative analytical expression of via structure GD:

$$GD(\omega) = \begin{bmatrix} \frac{2L_{via}(R_0 + 2R_{via})}{(R_0 + 2R_{via})^2 + 4L_{via}^2 \omega^2} \\ -\frac{R_{via}L_{via}}{R_{via}^2 + L_{via}^2 \omega} \end{bmatrix}.$$

(17)

### C. NOVEL LP NGD ANALYSIS OF VIA-HOLE STRUCTURE

The present subsection established the original NGD analysis enabling to demonstrate theoretically why the via-structure is susceptible to behave as a LP NGD function.

The LP NGD analysis is based on the transmission coefficient given in equation (13) and especially the GD expressed in the previous paragraph. It can be demonstrated analytically that the NGD cut-off frequency which is the root of equation:

$$GD(\omega) = 0 \tag{18}$$

is equal to:

$$\omega_n = \frac{\sqrt{2R_{via}(R_0 + 2R_{via})}}{2L_{via}}.$$

(19)

Moreover, at very low frequencies,  $\omega \approx 0$ , the GD established in (17) is reduced as:

$$GD_0 = GD(\omega \approx 0) = \frac{-R_0 L_{via}}{R_{via}(R_0 + 2R_{via})}$$

(20)

or:

$$GD_0 = \frac{-R_0}{\omega_n \sqrt{2R_{via}(R_0 + 2R_{via})}}.$$

(21)

The reflection and transmission parameters formulated in equations (12) and (13) become, respectively:

$$S_{11}(0) = \frac{R_0}{R_0 + 2R_{via}}$$

$$S_{21}(0) = \frac{2R_{via}}{R_0 + 2R_{via}}.$$

(22)

$$S_{21}(0) = \frac{2R_{via}}{R_0 + 2R_{via}}. (23)$$

It can be seen that the via-structure can be designed with these coefficients satisfying the reflection and transmission coefficient requirements in function of targeted RF and microwave applications:

$$S_{11}(0) < S_{11_{\text{max}}} \tag{24}$$

$$S_{21}(0) > S_{21_{\min}}.$$

(25)

It means from the present paragraph analysis that the via structure introduced in Figs. 1 is qualified as a LP NGD function with GD cut-off frequency and GD value formulated in equations (18) and (20), respectively.

# D. SYNTHESIS DESIGN EQUATIONS OF VIA PARAMETERS

The NGD analysis consists in studying the sign of transmission coefficient GD in function of the operating angular frequency. Nevertheless, similar to all RF and microwave circuits, the NGD analysis must be performed by taking into account to the requirements expected to  $S_{11_{max}}$  and  $S_{21_{min}}$  values. The NGD synthesis design equations of the via structure can be established by determining the parameters r, t and  $\sigma$  in function of desired NGD specifications:

· NGD value:

$$\tau_n < 0 \tag{26}$$

• NGD cut-off frequency:

$$f_n = \omega_n / (2\pi) \tag{27}$$

And transmission coefficient:

$$S_{21_n} < 1$$

(28)

· Or reflection coefficient:

$$S_{11} < 1.$$

(29)

The innovative design equations are established from the following equation system:

$$\begin{cases} GD_0(R_{via}, L_{via}) = \tau_n \Leftrightarrow \omega_n(R_{via}, L_{via}) = \tau_n \\ S_{21}(R_{via}, L_{via}) = S_{21_n} \end{cases}$$

$$\begin{cases} GD_0(R_{via}, L_{via}) = \tau_n \Leftrightarrow \omega_n(R_{via}, L_{via}) = \tau_n \\ S_{11}(R_{via}, L_{via}) = S_{11_n}. \end{cases}$$

(31)

$$\begin{cases} GD_0(R_{via}, L_{via}) = \tau_n \Leftrightarrow \omega_n(R_{via}, L_{via}) = \tau_n \\ S_{11}(R_{via}, L_{via}) = S_{11_n}. \end{cases}$$

(31)

Accordingly, by considering the insertion loss requirement, we have the formulas:

$$R_{via} = \frac{R_0 S_{21_n}}{2(1 - S_{21_n})} \tag{32}$$

$$L_{via} = \frac{-R_0 S_{21_n} \tau_n}{2(1 - S_{21_n})^2}.$$

(33)

However, with reflection loss requirement, the design equations are written as:

$$R_{via} = \frac{R_0(1 - S_{11_n})}{2S_{11_n}} \tag{34}$$

$$R_{via} = \frac{R_0(1 - S_{11_n})}{2S_{11_n}}$$

$$L_{via} = \frac{R_0(S_{11_n} - 1)\tau_n}{2S_{11_n}^2}.$$

(34)

To illustrate the feasibility of the NGD via theory, a PoC will be examined in the next section.

# IV. PROOF-OF-CONCEPT INVESTIGATION OF LP NGD **GENERATION WITH VIA STRUCTURE**

The present section deals with the applicative study of the previously developed innovative NGD theory of via-GND hole. The established equations will be exploited to determine an example of via structure generating LP NGD function presenting specifications:

$$\begin{cases} S_{11}(f \approx 0) = -10 \ dB \\ S_{21}(f \approx 0) = -3 \ dB. \end{cases}$$

(36)

The numerical calculations are performed with Matlab programming of the analytical model established in the previous section. Deep analysis about the practical design issue of via structure-based LP NGD circuit is introduced. Comparisons of calculated and simulated frequency and time domain results are discussed to illustrate the feasibility of the NGD via design.

### A. INVESTIGATION ON VIA PARAMETER CALCULATION FROM GIVEN NGD SPECIFICATIONS

Acting as particularly new NGD circuit design, it would be important to illustrate the influence of the constituting electrical and physical parameters on the NGD performances. For this reason, we present a particular innovative parametric analysis based on the previously established synthesis equations will be proposed in the following paragraphs.

**VOLUME 8, 2020**

130176

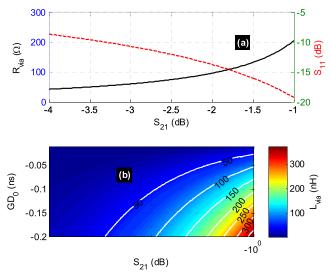

FIGURE 5. Plots of (a)  $R_{via}$  and  $S_{11}(0)$  graphs vs  $S_{21}(0)$  and cartography of  $L_{via}$  vs  $(S_{21}(0), GD_0)$ .

The analysis will provide key knowledge on the designability and also the prediction of the NGD performance in function of the design concept. Before the exploration of NGD structure, we propose a numerical synthesis of via parameters in function of NGD specifications.

# 1) LP NGD CALCULATION OF $R_{\emph{via}}$ AND $L_{\emph{via}}$ IN FUNCTION OF REFLECTION AND TRANSMISSION COEFFICIENTS

By considering  $S_{21}(0)$  varying from -4 dB to -1 dB, we can plot the via resistance by means of formula (32) displayed in Fig. 5(a). To reach  $S_{21}(0)$  in the considered range of insertion loss, the resistance must be between 43  $\Omega$  and 205  $\Omega$ . As indicated in right legend of Fig. 5(a), the reflection coefficient varies from -19 dB to -9 dB. It can be deduced from this graph that  $R_{via} \approx 60 \Omega$  to obtain  $S_{21}(0) \approx -3$  dB and  $S_{11}(0) \approx -10 \text{ dB}.$

In addition to  $S_{21}$ , we considered an NGD range of value  $GD_0$  from -0.2 ns to -10 ps as initial and given specifications to determine  $L_{via}$ . After numerical calculations via formula (33), we obtain the cartography of  $L_{via}$  varying from 11.7 nH to 45.1 nH. As expected, it can be seen in Fig. 5(b) that  $L_{via}$  is proportional to  $S_{21}(0)$  and absolute value of  $GD_0$ . It can be deduced from this mapping cartography that  $L_{via} \approx 20$  nH to obtain  $S_{21}(0) = -3$  dB and  $GD_0 = -0.1$  ns.

The proposed innovative results based on the new method emphasized in the previous section permits to emphasize that these values of circuit parameters can serve to determine the NGD via physical parameters. Therefore, numerical plotting of NGD via physical parameters based on formulas introduced in Section II-B will be explored in the next paragraph.

# 2) HOLOGRAPHICAL PLOT OF VIA ELECTRICAL PARAMETERS VERSUS PHYSICAL PARAMETERS

In the rest of the paper, we assume that the via metallic material is characterized by relative permeability  $\mu_r = 1$ . To determine  $R_{via}$  and  $L_{via}$ , the Matlab computations

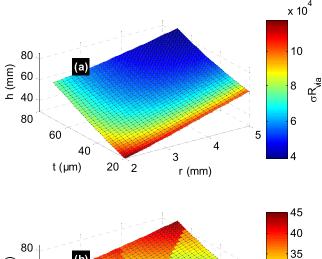

FIGURE 6. Cartographies of (a)  $\sigma R_{via}$  and (b)  $L_{via}$  versus (r, t).

generating the results depicted in Figs. 6 have been performed with via geometrical parameters, chosen arbitrarily, respectively:

- radius r varied from 2 mm to 5 mm,

- thickness t varied from 20  $\mu$ m to 70  $\mu$ m,

- and height h varied from 29 mm to 84 mm.

After numerical calculation via formula (1), we obtain the cartography of the conductivity-resistance product  $\sigma \times R_{via}$ displayed in Fig. 6(a). It can be noticed that this quantity varies from about  $4 \times 10^4$  to  $12 \times 10^4$ . This mapping enables to suggest the via metal conductivity range of value to get the reasonable value corresponding to the targeted specifications  $S_{21} \approx -3$  dB and  $S_{11} \approx -10$  dB. The same, by means of formula (2), the cartography of  $L_{via}$  versus via radius rand thickness t shown in Fig. 6(b) was established. It can be underlined that in the considered range of via geometrical parameters, Lvia varies from 12 nH to 45 nH.

The present mapping investigation enables to situate the ranges of values of r, t and h allowing to synthesize a via NGD satisfying the expected specifications. However, as proposed in Fig. 6(a), the via metal material conductivity was not explored rigorously. For this reason, we realize the numerical investigation taking into account the conductivity in the next paragraph.

# 3) GD, REFLECTION AND TRANSMISSION PARAMETER MAPPINGS VERSUS METALLIZATION CONDUCTIVITY AND THICKNESS

The present numerical investigation is based on the combinations of

**TABLE 2.** Numerical computation parameters for the GD and S-parameter mappings.

| Nature      | Parameter    | Designation       | Value   |

|-------------|--------------|-------------------|---------|

|             | Radius       | r                 | 3 mm    |

| Geometrical | Height       | h                 | 5 cm    |

| Geometricai | Thickness    | $t_{ m min}$      | 10 μm   |

|             |              | $t_{\rm max}$     | 90 μm   |

| Electrical  | Conductivity | $\sigma_{ m min}$ | 100 S/m |

| Electrical  |              | $\sigma_{ m max}$ | 1 kS/m  |

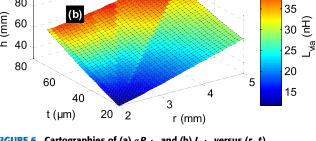

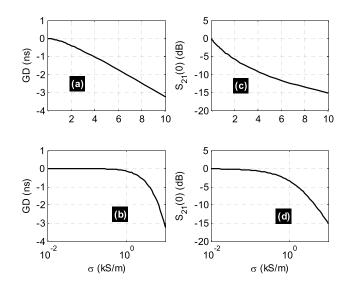

**FIGURE 7.** Cartography of via structure (a) GD, (b)  $S_{21}(0)$  and (c)  $S_{11}(0)$  in function of metallization thickness and conductivity.

- circuit parameters  $R_{via}$  and  $L_{via}$  introduced in formulas (1) and (2), respectively,

- and the GD,  $S_{21}$  and  $S_{11}$  introduced in formulas (12), (13) and (17), respectively.

As initial given date, we have assumed the metallization parameters addressed in Table 2. Therefore, we obtain the mappings shown in Figs. 7.

Fig. 7(a) displays the mapping of GD versus thickness and conductivity in the considered ranges of value. It can be emphasized that the GD is always negative and presents minimal value,  $GD_{min} = -0.31$  ns and maximal value,  $GD_{max} = -0.8$  ps. The corresponding S-parameters are introduced in Fig. 7(a) and in Fig. 7(b). The best compromises are realized for lower values of the via thickness and conductivity. It is noteworthy that the transmission coefficient  $S_{21}$  is better than -6 dB and reflection coefficient  $S_{11}$  is better than -9 dB.

For further rigorous visualization of conductivity effect, graphical plotting's of  $GD_0$  and  $S_{21}(0)$  by fixing  $t=50~\mu\mathrm{m}$  are depicted in Figs. 8. It can be understood from Fig. 7(a) an Fig. 8(b) that the NGD absolute value  $|GD_0|$  and from Fig. 8(c) and Fig. 8(d) that insertion less  $S_{21}(0)$  increase with the metallic conductivity.

**FIGURE 8.** Via structure GD (in (a) linear and (b) semi-log scale) and  $S_{21}(0)$  (in (c) linear and (d) semi-log scale) versus metallization conductivity.

The results of GD, reflection and transmission coefficient responses exposed in Figs. 7 and in Figs. 8 enable to raises a deep analysis about the practical design issue constituting the particularity of via-structure NGD design. Particular technological attention must be paid by the design research engineers on:

- The conductivity of the material constituting the cylindrical via introduced earlier in Fig. 1(b). Compared to the familiar conductor as Copper, Silver, Aluminum or Gold, material with low conductivity in order of hundreds of Siemens per second seems adequate to generate NGD with minus hundredth nanosecond value with low-attenuation loss and good access matching.

- The thickness of the hole cylindrical via plays an important role on the NGD performances (NGD value, NGD bandwidth), attenuation loss and reflection coefficients.

More depth analysis about the design results of via-structure will be described in the following subsection with S-parameter responses up to 0.7 GHz.

# B. VALIDATION RESULTS OF LP NGD RESPONSES FROM VIA-HOLE INNOVATIVE DESIGN

Based on the previous numerical investigation, NGD via proof-of-concept was chosen and comparative feasibility study between the calculated model and simulation results are discussed in the next paragraphs.

### 1) FREQUENCY DOMAIN ANALYSIS OF VIA PROOF-OF-CONCEPT

To generate NGD of about -0.1 ns under the S-parameter specifications predicted in the previous subsections, metallic conductivity less than 1 kS/m seems to be a good compromise, Substantially, as proof-of-concept, a via GND structure defined with the physical parameters summarized in Table 3 was considered.

**TABLE 3.** Physical parameters for the via GND structures.

| Parameter | r    | h    | t     | $\sigma_{ m min}$ | $\sigma_{ m max}$ |

|-----------|------|------|-------|-------------------|-------------------|

| Value     | 3 mm | 5 cm | 50 μm | 0.5 kS/m          | 1 kS/m            |

TABLE 4. Calculated very low frequency parameters corresponding to the results of Figs. 9.

| Conductivity | 0.7 kS/m  | 0.9 kS/m  | 1 kS/m   |

|--------------|-----------|-----------|----------|

| $GD_0$       | -68 ps    | -0.1 ns   | -0.12 ns |

| $f_n$        | 665 MHz   | 536 MHz   | 490 MHz  |

| $S_{21}(0)$  | -2.4 dB   | -3.04 dB  | -3.33 dB |

| $S_{11}(0)$  | -12.12 dB | -10.59 dB | -9.94 dB |

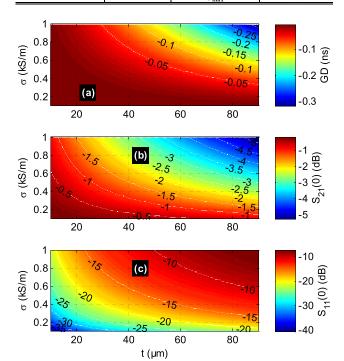

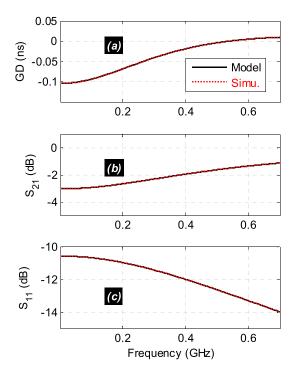

**FIGURE 9.** Calculated frequency responses: (a) GD, (b) transmission and (b) reflection coefficients of NGD via structure for conductivities  $\sigma = \{0.7 \text{ kS/m}, 0.9 \text{ kS/m}, 1 \text{ kS/m}\}.$

The frequency analyses have been performed from  $f_{min} = 1$  MHz to  $f_{max} = 0.7$  GHz. The frequency dependent GD,  $S_{21}$  and  $S_{11}$  models are calculated from formulas (12), (13) and (17), respectively. By considering three values of conductivity  $\sigma = \{0.7 \text{ kS/m}, 0.9 \text{ kS/m}, 1 \text{ kS/m}\}$ , we obtain the calculated results displayed in Figs. 8. It can be seen that typical LP NGD responses with GD values and cut-off frequencies, transmission coefficient, and reflection coefficients addressed in Table 4 are obtained.

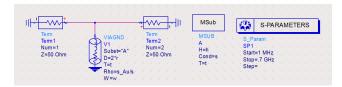

To confirm the efficiency of the present NGD via theory, S-parameter simulations have been performed with ADS@commercial tool from Keysight Technologies®. Fig. 10 highlights the ADS® implementation of the via structure and also the simulation parameters.

As results, the comparison between calculated and simulated ("Simu.") frequency responses from via PoC having physical parameters addressed in Table 3 and  $\sigma=0.9$  kS/m introduced in Figs. 11 are obtained.

FIGURE 10. ADS® design configuration of simulated via structure.

FIGURE 11. Comparative frequency response results of via GND PoC between modeled and simulated ("Simu.") (a) GD, (b)  $S_{21}$  and (c)  $S_{11}$ .

An excellent agreement between the calculation and simulation is confirmed by this result. It can be emphasized from this S-parameter analysis that a via GND structure can behave as a LP NGD function.

A particularly deep analysis about the via NGD design can be emphasized from the wideband frequency results. The main innovative remarks from the obtained results can be stated as follows:

- The NGD response is particularly sensitive to the via material conductivity of about hundreds of Siemens per second. The synthesis of such materials constituted a challenging task of RF and microwave material synthesizer.

- Compared to the familiarly designed via constituting the PCBs, in the present feasibility simulation study, we can understand that via with some millimeter diameters is necessary to generate hundredth minus nanosecond NGD value with considerable matching and low attenuation loss.

- Of course, the height of substrate, *h*, indicated in Table 3 is unconventional compared to the standard PCBs available in the market. Therefore, the design of via-structure NGD circuit requires a future challenge on the design

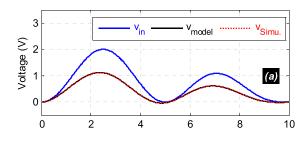

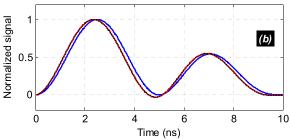

FIGURE 12. Calculated and simulated time-domain responses of via GND circuit.

of conventional thickness PCBs to achieve the expected NGD performances under low attenuation loss of about 3 dB and good reflection coefficient.

#### 2) TIME-DOMAIN ANALYSIS

As input  $v_{in}$ , the double pulse signal presenting arbitrary waveform with about 5 ns pulse time width and 2 V amplitude was considered for this time-domain analysis. The transient investigation was performed in 10 ns time window with 0.2 ns time step. It is important to note that to verify the NGD aspect, the input signal must be limited in bandwidth with frequency spectrum belonging into the NGD bandwidth.

After numerical calculation and ADS® transient simulations, we obtain the transient results displayed in Fig. 12(a).

The calculated and simulated outputs represented by  $v_{model}$  and  $v_{Simu}$ , respectively are in excellent correlation. Acting as a passive circuit, the outputs are attenuated compared to the input. It can be pointed out from normalized plots presented in Figs. 12(b) that the via GND structure generates the typical LP NGD function signature with the output signal in time advance of about  $GD_0 = -0.1$  ns compared to the input. It is important to underline that this LP NGD signature does not contradict the causality.

# C. DISCUSSION ON POTENTIAL APPLICATION OF NGD VIA CIRCUITS

The proposed via structure presents notable advantages as the analytical investigation possibility and design simplicity compared to the existing NGD circuits [21]–[36]. However, as ongoing research work, further investigation can be performed on the integration and conductor material design for the implementation of miniaturized via NGD circuits.

Moreover, as potential applications, the via NGD structure can be exploited for:

- the enhancement of GD flatness and the minimization of unwanted GD effects [40], [41] in the communication systems,

- the high-density packaged PCB RC, LC and RLC parasitic effects (including coupling effects) based on the equalization technique as introduced in [37],

- the reduction and cancellation of communication signal delays,

- and the equalization of the fading channels by integrating in the receiver antenna systems.

#### **V. CONCLUSION**

An RF and microwave circuit innovative theory of LP NGD function is investigated. The key research contribution of the study is stated with the first-time theorization and design LP NGD circuit fully based on via GND structure. The physical design of via structure and its equivalent circuit model is described. Thanks to the S-parameter model, the NGD analysis showing analytically the LP NGD existence and design feasibility is developed. The synthesis design equations of via structure parameters in function of the desired NGD specifications are formulated.

The validity of the developed via NGD theory is verified with relevant numerical investigations. The illustration of via parameter identifications through the established GD formulations is discussed. Then, the calculated GD and transmission/reflection parameters showing the LP NGD function are in excellent agreement with simulation from a reference commercial tool. Furthermore, time domain simulation highlighting the time advance aspect was also confirmed with the via NGD structure.

In the future, the developed NGD via design can be potentially exploited for enhancing packaged PCBs, wireless RF and microwave communication system, and EMC design performances.

#### **REFERENCES**

- B. Bottom, "Assembly and packaging white paper on system level integration," ITRS, White Papers, 2009. [Online]. Available: http://www. itrs.net/papers.html

- [2] C.-K. Koh, J. Jain, and S. F. Cauley, "Synthesis of clock and power/ground networks," in *Electronic Design Automation*. Atlanta, GA, USA: Georgia Institute of Technology 2009, pp. 751–850, ch. 13.

- Institute of Technology, 2009, pp. 751–850, ch. 13.

[3] L.-R. Zheng and H. Tenhunen, "Wires as interconnects," in *Interconnect-Centric Design for Advanced SoC and NoC*. Dordrecht, The Netherlands: Springer, 2004, ch. 2.

- [4] M. E. Goldfarb and R. A. Pucel, "Modeling via hole grounds in microstrip," *IEEE Microw. Guided Wave Lett.*, vol. 1, no. 6, pp. 135–137, Jun 1991

- [5] T. Le Gouguec, N. Mahdi, S. Cadiou, C. Quendo, E. Schlaffer, W. Pessl, and A. Lefevre, "Modeling up to 45 GHz of coupling between microvias and PCB cavities considering several boundary conditions," *Int. J. Microw. Wireless Technol.*, vol. 8, no. 3, pp. 421–430, May 2016.

- [6] M. Mongiardo, F. Alessandri, and R. Sorrentino, "Full wave modeling of microstrip via holes," *Annales Des Télécommun.*, vol. 47, nos. 11–12, pp. 543–544, Nov. 1992.

- [7] R. Sorrentino, F. Alessandri, M. Mongiardo, G. Avitabile, and L. Roselli, "Full-wave modeling of via hole grounds in microstrip by threedimensional mode matching technique," *IEEE Trans. Microw. Theory Techn.*, vol. 40, no. 12, pp. 2228–2234, Jan. 1992.

- [8] S. Huang and L. Tsang, "Fast broadband modeling of traces connecting vias in printed circuit boards using broadband Green's function method," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 7, no. 8, pp. 1343–1355, Aug. 2017.

- [9] B. J. La Meres, "Characterization of a printed circuit board via," Dept. Elect. Comput. Eng., Univ. Colorado, Tech. Rep. EAS\_ECE\_2000\_09, 2000

- [10] D. Kwon, J. Kim, K. Kim, S. Choi, J. Lim, J.-H. Park, L. Choi, S. Hwang, and S. Lee, "Characterization and modeling of a new via structure in multilayered printed circuit boards," *IEEE Trans. Compon. Packag. Technol.*, vol. 26, no. 2, pp. 483–489, Jun. 2003.

- [11] H. Sun, Z.-J. Jin, M.-G. Kim, C.-S. Park, and T.-Y. Yun, "Equivalent-circuit modeling for multilayer capacitors based on coupled transmission-line theory," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 1, no. 5, pp. 731–741, May 2011.

- pp. 731–741, May 2011.

G. Hernández-Sosa, "Characterization and modeling of complex chipto-chip interconnection channels on printed circuit boards using high-frequency techniques," M. Sc. Thesis, Instituto Nacional de Astrofísica, Óptica y Electrónica and Intel-Syst. Res. Center Mexico, Mexico, Mexico, Aug. 2008.

- [13] K. Singh and K. Nagachenchaiah, "Simple modelling approach for viahole characterization on silicon substrate at Ka-band," *Microw. Rev.*, *Mikrotalasna Revija*, pp. 20–23, Sep. 2011.

- [14] A. Hardock, Y. H. Kwark, R. Rimolo-Donadio, H.-D. Bruns, and C. Schuster, "Using via stubs in periodic structures for microwave filter design," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 4, no. 7, pp. 1212–1221, Jul. 2014.

- [15] Â. H. Reja, A. A.-H. Khader, S. N. Ahmad, and A. A. M. A. Salih, "Dual-band band-pass filters based on metallic via holes," *Procedia Comput. Sci.*, vol. 58, pp. 748–754, 2015.

- [16] Y. Zhang, Y. Wang, J. Xu, C. Sui, B. Sen, S. Jin, and J. Fan, "Estimating the via-plane capacitance for differential vias with shared-antipad based on analytical equations," in *Proc. IEEE Int. Symp. Electromagn. Com*pat. Signal/Power Integrity (EMCSI), Washington, DC, USA, Aug. 2017, pp. 272–276.

- [17] J. Xu, Y. Wang, Y. Zhang, C. Sui, B. Sen, S. Jin, and J. Fan, "A survey on modeling strategies for high-speed differential via between two parallel plates," in *Proc. IEEE Int. Symp. Electromagn. Compat. Signal/Power Integrity (EMCSI)*, Washington, DC, USA, Aug. 2017, pp. 527–531.

- [18] S. Uemura, Y. Hiraoka, T. Kai, and S. Dosho, "Isolation techniques against substrate noise coupling utilizing through silicon via (TSV) process for RF/mixed-signal SoCs," *IEEE J. Solid-State Circuits*, vol. 47, no. 4, pp. 810–816. Apr. 2012.

- pp. 810–816, Apr. 2012.

[19] L. L. W. Leung and K. J. Chen, "Microwave characterization and modeling of high aspect ratio through-wafer interconnect vias in silicon substrates," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 8, pp. 2472–2480, Aug. 2005.

- [20] D. Jiang, W. Mu, S. Chen, Y. Fu, K. Jeppson, and J. Liu, "Vertically stacked carbon nanotube-based interconnects for through silicon via application," *IEEE Electron Device Lett.*, vol. 36, no. 5, pp. 499–501, May 2015.

- [21] G. Liu and J. Xu, "Compact transmission-type negative group delay circuit with low attenuation," *Electron. Lett.*, vol. 53, no. 7, pp. 476–478, Mar. 2017.

- [22] T. Shao, Z. Wang, S. Fang, H. Liu, and S. Fu, "A compact transmissionline self-matched negative group delay microwave circuit," *IEEE Access*, vol. 5, pp. 22836–22843, Oct. 2017.

- [23] L.-F. Qiu, L.-S. Wu, W.-Y. Yin, and J.-F. Mao, "Absorptive bandstop filter with prescribed negative group delay and bandwidth," *IEEE Microw. Wireless Compon. Lett.*, vol. 27, no. 7, pp. 639–641, Jul. 2017.

- [24] Z. Wang, Y. Cao, T. Shao, S. Fang, and Y. Liu, "A negative group delay microwave circuit based on signal interference techniques," *IEEE Microw. Wireless Compon. Lett.*, vol. 28, no. 4, pp. 290–292, Apr. 2018.

- [25] T. Shao, S. Fang, Z. Wang, and H. Liu, "A compact dual-band negative group delay microwave circuit," *Radioengineering*, vol. 27, no. 4, pp. 1070–1076, Dec. 2018.

- [26] B. Ravelo, N. Li, F. Wan, and J. Feng, "Design, modeling and synthesis of negative group delay IL-shape topology," *IEEE Access*, vol. 7, pp. 153900–153909, Dec. 2019.

- [27] W. Fayu, N. Li, B. Ravelo, N. M. Mourad, and W. Rahajandraibe, "NGD analysis of turtle-shape microstrip circuit," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, early access, Jan. 20, 2020, doi: 10.1109/TCSII.2020. 2967892.

- [28] F. Wan, T. Gu, B. Ravelo, and S. Lalléchère, "S-parameter model of IB-shape interconnect lines including crosstalk perturbation," *IEEE Trans. Electromagn. Compat.*, early access, Apr. 16, 2020, doi: 10.1109/TEMC. 2020.2982380

- [29] S. Chu and S. Wong, "Linear pulse propagation in an absorbing medium," Phys. Rev. Lett., vol. 48, no. 11, pp. 738–741, Mar. 1982.

- [30] B. Segard and B. Macke, "Observation of negative velocity pulse propagation," *Phys. Lett. A*, vol. 109, no. 5, pp. 213–216, May 1985.

[31] M. W. Mitchell and R. Y. Chiao, "Causality and negative group delays in

- [31] M. W. Mitchell and R. Y. Chiao, "Causality and negative group delays in a simple bandpass amplifier," *Amer. J. Phys.*, vol. 66, no. 1, pp. 14–19, Jan 1998

- [32] M. W. Mitchell and R. Y. Chiao, "Negative group delay and 'fronts' in a causal system: An experiment with very low frequency bandpass amplifiers," *Phys. Lett. A*, vol. 230, nos. 3–4, pp. 133–138, Jun. 1997.

- [33] T. Nakanishi, K. Sugiyama, and M. Kitano, "Demonstration of negative group delays in a simple electronic circuit," *Amer. J. Phys.*, vol. 70, no. 11, pp. 1117–1121, Nov. 2002.

- [34] M. Kitano, T. Nakanishi, and K. Sugiyama, "Negative group delay and superluminal propagation: An electronic circuit approach," *IEEE J. Sel. Topics Quantum Electron.*, vol. 9, no. 1, pp. 43–51, Jan. 2003.

- [35] S. K. Podilchak, B. M. Frank, A. P. Freundorfer, and Y. M. M. Antar, "High speed metamaterial-inspired negative group delay circuits in CMOS for delay equalization," in *Proc. 2nd Microsyst. Nanoelectron. Res. Conf.*, Ottawa, ON, Canada, Oct. 2009, pp. 9–12.

- [36] K.-P. Ahn, R. Ishikawa, and K. Honjo, "Group delay equalized UWB InGaP/GaAs HBT MMIC amplifier using negative group delay circuits," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 9, pp. 2139–2147, Sep. 2009.

- [37] B. Ravelo, S. Lalléchère, A. Thakur, A. Saini, and P. Thakur, "Theory and circuit modeling of baseband and modulated signal delay compensations with low- and band-pass NGD effects," *AEU-Int. J. Electron. Commun.*, vol. 70, no. 9, pp. 1122–1127, Sep. 2016.

[38] B. Ravelo, "Similitude between the NGD function and filter gain

- [38] B. Ravelo, "Similitude between the NGD function and filter gain behaviours," *Int. J. Circuit Theory Appl.*, vol. 42, no. 10, pp. 1016–1032, Oct. 2014.

- [39] B. Ravelo, "On low-pass, high-pass, bandpass, and stop-band NGD RF passive circuits," URSI Radio Sci. Bull., vol. 2017, no. 363, pp. 10–27, Dec. 2017.

- [40] M. Karlsson, "Probability density functions of the differential group delay in optical fiber communication systems," *J. Lightw. Technol.*, vol. 19, no. 3, pp. 324–331, Mar. 2001.

- [41] X. Lei, Y. Song, X. Yao, B. Dong, and M. Jin, "Effect of group delay on channel estimation performance in OFDM system," *Appl. Math. Inf. Sci.*, vol. 6, no. 3, pp. 1037–1045, 2012.

**BLAISE RAVELO** (Member, IEEE) is currently the University Full Professor with NUIST, Nanjing, China. His research interest includes multiphysics and electronics engineering. He is a pioneer of the negative group delay (NGD) concept about t < 0 signal travelling physical space. This extraordinary concept is potentially useful for anticipating and prediction all kind of information. He was the Research Director of ten Ph.D. students (seven defended), postdocs, research engineers,

and Master internships. With USA, Chinese, Indian, European, and African partners, he is actively involved and contributes on several international research projects (ANR, FUI, FP7, INTERREG, H2020, and Euripides<sup>2</sup>, Eurostars). He is a member of IET Electronics Letters editorial board as a circuit and system Subject Editor. He has been a member of the Scientific Technical Committee of Advanced Electromagnetic Symposium (AES), since 2013. His Google scholar H-index in 2020 is 21. He is a member of research groups: URSI, GDR Ondes, and Radio Society, and (co)authors of more than 270 scientific research papers in new technologies published in International conference and journals. He is a Lecturer on circuit and system theory; science, technology, engineering and mathematics (STEM); and applied physics. He regularly invited to review articles submitted for publication to international journals, such as the IEEE Transactions on MICROWAVE THEORY AND TECHNIQUES, the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS, the IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY, the IEEE Transactions on Industrial Electronics, IEEE Access, IET CDS, and IET MAP, and books (Wiley and Intech Science).

FAYU WAN (Member, IEEE) received the Ph.D. degree in electronic engineering from the University of Rouen, Rouen, France, in 2011. From 2011 to 2013, he was a Postdoctoral Fellow with the Electromagnetic Compatibility Laboratory, Missouri University of Science and Technology, Rolla. He is currently a Full Professor with the Nanjing University of Information Science and Technology, Nanjing, China. His current research interests include negative group delay cir-

cuits, electrostatic discharge, electromagnetic compatibility, and advanced RF measurement.

**SÉBASTIEN LALLÉCHÈRE** (Member, IEEE) was born in Nevers, France, in 1979. He received the M.Sc. degree in computational modeling from Polytech Clermont, in 2002, and the Ph.D. degree in electronics/electromagnetism from Universite Blaise Pascal, Clermont-Ferrand, France, in 2006.

He has served as a Research Engineer with LASMEA, Clermont-Ferrand, in 2007, focusing on intensive computational methods for electromagnetics. He is currently an Associate Professor

with the Institut Pascal and Universite Clermont Auvergne, Clermont-Ferrand. His research interests include electromagnetic compatibility, including antennas and propagation, complex and reverberating electromagnetic environments, electromagnetic coupling, computational electromagnetics, stochastic modeling, and sensitivity analysis in electrical engineering.

WENCESLAS RAHAJANDRAIBE (Member, IEEE) received the B.Sc. degree in electrical engineering from Nice Sophia-Antipolis University, France, in 1996, the M.Sc. degree (Hons.) in electrical engineering from the Science Department, University of Montpellier, France, in 1998, and the Ph.D. degree in microelectronics from the University of Montpellier. He is currently a Full Professor with the University of Aix-Marseille, France. In 1998, he joined the

Informatics, Robotics and Microelectronics Laboratory of Montpellier (LIRMM), Microelectronics Department. In 2003, he joined the Materials, Microelectronics and Nanoscience Laboratory of Provence (IM2NP), Microelectronic Department, Marseille, France, where he was an Associate Professor. Since 2014, he has been a Professor with Aix Marseille University,

**PREETI THAKUR** received the M.Phil. and Ph.D. degrees from HPU, Shimla.

She is currently working as a Professor and the Head of the Physics Department, Amity University Haryana. She has published more than 100 research articles in national and international journals. She has filed 14 patents till date. She has supervised 66 Master and four Ph.D. students. She is invited by the Royal Academy of Engineering, U.K., to attend Invited Professors meet at Birming-

ham. She has several national and international collaborations and projects. She is a Gold Medalist in electronics with Himachal Pradesh University, Shimla.

**ATUL THAKUR** received the M.Sc., M. Phil., and Ph.D. degrees from Himachal Pradesh University, Shimla. He is a Postdoctorate from the University of Brest, France, and another Postdoctorate from National Taiwan University, Taiwan. He is currently working as the Director of the Centre for Nanotechnology, Amity University Haryana. He has worked on various projects sponsored by DRDO, DAE, DST, and MNRE. He has published more than 100 international research articles and

filed 15 patents. Recently, he has been awarded the Newton Award from the Royal Academy of Engineering, U.K.

0 0 0