Received May 21, 2020, accepted May 29, 2020, date of publication June 2, 2020, date of current version June 15, 2020. *Digital Object Identifier 10.1109/ACCESS.2020.2999544*

# A Unified Model-Based Framework for the Simplified Execution of Static and Dynamic Assertion-Based Verification

## MUHAMMAD WASEEM ANWAR<sup>®1</sup>, MUHAMMAD RASHID<sup>®2</sup>, (Member, IEEE), FAROOQUE AZAM<sup>®1</sup>, AAMIR NAEEM<sup>®1</sup>, MUHAMMAD KASHIF<sup>®3</sup>, AND WASI HAIDER BUTT<sup>®1</sup>

<sup>1</sup>Department of Computer and Software Engineering, CEME, National University of Sciences and Technology (NUST), Islamabad 44000, Pakistan <sup>2</sup>Computer Engineering Department, Umm Al-Qura University, Makkah 21955, Saudi Arabia <sup>3</sup>College of Computer Science and Engineering, Hamad Bin Khalifa University, Doha, Qatar

Corresponding author: Muhammad Waseem Anwar (waseemanwar@ceme.nust.edu.pk)

**ABSTRACT** The improved productivity and reduced time-to-market are essential requirements for the development of modern embedded systems and, therefore, the comprehensive as well as timely design verification is critical. Assertion Based Verification (ABV) is a renowned paradigm to timely achieve an optimum test coverage, either through static or dynamic techniques. However, the major limitation with ABV is its inherited low-level implementation complexity. In order to simplify its execution, various Model Based System Engineering approaches provide a higher abstraction layer. Nevertheless, the complete verification requirements, targeting the static as well as dynamic ABV at the same time in a unified framework, are not being addressed. Furthermore, the dynamic verification support is provided through some traditional languages (like C, Verilog) where the advanced ABV features cannot be exploited. Consequently, this article introduces the MODEVES (MOdel-based DEsign Verification for Embedded Systems) framework to simultaneously support the static and dynamic ABV. Particularly, the UML (Unified Modeling Language) and SysML (Systems Modeling Language) diagrams are used to model the structural and behavioral requirements. Moreover, the NLCTL (Natural Language for Computation Tree Logic) is proposed to include the verification requirements for static ABV while the SVOCL (SystemVerilog in Object Constraint Language) is used to represent the dynamic verification constraints. An open source transformation engine is developed to automatically generate the SystemVerilog Register Transfer Level (RTL) code, Timed Automata model, SystemVerilog assertions and Computation Tree Logic (CTL) assertions with minimum transformation losses. The significance of the MODEVES framework is established through several case studies and the quantitative analysis shows an improvement of almost 100% in design productivity, as compared to the conventional low-level implementations.

**INDEX TERMS** Assertion based verification, computation tree logic, embedded systems, model based system engineering, systemverilog assertions, timed automata, unified modeling language (UML).

#### I. INTRODUCTION

The complexity and demand of embedded systems have increased exponentially. In order to manage the reduced time-to-market and improved productivity goals, the comprehensive design verification in an optimal time duration is critical [1]. The design verification of embedded systems

The associate editor coordinating the review of this manuscript and approving it for publication was Wen-Sheng Zhao<sup>(b)</sup>.

is generally classified into static and dynamic verification categories [2]. The static verification techniques deal with the mathematical models to verify the correctness of system design [3]. On the other hand, the dynamic verification techniques are based on the simulation of Register Transfer Level (RTL) code for system validation. Although, the static verification techniques provide some sophisticated features, the issues like state explosion problem [4] and the reliable tool support restrict their applicability on large and complex designs. Similarly, an exhaustive testing is required for the dynamic verification process to achieve the maximum test coverage [5].

In order to address the limitations of conventional static and dynamic verification techniques, Assertion Based Verification (ABV) is employed which deals with the functional properties (assertions) of the system in a reduced simulation time [6], [7]. The two major types of ABV are static and dynamic [8]. In static ABV, the desired assertions are verified through formal methods. In this regard, Timed Automata [9] is a renowned formalism, particularly designed to validate the correctness of critical temporal aspects. On the other hand, the code of hardware design languages at RTL is simulated to perform dynamic ABV. However, in traditional hardware languages (Verilog, VHDL), ABV is not inherently supported [10], [11] as such languages mainly deal with the system design only. In this context, SystemVerilog [12] is an increasingly popular language that operates at RTL and provides dynamic ABV support through SystemVerilog Assertions (SVAs).

Despite the effectiveness of ABV in improving the design verification process, its low-level implementation complexities result in several verification delays [30]. In this regard, Model Based System Engineering (MBSE) plays an important role by providing a higher abstraction layer [2]. It first deals with the modeling phase to capture the design requirements and constraints at higher abstraction level (source models). Subsequently, a transformation phase is employed to automatically transform the source models into the target models at lower level of abstraction. Finally, the design verification (formal and/or dynamic) can be instantly performed through the automatically generated code. The Object Management Group (OMG) has introduced a standard Unified Modeling Language (UML) profile and its extensions like Systems Modeling Language (SysML) [20] to simplify the modeling phase.

#### A. LIMITATIONS OF EXISTING MBSE FRAMEWORKS

Several MBSE frameworks have already been proposed to overcome the low-level complexities of ABV (e.g. [8], [14], [30] etc.). However, the existing frameworks either deal with the static or dynamic verification at a time. On the other hand, the complexity of modern embedded systems is significantly increased due to a higher degree of heterogeneity in terms of both software and hardware components [39]. As a result, the complex designs usually require the application of both (static as well as dynamic) types collectively in a unified design environment, to achieve the maximum verification coverage in an optimum time [7].

In addition to the lack of a unified design environment, the existing frameworks do not usually include the verification properties in the actual design models which creates a gap between design and its verification. Consequently, there is a need for a unified model based framework, where the verification properties can be directly included in the design models, to simultaneously support the static and dynamic ABV. To the best of our knowledge (Section V), an MBSE framework to support both static and dynamic ABV, by means of a well-known Timed Automata formalism and SystemVerilog language respectively, is hard to find in the literature and industrial projects.

## **B. THE PROPOSED FRAMEWORK**

In order to address the limitations of existing frameworks, this article has proposed the *MODEVES* (*MOdel-based DEsign Verification for Embedded Systems*) framework. The objective is to improve the design productivity (Section IV-D) by providing a higher abstraction layer for both static and dynamic ABV, where the design as well as verification aspects are modeled collectively. Particularly, the idea is to enable the accurate transformation of a single/unified design model into SystemVerilog and Timed Automata simultaneously. Furthermore, the verification properties included in the high-level models are also transformed into SVAs and CTL assertions.

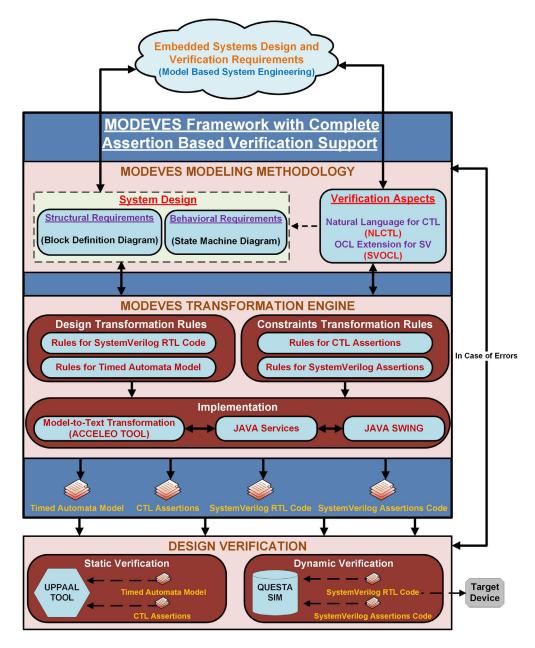

The overview of MODEVES framework is shown in **Figure 1**. A complete end-to-end MODEVES Modeling Methodology (MMM) is introduced in Section **II** to model the structural, behavioral and verification (static as well as dynamic) requirements collectively. Particularly, a UML and SysML based approach is introduced to model the system design (Section **II-A**) i.e. Block Definition Diagram (BDD) concepts are used to represent the system structure and State Machine Diagram (SMD) concepts are employed to represent the system behavior. Moreover, the NLCTL (Natural Language for Computation Tree Logic) is proposed (Section **II-B**) to include the verification properties for static verification. Furthermore, the SVOCL [15] is integrated in the framework for dynamic verification constraints.

Once the modeling of design and verification aspects is performed, an open source MODEVES Transformation Engine (MTE) [19] is developed (Section **III**) to automatically generate the target low level codes. It includes the SystemVerilog RTL code, SVAs, Timed Automata model and CTL (Computational Tree Logic) assertions. Particularly, certain transformation rules are developed to perform a conceptual mapping between BDD/SMD constructs and SystemVerilog RTL/Timed Automata constructs in Section **III-B** and Section **III-C** respectively. Similarly, multiple rules are also developed to convert the NLCTL verification properties into CTL assertions while the transformation of SVOCL is integrated to generate SVAs (Section **III-D**). Subsequently, the implementation of transformation rules is performed in JAVA and Acceleo [16].

While the MODEVES framework proposes a unified design model for the automatic generation of SystemVerilog and Timed Automata, it advocates the use of two different formalism for the representation of static and dynamic properties. The reason is that a unified approach is only beneficial where a single requirement can be simultaneously and correctly transformed into the respective SVA and CTL properties. Therefore, the unified representation for

FIGURE 1. Overview of the MODEVES framework.

verification constraints is not feasible without compromising the critical transformation losses due to the significant syntax and semantic differences between CTL and SVAs.

#### C. VALIDATION AND QUANTITATIVE ANALYSIS

The validation of MODEVES framework is performed (Section IV) through eight case studies i.e. Traffic Lights Controller, Car Collison Avoidance System, Arbiter, Elevator, Unmanned Aerial Vehicle, Automated Teller Machine, Train Gate and Bridge Crossing system. The system design and verification aspects are modeled through the proposed modeling methodology and the required target codes are automatically generated through the developed transformation engine. Finally, the QuestaSIM simulator [17] and UPPAAL tool [18] are used to perform dynamic and static ABV respectively. After the successful design verification, the SystemVerilog RTL code can be deployed to the target device as shown in **Figure 1**. The quantitative analysis of MODEVES framework with respect to the native SystemVerilog and Timed Automata technologies shows 100% productivity gain (Section **IV-D**). It is important to note that this article only includes the details of three case studies due to space limitations while the models of all the eight case studies, along with the source code of transformation engine, are available at [19] for further evaluation.

TABLE 1. Notations for the modeling of system structure.

| Sr. # | Name         | Graphical Representation                                                                                                                                                 | Description                                                                                                                                                                                                                                                  |

|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Flow Ports   | •block>     •     •     •     •     •     •     •     flow ports     •     •     inout flowport1: Boolean     ⊡    in flowport3: Boolean     ⊡    out flowport3: Boolean | The concept of flow ports is provided with three possible directions i.e. <i>in</i> , <i>out</i> and <i>inout</i> . The application of flow ports is proposed for the modeling of structure and linkage between various registers of the system.             |

| 2     | Data Types   | «datatype»<br>DataType1<br>properties<br>Attribute1: Bolean<br>Attribute2: Integer                                                                                       | The primitive data types (Integer Boolean, Real etc.) are used to represent different variables of the system structure.                                                                                                                                     |

| 3     | Enumeration  | enumeration»                                                                                                                                                             | The enumerations achieve a particular modeling requirement. A typical example is to represent all the states in a system.                                                                                                                                    |

| 4     | Signal Event | «signal»<br>ক্রে Signal1                                                                                                                                                 | The clock and timer are managed through an activity diagram, provided as a built-in function of the framework [21]. The clock and timer are declared in a block with associated properties, and for their desired execution, the signal event is introduced. |

#### D. SUMMARY OF NOVEL CONTRIBUTIONS

To summarize, the novel contributions of the proposed framework are as follows:

- 1) A unified model-based design approach, by utilizing the standard UML/SysML notations, is proposed. The high-level models contain the necessary information, required to concurrently transform them with minimum transformation losses.

- A formalism (NLCTL) is proposed to include the properties in design models with simplicity for static ABV. On the other hand, the SVOCL [15] is used to include the verification properties for dynamic ABV.

- The design and implementation of transformation rules to automatically generate the SystemVerilog RTL code, Timed Automata model, CTL properties and SVAs are proposed.

## **II. MODEVES MODELING METHODOLOGY**

The modeling phase provides a higher abstraction layer for some particular low-level technologies [2]. Subsequently, the transformation is performed to automatically generate the target low-level codes. Therefore, it is essential to systematically include the necessary information of the target technologies in the modeling phase to perform accurate transformations. In the MODEVES framework, we are dealing with SystemVerilog, Timed Automata, SVAs and CTL technologies. Consequently, the objective of MODEVES Modeling Methodology (MMM) is to enable the modeling of general design and verification concepts at higher level while logically preserving the semantics of target technologies. This section briefly describes the details of MMM regarding design (Section II-A) and verification (Section II-B) requirements.

### A. MODELING OF SYSTEM DESIGN

In MMM, we select the standard UML/SysML notations for the modeling of system design (structure and behavior). The structure of a system includes different variables and hardware elements like registers, ports etc. The BDD diagram in SysML, which has been extended from the UML class diagram, provides several modeling concepts like blocks, flow ports etc. for a realistic representation of the system structure. Therefore, the proposed MMM advocates the use of particular BDD concepts for the modeling of structural requirements, as given in **Table 1**. The first column "Sr. #" represents the *serial number* of a given modeling notation. The *names* and *graphical representations* are given in the second and third columns. Finally, the *description* is provided in the last column.

While it is relatively simple to model the structural elements of a system design process, the correct and meaningful modeling of the system behavior is relatively complex. Particularly, the behavior of embedded systems involves complex temporal aspects with several constraints while achieving the correct sequence of an execution flow. In this context, the SMD in SysML/UML provides several notations which are based on the principal of finite-state-transitions. Therefore, the SMD notations allows a systematic modeling of both simple as well as complex behavioral requirements, as given in **Table 2**.

For a better understating of MMM, consider a guiding example of Traffic Lights Controller (TLC). The functionality of TLC is to manage the road traffic at North-South (NS) and East-West (EW) roads intersection. There is a sensor attached at the EW road to detect the presence of a vehicle. The EW light should only be turned green to pass the traffic on the EW road if the EW sensor is activated. An emergency sensor is also deployed at the NS/EW intersection to manage the passage of emergency vehicles. To demonstrate

#### TABLE 2. Notations for the modeling of system behavior.

| Sr.#       | Name                  | Graphical Representation | Description                                                                                                                                                                                                                                                                               |  |

|------------|-----------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|            |                       | State1                   | The SMD <i>state</i> node represents different system states. It specifies a particular action / condition, while entering or leaving the states, and is accomplished through <i>entry point</i> and <i>exit point</i> pseudostates. For complex requirements, the proposed MMM allows to |  |

| 1          | State                 | InitialState             | call other behaviors, modeled in the SysML Activity Diagrams, inside a particular state. The clock and timer behaviors are the typical examples. The start and end points                                                                                                                 |  |

|            |                       | FinalState               | for a particular behavior are represented through SMD <i>initial</i> and <i>final</i> state nodes.                                                                                                                                                                                        |  |

| Transition |                       |                          | The SMD transition notation dispatches some particular events through the <i>trigger</i> notation. Moreover, the <i>constraints</i> can be associated with transitions through the <i>guard</i>                                                                                           |  |

| 2          | Transition            | 🚵 <trigger></trigger>    | notation. To summarize, the transition is activated on a particular event and success executed on the fulfilment of given constraints.                                                                                                                                                    |  |

|            |                       | Guard {?} Constraint1    | executed on the furthing of given constitutions.                                                                                                                                                                                                                                          |  |

| 3          | Fork<br>pseudostate   | $\rightarrow$            | The <i>fork</i> pseudostate is used to split a single input transition into two or more output ransitions for concurrent execution.                                                                                                                                                       |  |

| 4          | Join<br>pseudostate   |                          | The <i>join</i> pseudostate combines two or more input transitions into a single output transition. Logically, it checks the combination of several input conditions (transition to produce a single output transition when all the input conditions become true.                         |  |

| 5          | Choice<br>pseudostate | <-↓>                     | The use of <i>choice</i> pseudostate is suggested in order to achieve a conditional branching for particular modeling purposes.                                                                                                                                                           |  |

(b) System Behavior

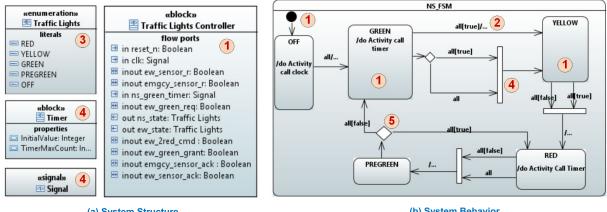

FIGURE 2. Modeling the (a) Structure and (b) Behavior of Traffic Light Controller.

the effectiveness of MMM, the structure and behavior of TCL is modeled in Figure 2 (a) and Figure 2 (b) respectively where the circled numbers demonstrate the usage of respective UML/SysML notation in Table 1 and Table 2 respectively. For simplicity, we only consider the modeling of NS behavioral requirements rather than complete TLC system.

Figure 2 (a) shows that the registers, sensors and other elements are modeled through flow ports (Sr. 1 in Table 1), while different states are represented through enumeration (Sr. 3 in Table 1). Furthermore, the built-in clock and timer are declared with associated variables through block and signal events (Sr. 4 in Table 1). The modeling of TLC behavior (only NS) is shown in Figure 2 (b). The different states like initial state, green, yellow etc. are modeled through state node (Sr. 1 in Table 2). Furthermore, several transitions (Sr. 2 in Table 2) are utilized to model the desired flow between different states by applying the associated trigger and guard conditions. However, the complete trigger and guard conditions of transitions cannot be represented graphically due to space limitations and only true/ false is displayed on each transition as shown in Figure 2 (b).

In order to achieve certain behavioral requirements between the execution flows of different states, the pseudostate like join (Sr. 4 in Table 2) and choice (Sr. 5 in Table 2) are used. For example, assume there is a behavioral requirement that the TLC should only move from yellow to red state if NS timer for green state is equal to 3 and reset is

false. The both conditions (i.e. ns-timer = 3 and reset = false) are managed separately through two different transitions from the yellow state. Subsequently, if both conditions become true simultaneously, the join pseudostate combines these two transitions from the yellow state into a single one and take the system in the red state as shown in **Figure 2** (b). Similarly, other pseudostates like fork, choice are used as per given behavioral requirements.

To summarize, the MMM is capable of modeling both simple as well as complex system designs. It is important to note that we have only explained some of the modeling concepts here, through the TLC guiding example. However, the modeling and transformation capabilities of the MODEVES framework are comprehensively explained in Section **IV** through some complete case studies.Furthermore, the interested readers can find the detailed modeling guidelines with examples at [21].

## **B. MODELING OF VERIFICATION REQUIREMENTS**

While the system design is based on a unified model (as shown in Section **II-A**), the system verification in the proposed framework requires two different formalisms: (1) the NLCTL is proposed to represent CTL properties in design models for static ABV, (2) the SVOCL is used to include SVAs for dynamic ABV. It is important to note that the SVOCL is already proposed in [15] and only its overview is provided here for the completeness of the framework.

## 1) NATURAL LANGUAGE FOR COMPUTATION TREE LOGIC (NLCTL)

The motivation behind the NLCTL is to provide a simple and logical modeling approach to include the CTL properties directly in the design models through a natural language alike syntax. The CTL [26] is a well-known temporal logic to specify the branching time constraints and deals with two temporal operators for paths quantifiers i.e. All and Exist. Furthermore, it also provides some temporal operators for the path specific quantifiers i.e. Next, Globally, Finally, Until and Weak Until.

The proposed framework directly loads the Timed Automata model and the CTL properties in UPPAAL tool to perform static ABV instantly [18]. In this context, a subset of standard CTL is utilized in UPPAAL to express the properties for the verification of Timed Automata model. Particularly, five temporal operators, based on the standard CTL concepts, are used. The Possibly operator deals with the reachability properties while the Invariantly and Potentially Always operators deal with the safety properties. Finally, the Eventually and Leads to operators deal with the liveness properties. In NLCTL, we consider all the aforementioned five operators for the modeling and transformation of both simple as well as complex CTL properties.

*Proposed Formalism:* We systematically develop NLCTL by utilizing the concepts of Extended Backus–Naur Form (EBNF) [27], which is a standard approach for the development of new languages e.g. Accellera Portable Test and

Stimulus Standard (PSS) [28] etc. The grammar of NLCTL is defined using EBNF concepts through the following fourteen rules:

1. < Requirement>:: =< Property> < Type>

The first rule states that the verification requirement/CTL assertion, represented as a <Requirement>, can be defined through "Property" and "Type" non-terminal symbols. The definition of Property and Type is given in Rule 2 and 14 respectively.

| 2. <property></property> | ::= | <exp></exp>                     |

|--------------------------|-----|---------------------------------|

|                          |     | if <exp> then <exp></exp></exp> |

|                          |     | <deadlock_exp></deadlock_exp>   |

|                          |     | <exp> and <exp></exp></exp>     |

|                          | Ι   | <exp> or <exp></exp></exp>      |

The second rule defines that the property can be stated through expression  $\langle Exp \rangle$  or "if then expression" or "deadlock expression"  $\langle Deadlock\_Exp \rangle$ . Furthermore, the property can be defined through and/or expressions  $\langle Exp \rangle$ . The definitions of expression  $\langle Exp \rangle$  and deadlock expression  $\langle Deadlock\_Exp \rangle$  are given in Rule 4 & 3 respectively.

| 3. <deadlock_exp></deadlock_exp> | ::= | never deadlock          |

|----------------------------------|-----|-------------------------|

|                                  |     | system is deadlock free |

|                                  |     | deadlock                |

|                                  |     | system has deadlock     |

|                                  |     |                         |

The third rule defines the syntax of a deadlock expression with four terminal symbols i.e. never deadlock, system is deadlock free, deadlock and system has deadlock.

| :: = | = ( <property>)</property>    |

|------|-------------------------------|

|      | never <exp></exp>             |

|      | <state_exp></state_exp>       |

|      | <time_exp></time_exp>         |

|      | <logical_exp></logical_exp>   |

|      | <deadlock_exp></deadlock_exp> |

|      | .1                            |

The fourth rule implies that it is possible to use the property non terminal symbol (Rule 2) in the expression repeatedly i.e. zero to n times. Furthermore, the expression can be defined along with "never" terminal symbol. In addition, the expression can be defined through <State\_Exp>, <Time\_Exp>, <Logical\_Exp> and <Deadlock\_Exp >, as given in the Rule 5, 6, 8 & 3 respectively.

| 5. <state_exp>:: =</state_exp> |  | <process_name> state</process_name> | e is  |    |

|--------------------------------|--|-------------------------------------|-------|----|

|                                |  | <state_name></state_name>           |       |    |

|                                |  | <process_name></process_name>       | state | is |

equal to <State\_Name>

4.  $\langle Exp \rangle$

It defines the syntax of state expression <State\_Exp>. The terminal symbol "state is" should be used between the process name and the state name. Similarly, the terminal symbol "state is equal to" can also be used between the process name and the state name non terminal symbols. The definitions of <Process\_Name> and <State\_Name> are given in Rule 13 & 12 respectively.

It defines the syntax of time expression <Time\_Exp>. The time expression can be specified by using variable name <Variable\_Name>, operator <OPT> and value <Value> non terminal symbols where the operator non terminal symbol should be used between the variable name and the value non terminal symbols. Similarly, time expression can also be defined by using the operator non terminal symbol between the two variable name non terminal symbols. The definitions of <Variable\_Name>, <OPT> and <Value> non terminal symbols are given in Rule 11, 7 and 10 respectively.

7.  $\langle OPT \rangle$  :: = less than | greater than equal to

The syntax of operator <OPT> can be defined either through "less than" or "greater than equal to" terminal symbols.

The logical expression <Logical\_Exp> can be specified by using the variable name <Variable\_Name>, logical operator <Logical\_OPT > and value <Value> non terminal symbols where logical operator non terminal symbol should be used between the variable name and the value non terminal symbols. The definitions of <Variable\_Name>, <Logical\_OPT>, <Value> non terminal symbols are given in Rule 11, 9 and 10 respectively.

| 9. <logical_opt></logical_opt> | :: =    | equal to         |

|--------------------------------|---------|------------------|

|                                | less th | nan              |

|                                | greate  | er than equal to |

|                                | less th | nan equal to     |

The logical operator <Logical\_OPT> can be defined in four different ways, as shown above.

| 10. <value></value>                 | ::=  | ([a-z][A-Z][0-9])* |

|-------------------------------------|------|--------------------|

| 11. <variable_name></variable_name> | :: = | ([a-z][A-Z][0-9])* |

| 12. <state_name></state_name>       | ::=  | ([a-z][A-Z][0-9])* |

| 13. <process_name></process_name>   | ::=  | ([a-z][A-Z][0-9])* |

|                                     |      |                    |

The rules 10, 11, 12 and 13 provide the definitions for declaring a value, variable name, state name and the process name non terminal symbols respectively. The value can be defined through the combination of 0-9 integers e.g. 12, 987 etc. Moreover, both small as well as capital alphabetical letters (i.e. a to z or A to Z) can be used in different combinations to define a particular value. Furthermore, an alpha numeric combination can also be used to define a value. Similarly, the variable, state and process names can be defined as per given aforementioned value rules.

| 14. <type></type> | ::= | Possibly           |

|-------------------|-----|--------------------|

|                   |     | Invariantly        |

|                   |     | Potentially always |

|                   | 1   | Eventually         |

|                   |     | Leads to           |

There are three major types of CTL queries (i.e. Reachability, Safety, Liveness) for the verification of Timed Automata model in UPPAAL tool. To include all the four types of verification queries in NLCTL, type <Type> non terminal symbol is introduced. The type can be defined through

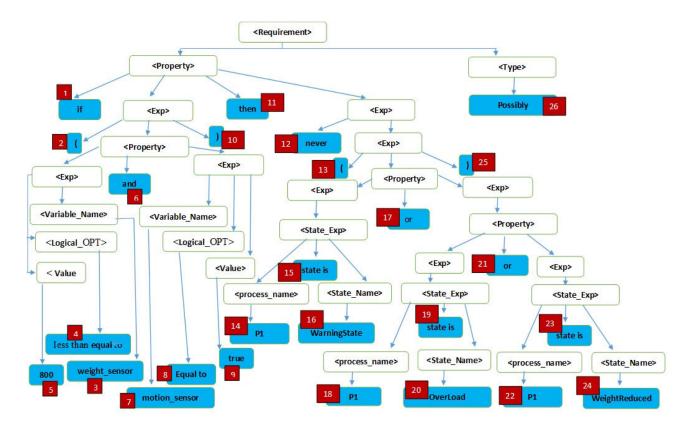

FIGURE 3. NLCTL Syntax Tree for Example 1.

five terminal symbols (Possibly, Invariantly, Potentially always, Eventually and Leads to).

Application of NLCTL: This section demonstrates the application of NLCTL, based on the proposed EBNF grammar, with examples. Particularly, the objective is to demonstrate the systematic working of NLCTL grammar through syntax tree.

*Example 1*: This example is taken from the TLC system where the requirement is to check a deadlock in the system. This property can be represented in NLCTL as:

#### *Property* = *System is deadlock free*, *Type* = *Invariantly*

The syntax tree of NLCTL grammar for a given property is shown in **Figure 3**. Please note that the terminal symbols are highlighted in blue color and the sequence of terminal symbols during parsing is shown in red color with a respective number.

**Figure 3** shows that the given verification requirement is expressed through *Property* and *Type* non terminal symbols (rule 1 of the NLCTL grammar). The *Property* non terminal symbol can be directly represented through *deadlock expression* (rule 2). Finally, the deadlock expression can be represented through "system is deadlock free" terminal symbol (rule 3). On the other hand, *Type* non terminal symbol can be represented through "invariantly" symbol (rule 14). Consequently, the given requirement is correctly expressed through NLCTL grammar rules.

*Example 2*: This example is taken from an elevator system. Particularly, the requirement is to check the reachability of warning, overload and weight reduced states while the weight\_sensor is under the allowed limit (i.e. 800 KG) and motion\_sensor is activated. It can be expressed as:

Property = If (weight\_sensor less than equal to 800 and motion\_sensor equal to true) then never (P1 state is WarningState or P1 state is OverLoad or P1 state is WeightReduced), Type = Possibly

The syntax tree for Example 2, as shown in **Figure 4**, utilizes most of the NLCTL grammar rules. The given example is started through rule 1 by utilizing the property and type non terminal symbols. Subsequently, the property can be defined through "if <exp> then <exp>" as per rule 2 of the NLCTL grammar. Therefore, the rule 2 is applied to achieve the desired representation, as shown in **Figure 4**. According to rule 4, expression <exp> can be defined as a property recursively. Similarly, various NLCTL rules are utilized to correctly express the given requirements.

FIGURE 4. NLCTL Syntax Tree for Example 2.

To summarize, the NLCTL is a significant step to express the verification properties at a higher abstraction level. To complete the MBSE flow, its grammar is implemented in the transformation engine, so that, the high-level NLCTL constraints can be automatically transformed to the corresponding CTL assertions (See Section **III-D** for the details of transformation process). The user manual and further details of NLCTL can be found at [31].

#### 2) SVOCL FOR SystemVerilog ASSERTIONS

We have already developed an OCL extension, named as SVOCL [15], to include the dynamic verification requirements in high-level models. In this regard, seven functions are included in SVOCL, as shown in **Table 3** (sr. # 1 to sr. # 7). Furthermore, Disif expression (sr. # 8 of **Table 3**) is incorporated for conditional statements. In the proposed framework, we have integrated the SVOCL for dynamic ABV. In this regard, the practical usage of SVOCL functions (**Table 3**), along with the complete technical details, can be found at [15].

## **III. MODEVES TRANSFORMATION ENGINE (MTE)**

This section describes the MODEVES Transformation Engine (MTE). Firstly, the general architecture is described in Section III-A. In order to develop some appropriate transformation rules for system structure, the conceptual mapping between SysML BDD notations and SystemVerilog constructs is defined in Section III-B. For system behavior, the conceptual mapping of SystemVerilog and Timed Automata constructs with respect to SMD notations is described (Section III-C). Finally, the transformation rules to generate CTL assertions from NLCTL constraints are provided in Section III-D.

#### A. GENERAL ARCHITECTURE

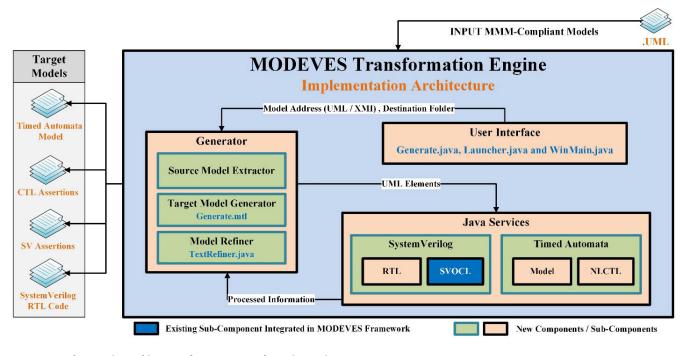

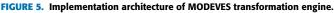

We practice a Model-to-Text (M2T) transformation approach, using the open source Acceleo tool [16], for the implementation of MODEVES Transformation Engine (MTE). Acceleo is a well-known tool for a seamless execution of transformations in MBSE [29]. **Figure 5** shows that the implementation of MTE is accomplished through three main modules: (1) *User Interface*, (2) *Generator* and (3) *Java Services*. In the following, the brief description of each module and respective sub-modules is presented.

*User Interface:* It launches the application and displays the user interface of MTE on the screen. It takes the MMM compliant models in .UML extension and sends their address to *Generator* module for further processing (e.g. extraction of model elements etc.). Furthermore, it also sends the destination folder address (where the target models are required to be generated) to the *Generator* module.

*Generator:* It receives the input UML models and generates the target SystemVerilog RTL, Timed Automata model,

#### TABLE 3. Fundamental constructs of SVOCL.

| Sr. # | Required Functionality for Timing Constraints at Higher<br>Abstraction Level | Representation of Constraints with SVOCL                           |  |

|-------|------------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| 1.    | Sequential delay between two expressions                                     | SVSeq (sequential expr, sequential delay, preceding expr)          |  |

| 2.    | Consecutive repetitions of an expression                                     | SVRep (expr, numeric value of repetitions)                         |  |

| 3.    | Implications of behaviors/sequences/expressions                              | SVImplication (antecedent expr, consequent expr, implication type) |  |

| 4.    | Whether the value of an expression is stable                                 | SVStable (expr)                                                    |  |

| 5.    | Whether the value of an expression has changed                               | SVChanged (expr)                                                   |  |

| 6.    | Whether the value of an expression is changed from False to True             | SVRose (expr)                                                      |  |

| 7.    | Whether the value of an expression is changed from True to False             | SVFell (expr)                                                      |  |

| 8.    | Customized conditional statements                                            | Disif expression                                                   |  |

SVAs and CTL assertions. Particularly, the *source model extractor* extract the required UML elements (e.g. BDD attributes, state and transition elements etc.) from the input models which are then passed to *Java Services* module for further processing. Finally, the *target model generator* generates the target models after receiving the processed information from the *Java Services*. Lastly, the *model refiner* is responsible to manage the formatting issues in the generated target models.

Java Services: It implements the logic of transformation rules (Section III-B, Section III-C and Section III-D). Particularly, the SystemVerilog sub-module contains the corresponding transformation rules for the RTL code and SVOCL. It is important to note that the SVOCL sub-module is already implemented [15] and only the integration is performed here. On the other hand, the *Timed Automata* sub-module implements the transformation rules for the Timed Automata model and NLCTL assertions. The processed transformation rules from *Java services* component are sent back to the *Generator* module to ultimately generate the target codes, as shown in **Figure 5**.

It can be seen from **Figure 5** that the architecture of MTE is based on a modular approach as the coupling between different modules is as minimum as possible. Consequently, the MTE is highly supportive in terms of scalability and usability. For example, some additional CTL constructs can be added in the current version by only updating the NLCTL sub-component. Similarly, the other components can also be upgraded with simplicity according to some particular requirements.

In addition to the scalability, the architecture of MTE also provides the usability features as different components can be used in other implementations with slight modifications. For example, it is fairly possible to include the

| Sr. # | SMD Notations | Corresponding SystemVerilog Concepts                              | Corresponding Timed Automata<br>Concepts |

|-------|---------------|-------------------------------------------------------------------|------------------------------------------|

| 1     | Name          | Module Name                                                       | File Name                                |

| 2     | Region        | Sub-section of code for a particular FSM                          | Timed Automata                           |

| 3     | Initial Node  | Starting point for particular code                                | Initial Location                         |

| 4     | State         | State in the context of code                                      | Location                                 |

|       | Name          | Name in code                                                      | Name                                     |

|       | Entry         | Code specification when the system enters in a particular state   | Invariant                                |

|       | Exit          | Code specification when the system exits from a particular state  | Invariant                                |

|       | Do Activity   | Code logic for the activity which is called in a particular state | Time concepts                            |

| 5     | Transition    | Code specification between different states                       | Edge                                     |

|       | Guard         | Conditional code to move from one state to another state          | Guard attribute of Edge                  |

|       | Trigger       | Code for ports that trigger in a particular transition            | Sync attribute of Edge                   |

|       | Effect        | Code specification after the successful execution of transition   | Update attribute of Edge                 |

| 6     | Fork          | Concurrent execution for blocks of code                           | Location                                 |

| 7     | Join          | Conditional Statement by combining different expressions          | Location                                 |

| 8     | Choice        | Conditional branching e.g. If / else, Case                        | Location                                 |

functionality of NLCTL in other frameworks with simplicity. The only requirement is to use the "GenerateCTL.java" file of NLCTL sub-component and a small portion of existing code is required from the Generator and Java Services components. To conclude, the further addition of functions in MTE is easy to implement and the integration of a particular MTE function in other frameworks is quite simple.

We do not include the complete MTE details here due to space limitations and further details like user/installation manual, the low-level architecture containing implementation details, the download link (source code) and the sample case studies can be found at [19]. However, the summary of MTE transformation rules is provided in subsequent sections.

#### **B. TRANSFORMATION FOR SYSTEM STRUCTURE**

The SysML BDD notations are proposed in Section II (Table 1) for the modeling of system structure. Here, the generic transformation rules are defined to generate SystemVerilog structural code from the BDD notations as follows:

1) Flow ports are transformed to SystemVerilog registers where *in* and *out* flow port types are mapped to SystemVerilog *input* and *output* registers/logic respectively. Furthermore, the flow port with *inout* direction type is mapped to SysemVerilog *wire*.

2) The UML/SysML primitive data types are transformed to equivalent SystemVerilog variable types like integer.

3) The UML/SysML enumeration type is transformed to equivalent SystemVerilog enumeration (*typedef enum*).

4) Although the activity diagram is used to implement the clock and timer, the signal type is actually used to represent it in the model. On the other hand, the SystemVerilog has inherited process for clocking. Therefore, only the definition

of clock, on the basis of signal type and associated properties, is generated in the target structural code.

It is important to note that although we consider major SystemVerilog data types in the transformation process in order to define the structural aspects of system in RTL code, SystemVerilog supports different variations in standard datatypes e.g. integer datatype can be *signed* or *unsigned* etc. In transformation, we do not consider such variations in standard SystemVerilog datatypes and one can manually include such information in generated RTL code after transformation. Similarly, SystemVerilog also supports advanced datatypes like *chandle* to store pointers during Direct Programming Interface (DPI) [6]. We also do not consider such advanced datatypes in transformation.

#### C. TRANSFORMATION FOR SYSTEM BEHAVIOR

The behavioral models are simultaneously transformed into SystemVerilog RTL and Timed Automata model to perform both dynamic as well as static ABV. In this regard, it is essential to develop various rules to transform SMD notations into the corresponding SystemVerilog and Timed Automata concepts, as given in **Table 4**.

**Table 4** shows that the mappings between SMD notations and Timed Automata are straightforward, as both are based on the principal of finite-state-transition. For example, the SMD transition is logically equivalent to Timed Automata edge. Therefore, the attributes of a transition like guard, trigger and effect can be directly mapped to the edge attributes like gurad, Sync and update respectively. Similarly, the SMD state is logically equivalent to Timed Automata location. Therefore, the state attributes like entry can be directly mapped to the location invariant. Moreover, the SMD Pseudostates like fork, join and choice are logically equivalent to location in Timed Automata.

It is important to note that we target all the major elements of Timed Automata (i.e. initial location, location, committed location, edge with guard, update and sync attributes and invariant), which are defined in UPPAAL tool. However, few customized features of UPPAAL tool like urgent channel/location are not considered in the proposed transformation. Similarly, few variables are needed to be declared in UPPAAL tool in order to perform simulation. However, the information of global declaration variables cannot be incorporated systematically without compromising the simplicity and generic applicability of the framework. One possibility is to include the information of global declaration variables through UML comments; however, this is a non-standard way and of least use for researchers and practitioners. Therefore, we do not provide the modeling and transformation provision for global declaration variables as this information can easily be included in the automatically generated Timed Automata model manually.

On the other hand, it can be seen from Table 4 that the mappings between SMD notations and SystemVerilog are indirect as the former is based on finite-state-transition concepts while the latter is a low-level hardware language. For example, the entry attribute of a state refers to the specific condition while the system is entering into a particular state. In SystemVerilog, this refers to a low-level code for a specific condition in the context of a particular state. Therefore, the flow of states and the transitions along with the respective attributes in the model is considered for the transformation of respective SystemVerilog RTL code. For example, the sequence of states belongs to the major (outer) structure of SystemVerilog RTL code while the sequence of transitions belongs to the inner code within the main structure. In this regard, the SMD region attribute is used to provide further division in the main structure i.e. a separate code block in RTL code for each region.

Similarly, the initial node provides a starting point for a particular block of code. Consequently, in order to generate the RTL code for the main structure (based on states) and the inner logic (based on transitions), we consider certain low-level SystemVerilog constructs in the transformation process.

For example, we consider certain procedural statements (i.e. *initial, final, always and function*) during the transformation process to generate the main structure of behavioral code. Moreover, the conditional branching (based on SMD Choice Pseudostate) is achieved in transformation process through SystemVerilog *if / else* and *case* statements. Similarly, we consider SystemVerilog *for* and *foreach* loops in the transformation process. To summarize, all the significant SystemVerilog constructs have been considered in the transformation process which are essential to specify both simple as well as complex design and verification requirements in RTL code and SVAs respectively. Furthermore, in case of any particular requirement, the generated RTL

and assertions code can be optimized manually. In addition, it is also important to note that SystemVerilog is a complete design and verification language with several advanced features [33]. Therefore, it is not possible to consider all the aspects of SystemVerilog in the proposed framework. For example, SystemVerilog fully supports the object oriented concepts [33] like inheritance, polymorphism etc. to develop some complex test benches. Similarly, it can interact with other hardware languages through DPI features [6]. We do not consider the modeling and transformation of such advanced SystemVerilog features as these concepts are irrelevant in the given research context.

In **Table 4**, the major details regarding the conceptual mapping of SystemVerilog and Timed Automata with respect to SMD constructs are provided, without going into the low-level implementation details. It is important to mention here that the OCL basic operators like arithmetic, comparison etc. are logically equivalent to the SystemVerilog operators [34]. Consequently, it is straightforward to convert the OCL expressions, given in the SMD attributes like guard, effect etc., into the corresponding SystemVerilog code. On the other hand, the OCL basic operators are also available in Timed Automata. We are not including the low-level implementation details of Timed Automata operators and concepts like locations, edges etc. because such details can be found at [9]. Furthermore, the source code of MTE is publically available [19], where all the low-level details are available with proper comments.

#### D. TRANSFORMATION FOR NLCTL

The proposed NLCTL grammar is implemented, to accurately generate the corresponding CTL assertions. For example, the NLCTL rule 1 states that the requirement can be expressed through *Property* and *Type* terminal symbols. In MTE, the *Requirement* is transformed to *property* attribute in CTL. Moreover, the NLCTL *Property* terminal symbol is transformed to *Query attribute* in CTL. Furthermore, the *Type* terminal symbol of NLCTL is transformed to *Query Operator* in CTL.

Particularly, the *Type* terminal symbol is ultimately represented through five nonterminal symbols in NLCTL as per rule 14. To implement rule 14 in MTE, the NLCTL Type nonterminal symbols "*Possibly, Invariantly, Potentially always, Eventually* and *Leads to*" are transformed into the CTL operators "E <>, A[], E[], A <> and  $\rightarrow$ " respectively. Similarly, all the proposed NLCTL grammar rules are implemented. Consequently, the MTE is able to accurately generate CLT properties from NLCTL assertions.

For a better understanding of MTE capabilities, consider the transformation of TLC guiding example (introduced in Section II) as given in Figure 6. Particularly, the MMM-compliant model of TLC is given to MTE which automatically generates four files i.e. SystemVerilog RTL, SVAs, timed automata and CTL properties. As 'SV' is a standard extension for SystemVerilog, the dynamic ABV can be performed instantly in existing Universal Verification

FIGURE 6. Transformation of traffic lights controller guiding example.

Methodology (UVM) [38] based simulators like QuestaSIM. On the other hand, the static ABV can also be performed instantly in UPPAAL tool as it fully recognizes the timed automata model and CTL properties through 'XTA' and 'Q' formats respectively.

#### **IV. VALIDATION**

The applicability of MODEVES framework is demonstrated through eight benchmark case studies i.e. Traffic Lights Controller (TLC), Car Collison Avoidance System (CCAS), Arbiter, Elevator, Unmanned Aerial Vehicle (UAV), Automated Teller Machine (ATM), Train Gate and Bridge Crossing system. However, this article includes the details of only three case studies (i.e. Arbiter, Elevator and Unmanned Aerial Vehicle) due to space limitations. In this regard, the models of all the eight case studies, along with the source code of MTE, are available at [19] for further evaluation. The MMM is applied to capture the structural, behavioral and verification requirements (Section IV-A, Section IV-B and Section IV-C), using the Papyrus modeling editor [35]. Subsequently, the MTE is utilized to generate the target code.

## A. ARBITER CASE STUDY

This case study represents the design of an arbiter that is implemented as one-hot coding style state machine. It has seven possible states i.e. MASTER1, MASTER2, MASTER3, IDLE, IDLE1, IDLE2 and IDLE3. Any or all of the three master devices can make a request for the grant of the bus and the arbiter will select who gets the bus by using the round robin policy. The master device will be able to perform certain transactions after acquiring the bus. The bus is available for other requests after the completion of transaction.

#### 1) REQUIREMENTS SPECIFICATION

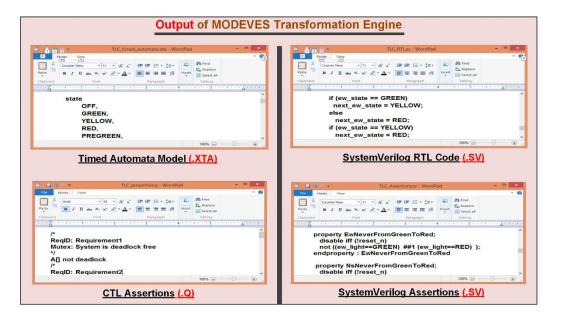

**Figure 7** shows the structural requirements of arbiter, captured through the MMM guidelines. The arbiter states have been represented through enumeration. We identify and capture the following behavioral requirements:

- State machine goes to the IDLE state on system reset.

- In the IDLE state, any or all the masters can send a request to acquire the bus. The decision of bus grant is taken in a priority-encoding fashion. For example, the bus will be granted to the MASTER1 device if all the master devices request for the bus in the IDLE state. In the MASTER state, the grant signal will be asserted to the respective master device. The master device will free the bus by sending the done signal and consequently the system moves to the IDLE state of the corresponding master device (e.g. IDLE1).

- When the system is in IDLE1 state, it prioritizes the assignment of a bus to the master devices in the order of MASTER2, MASTER3 and then MASTER1. Similarly, the priority of bus assignment is MASTER3, MASTER1 and then MASTER2 if the system is in IDLE2 state. Finally for IDLE3 state, the priority of bus assignment is MASTER1, MASTER2 and then MASTER3.

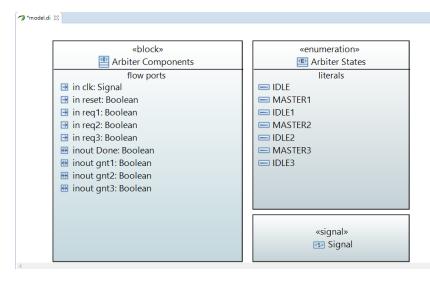

The behavior of arbiter is modeled and verification aspects are included in the models through both SVOCL as well as NLCTL, as shown in **Figure 8**. The following verification aspects have been identified and included in the arbiter model:

1. A grant should be asserted for every request received by the arbiter. The "gnt" signal should be asserted within 1 clock cycle for any one of the requesting masters.

FIGURE 7. Structural requirements of arbiter through MMM.

- 2. The arbiter IDLE state should be working correctly i.e. it cannot go to IDLE 1, IDLE 2 and IDLE 3 from the IDLE state.

- 3. The arbiter master states should work as: 1) arbiter cannot go to IDLE2, IDLE3, MASTER2 and MASTER3 states from MASTER1 state 2) arbiter cannot go to IDLE1, IDLE3, MASTER1 and MASTER3 states from MASTER2 state 3) arbiter cannot go to IDLE1, IDLE2, MASTER1 and MASTER2 states from MASTER3 state.

- Arbiter idle states should work as: (1) arbiter cannot go to IDLE2 and IDLE3 states from IDLE1 state.

(2) arbiter cannot go to IDLE1 and IDLE3 states from IDLE2 state. (3) arbiter cannot go to IDLE1 and IDLE2 states from IDLE3 state.

- 5. Ensure the fairness of arbiter i.e. the grants should be assigned to masters on equal basis.

As design and verification requirements are modeled altogether (**Figure 8**), this provides the basis to generate both SVAs and CTL assertions along with SystemVerilog RTL code and Timed Automata model through MTE. It is important to note that we differentiate SVOCL and NLCTL assertions through Requirement key word of NLCTL, as shown in **Figure 8**. The next step is to utilize the MTE to transform the source models into the target models, as shown in **Figure 9**.

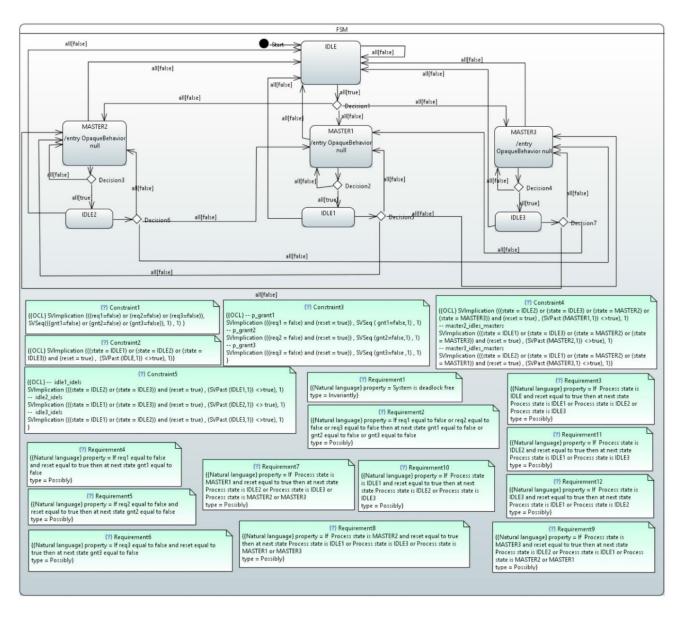

The MTE generates model\_asserts.sv, model\_behavior.sv, model\_timed\_automata.xta and model\_properties.q files for SVAs, SystemVerilog RTL code, Timed Automata model and CTL assertions respectively. It is not possible to describe the complete MTE details due to space limitations. However, we upload MTE and arbiter case study here [19], so that, the interested readers can perform further evaluation.

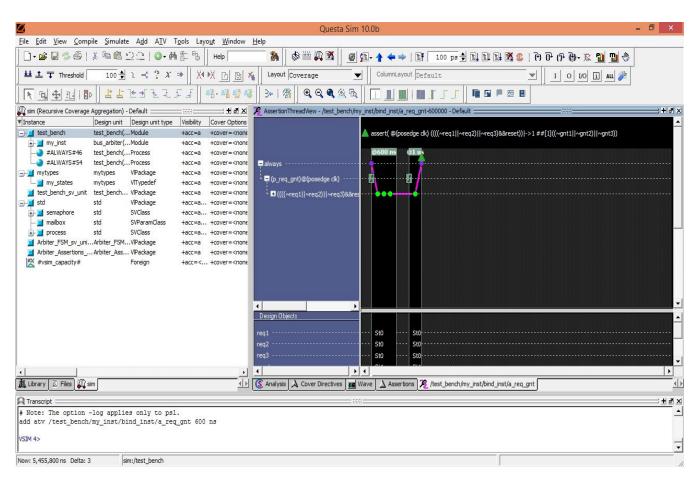

## 2) DESIGN VERIFICATION

After the automatic generation of target models through MTE, both static as well as dynamic ABV can be performed

in the respective tools. Here, we use QuestaSIM to perform dynamic ABV by utilizing the SystemVerilog RTL and assertions files which are generated through MTE. During the design varication (simulation), we encounter failure of an assertion. We analyze the cause of failure by utilizing the advance features of QuestaSIM, as shown in **Figure 10**. We investigated the cause of this failure and correct the design accordingly. Finally, after rigorous simulation, it has been analyzed that the arbiter design is free of errors. Here, we include the summary of design verification, however, the complete details can be found at [36].

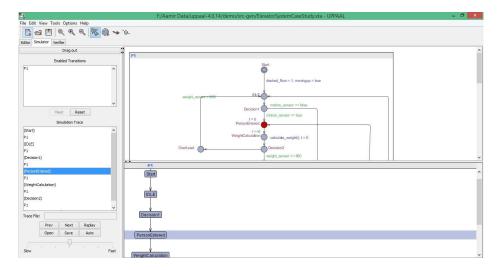

In addition to dynamic ABV, we also perform static ABV by using open source UPPAAL tool. Particularly, we use Timed Automata model and CTL assertions files that are generated through MTE. We verify different properties like deadlock etc. as included in the model through NLCTL. The verification of one property in UPPAAL tool is shown in **Figure 11**. Further details regarding the static ABV of arbiter can be found at [36].

After successful verification, we employ Xilinx Vivado [37] to perform the code synthesis of SystemVerilog RTL code. However, we are not including the details of dynamic ABV (QuestaSim) and code synthesis (Xilinx Vivado) here due to space limitations. The interested readers can find the complete design verification and code synthesis details at [36].

#### **B. ELEVATOR CASE STUDY**

The case study represents the design of an elevator which is used to move the people and goods between different floors of a building. A weight sensor is installed to calculate the overall load. The maximum allowed wait is 800 kg. The panel is attached in the elevator to select the desired floors in a sequence as per requirements. The emergency sensor is also installed to instantly stop and open exit passage of the moving elevator in the case of emergency situations.

FIGURE 8. Modeling behavioral and verification requirements of arbiter through MMM.

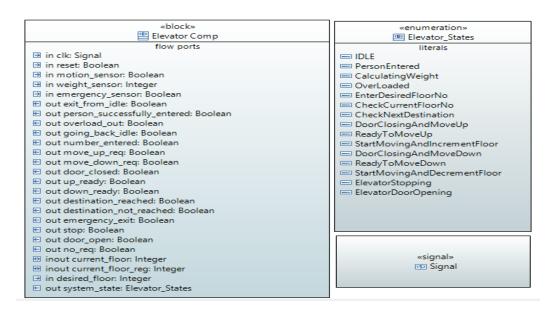

#### 1) REQUIREMENTS SPECIFICATION

The structure of elevator is modeled through the MMM guidelines, as shown in **Figure 12**. The following behavioral requirements of elevator are required:

- Initially, elevator should be in the IDLE state. Once persons are entered into an elevator, the overall weight is calculated. Subsequently, if the weight of elevator is greater than 800 than it is moved to the IDLE state by producing weight overload alarm. Otherwise, elevator should move further to check the desired floor number.

- The elevator should move upward or downward depending upon desired floor number and current floor of elevator.

- Finally, the elevator should reach to desired floor and subsequently move to initial state (IDLE).

The following verifications aspects of elevator are identified:

- 1. Confirm that whenever an elevator is moving, it should not be in the IDLE state.

- 2. Confirm the correct operating mechanism of elevator i.e. It shouldn't move in the upward and downward direction at the same time.

- 3. Confirm that when the elevator is moving either upward or downward, the door of elevator should not be opened.

- 4. Confirm that the overall weight of the elevator should be within the given limits (less than 800 KG).

- 5. Confirm that whenever the emergency sensor gets activated, the emergency exit should also be activated at the same time.

| MODEVES Transformation Eng | ine                                                                                                                    |                                                      | _                                                                           |                          | ×   |

|----------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------|-----|

| Input Model: CSE           | E\workspace_research_MDSE_new\CS2 lat                                                                                  | est\model.uml                                        | i<br>Browse                                                                 |                          |     |

| Select Method:<br>Both     | <ul> <li>☑ Assertions Code</li> <li>☑ Behavior Code</li> <li>☑ Timed Automata Code</li> <li>☑ Property Code</li> </ul> | File Name:<br>File Name:<br>File Name:<br>File Name: | model_asserts<br>model_behavior<br>model_timed_automata<br>model_properties | .sv<br>.sv<br>.xta<br>.q | > > |

| Destination Folder:        | C:\Users\AamirNaeem\Desktop\target                                                                                     | Reset                                                | Browse Generate                                                             |                          |     |

| Status                     |                                                                                                                        |                                                      |                                                                             |                          |     |

|                            | [                                                                                                                      | Open Folder                                          | Close                                                                       |                          |     |

FIGURE 9. Generating target files for the arbiter model through MTE.

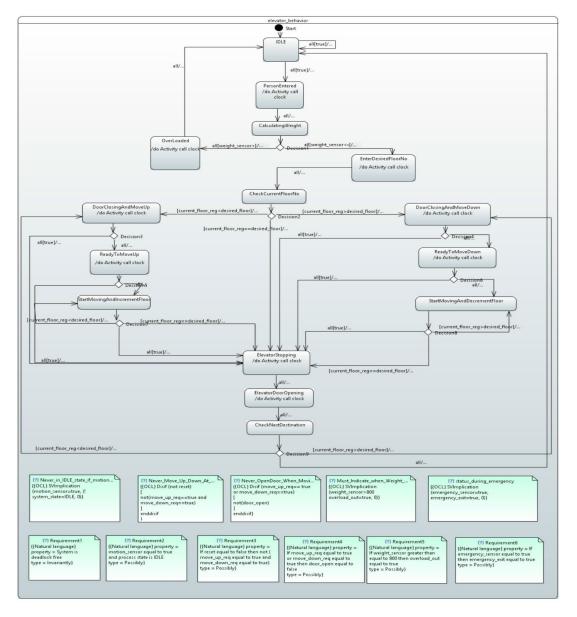

The aforementioned verification requirements are included in the behavioral model of elevator by utilizing both SVOCL and NLCTL approaches as shown in **Figure 13**. Once the design and verification requirements have been successfully modeled (**Figure 12** and **Figure 13**), we generate SystemVerilog RTL, Timed Automata model, SystemVerilog Assertions and CTL assertions through MTE. However, we are not including the details of code generation here because such details are already given in Section **IV-A-2**.

## 2) DESIGN VERIFICATION

We have performed both static as well as dynamic ABV for elevator system by utilizing the generated target files i.e. SystemVerilog RTL, Timed Automata model, SystemVerilog Assertions and CTL assertions. Firstly, we perform static ABV by utilizing UPPAAL tool. Particularly, the Timed Automata model and CTL assertions file, generated through MTE, are given to UPPAAL tool. Subsequently, design verification is performed through UPPAAL tool as shown in **Figure 14**. Once, all the given properties are successfully verified through UPPAAL, we perform dynamic ABV. Particularly, SystemVerilog RTL and assertions files are given as an input to QuestaSIM simulator. Subsequently, the simulation is performed to verify the given properties.

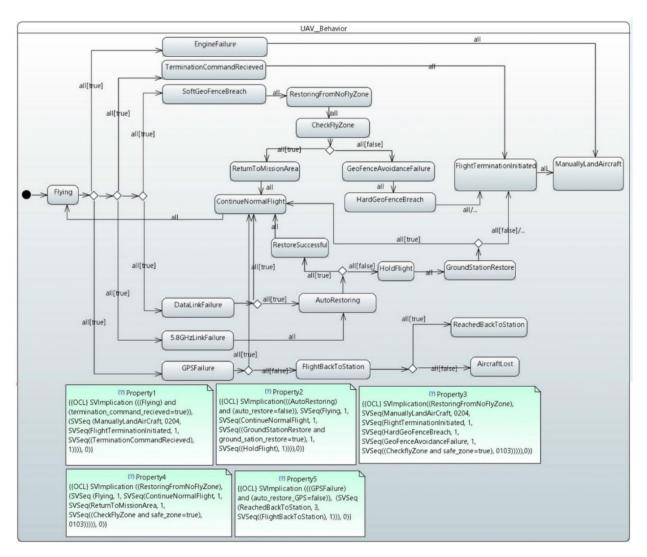

#### C. UNMANNED AERIAL VEHICLE (UAV) SYSTEM

The UAV is typically an aircraft that can be controlled remotely or fly autonomously on the basis of pre-programmed flight plans. It has quite complex dynamic automation systems. This case study demonstrates the design of UAVs with various safety constraints.

## 1) REQUIREMENTS SPECIFICATION AND DESIGN VERIFICATION

The structure of UAV system comprises one major block that contains required ports/registers. Furthermore, various UAV states are represented through enumeration, as shown in **Figure 15**. The following behavioral requirements are identified:

- Initially, the system is in FLYING state and continuously monitoring the engine failure and GPS failure states. The system moves to either ENGINE FAILURE state or GPS FAILURE state depending on the sensor values (engine\_failure\_sensor and gps\_failure\_sensor). Similarly, the system is also monitoring TERMINATION COMMAND RECEIVED, 2.4GHz LINK FAILURE, SOFT GEOFENCE BREACH and DATALINK FAIL-URE states through the termination\_command\_recieved, 2.5GHz\_link\_failue\_senor, geo\_fencing\_sensor and datalink\_failure\_sensor respectively.

- Once the system is in ENGINE FAILURE state, it has to be landed on emergency basis within 3 clock cycles. In the TERMINATION COMMAND RECEIVED state, the system should move to the FLIGHT TERMINA-TION INITIATED state after one clock cycle and

FIGURE 10. Performing design verification of arbiter in QuestaSIM.

subsequently move to the MANUALLY LAND AIRCRAFT state within three clock cycles.

- Once the system is in SOFT GEOFENCE BREACH state, it should move to RESTORING FROM NO FLY ZONE state on the next clock cycle and perform certain checks to move into respective state. Similarly, in the DATA LINK FAILURE state, the system evaluates certain conditions (e.g. 900MHz\_link\_failure\_sensor, 5.8GHz\_link\_failure\_sensor etc.) to move into a particular state accordingly.

- In case of GPS failure, the system continues normal flight on a successful GPS auto restore. Otherwise, the system should move to the FLIGHT BACK TO STATION state and subsequently moves to either REACHED BACK TO STATION state or AIRCRAFT LOST state, depending on the underlying conditions.

Following safety constraints are identified (Figure 16):

1. Property1: In case of termination command during the flight, the system should move to FlightTerminationInitiated within two clock cycles and subsequently enters into ManuallyLandAirCraft state within two to four clock cycles.

- 2. Property2: From AutoRestoring state, the system should move to Flying state in 4 clock cycles on the activation of auto\_restore and ground\_station\_restore.

- 3. Property3: From RestoringFromNoFlyZone, the system should move to CheckFlyZone within 1 to 3 clock cycles. However, on the deactivation of safe\_zone, the system should move to FlightTerminationInitiated state within 3 clock cycles and subsequently to ManuallyLandAirCraft state within 2 to 4 clock cycles.

- 4. Property4: The system should move from RestoringFromNoFlyZone to CheckFlyZone within 1 to 3 clock cycles and upon the activation of safe\_zone, the system should move to the Flying state after 3 clock cycles.

- 5. Property5: In case of a GPS failure with an unsuccessful automatic restore, the system should go back to station within 4 clock cycles.

In arbiter and elevator case studies, we represent the verification aspects through both SVOCL as well as NLCTL to demonstrate the simultaneous application of both approaches. Now, we prove the application of SVOCL and NLCTL individually. Particularly, the idea is to show that SVOCL and NLCTL can be used separately through the MODEVES framework as per requirements. Here, we include the

| <u>B</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | F:/Aamir Data/uppaal-4.0.14/demo/src-gen/ArbitorCaseStudy.xml - UPPAAL | - 0 ×                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------|

| File Edit View Tools Options Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                        |                                       |

| Editor Simulator Verifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                        |                                       |