Received February 29, 2020, accepted March 20, 2020, date of publication March 27, 2020, date of current version April 14, 2020. *Digital Object Identifier* 10.1109/ACCESS.2020.2983796

# A -193.6 dBc/Hz FoM<sub>T</sub> 28.6-to-36.2 GHz Dual-Core CMOS VCO for 5G Applications

# YUPENG FU<sup>®</sup>, (Student Member, IEEE), LIANMING LI<sup>®</sup>, (Member, IEEE), DONGMING WANG<sup>®</sup>, (Member, IEEE), AND XUAN WANG

School of Information Science and Engineering, Southeast University, Nanjing 210096, China National Mobile Communication Research Laboratory, Southeast University, Nanjing 210096, China Purple Mountain Laboratories, Nanjing 211111, China

Corresponding authors: Lianming Li (lianming.li@seu.edu.cn) and Dongming Wang (wangdm@seu.edu.cn)

This work was supported in part by the National Key Research and Development Program of China under Grant 2018YFE0205900, in part by the National Science and Technology Major Project under Grant 2018ZX03001008, in part by the National Nature Science Foundation of China under Grant 61306030 and Grant 61674037, and in part by the Natural Science Foundation of Jiangsu Province of China under Grant BK20180368.

ABSTRACT By combining the transformer feedback and VCO multi-core techniques, this paper presents a 0.5 V low voltage 28.6-to-36.2 GHz dual-core VCO for 5G applications. Based on the transformer feedback topology, with the power-ground interconnect inductor and embedded decouple capacitor, the second harmonic real impedance is achieved at the VCO cross-couple pair source terminal. Accordingly, the common-mode current path is reduced and the signal symmetry improved, suppressing the flicker noise up conversion. With a 4 bit switch capacitors and varactors, the proposed VCO achieves a 28.6-to-36.2 GHz (23.5 %) tuning range, and its flicker noise corner is from 250 to 980 kHz. Fabricated in a 65nm CMOS process, the VCO consumes 4.6mW from a 0.5 V supply voltage with a core area of about 0.24 × 0.5 mm<sup>2</sup>. At 31 GHz, the proposed VCO achieves a phase noise of -103 dBc/Hz@1MHz offset, resulting in a figure-of-merit (FoM) of -186.2 dBc/Hz and tuning range figure-of-merit (FoM<sub>T</sub>) of -193.6 dBc/Hz, respectively.

**INDEX TERMS** Dual core, low supply, transformer feedback, VCO.

#### I. INTRODUCTION

In WRC-19, 5G millimeter wave (mmWave) spectra have been selected, the mmWave RF front-end comes to the turning point from concept to implementation [1]. With wide bandwidth characteristics, the mmWave band, such as the 28 and 39 GHz, can be used to realize Gbps data rate with high-order modulation schemes [2], [3]. From the implementation point of view, this poses very challenging requirements for the VCO phase noise and tuning range. Moreover, for the portable wireless communication application, it is preferred to realize VCO with low voltage and low power consumption.

In response to above requirements, a transformer feedback VCO topology is proposed [3]–[5], improving the start-up gain and achieving low supply operation. However, to realize more than 20% tuning range, the ratio of the switch capacitor  $C_{max}$  to  $C_{min}$  is large. As a result, the tank quality-factor (*Q*-factor) and the tank impedance is limited, worsening the

The associate editor coordinating the review of this manuscript and approving it for publication was Xiaoguang Leo Liu<sup>10</sup>.

VCO phase noise. As an alternative solution, with the VCO multi-core techniques [6], the VCO phase noise can be improved by 10 logN dB, where N is the VCO core number. In addition, by doing so the VCO tuning range is increased due to less ratio of the buffer parasitic capacitor over the LC tank capacitor. Moreover the output signals of each VCO core are coupled with each other, improving the signal symmetry [6]. However, the VCO power consumption is enlarged as the VCO core number increases.

To address the low voltage, wide tuning range and low phase noise issues of mmWave VCOs, considering the trade-off between the VCO phase noise and power consumption [7], in this paper a dual-core transformer feedback VCO is proposed by combining the transformer feedback and VCO multi-core techniques. Based on the transformer feedback VCO topology, with the power-ground interconnect inductor and embedded decouple capacitor, the common-mode current return path is reduced, and the common-mode resonance is achieved at the VCO second harmonic frequency. Accordingly, the source tank impedance becomes real at the second

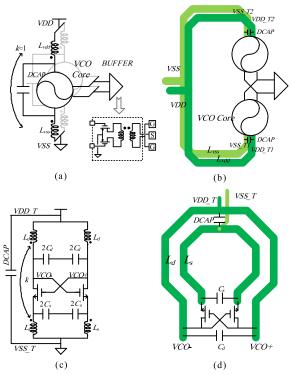

FIGURE 1. (a) Dual-core VCO topology, and (b) layout; (c) VCO cell topology, and (d) layout.

harmonic frequency, aligning the fundamental and the second harmonic phase and improving the signal symmetry and phase noise performance [8]–[9].

This paper is organized as follows. In Section II, the proposed dual-core VCO is discussed and simulated. Section III presents the VCO test results and performance comparison. Final conclusion is drawn in Section IV.

## **II. DESIGN AND ANALYSIS OF THE DUAL-CORE VCO**

Fig. 1(a) and (b) presents the proposed dual-core VCO topology and its layout floorplan, in which the power-ground interconnect tail inductors, Lvdd and Lvss, are strongly coupled with each other with a coupling coefficient of about 1. With the decouple capacitor DCAP, the common-mode signal at each VCO power supply (such as VDD T1 and VDD T2) is directly coupled to the ground (such as *VSS\_T1* and *VSS\_T2*). In this way, the VCO common-mode current return path is reduced, relaxing the outside parasitics effect and filtering the supply noise [9]. As to be explained shortly, the VCO common-mode resonance frequency is set at the second harmonic, thereby increasing the common-mode impedance for less second harmonics and improving the signal symmetry. For test purpose, the output buffer is required, which directly connects with the VCO output as close as possible to reduce the parasitic capacitor. As indicated in Fig. 1(b), with the dual-core topology the VCO layout can be realized in a symmetrical way, improving the VCO symmetry further. With less second harmonics and improved signal symmetry, the VCO flicker (1/f) noise up-conversion can be suppressed [10].

Fig. 1(c) shows the topology of the oscillator cell. As indicated, with a coupling coefficient of k, the transformer's primary and secondary inductors,  $L_d$  and  $L_s$ , are connected to the transistor drain and source terminals, respectively. With the 4 bit switch capacitors  $C_d$  and  $C_s$ , varactors and parasitic capacitance, the above two inductors realize an LC tank. Fig. 1(d) presents the detailed layout of the VCO cell, in which the embedded decoupling capacitor *DCAP* connects VCO core power and ground (*VDD\_T* and *VSS\_T*), resulting in a very compact layout.

According to [3]–[7], the transformer based VCO has two resonance frequencies:

$$\omega_{1,2} = \sqrt{\frac{(\omega_s^2 + \omega_d^2) \pm \sqrt{(\omega_s^2 + \omega_d^2)^2 - 4(1 - k^2)\omega_s^2\omega_d^2}}{2(1 - k^2)}}$$

(1)

where  $\omega_d = 1/\sqrt{2L_dC_d}$  and  $\omega_s = 1/\sqrt{2L_sC_s}$ . Note that, the lower frequency  $\omega_1$  is the operating frequency and mainly determined by  $L_d$  and  $C_d$ . To achieve the aforementioned phase alignment of the fundamental and second harmonic for better signal symmetry [8], for initial design  $\omega_2$  is firstly set to be twice of the  $\omega_1$ . In principle, the second harmonic frequency  $\omega_2$  should be calculated with the VCO common-mode model, whose inductor and capacitor values are different from that of the differential model. In this design, the VCO resonance frequency and design parameters are optimized with simulations.

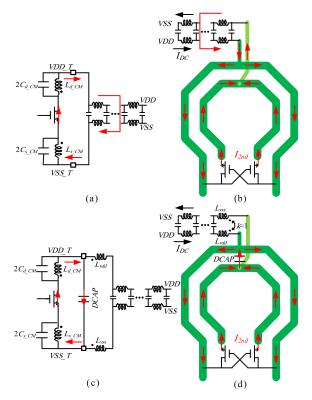

For the VCO second harmonic impedance optimization, Fig. 2(a) and (b) present the common-mode return path schematic and layout of the transformer based VCO without the interconnect inductor and the embedded DCAP, respectively. As indicated, without the interconnect its common-mode resonance frequency will be affected by the outside decouple network parasitics, resulting in the inductor and the embedded DCAP the VCO power and ground are connected to the outside decouple network, and uncontrolled second harmonic frequency and worsening the signal symmetry. In contrast, as indicated in Fig. 2(c) and (d), with the DCAP and the strongly-coupled interconnect inductor, the VCO power and ground common-mode return path is reduced and well controlled. With optimizations, the VCO common-mode resonance frequency is set at the second harmonic frequency. Note that, in the common-mode model the equivalent inductor and capacitor values at the transistor drain and source terminals are represented as Ld CM, Ls CM and  $C_d C_M, C_s C_M$ , respectively.

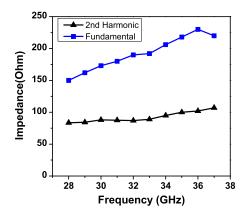

To achieve good phase noise performance, the VCO tank loaded Q-factor is optimized by tuning  $L_d$ ,  $L_s$  and k to achieve the transistor source to drain terminal voltage ratio of 0.5 at the operating frequency, which helps to increase the start-up gain at the same time [3]–[5]. To increase output power, the VCO tank impedance is optimized to match the input impedance of the output buffer by optimizing  $L_d$ and  $C_d$ . For this VCO, its design parameters are:  $L_d =$ 110pH,  $L_s = 80$  pH, and k = 0.6. Fig. 3 shows the

<sup>noise</sup>(t)(10<sup>3</sup>C<sup>-1</sup>A/sqrt(Hz))

(1), ds

FIGURE 2. The common-mode return path of the transformer based VCO (a) schematic and (b) layout w/o the interconnect inductor and the embedded DCAP; (c) schematic and (d) layout w/ the interconnect inductor and the embedded DCAP.

FIGURE 3. The fundamental and second harmonic impedances at the cross-coupled pair drain and source terminals, respectively.

tank fundamental and second harmonic impedances at the cross-couple pair drain and source terminals, respectively. Accordingly, the fundamental tank impedance at the drain is about 200  $\Omega$ . In this way, an impedance match is realized between the cross-couple pair and the output buffer, increasing the output power. As indicated, the VCO second harmonic tank impedance at the cross-couple pair source terminal is real, about 70  $\Omega$ , increasing the symmetry of the signal [7]–[12]. Moreover, with the source degeneration effect, the second harmonic current into the LC tank will be suppressed. With the improved signal symmetry and less second harmonics, the 1/f noise up-conversion is reduced.

1.5

1.0

0.5

0.0

/<sub>noise</sub>@10KHz(nA/sqrt(Hz))

Inoise@10KHz

- h<sub>ds</sub>(t)\*I<sub>nois</sub>

15 20

t (ps)

25 30

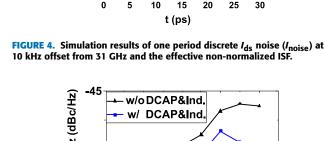

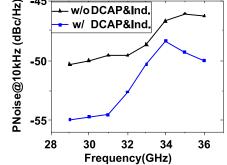

FIGURE 5. Phase noise simulation w/ and w/o the power-ground interconnect inductor and the DCAP.

To illustrate the improved signal symmetry, with the PSS and PXF simulations Fig. 4 shows the discrete  $I_{ds}$ noise at 10 kHz offset and the effective non-normalized impulse sensitivity function (ISF) which is the product of the non-normalized ISF,  $h_{ds}(t)$ , and  $I_{ds}$  noise,  $I_{noise}$  respectively [12]. As indicated, the VCO conduction angle is 180 degree, and benefiting from the physical symmetry and the improved signal symmetry, the proposed dual-core VCO ISF is symmetrical. With the ISF result, the VCO phase noise can be calculated as,

$$L(\Delta\omega) = \left(\frac{\sqrt{2}}{2\Delta\omega}\frac{1}{T}\int_0^T h_{ds}(t)I_{noise}(t)dt\right)^2$$

(2)

where T is the period of the VCO. Accordingly, the calculated phase noise is -54 dBc/Hz at 10 kHz offset from 31 GHz.

Fig. 5 shows the phase noise simulation results at 10 kHz offset with and without the power-ground interconnect inductor and the DCAP. As indicated, with the power-ground interconnect inductor and the DCAP, the VCO phase noise is lower, proving their advantages on the 1/f noise reduction. To be specific, the phase noise is about -54 dBc/Hz at 10 kHz offset from 31 GHz output frequency, which is the same as the above calculated results.

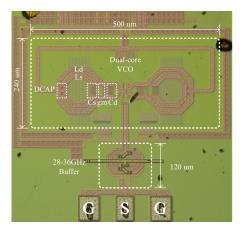

FIGURE 6. Chip micrograph.

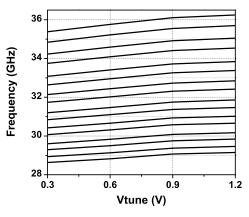

FIGURE 7. Tuning range with 4 bit switch capacitor.

#### **III. IMPLEMENTATION AND MEASUREMENT RESULTS**

Fig. 6 shows the micrograph of the proposed VCO. Fabricated in a 65nm CMOS process, the dual-core VCO core area is  $0.24 \times 0.5 \text{ mm}^2$ . Corresponding to the VCO structure, the inductors ( $L_d$  and  $L_s$ ), capacitors ( $C_d$  and  $C_s$ ) and transistors ( $g_m$ ) are indicated. To reduce the substrate loss and to increase the tank *Q*-factor, the floating metal shield is used for the inductor. The VCO consumes a DC power of about 4.6 mW from a 0.5 V supply.

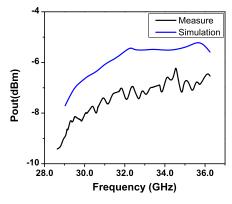

With the Rhode & Schwarz phase noise analyzer equipment, the oscillator tuning range, the output power and the phase noise are measured. As shown in Fig. 7, with a 4 bit switch capacitor, the VCO achieves a 28.6 to 36.2 GHz (23.5 %) tuning range. As indicated in Fig. 8, compared to the simulation results, due to the cable loss the VCO output power is about 1 dB lower.

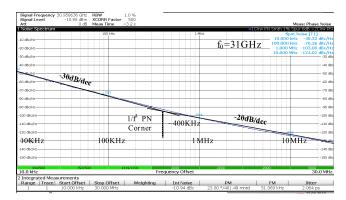

Fig. 9 shows the VCO phase noise performance at 31 GHz. As indicated, the VCO achieves a phase noise of -103 and -124 dBc/Hz at 1 and 10 MHz offset, respectively, and the 1/f noise corner is about 400 kHz. Note that, as indicated in [8], the 1/f noise is very sensitive to the transformer coupling coefficient k and the VCO common-mode impedance. Suffering from the process PVT corner and the EM simulation accuracy, the tested phase noise at 10 kHz offset is

FIGURE 8. Output power comparison between simulations and measurements.

FIGURE 9. Phase noise measurement at 31 GHz.

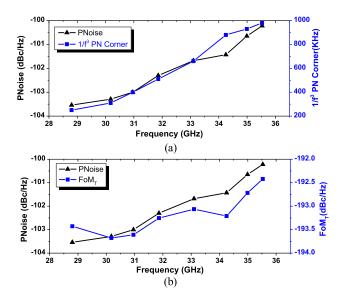

**FIGURE 10.** (a) Output phase noise and 1/f noise corner, (b) output phase noise and  $FoM_T$  versus the operating frequency.

about -48 dBc/Hz, which is 6 dB higher than the above calculation result. Accordingly, the 1/f noise corner frequency is about 1.5 times higher than the simulation results.

Versus the operating frequency, Fig. 10(a) shows the output phase noise at 1MHz offset and 1/f noise corner, while

#### TABLE 1. Performance summary of state-of-the-art oscillators.

|                                    | This Work | VLSI 2019 [3] | TCSI 2018 [8] | JSSC 2018 [9] | ISSCC 2019 [13] | RFIC 2018 [14] |

|------------------------------------|-----------|---------------|---------------|---------------|-----------------|----------------|

| FO (GHz)                           | 31        | 25.6          | 25            | 31.2          | 29.92           | 26             |

| FTR (%)                            | 23.5      | 14            | 12            | 17            | 16              | 42.3           |

| PNoise @1MHz<br>(dBc/Hz)           | -103      | -105.8        | -110          | -104          | -112.3°         | -102.6         |

| Power (mW)                         | 4.6       | 10.8          | 4.8           | 13            | 4               | 5.5            |

| VDD (V)                            | 0.5       | 0.9           | 0.6           | 1             | 0.48            | 0.9            |

| FoM @1MHz<br>(dBc/Hz)              | -186.2    | -184          | -191.2        | -183          | -189.8          | -183.3         |

| FoM <sub>T</sub> @1MHz<br>(dBc/Hz) | -193.6    | -186.9        | -192.8        | -187.6        | -193.9          | -195.8         |

| Process<br>(CMOS)                  | 65 nm     | 65 nm         | 65 nm         | 28 nm         | 65 nm           | 28 nm          |

a. FoM = PNoise-20log( $f_0 / \Delta f$ ) + 10log( $P_{DISS} / 1mW$ )

b. FoM<sub>T</sub> = PNoise-20log( $f_0 / \Delta f$ ) + 10log( $P_{DISS} / 1mW$ ) - 20log(*FTR*/10)

c. Measured with divide-by-2 divider

Fig. 10(b) indicates the output phase noise and tuning range figure-of-merit (FoM<sub>T</sub>). Over the 28.6-to-36.2 GHz tuning range, the phase noise is from -103.5 to 100.5 dBc/Hz at 1MHz offset, and the 1/f noise corner is from 250 to 980 kHz. At 31 GHz, the FoM<sub>T</sub> is about -193.6 dBc/Hz.

Table 1 summarizes the comparison with state-of-the-art results. With the proposed structure, this oscillator achieves a good tuning range and phase noise performance, resulting in a -193.6 dBc/Hz FOM<sub>T</sub> and -186.2 dBc/Hz FoM with a low supply voltage.

## **IV. CONCLUSION**

This paper presents a low voltage 28.6-to-36.2GHz dual-core VCO in a 65nm CMOS process for 5G applications. Based on the transformer feedback topology, with the powerground interconnect inductor and embedded decouple capacitor, the second harmonic real impedance is achieved at the VCO cross-couple pair source terminal. Accordingly, the common-mode current path is reduced and the signal symmetry improved, suppressing the flicker noise up conversion. With a 4 bit switch capacitor, the VCO achieves a 23.5 % tuning range from 28.6 to 36.2 GHz. At 31 GHz, the proposed VCO achieves phase noise of -103 dBc/Hz and FoM<sub>T</sub> of - 193.6 dBc/Hz at 1 MHz offset.

#### REFERENCES

- [1] L. Li, D. Wang, X. Niu, Y. Chai, L. Chen, L. He, X. Wu, F. Zheng, T. Cui, and X. You, "MmWave communications for 5G: Implementation challenges and advances," *Sci. China Inf. Sci.*, vol. 61, no. 2, Feb. 2018, doi: 10.1007/s11432-017-9262-8.

- [2] J. Zhang, H. Liu, Y. Wu, C. Zhao, and K. Kang, "An injectioncurrent-boosting locking-range enhancement technique for ultrawideband mm-wave injection-locked frequency triplers," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 7, pp. 3174–3186, Jul. 2019, doi: 10.1109/TMTT.2019.2907254.

- [3] Y. Fu, L. Li, D. Wang, X. Wang, and L. He, "28-GHz CMOS VCO with capacitive splitting and transformer feedback techniques for 5G communication," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 27, no. 9, pp. 2088–2095, Sep. 2019.

- [4] K. Kwok and H. C. Luong, "Ultra-low-Voltage high-performance CMOS VCOs using transformer feedback," *IEEE J. Solid-State Circuits*, vol. 40, no. 3, pp. 652–660, Mar. 2005.

- [5] J. Yang, C.-Y. Kim, D.-W. Kim, and S. Hong, "Design of a 24-GHz CMOS VCO with an asymmetric-width transformer," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 57, no. 3, pp. 173–177, Mar. 2010.

- [6] J. Zhang, C. Zhao, Y. Wu, H. Liu, Y. Zhu, and K. Kang, "An ultralow phase noise eight-core fundamental 62-to-67-GHz VCO in 65-nm CMOS," *IEEE Microw. Wireless Compon. Lett.*, vol. 29, no. 2, pp. 125–127, Feb. 2019.

- [7] A. Hajimiri and T. H. Lee, "A general theory of phase noise in electrical oscillators," *IEEE J. Solid-State Circuits*, vol. 33, no. 2, pp. 179–194, Feb. 1998.

- [8] S. Guo, P. Gui, T. Liu, T. Zhang, T. Xi, G. Wu, Y. Fan, and M. Morgan, "A low-voltage low-phase-noise 25-GHz two-tank transformer-feedback VCO," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 10, pp. 3162–3173, Oct. 2018.

- [9] Y. Hu, T. Siriburanon, and R. B. Staszewski, "A low-flicker-noise 30-GHz class-F23 oscillator in 28-nm CMOS using implicit resonance and explicit common-mode return path," *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 1977–1987, Jul. 2018.

- [10] M. Shahmohammadi, M. Babaie, and R. B. Staszewski, "A 1/f noise upconversion reduction technique for voltage-biased RF CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 51, no. 11, pp. 2610–2624, Nov. 2016.

- [11] E. Hegazi, H. Sjoland, and A. Abidi, "A filtering technique to lower oscillator phase noise," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, 2001, pp. 364–365.

- [12] Y. Hu, T. Siriburanon, and R. B. Staszewski, "Intuitive understanding of flicker noise reduction via narrowing of conduction angle in voltage-biased oscillators," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 12, pp. 1962–1966, Dec. 2019.

- [13] H. Guo, Y. Chen, P.-I. Mak, and R. P. Martins, "26.2 a 0.08 mm<sup>2</sup> 25.5-to-29.9GHz multi-resonant-RLCM-tank VCO using a single-turn multi-tap inductor and CM-only capacitors achieving 191.6dBc/Hz FoM and 130 kHz 1/f3 PN corner," in *IEEE Int. Solid- State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2019, pp. 410–412.

- [14] Y. Shu, H. J. Qian, and X. Luo, "A 20.7–31.8 GHz dual-mode voltage waveform-shaping oscillator with 195.8 dBc/Hz FoMT in 28 nm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2018, pp. 216–219.

**YUPENG FU** (Student Member, IEEE) was born in Heilongjiang, China, in 1991. He received the B.S. and M.S. degrees in circuits and systems from Southeast University, Nanjing, in 2014 and 2016, respectively, where he is currently pursuing the Ph.D. degree. His research interests are CMOS integrated circuits specific in PLLs for radar and communication systems.

**LIANMING LI** (Member, IEEE) was born in Runan, Henan, China, in 1978. He received the B.S. degree in physics and the M.S. degree in electrical engineering from Southeast University, Nanjing, China, in 2001 and 2004, respectively, and the Ph.D. degree from Katholieke Universiteit Leuven, Leuven, Belgium, in May 2011. From 2006 to 2011, he was a Research Assistant of ESAT-MICAS, Katholieke Universiteit Leuven, working on the mmWave CMOS design. Since

May 2011, he has been working with the School of Information Science and Engineering, Southeast University, as an Associate Professor. His present research interests focus on mmWave circuits and system design, antenna, and packaging design, as well as the frequency generation circuits design.

**DONGMING WANG** (Member, IEEE) received the Ph.D. degree from Southeast University, China, in 2006. Since then, he has been with the National Mobile Communications Research Laboratory, Southeast University, where he is currently an Associate Professor. His research interests include distributed antenna systems, large-scale MIMO systems, channel estimation, and MIMO detection. He has served as the Symposium Co-Chair of the 2015 IEEE International Confer-

ence on Communications (ICC 2015) and the IEEE Wireless Communications and Signal Processing Conference (IEEE WCSP 2017). He is currently an Associate Editor of the *Science China Information Sciences*.

**XUAN WANG** received the B.S. degree from Southeast University, Jiangsu, China, in 2017, where he is currently pursuing the Ph.D. degree. His research interests are RF and millimeter-wave CMOS integrated circuits for communication in general and more specific in PLLs.

...