Received February 24, 2020, accepted March 8, 2020, date of publication March 11, 2020, date of current version March 24, 2020. Digital Object Identifier 10.1109/ACCESS.2020.2980080

# **Hybrid Internal Vth Cancellation Rectifiers for RF Energy Harvesting**

## MUNIR A. AL-ABSI<sup>®</sup>, (Senior Member, IEEE), AND SAMI R. AL-BATATI

Department of Electrical Engineering, King Fahd University of Petroleum and Minerals, Dhahran 31261, Saudi Arabia Corresponding author: Munir A. Al-Absi (mkulaib@kfupm.edu.sa)

This work was supported by the King Fahd University of Petroleum and Minerals under Project SF191-EE-540.

**ABSTRACT** This paper presents two Internal Threshold Voltage (IVC) cancellation schemes for rectifiers used in RF energy harvesting: N-stage IVC based rectifier and IVC based rectifier with Self Vth Cancellation (SVC). The presented rectifiers reduce the threshold voltage of the transistors and deliver a high-rectified output voltage at an input frequency of 402MHz. Tanner TSPICE simulation tool in 0.18µm TSMC CMOS technology is used to confirm the functionality of the proposed designs. Simulation results show that the proposed design is superior to the previously published works in reducing the MOSFET threshold voltage and delivering a rectified high output voltage at an input voltage at an input voltage of 200mV and frequency of 402 MHz.

**INDEX TERMS** RF energy harvesting, threshold compensation, internal Vth cancellation, CMOS rectifier.

## I. INTRODUCTION

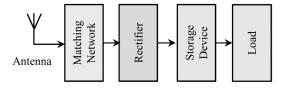

Energy harvesting is the process of extracting electrical energy from the available sources in the environment including solar, thermal, mechanical, fluid and Radio Frequency (RF) energy. In the recent years, the interest in RF energy harvesting as a promising substitute for a battery has increased rapidly. This can be attributed to the wide range of applications for wireless power transmission in areas like Radio Frequency Identification (RFID), biomedical devices, and wireless sensor networks is increasing. A typical RF energy harvesting system shown in Fig.1 consists of the antenna which receives incident power, a matching network for maximizing the power transfer and minimizing the signal reflection from the load, an RF-to-DC rectifier which is mostly responsible for the performance of energy harvesting system, storage devices which could be batteries or capacitors, and the load.

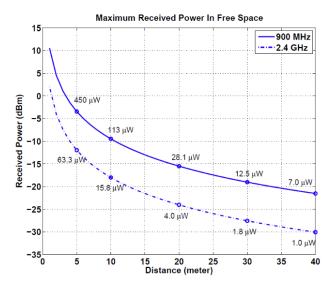

Typically, the power density for RF energy source ranges between 0.01 to  $0.1\mu$ W/cm<sup>2</sup>, which is the lowest among other sources such as vibration and thermal [2]. For instance, the maximum power received for a free space distance of 40m is  $7\mu$ W and  $1\mu$ W for frequencies of 900MHz and 2.4GHz respectively. Another important factor playing a role in the received power is the distance as shown in Fig.2.

FIGURE 1. Block diagram of a typical RF energy harvesting [1].

FIGURE 2. Maximum received power in free space versus distance [2].

Table 1 summarizes the experimental data obtained from different RF sources varying in frequency, power, and distance with the amount of harvested energy [3].

The associate editor coordinating the review of this manuscript and approving it for publication was Sun Junwei<sup>10</sup>.

| Source                                | Source<br>Power<br>(W) | Frequen<br>cy<br>(MHz) | Distance<br>(m) | Energy<br>Harvest<br>ed Rate<br>(µW) |

|---------------------------------------|------------------------|------------------------|-----------------|--------------------------------------|

| Isotropic RF<br>transmitter           | 4                      | 902-928                | 15              | 5.5                                  |

| Isotropic RF<br>transmitter           | 1.78                   | 868                    | 25              | 2.3                                  |

| Isotropic RF<br>transmitter           | 3                      | 915                    | 27              | 2                                    |

| TX91501<br>Powercaster<br>transmitter | 3                      | 915                    | 5               | 189                                  |

| TX91501<br>Powercaster<br>transmitter | 3                      | 915                    | 11              | 1                                    |

| KING-TV<br>tower                      | 960k                   | 674-680                | 4.1k            | 60                                   |

TABLE 1. Experimental data of RF energy harvesting.

CMOS technology is widely used in the design of rectifiers for RF energy harvesting. Due to the very small RF energy density, the input voltage amplitude after the matching impedance does not typically reach 300mV which is lower than the threshold voltage of the MOS transistor even though the matching impedance network is also used to boost the voltage induced by the antenna [4]. Researchers proposed different topologies to reduce the threshold voltage. Some of them reduce the threshold voltage using the body effect [3], [5]. Other techniques compensate the threshold voltage using an external auxiliary circuit to generate gate bias voltage [6]–[8]. In [9], auxiliary transistors are used to enhance the forward conduction and also to reduce the leakage of current.

Some techniques use bootstrapping circuit by charging up the bootstrapping capacitors to apply it to the gate of the main rectifying pMOS transistors [10]. In [11], a high-speed comparator is used to control the reverse leakage current. Self-Vth cancellation (SVC) is used in [12] to bias the gate by the output voltage of the rectifier itself in order to decrease the threshold voltage of the transistor by the same amount of the output DC voltage. In [13], clamper circuits were used to insert a negative DC level to bias the gates of the main rectifying pMOS devices during its conduction state.

Another approach to reducing the threshold voltage of a MOS transistor is by injecting some charges on its gate oxide. It could be done by applying a high voltage to the gate causing charges to be trapped in the oxide due to the tunneling effect. However, this approach has two main drawbacks. The trapped electrons will be released gradually over time and temperature which makes it not reliable for the long term. In addition, it has an additional fabrication cost [14].

Some schemes use advanced technologies such as zero threshold voltage MOS. However, it is not available in the standard CMOS process and requires additional fabrication

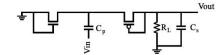

FIGURE 3. The conventional CMOS rectifier.

cost. Also, it has zero  $V_{th}$  for a small current range [15]. Schottky diode-based rectifiers are also used because of their low forward-voltage drop of about 150mV which makes it suitable for ultra-low power applications [16]. In this design, a 10-stage rectifier using Schottky diodes is proposed. It achieves an output voltage of 1.55V with an input voltage of 200 mV and it achieves an output voltage of 1.60V with an input voltage as low as 100 mV at 7.2 MHZ. The multiple stages were added in the design to boost up the voltage across the rectifier. However, Schottky diodes require additional fabrication steps because of the manufacturing incompatibility with the standard CMOS process which results in high cost. The design in [17] is based on the Villard voltage doubler circuit. The cross-coupled rectifier is another commonly used topology circuit due to its small on-resistance and dynamic compensating of the threshold voltage.

In this paper, two new IVC based CMOS rectifiers suitable for RF energy harvesting are proposed. The two designs reduce the threshold voltage of the transistors and deliver a high-rectified output voltage at an input frequency of 402MHz.

The rest of the paper is organized as follows: The two proposed rectifiers analysis and simulation results are presented in section II. The paper conclusion is presented in Section III.

#### **II. PROPOSED DESIGN**

### A. N-STAGE IVC BASED RECTIFIER

Starting from the conventional CMOS rectifier shown in Fig. 3, the output voltage can be described as:

$$V_{out} = 2V_p - V_{drop} \tag{1}$$

where  $V_{out}$  is the output voltage,  $V_p$  is the peak RF input voltage and  $V_{drop}$  is the voltage losses due to mainly the threshold voltages of the nMOS and pMOS transistors.

Therefore, it is obvious from equation (1) that the threshold voltage is the main cause of the decrease of the output voltage. By reducing the threshold voltage, not only the output voltage is maximized but also it becomes suitable for lowpower applications. In the case of using N-stage charge pump schemes, the voltage drop is multiplied by the number of stages as expressed in (2).

$$V_{out} = N(2V_p - V_{drop}) \tag{2}$$

However, the output voltage is lower in practice with the increase of the number of stages due to the increasing threshold voltage of the nMOS transistor which is another problem. In the standard CMOS process, the bulk of nMOS must be connected to the lowest potential (ground in this design). Therefore, with the increasing number of stages, the voltage

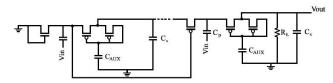

FIGURE 4. Proposed N-stage IVC based rectifier with nMOS transistors.

FIGURE 5. Proposed N-stage IVC based rectifier with pMOS transistors.

difference between the bulk and the source will increase which causes a higher threshold voltage. The relationship between the threshold voltage and the voltage difference  $V_{SB}$ is known as the body effect and it is given by:

$$V_{TH} = V_{TH0} + \gamma(\sqrt{2|\emptyset_F| + V_{SB}} - \sqrt{2\emptyset_F})$$

(3)

where  $\gamma$  is the body effect coefficient,  $\emptyset_F$  is the surface potential of MOS transistor,  $V_{TH0}$  is the threshold voltage when  $V_{SB} = 0$  and  $V_{SB}$  is the source-bulk voltage.

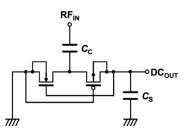

To tackle the first problem, an IVC scheme is used in the proposed design as shown in Fig. 4. It reduces  $V_{drop}$  by internally compensating for  $V_{thp}$  using an auxiliary pMOS added to the main pMOS and a capacitance  $C_{AUX}$  connected from the common gate node to ground for each stage. Therefore, the output voltage can be simplified as:

$$V_{out} = \frac{1}{2}(V_p + (V_{thp1} - V_{thp2}) + V_{AUX}) + V_p - V_{thn}$$

(4)

$$V_{out} = \frac{3}{2}V_p + \frac{1}{2}V_{AUX} + \frac{1}{2}(V_{thp1} - V_{thp2}) - V_{thn}$$

(5)

where  $V_{AUX}$  is the voltage across  $C_{AUX}$ .

And for N stages,

$$V_{out} = N(\frac{3}{2}V_p + \frac{1}{2}V_{AUX} + \frac{1}{2}(V_{thp1} - V_{thp2}) - V_{thn})$$

(6)

Equation (6) shows that this arrangement can decrease  $V_{drop}$  by compensating the threshold voltages of pMOS transistors which results in enhancing the DC extraction ability. However, there is still the threshold voltage of nMOS transistors which is the second problem, not only because it degrades the output voltage, but also because of its contribution to e body effect problem.

One way to eliminate the body effect is by using deep n-well layer with the nMOS transistors. However, this requires an adopted fabrication process and cannot be implemented in standard CMOS [4].

The proposed solution to overcome this issue is to replace all the nMOS devices, except the first stage, by pMOS transistors as shown in Fig.5. The gate of the pMOS transistor is biased by the former stage. This scheme solves two problems. The first one is the body effect problem since we can connect

FIGURE 6. Comparison of different IVC based rectifiers with the proposed schemes in two stages.

the bulk to the source in the standard CMOS process. The second one is the threshold voltage which will be compensated by the former stage bias.

Therefore, the output voltage can be simplified as:

$$V_{out} = \frac{3}{2}V_p + \frac{1}{2}V_{AUX} + \frac{1}{2}\left(V_{thp1} - V_{thp2}\right) + (V_{bias} - V_{thn})$$

(7)

And for N stages,

$$V_{out} = N\left(\frac{3}{2}V_p + \frac{1}{2}V_{AUX} + \frac{1}{2}\left(V_{thp1} - V_{thp2}\right) + \left(V_{bias} - V_{thn}\right)\right)$$

(8)

### **III. SIMULATION RESULTS**

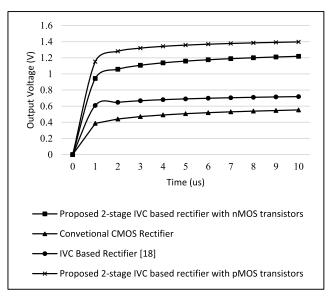

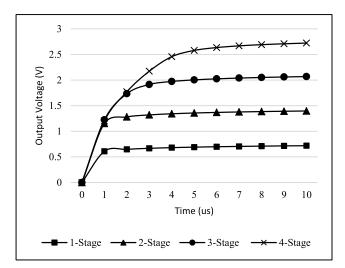

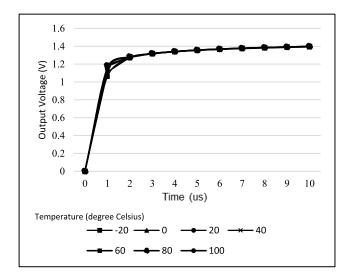

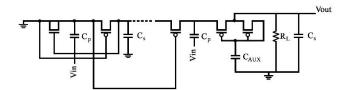

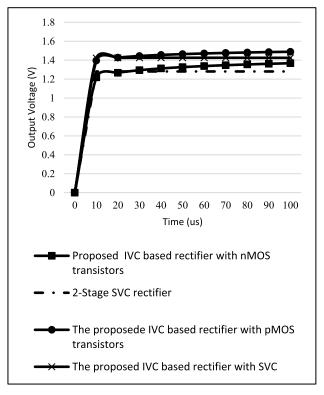

The proposed design was simulated using Tanner TSPICE in  $0.18\mu m$  TSMC CMOS technology. Drawn gate length and width of rectifier MOS transistors are  $0.4\mu m$  and  $40\mu m$ for n-MOS transistors and  $0.4\mu m$  and  $120\mu m$  for p-MOS transistors. Fig 6 demonstrates a comparison of different IVC based rectifiers with the proposed two stages schemes at input voltage 0.55V and at a frequency of 402MHz suitable for Medical Implant Communication Systems(MICS). It is clear from the plot that the proposed N stages IVC based deliver a higher voltage than the other schemes. Moreover, the proposed scheme with pMOS transistors deliver even a higher voltage than the proposed scheme with nMOS transistors which is expected from the previous equations. Fig 7 demonstrates a comparison of different stages of the proposed scheme with pMOS transistors. It is evident from the plot that more stages will produce a higher DC output voltage. The design was simulated for temperature analysis. Fig 8 is demonstrating a plot of IVC based rectifier with pMOS transistors in two stages for different temperatures. It is clear from the plot that the variation in the output voltage to the variation in the temperature is very small.

**FIGURE 7.** Comparison of different stages of the proposed IVC based rectifier using pMOS transistors.

FIGURE 9. Self-Vth-cancellation (SVC) rectifier scheme [13].

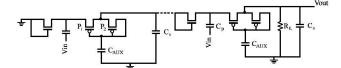

## A. IVC BASED RECTIFIER WITH SELF VTH CANCELLATION (SVC)

Self-Vth cancellation (SVC) shown in Fig. 9 is used in [12] to bias the gate by the output voltage of the rectifier. This configuration will decrease the threshold voltage of the transistor by the same amount of the output DC voltage.

FIGURE 10. The proposed IVC based rectifier with SVC.

FIGURE 11. Comparison of the proposed rectifiers with other rectifier.

Although N-stage SVC could be used to boost the output voltage, a better solution is to cascade it with IVC circuits, as proposed in Fig. 10. The circuit of Fig. 10 was simulated with RF input voltage of 200mV at a frequency of 402MHz. The simulation results shown in Fig. 11 demonstrates a comparison of the proposed rectifier with the other rectifiers. It is clear from the plot that the proposed IVC based rectifiers are superior to the recent published rectifier.

#### **IV. CONCLUSION**

Two internal threshold voltage cancellation schemes for rectifiers used in RF energy harvesting have been proposed: N-stage IVC based rectifier and IVC based rectifier with self Vth cancellation (SVC). The developed rectifiers reduce the threshold voltage, solve the body effect problem, and deliver a high rectified output voltage at an input voltage of 200mV and frequency of 402MHz.

#### REFERENCES

S. M. Noghabaei, R. L. Radin, Y. Savaria, and M. Sawan, "A highefficiency ultra-low-power CMOS rectifier for RF energy harvesting applications," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, Florence, Italy, 2018, pp. 1–4.

- [2] M. P. Aparicio, A. Bakkali, J. Pelegri-Sebastia, T. Sogorb, V. Llario, and A. Bou, "Radio frequency energy harvesting—Sources and techniques," in *Renewable Energy: Utilisation and System Integration*. Rijeka, Croatia: InTech, 2016, doi: 10.5772/61722.

- [3] X. Lu, P. Wang, D. Niyato, D. I. Kim, and Z. Han, "Wireless networks with RF energy harvesting: A contemporary survey," *IEEE Commun. Surveys Tuts.*, vol. 17, no. 2, pp. 757–789, 2nd Quart., 2015.

- [4] L. Liu, J. Mu, N. Ma, and Z. Zhu, "A hybrid threshold self-compensation rectifier for RF energy harvesting," *IEICE Electron. Express*, vol. 11, no. 23, 2014, Art. no. pp. 20141000.

- [5] Y. Chang, S. S. Chouhan, and K. Halonen, "A scheme to improve PCE of differential-drive CMOS rectifier for low RF input power," *Anal. Integr. Circuits Signal Process.*, vol. 90, no. 1, pp. 113–124, Jan. 2017.

- [6] Z. Hameed and K. Moez, "A 3.2 V –15 dBm adaptive threshold-voltage compensated RF energy harvester in 130 nm CMOS," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 4, pp. 948–956, Apr. 2015.

- [7] S. S. Chouhan and K. Halonen, "Threshold voltage compensation scheme for RF-to-DC converter used in RFID applications," *Electron. Lett.*, vol. 51, no. 12, pp. 892–894, Jun. 2015.

- [8] T. Umeda, H. Yoshida, S. Sekine, Y. Fujita, T. Suzuki, and S. Otaka, "A 950-MHz rectifier circuit for sensor network tags with 10-m distance," *IEEE J. Solid-State Circuits*, vol. 41, no. 1, pp. 35–41, Jan. 2006.

- [9] D. Khan, H. Abbasizadeh, Z. Hayat, N. Khan, and K. Yoon, "A 33.3% power efficiency RF energy harvester with -25 dBm sensitivity using threshold compensation scheme," *IDEC J. Integr. Circuits Syst*, vol. 3, no. 3, Jul. 2017.

- [10] S. S. Hashemi, M. Sawan, and Y. Savaria, "A high-efficiency low-voltage CMOS rectifier for harvesting energy in implantable devices," *IEEE Trans. Biomed. Circuits Syst.*, vol. 6, no. 4, pp. 326–335, Aug. 2012.

- [11] H.-M. Lee and M. Ghovanloo, "An integrated power-efficient active rectifier with offset-controlled high speed comparators for inductively powered applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 8, pp. 1749–1760, Aug. 2011.

- [12] K. Kotani and T. Ito, "High efficiency CMOS rectifier circuit with self-Vth-cancellation and power regulation functions for UHF RFIDs," in *Proc. IEEE Asian Solid-State Circuits Conf.*, Jeju-do, South Korea, Nov. 2007, pp. 119–122.

- [13] M. Mahmoud, A. B. Abdel-Rahman, G. A. Fahmy, A. Aliam, H. Jia, and R. K. Pokharel, "Dynamic threshold compensated, low voltage CMOS energy harvesting rectifier for UHF applications," in *Proc. IEEE 59th Int. Midwest Symp. Circuits Syst. (MWSCAS)*, Abu Dhabi, United Arab Emirates, Oct. 2016, pp. 16–19.

- [14] A. Shameli, A. Safarian, A. Rofougaran, M. Rofougaran, and F. De Flaviis, "Power harvester design for passive UHF RFID tag using a voltage boosting technique," *IEEE Trans. Microw. Theory Techn.*, vol. 55, no. 6, pp. 1089–1096, Jun. 2007.

- [15] H. Dai, Y. Lu, M.-K. Law, S.-W. Sin, U. Seng-Pan, and R. P. Martins, "A review and design of the on-chip rectifiers for RF energy harvesting," in *Proc. IEEE Int. Wireless Symp. (IWS)*, Shenzhen, China, Mar. 2015, pp. 1–4.

- [16] N. T. Tasneem, S. R. Suri, and I. Mahbub, "A low-power CMOS voltage boosting rectifier for wireless power transfer applications," in *Proc. Texas Symp. Wireless Microw. Circuits Syst. (WMCS)*, Waco, TX, USA, Apr. 2018, pp. 1–4.

- [17] E. M. Ali, N. Z. Yahya, N. Perumal, and M. A. Zakariya, "Design of RF to DC rectifier at GSM band for energy harvesting applications," *PLATFORM J. Eng.*, *Sci. Soc.*, vol. 10, no. 2, pp. 15–22, Dec. 2014.

- [18] S. S. Chouhan and K. Halonen, "Internal Vth cancellation scheme for RF to DC rectifiers used in RF energy harvesting," in *Proc. 21st IEEE Int. Conf. Electron., Circuits Syst. (ICECS)*, Marseille, France, Dec. 2014, pp. 235–238.

**MUNIR A. AL-ABSI** (Senior Member, IEEE) received the B.Sc. and M.Sc. degrees from the King Fahd University of Petroleum and Minerals (KFUPM), Dhahran, Saudi Arabia, in 1984 and 1987, respectively, and the Ph.D. degree from UMIST, U.K., in 2001. He is currently an Associate Professor with the EE Department, KFUPM, teaching electronics and instrumentation courses. His research interests include analog computational circuits using MOS in weak inversion, biomedical circuits, and analog signal processing.

**SAMI R. AL-BATATI** received the B.Sc. degree from the King Fahd University of Petroleum and Minerals (KFUPM), Dhahran, Saudi Arabia, where he is currently pursuing the master's degree with the Electrical Engineering Department. His research interest includes analog circuits design using CMOS technology.

...