Received January 30, 2020, accepted February 26, 2020, date of publication March 2, 2020, date of current version March 13, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.2977754

# A Novel IUPQC for Multi-Feeder Systems Using Multilevel Converters With Grid Integration of Hybrid Renewable Energy System

# T. SURYA PRAKASH<sup>®</sup> (Member, IEEE), P. SATISH KUMAR<sup>®</sup>, (Senior Member, IEEE), AND R. P. S. CHANDRASENA<sup>3</sup>

Department of Electrical and Electronics Engineering, G. Narayanamma Institute of Technology and Science for Women (GNITS), Hyderabad 500104, India

Corresponding author: T. Surya Prakash (thota.surya@gmail.com)

This work was supported by the Department of Science and Technology (DST), Government of India, and the Ministry of Science, Technology and Research (MSTR), Government of the Democratic Socialist Republic of Sri Lanka under Indo-Sri Lanka Joint Research Project at the Department of Electrical Engineering, University College of Engineering, Osmania University, India, and the Department of Electrical and Information Engineering, Faculty of Engineering, University of Ruhuna, Galle, Sri Lanka under Grant DST/INT/SL/P-18/2016.

**ABSTRACT** This paper presents a novel topology of interline unified power quality conditioner (IUPQC) for multi-bus/multi-feeder systems, capable of compensating both voltage and current imperfections simultaneously for power quality improvement. In this system, four voltage-source converters (VSC) with multilevel configuration are considered and space vector pulse width modulation is used in hexagonal coordinate system to reduce the complexity in generating switching pulses. In the proposed IUPQC, all converters share a common dc-link capacitor. Hence, power can be transferred from healthy feeder to adjacent feeders for compensation of sag/swell and current/voltage harmonics. This IUPQC is implemented between two feeders with hybrid renewable energy system as one of the feeders. The performance of the proposed system for various power quality problems is analyzed and presented using MATALB/SIMULINK.

**INDEX TERMS** Grid integration, multi-feeder systems, multi-level converters, power quality improvement, renewable energy systems.

#### I. INTRODUCTION

In the era of liberalization, the privatization of world electric energy market brought in a new level of competition in the energy supply business. The increasing use of sophisticated equipment for domestic and industrial applications, has increased its vulnerability to power quality problems.

In order to mitigate the power quality disturbances and to give customized solutions [1]–[3], newer devices based on power electronics called "custom power devices", have been developed. Modern solutions for load related problems and imperfections in supply voltage include unified power quality conditioner (UPQC) [4]. It is obtained by combining shunt compensator and series compensator to provide a solution for multiple power quality problems. The shunt compensator improves the current profile and the series compensator improves the voltage profile.

The associate editor coordinating the review of this manuscript and approving it for publication was Pietro Varilone.

Based on the idea of taking power from adjacent healthy feeder to compensate the problems in the existing feeder, multi-feeder custom power devices have evolved. When compared to single feeder custom power devices, superior performance is assured with these devices. Some of the interline custom power devices include interline dynamic voltage restorer (IDVR) [7], [8], interline voltage controller (IVOLCON) [9], [10], IUPQC with two VSCs [11].

In secondary selective systems the customer load is generally divided between two feeders and supplied from two different substations. In this regard, it is considered that the effect of voltage variation in a feeder on the other feeder is negligible. Hence, two feeders are considered as two isolated sources based on the fault level at point of common coupling. In IUPQC [11] with two VSCs, one converter is connected in shunt with one feeder and another converter in series with another feeder. In this configuration, current profile of the first feeder and the voltage profile of the second feeder are improved. In this connection, many other possibilities are explored by the addition of third converter [12]–[16] with

<sup>&</sup>lt;sup>2</sup>Department of Electrical Engineering, University College of Engineering (UCE), Osmania University (OU), Hyderabad 500007, India

<sup>&</sup>lt;sup>3</sup>Department of Electrical and Information Engineering, Faculty of Engineering, University of Ruhuna (UR), Galle 80000, Sri Lanka

different nomenclature such as UPQS [13], DS-UniCon [12] and MC-UPQC with 3 VSCs [16].

A new topology of unified power-quality conditioning system, IUPQC with four VSCs is proposed in this paper. This IUPQC is able to improve voltage and current profiles in multi-bus/multi-feeder systems simultaneously. The proposed IUPQC is implemented between grid and the HRES [17].

#### **II. PROPOSED SYSTEM**

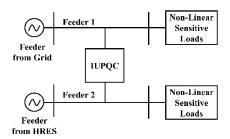

The proposed IUPQC system is connected between two feeders, in which HRES is considered as one feeder and another feeder from grid as shown in Fig.1. The HRES consists of solar, wind energy system supported by battery storage system.

FIGURE 1. General block diagram of proposed system.

### A. INTERLINE UNIFIED POWER QUALITY CONDITIONER

#### 1) SYSTEM DESCRIPTION

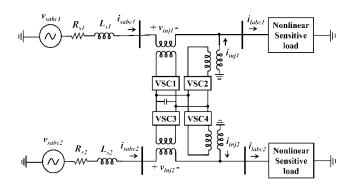

In this IUPQC configuration, two shunt VSCs and two series VSCs exist. This system can be connected between two adjacent feeders to compensate the imperfections in both source voltage and load current on both the feeders. To have the power transfer capability between the feeders for the compensation of sag/swell and voltage/current harmonics, all converters are connected back to back with a common dc-link capacitor as shown in Fig.2.

FIGURE 2. Single line diagram of four converter topology for multi-feeder system.

In the proposed configuration, two VSCs are connected in series and two VSCs are connected in parallel with loads at feeders 1 and 2. It is capable of regulating load voltages to

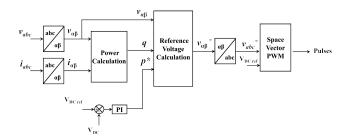

FIGURE 3. Shunt compensation control diagram.

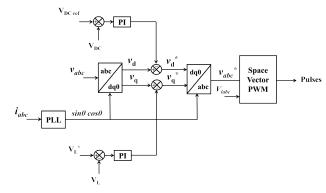

FIGURE 4. Series compensation control diagram.

FIGURE 5. Control diagram for SVPWM implementation.

FIGURE 6. Space vector diagram of three-level inverter.

protect the loads from voltage disturbances in the system. Also, compensates for the reactive and harmonic components of nonlinear load currents ( $i_{l1}$  and  $i_{l2}$ ). Here, series VSCs are operated so as to control voltage while the shunt VSCs are operated to control current in both the feeders.

FIGURE 7. Schematic diagram of HRES.

**TABLE 1.** Equivalent components in first sector.

| gh components                               | Sector | Equivalent Components                              |

|---------------------------------------------|--------|----------------------------------------------------|

| $V_g > 0 \& V_h > = 0$                      | 1      | $\mathbf{m}_1 = V_g$ , $\mathbf{m}_2 = V_h$        |

| $V_g < 0 \& V_h > = 0 \& (V_g + V_h) > = 0$ | 2      | $\mathbf{m}_1 = V_g$ , $\mathbf{m}_2 = V_g + V_h$  |

| $V_g < 0 \& V_h > = 0 \& (V_g + V_h) < 0$   | 3      | $\mathbf{m}_1 = V_h$ , $\mathbf{m}_2 = -V_g - V_h$ |

| $V_g < 0 \& V_h < 0$                        | 4      | $\mathbf{m}_1 = -V_h$ , $\mathbf{m}_2 = -V_g$      |

| $V_g > 0 \& V_h < 0 \& (V_g + V_h) < 0$     | 5      | $\mathbf{m}_1 = -V_g - V_h,  \mathbf{m}_2 = V_g$   |

| $V_g >= 0 \& V_h < 0 \& (V_g + V_h) > = 0$  | 6      | $\mathbf{m}_1 = V_g + V_h,  \mathbf{m}_2 = V_h$    |

FIGURE 8. Solar irradiance and wind speed levels.

Multilevel converters are used for the VSCs in the proposed system. Three level diode-clamped three phase converters are used. Many PWM techniques such as sinusoidal triangular comparison technique, selective harmonic elimination & hysteresis techniques, and space vector pulse width modulation (SVPWM) [18] are available for the multilevel converters. Based on the advantage of reducing common mode and

**TABLE 2.** Parameter of HRES.

| Equipment                  | Parameter                              | Value                |

|----------------------------|----------------------------------------|----------------------|

| PMSG                       | Nominal Power                          | 750 kW               |

|                            | Nominal Voltage                        | 575 V                |

|                            | Rated Speed                            | 25 rpm               |

|                            | Stator Resistance R <sub>s</sub>       | $0.01~\Omega$        |

|                            | Stator Self-Inductance, L <sub>S</sub> | 7.79 mH              |

|                            | Pole pairs, p                          | 42                   |

|                            | Permanent Magnetic Flux, $\phi_a$      | 7.35 Nm/A            |

| PV Arrays                  | Total Maximum Power                    | 600 kW               |

|                            | No. of arrays in parallel              | 3                    |

|                            | No. of Parallel Strings per array      | 64                   |

|                            | No. of Series Strings per array        | 10                   |

| PV<br>Module               | Nominal Power                          | 315 W                |

|                            | Open Circuit Voltage                   | 64.6 V               |

|                            | Maximum Power Point Voltage            | 54.7 V               |

|                            | Short-Circuit Current                  | 6.14 A               |

|                            | Current at MPP                         | 5.76 A               |

| Battery                    | Voltage                                | 48 V                 |

|                            | Capacity                               | 58.5 Ah              |

|                            | No. of Batteries in series             | 12                   |

| DC Bus<br>and RL<br>Filter | DC-bus voltage reference               | 1000 V               |

|                            | Filter resistance                      | $1~\mathrm{m}\Omega$ |

|                            | Filter inductance                      | 45 μΗ                |

balancing DC link capacitor voltage, SVPWM is preferred for multilevel inverters in this work.

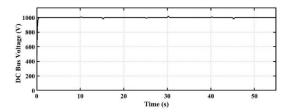

FIGURE 9. DC Bus voltage.

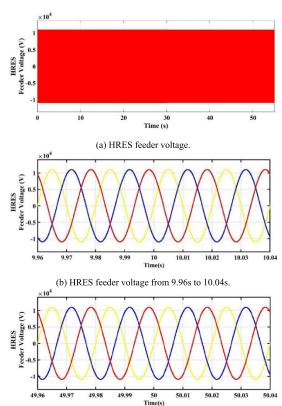

FIGURE 10. HRES feeder voltage.

#### 2) CONTROL STRATEGY

Independent control of all VSCs is adopted in this configuration. Shunt VSCs compensate reactive and harmonic components of the nonlinear loads in addition to capacitor voltage regulation. Series VSCs mitigate voltage distortions like sag/swell, harmonics and interruptions. Series VSCs control is based on SRF (synchronous reference frame) theory and PQ theory is used for instantaneous power calculation in order to control the shunt VSCs.

(c) HRES feeder voltage from 49.96s to 50.04s.

The shunt VSC control for each feeder is shown in Fig 3. power reference values are calculated from load voltages and load currents by using abc to  $\alpha\beta$  transformation. To achieve synchronization with supply, desired voltage reference values are generated with the compensated power references. The voltage references in addition to DC reference voltage are given to SVPWM controller to generate the gating pulses to the shunt VSC.

The series VSCs control diagram is shown in Fig.4. The series VSC is operated such that the injected voltages

FIGURE 11. Voltages and currents at feeder 1.

$(V_{inja}, V_{injb})$  and  $V_{injc})$  compensate the distortions in the supply voltages  $(V_{sa}, V_{sb})$  and  $V_{sc}$ . This ensures perfectly sinusoidal voltages at PCC  $(V_{la}, V_{lb})$  and  $V_{lc}$  with the required amplitude. In SRF theory, using Park's transformation, source voltages are converted to rotating reference frame to estimate the reference signal. The DC bus voltage and load voltages are controlled by two PI controllers. The SVPWM generator produces the gating pulses to the series VSCs based on the actual and reference values of load voltages.

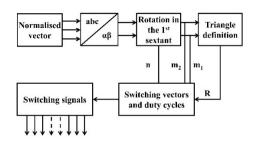

Implementation of SVPWM involves complex computations. Control diagram for SVPWM is shown in Fig.5. Based on the refrence voltage, the sector in which the voltage vector lies is identified.

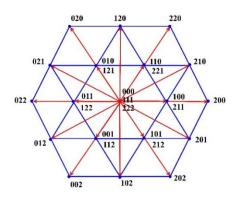

Sector division with corresponding voltage spaces are represented with switching positions in Fig.6. With the sector identification, corresponding duty cycles are calculated and sequence of voltage states is generated.

To determine the reference voltage vector location, hexagonal (g-h space) coordinate system is used, as it is complex with cartesian coordinate system. Sectors and their equivalent components in g-h space are mentioned in Table.1.

# B. HYBRID RENEWABLE ENERGY SYSTEM

The HRES consists of a 750kW permanent magnet synchronous generator (PMSG) based wind turbine, a 600kW

FIGURE 12. Voltages and currents at feeder 1.

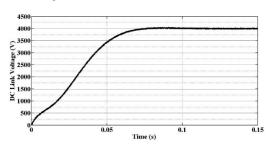

FIGURE 13. DC link voltage.

photovoltaic system comprising of four sets of arrays connected in parallel with each array consisting of 10 panels connected in series and 64 panels connected in parallel, and a battery energy storage system (BESS) consisting of 12 lithium-ion batteries connected in series. This HRES is designed to maintain constant voltage at the dc link regardless of the variations in the solar irradiance level and wind speed. This is achieved by appropriate control of BESS. The detailed HRES parameters are shown in Table 2.

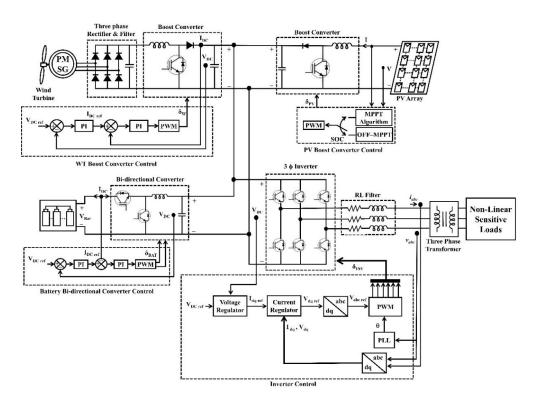

The detailed schematic of the HRES system is shown in Fig.7. The PMSG based wind turbine output is rectified and the voltage is boosted to 1kV with the help of a boost converter. The wind turbine boost controller uses a simple PI controller. The solar PV array operates in two modes of

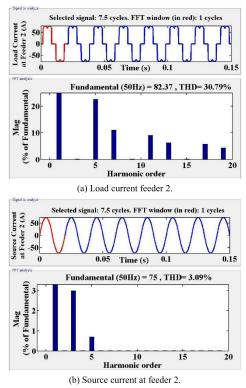

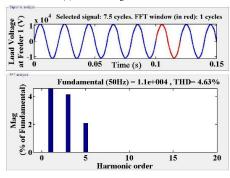

FIGURE 14. FFT analysis at feeder 1.

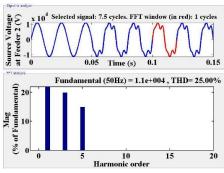

FIGURE 15. FFT analysis at feeder 2.

operation; MPPT mode and off-MPPT mode. Depending on the state of charge (SoC) of the battery, the PV mode of operation is switched to either the P&O based maximum power point tracking mode or off-MPPT mode inorder to mainatin the system power balance.

FIGURE 16. Voltages and currents at feeder 1.

FIGURE 17. Voltages and currents at feeder 2.

FIGURE 18. DC link voltage.

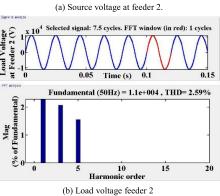

(b) Load voltage feeder 1.

FIGURE 19. FFT analysis at feeder 1.

The BESS consists of batteries connected in series and a bi-directional buck boost converter. When the power generated from RES is insufficient to meet the load demand, the BESS operates in boost mode and delivers power. When there is excess power generation from RES, the BESS operates in buck mode and receives power and thus charging the batteries, also during this condition, when the SoC of the battery reaches its maximum limit, then in order to avoid damage to the batteries, the PV boost converter operates in off-MPPT mode. The bidirectional converter uses a PI based controller.

The HRES consists of the PMSG based WT, PV array and the BESS all connected to a dc bus. A three-phase inverter is connected to this dc bus and with the help of an inverter control algorithm, the inverter provides a constant output voltage. The inverter output is filtered and stepped up to 11kV by the step-up power transformer and supplies power to the load.

FIGURE 20. FFT analysis at feeder 2.

# **III. RESULTS AND DISCUSSIONS**

The performance of the proposed system is analyzed and presented using MATALB/SIMULINK. Firstly, the performance of HRES is presented by considering various combinations of renewable energy inputs. Later, the performance evaluation of IUPQC for grid integration of HRES is discussed.

### A. HRES PERFORMANCE

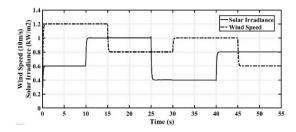

The HRES is designed to maintain a constant voltage regardless of the variations in the wind and solar inputs with the help of BESS. The HRES is designed to provide the performance of an actual grid. As shown in Fig. 8., the solar irradiance and wind speeds are varied for different combinations of wind and solar conditions in order to test the performance of the HRES.

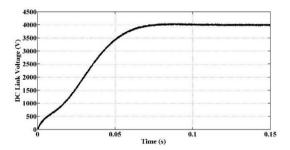

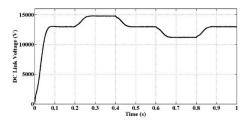

The dc bus voltage is maintained for 1kV as shown in Fig. 9, even for the different variations of the wind speed and solar irradiance, the voltage is maintained constant at the dc bus, this is achieved by the BEES.

The voltage at the output of the transformer secondary is shown in Fig. 10 and it is remains constant at 11kV since the dc bus voltage is maintained constant. Thus, the HRES system provides a stable constant voltage and frequency which can be supplied to the load.

# **B. IUPQC PERFORMANCE**

The proposed IUPQC topology for two feeder System and its control schemes have been tested through extensive case studies. The power system with two feeders of three-phase, three-wire 11kV, 50-Hz utilities is considered. Results are

FIGURE 21. Voltages and currents at feeder 1.

presented, and the performance of IUPQC is discussed. Different power quality problems namely, current harmonics due to nonlinear loads and supply voltage imperfections like sag/swell and voltage harmonics, are considered as different cases and the performance of IUPQC is presented.

# 1) CURRENT HARMONICS

The feeders 1 and 2 are supplying resistive loads 100ohms and 200 ohms respectively through diode bridge rectifier to have nonlinearities in the load.

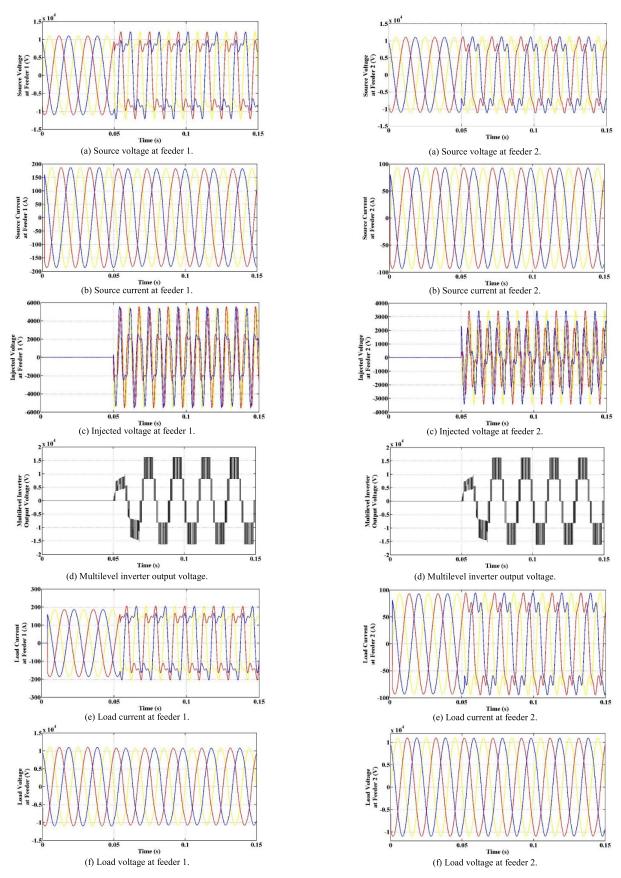

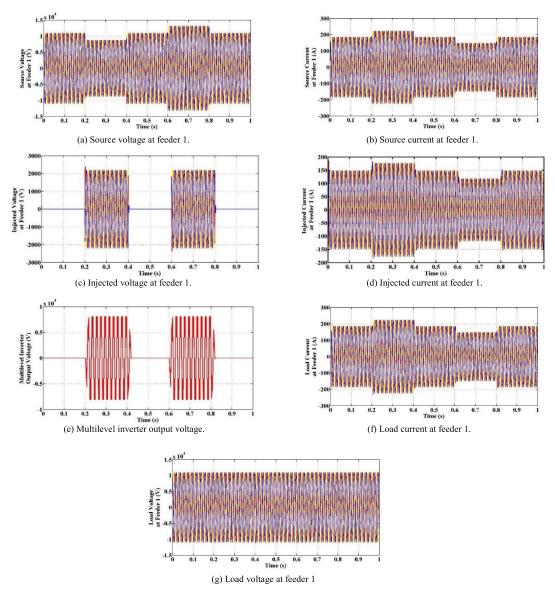

It can be clearly seen in Fig. 11 and Fig. 12 that the load currents are containing harmonic content due to the nonlinear loads and source currents are almost sinusoidal.

The DC link capacitor voltage is presented in Fig.13, showing good dynamic response of the system.

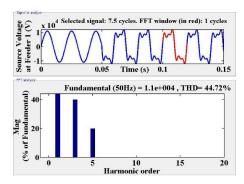

From load current to source current, THD of first feeder is reduceed from 30.84% to 3.08% and that of second feeder is reduced from 30.79% to 3.09%. FFT analysis with THD values are shown in Fig.14 and Fig. 15.

# 2) VOLTAGE HARMONICS

To consider supply voltage imperfections, 3rd and 5th harmonics are introduced intentionally in both the feeders. First feeder voltage with 15% 3rd and 20% 5th order harmonics, second feeder with 15% 3rd and 15% 5th order harmonics are considered from t=0.05s to supply the loads.

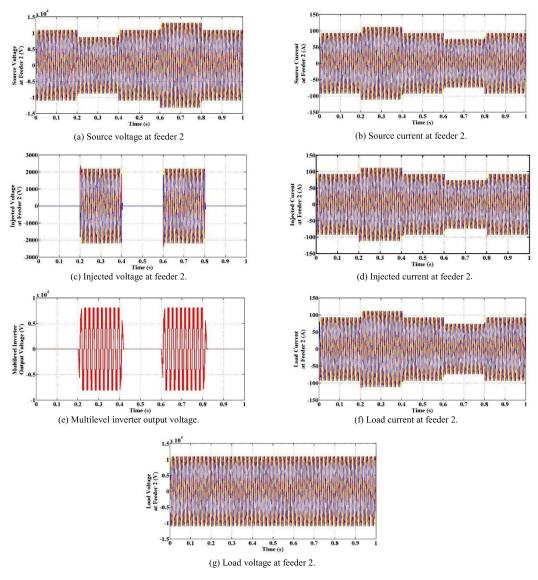

Source voltages, load voltages, source currents, load currents, injected voltages and multilevel converter voltages of both the feeders are shown in Fig. 16 and Fig. 17.

Distorted voltages at the source side of both the feeders are compensated at the load side. Good dynamic response of

FIGURE 22. Voltages and currents at feeder 2.

FIGURE 23. DC link voltage.

the system can be observed by the DC link capacitor voltage in Fig.18.

FFT analysis with THD values are shown in Fig. 19 and Fig. 20. It is observed that THD of Feeder 1 is improved from 44.72% to 4.63% and that of Feeder 2 is improved from 25% to 2.59%.

# 3) SAG AND SWELL

Sag and swell conditions are introduced in the source voltages of both the feeders simultaneously. Considered feeder voltages contain 20% sag and swell between 0.2s to 0.4s and 0.6s to 0.8s respectively. First feeder supplies RL of  $50\Omega$  and 100mH and second feeder supplies RL load of  $100\Omega$  and 200mH. Source voltages, source currents, load voltages, load currents, injected voltages and multilevel converter voltages of both the feeders are shown in Fig. 21 and Fig. 22.

It can be observed that source voltages are compensated at the loads of both the feeders. DC link capacitor voltage can be observed from Fig. 23.

## **IV. CONCLUSION**

The hybrid renewable energy system is developed and implemented for different variations in the supply and load demand.

The results show that proposed IUPQC can be satisfactorily implemented for grid integration of HRES. IUPQC is capable of regulating load voltages to protect the loads from voltage disturbances in the system. Also, compensates for the reactive and harmonic components of nonlinear load currents. Power can be transferred from healthy feeder to adjacent feeders for compensation of sag/swell and current/voltage harmonics. It can be inferred that IUPQC can be a better solution to multiple power quality problems in multi-feeder systems.

#### **REFERENCES**

- M. Rastogi, R. Naik, and N. Mohan, "A comparative evaluation of harmonic reduction techniques in three-phase utility interface of power electronic loads," in *Proc. IEEE Ind. Appl. Conf. 28th IAS Annu. Meeting*, Toronto, ON, Canada, Oct. 1993, pp. 971–978.

- [2] H. Akagi, "New trends in active filters for power conditioning," *IEEE Trans. Ind. Appl.*, vol. 32, no. 6, pp. 1312–1322, Nov/Dec. 1996.

- [3] F. Z. Peng, "Application issues of active power filters," *IEEE Ind. Appl. Mag.*, vol. 4, no. 5, pp. 21–30, Sep./Oct. 1998.

- [4] H. Fujita and H. Akagi, "The unified power quality conditioner: The integration of series- and shunt-active filters," *IEEE Trans. Power Electron.*, vol. 13, no. 2, pp. 315–322, Mar. 1998.

- [5] J. W. Dixon, G. Venegas, and L. A. Moran, "A series active power filter based on a sinusoidal current-controlled voltage-source inverter," *IEEE Trans. Ind. Electron.*, vol. 44, no. 5, pp. 612–620, Oct. 1997.

- [6] V. Khadkikar, "Enhancing electric power quality using UPQC: A comprehensive overview," *IEEE Trans. Power Electron.*, vol. 27, no. 5, pp. 2284–2297, May 2012.

- [7] D. Vilathgamuwa, H. M. Wijekoon, and S. S. Choi, "A novel technique to compensate voltage sags in multiline distribution system—The interline dynamic voltage restorer," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1603–1611, Oct. 2006.

- [8] D. M. Vilathgamuwa, H. M. Wijekoon, and S. S. Choi, "Interline dynamic voltage restorer: A novel and economical approach for multiline power quality compensation," *IEEE Trans. Ind. Appl.*, vol. 40, no. 6, pp. 1678–1685, Nov. 2004.

- [9] A. K. Jindal, A. Ghosh, A. Joshi, and A. M. Gole, "Voltage regulation in parallel distribution feeders using IVOLCON," in *Proc. IEEE Power Energy Soc. Gen. Meeting-Convers. Del. Electr. Energy 21st Century*, Jul. 2008, pp. 1–8.

- [10] A. K. Jindal, A. Ghosh, and A. Joshi, "Power quality improvement using interline voltage controller," *IET Gener., Transmiss. Distribution*, vol. 1, no. 2, p. 287, 2007.

- [11] A. K. Jindal, A. Ghosh, and A. Joshi, "Interline unified power quality conditioner," *IEEE Trans. Power Del.*, vol. 22, no. 1, pp. 364–372, Jan. 2007.

- [12] M.-C. Wong, C.-J. Zhan, Y.-D. Han, and L.-B. Zhao, "A unified approach for distribution system conditioning: Distribution system unified conditioner (DS-UniCon)," in *Proc. Power Eng. Soc. Winter Meeting*, Jan. 2000, pp. 2757–2762.

- [13] A. Rufer, V. Katic, and D. Graovac, "Power quality compensation using universal power quality conditioning system," *IEEE Power Eng. Rev.*, vol. 20, no. 12, pp. 58–60, Dec. 2000.

- [14] P. Li, Q. Bai, B. Zhao, and Y. Yang, "Power quality control center and its control method," in *Proc. IEEE/PES Transmiss. Distrib. Conf. Expo.*, Asia and Pacific, Aug. 2005, pp. 1–6.

- [15] P. Li, Q. Bai, and G. Li, "Coordinated control strategy for UPQC and its verification," in *Proc. IEEE Power Eng. Soc. Gen. Meeting*, Jun. 2006, pp. 1–8.

- [16] H. R. Mohammadi, A. Y. Varjani, and H. Mokhtari, "Multiconverter unified power-quality conditioning system: MC-UPQC," *IEEE Trans. Power Del.*, vol. 24, no. 3, pp. 1679–1686, Jul. 2009.

- [17] P. S. Kumar, R. P. S. Chandrasena, V. Ramu, G. N. Srinivas, and K. V. S. M. Babu, "Energy management system for small scale hybrid wind solar battery based microgrid," *IEEE Access*, vol. 8, pp. 8336–8345, 2020.

- [18] N. Susheela, P. S. Kumar, and S. K. Sharma, "Generalized algorithm of reverse mapping based SVPWM strategy for diode-clamped multilevel inverters," *IEEE Trans. Ind. Appl.*, vol. 54, no. 3, pp. 2425–2437, May 2018.

**T. SURYA PRAKASH** (Member, IEEE) received the B.Tech. degree in EEE from Nagarjuna University, and the M.E. degree in industrial drives and control from Osmania University, India, where he is currently pursuing the Ph.D. degree. He is also working as an Assistant Professor at the Department of Electrical and Electronics Engineering, G. Narayanamma Institute of Technology and Science for Women (GNITS), Hyderabad. He has 16 years of teaching and research experience.

He has published research articles in two international journals and three international conferences. He has filed one patent in the area of power quality. He visited Tokyo, Japan, to present his research paper in international conference. His research areas are power quality, renewable energy sources, power electronics, grid integration of microgrid, and multilevel inverters.

**P. SATISH KUMAR** (Senior Member, IEEE) received the B.Tech. degree in EEE, the M.Tech. degree in power electronics, and the Ph.D. degree in multilevel inverters from JNTUH, in 2011.

He is currently an Associate Professor with the Department of Electrical Engineering, University College of Engineering, Osmania University, Hyderabad, India. He has more than 23 years of teaching and research experience. His four Ph.D. students has been awarded under his supervision

and at present guiding eight Ph.D. scholars in the area of power electronics. He visited USA, France, Switzerland, Japan, Singapore, Hong Kong, Bangkok, and Sri Lanka to present his research papers in various international conferences. He has published 93 research articles in international journals and has presented 32 papers in international conferences, and filed three patents in the area of multilevel inverters. He has authored one text book entitled Pulse Width Modulation: Analysis and Performance in Multilevel Inverters. His areas of interests are power electronics, drives, power converters, multilevel inverters, special machines, and renewable energy sources. He is a Fellow of IEI, a member ISTE, and an editorial member of various international journals. As the Principal Investigator, he completed two Major Research Projects funded by UGC and SERB, Government of India. He is also implementing Indo-Sri Lanka joint research project sponsored by DST, Government of India. He received the Best Teacher Award from the State Government of Telangana, in September 2014, the Fast Track Scheme for Young Scientist Award from SERB, in 2013, the Award for Research Excellence, in 2014, and the Global Teacher Role Model Award, in 2015.

**R. P. S. CHANDRASENA** received the B.Sc. (Eng.) degree from the Faculty of Engineering, University of Peradeniya, Sri Lanka, in 1998, the M.Eng. degree from the Faculty of Engineering, University of Moratuwa, Sri Lanka, in 2004, the M.Phil. degree in electrical engineering from the Faculty of Engineering, University of Peradeniya, in 2011, and the Ph.D. degree in converter control in microgrid from the Faculty of Engineering, Curtin University, WA, in 2015.

He is currently a Senior Lecturer with the Department of Electrical and Information Engineering, Faculty of Engineering, University of Ruhuna, Sri Lanka. He has more than 15 years of experience as an Academic Researcher. He has published more than 15 publications in international journals and conferences. He is also supervising one M.Phil. student and he has taught undergraduate courses, such as electrical machines, power systems, power electronics, and so on. He has coauthored a book chapter in *Renewable Energy Integration Challenges and Solutions* (Springer Press, Singapore, in 2014). His areas of interest are power electronic converter control, microgrids, and renewable energy generation. He received the IET Premium Award 2015. He received a research grant worth around 5 million rupees for a joint project proposal submitted to the Ministry of Science, Technology and Research, Sri Lanka, under the Indo-Sri Lanka Joint Research Program.