Received January 12, 2020, accepted January 21, 2020, date of publication January 30, 2020, date of current version February 6, 2020. Digital Object Identifier 10.1109/ACCESS.2020.2970502

## A Novel Planar Architecture for Heterojunction TFETs With Improved Performance and Its Digital Application as an Inverter

# SHIZHENG YANG<sup>®1</sup>, HONGLIANG LV<sup>®1</sup>, (Member, IEEE), BIN LU<sup>®2</sup>, SILU YAN<sup>®1</sup>, AND YUMING ZHANG<sup>®1</sup>, (Senior Member, IEEE)

<sup>1</sup>State Key Discipline Laboratory of Wide Band Gap Semiconductor Technology, School of Microelectronics, Xidian University, Xi'an 710071, China <sup>2</sup>School of Physics and Information Engineering, Shanxi Normal University, Linfen 041004, China

Corresponding authors: Hongliang Lv (hllv@mail.xidian.edu.cn) and Bin Lu (lubinsxnu@sina.cn)

This work was supported in part by the National Natural Science Foundation of China under Grant 90304190002, and in part by the Applied Basic Research Plan of Shanxi Province under Grant 201901D211400.

**ABSTRACT** A novel planar architecture is proposed for tunnel field-effect transistors (TFETs). The advantages of this architecture are exhibited, taking the InAs/Si TFET as an example, and the effects of different device parameters are analyzed in detail. Owing to the gate field being parallel to the tunneling interface, the gate control is enhanced, and a better electrical performance is obtained. Moreover, different from a conventional TFET, in which the effective tunneling area and current can hardly be modulated by the gate length, in our proposed device, the effective tunneling area and current can be adjusted depending on the actual requirements of circuit design, which increases the flexibility of TFET-based circuit design. In addition, the device architecture can also be extended to other materials, such as Ge/Si and GaSb/InAs, and thus be used for both n-type and p-type devices. The results show that the complementary digital inverter structure with InAs/Si as the n-type TFET and Ge/Si as the p-type TFET would be helpful for future ultralow power applications. This proposed structure without any complicated fabrication steps shows better compatibility with CMOS technology compared to other TFETs with heterojunction and structural innovations presented in theoretical works.

**INDEX TERMS** Tunnel field-effect transistor, band-to-band tunneling, InAs/Si heterojunction, complementary TFET inverters.

#### I. INTRODUCTION

TFETs based on the band-to-band tunneling (BTBT) mechanism can break the 60 mV/decade thermal limitation of the subthreshold swing (SS) and offer steep switching under further scaled supply voltage ( $V_{DD}$ ), becoming promising for future low power applications [1]–[4]. TFETs have been intensively investigated in recent years and are expected to be seen in semiconductor products after 2022 [5], [6].

Benefiting from the highly mature CMOS technology, many Si TFETs are experimentally reported to break the 60 mV/decade limitation [7]–[9]. However, owing to the low BTBT probability arising from the large and indirect bandgap, the silicon TFET suffers from an unacceptably low on-state current (I<sub>ON</sub>), which is even lower than the demand

The associate editor coordinating the review of this manuscript and approving it for publication was Rahul A. Trivedi<sup>D</sup>.

reported by the International Technology Roadmap for Semiconductors (ITRS) [10]. This low on-state current leads to a large switching delay ( $CV_{DD}/I_{ON}$ ), and therefore, practical application of the silicon TFET is hindered.

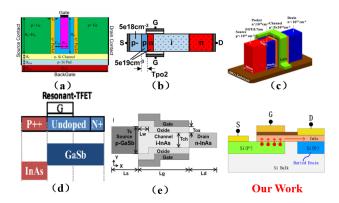

To resolve this issue, various design improvements have been proposed [11]–[18]. In [11], the Ge/Si heterojunction is proposed, and a U-shaped gate with an n+ pocket is introduced to enhance the tunneling efficiency. Moreover, the U-shaped gate facilitates implementation of a smaller device area. In [12], a low doped pocket is added into the source of staggered heterostructure p-n-i-n TFETs to fully utilize the strain-induced increase in the on-state current. In [13], a uniaxial tensile stress is incorporated into the GeSn n-channel fin TFET to boost the device performance, and a more pronounced I<sub>ON</sub> is obtained. In [14], a new resonant-TFET (R-TFET) is proposed, and a 100x current advantage over the MOSFET is obtained. In [15], a scalable GaSb/InAs TFET with nonuniform body thickness is introduced, and a high  $I_{ON}$  of approximately 284 A/m is exhibited. All of these studies are excellent works, and the device performance is largely enhanced by different structural innovations and heterojunctions with much lower tunneling barriers compared with that of the homojunction. However, the fabrication steps required for the novel structures are very complicated and difficult to incorporate into the current CMOS technology [19]. Fabrication compatibility with the conventional platform is extremely significant not only for the practical application of TFETs in the future but also for the TFET-CMOS hybrid design [20], [21].

Another issue that also contributes to the small tunneling current is the small tunneling area limited to the narrow channel/oxide interface near the source side. The limited and concentrated tunneling area also results in almost unchanged tunneling current with channel length [22], [23]. This phenomenon makes modulating the device driving capability to meet the actual needs during the circuit design process difficult.

In addition to the single device performance, that of the complementary TFET inverter, in which both the N-TFET and the P-TFET should be properly designed for complementary performance, is another issue. To boost the on-state current, generally, III-V materials are adopted for n-type TFETs, and group IV materials, such as Ge or GeSi, are used for p-type TFETs [24]. However, the proposed novel structures are usually only suitable for n-type or p-type TFETs due to the lack of material universality, and the two types are usually investigated separately. Thus, the proposed structure usually focuses on only one type, resulting in degraded p-type or n-type performance and accordingly unsatisfactory complementary behavior.

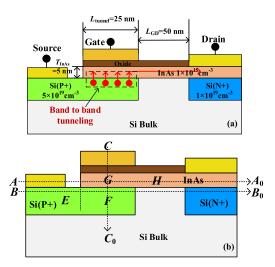

**FIGURE 1.** (a) Schematic cross-sectional view of the proposal planar TFET structure with an InAs/Si tunneling heterojunction, and (b) region and cutline markers for convenience of subsequent description.

In this paper, a novel architecture is proposed for heterojunction TFETs, as shown in Fig. 1(a), in which the InAs/Si tunneling heterojunction is taken as an example. Compared with the existing methods, our novel structure exhibits many advantages. First, the gate control of the tunneling process is enhanced because the gate field is aligned with the tunneling direction, and much steeper transfer characteristics with a minimum SS of approximately a few millivolts per decade are obtained. Second, the effective tunneling area is enlarged, which boosts ION. Moreover, the effective tunneling area and I<sub>ON</sub> can be modulated by the gate length to meet the actual requirements of circuit design, which is of great significance for improving the circuit design flexibility. Third, the structure is the simplest compared with other works and exhibits better compatibility with CMOS technology without any complicated fabrication steps while allowing the current enhancement due to a heterojunction. Finally, the proposed structure shows better material universality. Although the InAs/Si heterojunction is taken as an example, this structure can be extended to other materials. Therefore, it is suitable for both n-type and p-type devices, which is of significance for complementary digital applications.

This article is arranged as follows: Section II presents the device structure and some important simulation details. In Section III, the effects of different device parameters are studied, and the optimized device performance is compared with that of novel TFET structures presented in other theoretical works. The performance of the complementary TFET inverter based on the proposed structure is studied in Section IV. The conclusions are highlighted in Section V.

#### **II. DEVICE STRUCTURE AND NUMERICAL SIMULATION**

In this paper, the proposed structure is introduced, taking the InAs/Si TFET as an example considering its very low tunneling mass. However, this does not mean that the structure can only be used for the InAs/Si material. It can be extended to other materials such as the Ge/Si heterojunction, as discussed later. Fig. 1(a) shows the schematic structure of the proposed planar InAs/Si TFET. The uniform doping profiles of the InAs channel layer, P+-doped Si, and N+doped Si are  $N_{InAs} = 1 \times 10^{15}$  cm<sup>-3</sup>,  $N_{Sour} = 5 \times 10^{19}$  cm<sup>-3</sup>, and  $N_{Drain} = 1 \times 10^{19}$  cm<sup>-3</sup>, respectively. The gate oxide thickness of SiO<sub>2</sub>(T<sub>OX</sub>) and the InAs layer thickness (T<sub>InAs</sub>) are 1 nm and 5 nm, respectively. The overlapping part of the InAs layer and the P+-doped Si is L<sub>tunnel</sub> = 25 nm, and the underlapped length between the gate metal and the drain metal L<sub>GD</sub> is set as 50 nm.

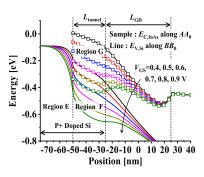

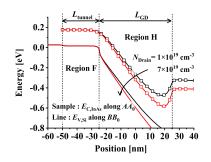

For convenience of subsequent analysis and description, some regions and cutlines are marked in Fig. 1(b). Region G indicates the InAs channel directly under the gate metal, and region H is the InAs part between the gate metal and the drain metal. The P+-doped Si directly under region G is marked as region F, and the rest is region E. Cutlines AA<sub>0</sub> and BB<sub>0</sub> are 1 nm above and below the InAs/Si interface, respectively. CC<sub>0</sub> is perpendicular to the InAs/Si interface and goes through the gate metal and regions G and F. Obviously, the gate (metal and dielectric), InAs channel (region G), and P+-doped Si (region F) form a sandwich structure. Once the conduction band edge of InAs (E<sub>C,InAs</sub>) in region G modulated by the gate voltage ( $V_{GS}$ ) is lower than the valance band edge of Si ( $E_{V,Si}$ ) in region F, the carriers in region F can tunnel into region G and then drift in the InAs channel until they are collected by the drain.

The performance of the device has been simulated using the Synopsys Sentaurus Technology Computer-Aided Design (TCAD) tools as in other theoretical works [25], [26]. The BTBT model with the dynamic nonlocal path accounting for the arbitrary tunneling barrier with a nonuniform electrical field is adopted. To obtain reasonable parameters and numerical results as reliable as possible, the experimentally calibrated tunneling parameters  $A_{path} = 3 \times 10^{19} \text{ cm}^{-3} \cdot \text{s}^{-1}$ and  $B_{path} = 2.6 \times 10^6 \text{ V} \cdot \text{cm}^{-1}$  are adopted in the BTBT model for InAs [27]. For the Si side, the default values of  $A_{path} = 4 \times 10^{14} \text{ cm}^{-3} \cdot \text{s}^{-1}$  and  $B_{path} = 1.9 \times 10^{17} \text{ V} \cdot \text{cm}^{-1}$  are used, which are also obtained from experimental data [28]. To ensure the accuracy of the results at very small dimensions of T<sub>InAs</sub>, the modified local-density approximation (MLDA) is used to account for the quantum confined carrier distributions. The doping-dependent mobility along with the high-field saturation model, the Shockley-Read-Hall (SRH) recombination model, the band gap narrowing model, and Fermi statistics are also applied in the simulation.

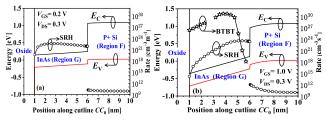

FIGURE 2. Energy band diagrams of the planar InAs/Si TFET along cutline  $CC_0$  in the (a) off-state and (b) on-state.

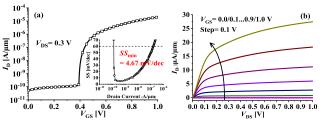

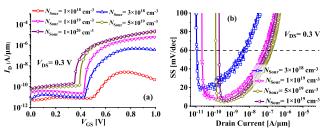

The device principle can be understood based on the energy band diagrams, BTBT rate, and SRH generation rate along cutline CC<sub>0</sub> demonstrated in Fig. 2. In the off-state, BTBT under the gate from region F to G is forbidden since the  $E_{C,InAs}$  in region G is misaligned with the  $E_{V,Si}$  in region F, as shown in Fig. 2(a). When a larger  $V_{GS}$  is applied,  $E_{C,InAs}$ can be lower than E<sub>V,Si</sub>, as exhibited in Fig. 2(b); the current starts to be mainly dominated by the carriers flowing vertically from region F to region G via BTBT, and thus, the device is turned on. Obviously, the gate field is aligned with the carrier tunneling direction in our device, which is different from the gate field being perpendicular to the tunneling direction in conventional TFETs. This alignment enhances the gate control efficiency and improves the device performance, as demonstrated in Fig. 3, which shows the simulated transfer and output characteristics. A small SS<sub>min</sub> as low as 4.67 mV/dec is obtained, and SS can be less than 60 mV/dec for 3 decades of current, exhibiting excellent transfer properties.

## **III. KEY PARAMETERS AND DEVICE OPTIMIZATION**

In this section, different parameters, including  $L_{tunnel}$ ,  $T_{InAs}$ ,  $T_{ox}$ ,  $N_{InAs}$ ,  $N_{Sour}$ ,  $N_{Drain}$ , and  $L_{GD}$ , are studied in detail,

**FIGURE 3.** (a)  $I_{DS}$ -V<sub>GS</sub> characteristics and SS-I<sub>DS</sub> curve (insert) and (b) output characteristics of the proposed planar InAs/Si TFETs.

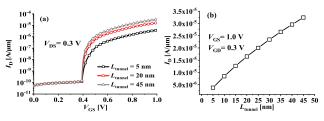

FIGURE 4. Effect of  $L_{tunnel}$  on the (a)  $I_{DS}$ - $V_{GS}$  characteristics and (b) on-state current.

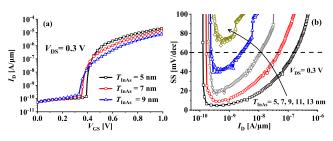

FIGURE 5. Effect of T<sub>InAs</sub> on the (a) I<sub>DS</sub>-V<sub>GS</sub> characteristics and (b) SS.

and the device performance is enhanced by adopting the optimized values.

In the on-state of our proposed device, the carriers vertically tunnel from region F to G. The interface length  $L_{tunnel}$ between regions F and G dominates the effective tunneling area. Therefore, a large  $L_{tunnel}$  is intuitively understood to result in enhanced  $I_{ON}$  due to the enlarged tunneling area, as presented in Fig. 4(a). In a conventional TFET, the carrier tunneling is limited to the channel/oxide interface near the source side. The effective tunneling area and the tunneling current can hardly be modulated by the gate length [22], [23]. However, in our devices, the almost linear relationship between  $I_{ON}$  and  $L_{tunnel}$  indicated in Fig. 4(b) allows designers to easily adjust  $I_{ON}$  to meet the actual demand of different circuits and thus enhances the flexibility of circuit design, similar to that in MOSFETs.

Because the InAs layer is between the gate and the tunneling junction, a thick InAs layer would lead to weakened gate control of the InAs/Si tunneling junction. The influence of  $T_{InAs}$  on the device performance is exhibited in Fig. 5. A thicker  $T_{InAs}$  obviously results in slightly decreased  $I_{ON}$  and degraded SS characteristics. Actually, SS, namely, the gate voltage required to change the drain current by one order of magnitude when the transistor is operated in

the subthreshold region, can be expressed as follows [29].

$$SS = \underbrace{\frac{dV_G}{d\varphi_{\text{inter}}}}_{m} \underbrace{\frac{d\varphi_{\text{inter}}}{d\left(\log_{10}I_{ON}\right)}}_{n} \tag{1}$$

where  $\varphi_{inter}$  is the potential at the tunneling interface between regions G and F. The term m reflects the efficiency of control of  $\varphi_{inter}$  by V<sub>GS</sub>, and the smaller m is, the stronger the gate control efficiency and the smaller m eSS. The term n is a factor that characterizes the change in the drain current with potential  $\varphi_{inter}$ , reflecting the conduction mechanism. For our proposed structure, the gate (metal and dielectric), InAs channel (region G), and P+-doped Si (region F) form a sandwich structure. The term m can be obtained using the gate oxide capacitance C<sub>ox</sub>, InAs layer capacitance C<sub>InAs</sub>, and depletion capacitance C<sub>dep</sub> in series, as in (2).

$$m = \frac{dV_G}{d\varphi_{\text{inter}}} = 1 + \frac{C_{dep}}{C_{ox}} + \frac{C_{dep}}{C_{InAs}}$$

(2)

m obviously exhibits a minimum of 1. Increased  $C_{ox}$  and  $C_{InAs}$  and decreased  $C_{dep}$  help reduce m and SS. Therefore, a thicker  $T_{InAs}$  leads to degraded SS owing to the decreased  $C_{InAs}$ . To achieve SS less than 60 mV/dec over at least two decades of drain current,  $T_{InAs}$  should be kept thinner than approximately 10 nm, which is not a great issue for modern nanotechnology [30], [31].

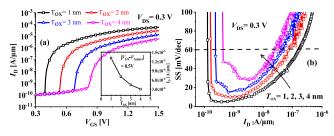

FIGURE 6. Effect of T<sub>ox</sub> on the (a)  $I_{DS}$ -V<sub>GS</sub> characteristics and  $I_{ON}$  extracted at  $|V_{GS}$ -V<sub>tunnel</sub>| = 0.5 V (insert) and (b) SS.

$T_{ox}$  is also an important factor affecting device performance, and its influence is exhibited in Fig. 6(a). A thicker  $T_{ox}$  leads to increased  $V_{tunnel}$  at which the drain current starts to be higher than the reverse leakage current. The increased  $V_{tunnel}$  indicates a weakened tunneling capability. The  $I_{ON}$  extracted at  $|V_{GS}-V_{tunnel}| = 0.5$  V is presented in the insert of Fig. 6(a), and obviously, a thicker  $T_{ox}$  results in a reduced  $I_{ON}$ . In addition to  $I_{ON}$ , SS can also be degraded with thicker  $T_{ox}$ , as shown in Fig. 6(b) by the increased SS<sub>min</sub> and the reduced current range over which SS is less than 60 mV/dec. Actually, this result is similar to the influence of  $T_{InAs}$ . The decreased  $C_{ox}$  caused by a thicker  $T_{ox}$  results in an increased m in (2) and thus a degraded SS in (1).

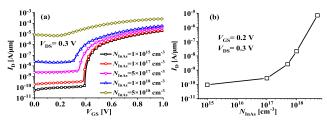

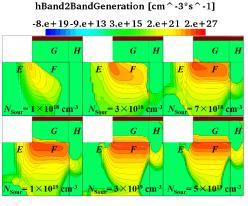

The InAs layer doping density  $N_{InAs}$  has a great effect on the device performance, as shown in Fig. 7. With increased  $N_{InAs}$ ,  $I_{OFF}$  and SS are significantly degraded, and the device cannot be turned off for  $N_{InAs} = 5 \times 10^{18}$  cm<sup>-3</sup>. Fig. 8(a) gives the SRH and BTBT rates along cutline AA<sub>0</sub> in the offstate. The BTBT rate in region H is clearly much larger than

FIGURE 7. Device (a) I<sub>DS</sub>-V<sub>CS</sub> characteristics and (b) off-state current as a function of the InAs layer doping density N<sub>InAs</sub>.

**FIGURE 8.** (a) SRH and BTBT rates along cutline AA<sub>0</sub> and (b)  $E_{C,InAs}$  along AA<sub>0</sub> and  $E_{V,Si}$  along BB<sub>0</sub> in the off-state ( $V_{GS} = 0.2$  V,  $V_{DS} = 0.3$  V) for different N<sub>InAs</sub>.

**FIGURE 9.** Device (a)  $I_{DS}$ -V<sub>GS</sub> and (b) SS-I<sub>D</sub> characteristics as a function of the P+ Si doping concentration N<sub>Sour</sub>.

the SRH generation rate and should dominate  $I_{OFF}$ . To determine where the carriers in region H tunnel from, Fig. 8(b) illustrates the  $E_{C,InAs}$  along  $AA_0$  and the  $E_{V,Si}$  along  $BB_0$ . The  $E_{V,Si}$  in region F obviously overlaps with the  $E_{C,InAs}$  in region H, allowing electrons to tunnel from region F into H. The unexpected parasitic tunneling dominates  $I_{OFF}$ . Moreover, with increased  $N_{InAs}$ ,  $E_{C,InAs}$  becomes lower, which reduces the tunneling barrier width between regions F and H. Thus, the BTBT rate in region H becomes higher (Fig. 8(a)), and  $I_{OFF}$  increases (Fig. 7(b)).

The impact of N<sub>Sour</sub> is shown in Fig. 9(a), and increased N<sub>Sour</sub> clearly leads to increased I<sub>OFF</sub> and I<sub>ON</sub>. However, for N<sub>Sour</sub> above  $1 \times 10^{19}$  cm<sup>-3</sup>, I<sub>OFF</sub> and I<sub>ON</sub> are not very different. Considering that the current range over which SS is below 60 mV/dec is reduced with N<sub>Sour</sub> above  $1 \times 10^{19}$  cm<sup>-3</sup>, as depicted in Fig. 9(b), taking N<sub>Sour</sub> =  $1 \times 10^{19}$  cm<sup>-3</sup> as the optimal value is reasonable.

The slightly P+-doped Si region can be considered to be depleted, and the gate voltage drops in both regions G and F. In other words, the  $E_{C,InAs}$  in region G and the  $E_{V,Si}$  in region F simultaneously decrease when  $V_{GS}$  increases. Thus, the  $E_{C,InAs}$  in region G and the  $E_{V,Si}$  in region F cannot overlap, and carrier tunneling from region F to G never occurs,

FIGURE 10.  $E_{C,\,InAs}$  along  $AA_0$  and  $E_{V,\,Si}$  along  $BB_0$  for  $N_{Sour}=1\,\times\,10^{18}$   $cm^{-3}.$

FIGURE 11. Contour mapping of the hole BTBT rate distribution for the devices with different  $N_{Sour}$  at  $V_{GS} = 1.0$  V.

as demonstrated in Fig. 10, which shows the E<sub>C,InAs</sub> along AA<sub>0</sub> and the E<sub>V,Si</sub> along BB<sub>0</sub> for a device with a low P+ doping concentration of  $N_{Sour} = 1 \times 10^{18} \text{ cm}^{-3}$ . However, the  $E_{V,Si}$  in region E drops slower than the  $E_{C,InAs}$  in region G, and the  $E_{V,Si}$  in region E overlaps with the  $E_{C,InAs}$  in region G with increased V<sub>GS</sub>. This phenomenon allows the carriers in region E to tunnel into region G, dominating the drain current. With increased NSour, the P+-doped Si in region F is no longer depleted, and the large number of carriers in region F screen the gate electric field. Therefore, the gate voltage mainly drops in region G, and the EV, Si in region F remains almost unchanged when the E<sub>C,InAs</sub> in region G decreases with increased  $V_{GS}$ . Thus, carrier tunneling from region F to G occurs. Fig. 11 illustrates the contour mapping of the hole BTBT rate distribution for different N<sub>Sour</sub>. For slightly doped N<sub>Sour</sub>, the tunneling process mainly occurs between regions E and G, and holes are mainly generated in region E. With increased N<sub>Sour</sub>, the tunneling process gradually moves to between regions F and G, and the hole generation gradually moves to region F.

As a part of the tunneling junction, the P+-doped Si is the source of carriers tunneling into the InAs channel. Different from this, the N+-doped Si region does not participate in the tunneling process. The main role of the N+-doped Si is to form a reverse PN junction with the P+-doped region obstructing the current path in the Si substrate and allowing

FIGURE 12. Device (a)  $I_{DS}\text{-}V_{GS}$  characteristics and (b)  $I_{OFF}$  as a function of the N+ Si doping concentration  $N_{Drain}.$

FIGURE 13.  $E_{C,\,InAs}$  along  $AA_0$  and  $E_{V,\,Si}$  along  $BB_0$  for different  $N_{Drain}$  at  $V_{GS}=0.2$  V and  $V_{DS}=0.3$  V.

FIGURE 14. Device (a)  $I_{DS} - V_{GS}$  characteristics and (b)  $I_{OFF}$  as a function of  $L_{GD}$ .

current flow only through the InAs/Si junction by tunneling. The influence of the N+ doping concentration N<sub>Drain</sub> is shown in Fig. 12, and the device with a lightly N+-doped region exhibits large I<sub>OFF</sub>. For N<sub>Drain</sub> =  $1 \times 10^{17}$  cm<sup>-3</sup>, the device cannot be thoroughly turned off, as the current directly flows from the P+-doped region to the N+-doped region via drift. With increased N<sub>Drain</sub>, I<sub>OFF</sub> is suppressed. However, the slightly increased  $I_{OFF}$  above  $N_{Drain} = 5 \times 10^{18}$  $cm^{-3}$  indicates an optimal value of approximately  $5 \times 10^{18}$  $cm^{-3}$  at which I<sub>OFF</sub> reaches the minimum value. This result can be explained using Fig. 13, which shows the E<sub>C InAs</sub> along  $AA_0$  and the  $E_{V,Si}$  along  $BB_0$  in the off-state. Although the increased N<sub>Drain</sub> suppresses the current component through the Si bulk, it also induces a larger electric field and a steeper energy band profile between the P+ Si region and the N+ Si region, leading to a smaller tunneling width and an enhanced tunneling probability from region F to H.

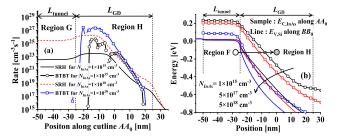

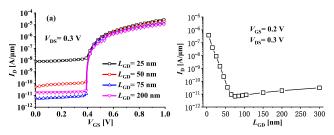

The distance between the gate metal and the drain metal  $L_{GD}$  is another important parameter, and its effect is exhibited in Fig. 14. Similar to  $N_{Drain}$ ,  $L_{GS}$  also mainly affects  $I_{OFF}$ , and

**FIGURE 15.** (a)  $E_{C,InAs}$  along  $AA_0$ ,  $E_{V,Si}$  along  $BB_0$  and tunneling width (insert) and (b) SRH and BTBT rates along  $AA_0$  for different  $L_{GD}$  at  $V_{GS} = 0.2$  V and  $V_{DS} = 0.3$  V. Note that the edge of regions G and H is at position =  $-L_{GD}/2$  because the coordinate origin is set at the midpoint of region H in our work.

an optimal value of approximately 75 nm is obtained. Considering that  $I_{OFF}$  mainly arises from the parasitic tunneling between regions F and H, Fig. 15(a) depicts the  $E_{C,InAs}$  along AA<sub>0</sub> and the  $E_{V,Si}$  along BB<sub>0</sub> in the off-state for different  $L_{GD}$ . An increased  $L_{GD}$  obviously leads to a smooth energy band profile and thus an increased tunneling width (insert in Fig. 15(a)) between regions F and H, which suppresses the parasitic tunneling probability, as demonstrated in Fig. 15(b). This phenomenon is why I<sub>OFF</sub> decreases with increasing  $L_{GD}$  below 75 nm. However, as shown in Fig. 15(b), the parasitic BTBT rate only dominates I<sub>OFF</sub> for  $L_{GD} < 75$  nm, and for  $L_{GD} > 75$  nm, the SRH rate plays the major role. Therefore, I<sub>OFF</sub> shows a slight linear increase with increasing  $L_{GD}$  above 75 nm owing to the enhanced SRH current resulting from the enlarged SRH area.

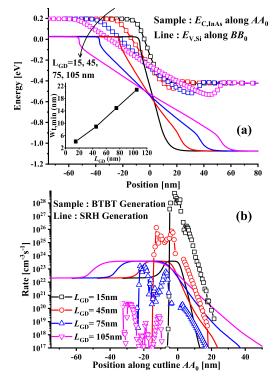

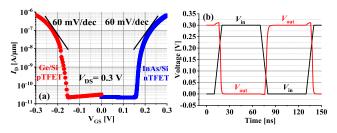

Fig. 16 presents a performance comparison among the optimized InAs/Si TFET and other TFETs with heterojunction and structural innovations presented in theoretical works [11]–[15]. The transfer curves have been translated so that the tunneling current starts to be higher than I<sub>OFF</sub> at  $V_{GS} = 0$  V for ease of comparison. Despite the relatively low I<sub>ON</sub> at  $V_{GS} = 1.0$  V, our proposed InAs/Si TFET exhibits the highest I<sub>ON</sub> for  $V_{GS} < 0.15$  V (Fig. 16(a)) and the lowest SS (Fig. 16(b)) even with a relatively large effective oxide thickness (EOT), indicating that the proposed device is much more promising for future ultralow power applications.

**FIGURE 16.** (a)  $I_{DS}$ -V<sub>GS</sub> and (b) SS-I<sub>DS</sub> characteristic comparison among the proposed InAs/Si TFET and novel TFET structures presented in other theoretical works.

**FIGURE 17.** Structure comparison of some novel TFET devices. (a) Ge/Si SUTFET, (b) GaAsSb/InGaAs  $P^- P^+$  TFET, (c) GeSn Fin-TFET, (d) GaSb/InAs R-DGTFET, and (e) GaSb/InAs TFET with nonuniform body thickness.

In addition to the excellent performance, our proposed architecture also presents advantages in terms of structure design and fabrication process. Fig. 17 demonstrates the novel device structures in [11]–[15] with corresponding transfer curves in Fig. 16. The proposed device structures in Fig. 17(a)-(e) are clearly relatively complicated and show poor compatibility with the conventional CMOS technology. By comparison, our proposed structure is planar and the simplest. The basic steps of the process flow are exhibited in Fig. 18 in a convenient manner. Obviously, our structure is more compatible with the conventional CMOS fabrication, which is of extreme significance for the practical application of TFETs in the future.

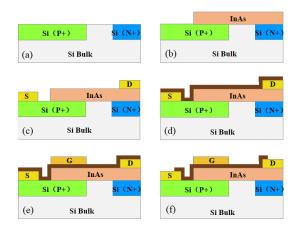

**FIGURE 18.** Proposed process steps for the planar InAs/Si TFET. (a) P+ and N+ ion implantation and annealing in the Si bulk. (b) InAs layer epitaxy. (c) Source and drain metal patterning. (d) Gate dielectric deposition. (e) Gate metal patterning. (f) Dielectric etching.

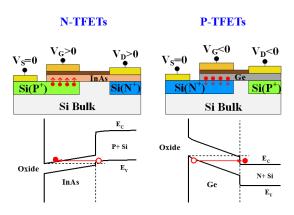

FIGURE 19. Proposed InAs/Si N-TFET and Ge/Si P-TFET, and corresponding energy band profiles along cutline CC<sub>0</sub> in the on-state.

## IV. PERFORMANCE OF THE COMPLEMENTARY TFET INVERTER BASED ON THE PROPOSED STRUCTURE

As noted in Section I, the N-TFET and P-TFET are usually investigated separately to obtain the optimal performance for only one type of device, which results in unsatisfactory complementary behavior due to the lack of material universality and degraded p-type or n-type performance. By comparison, our proposed structure is suitable for different materials, such as InAs, Ge, and GaSb, and is more suitable for complementary device performance and inverters. Taking Ge as an example, Fig. 19 shows the proposed InAs/Si N-TFET and Ge/Si P-TFET along with the corresponding energy band along cutline CC<sub>0</sub> in the on-state. The principle of the Ge/Si P-TFET is similar to that of the InAs/Si N-TFET discussed above. As the valance band of Ge is elevated to be higher than the conductance band of N+ Si, electrons can tunnel from the Ge to N+- doped Si region, and thus, a current flows from the source to the drain.

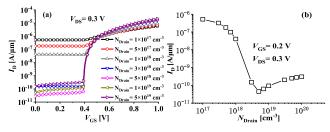

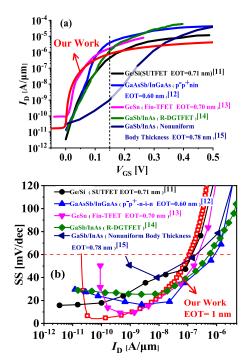

For the device parameters listed in Table 1, the highly complementary performance shown in Fig. 20(a) is obtained. Both the N-TFET and the P-TFET show steep  $I_{DS}$ -V<sub>GS</sub>

| TABLE 1. Device parameters adopted in the TFET inverter based on the |

|----------------------------------------------------------------------|

| proposed InAs/Si N-TFET and Ge/Si P-TFET.                            |

| Symbol            | Ge/Si P-TFET                       | InAs/Si N-TFET                       |

|-------------------|------------------------------------|--------------------------------------|

| EOT               | 0.71 nm                            | 1 nm                                 |

| $T_{Ge}/T_{InAs}$ | 5 nm                               | 5 nm                                 |

| $N_{Ge}/N_{InAs}$ | $1 \times 10^{18} \text{ cm}^{-3}$ | $1 \times 10^{18} \text{ cm}^{-3}$   |

| N <sub>Sour</sub> | $2 \times 10^{19} \text{ cm}^{-3}$ | $1.2 \times 10^{19} \text{ cm}^{-3}$ |

| $N_{Drain}$       | $5 \times 10^{18} \text{ cm}^{-3}$ | $5 \times 10^{18} \text{ cm}^{-3}$   |

| $L_{tunnel}$      | 30 nm                              | 30 nm                                |

| L <sub>GD</sub>   | 50 nm                              | 50 nm                                |

**FIGURE 20.** (a) I<sub>DS</sub>-V<sub>GS</sub> characteristics of the complementary TFET using the InAs/Si N-TFET and Ge/Si P-TFET with the parameters listed in Table 1. (b) Input signal and transient response of the complementary TFET inverter with our proposed devices.

characteristics, and SS can be less than 60 mV/dec over almost four decades of current, which indicates that the devices are promising for further reducing the supply voltage. The transient response of the complementary inverter is exhibited in Fig. 20(b), and the inverted output signal with the input signal at a supply voltage of 0.3 V reveals that our proposed devices are promising for future low power digital applications.

### **V. CONCLUSION**

A novel architecture is proposed for TFETs, and taking the InAs/Si TFET as an example, the device parameters are investigated in detail. The advantages of the proposed architecture include the following: First, the gate control is enhanced and the electrical performance is improved owing to the gate field being parallel to the tunneling direction. Second, the effective tunneling area and current in our proposed devices can be adjusted depending on the actual requirements of circuit design, which increases the flexibility of TFET-based circuit design. Third, the device architecture exhibits better material compatibility and can be adopted for both n-type and p-type devices. Fourth, this proposed structure shows good compatibility with CMOS technology without any complicated fabrication steps. In summary, the proposed architecture would be helpful for future ultralow power digital applications.

#### REFERENCES

[1] K. Kumar, Y.-F. Hsieh, J.-H. Liao, K.-H. Kao, and Y.-H. Wang, "Significance of multivalley and nonparabolic band structure for GeSn TFET simulation," *IEEE Trans. Electron Devices*, vol. 65, no. 10, pp. 4709–4715, Oct. 2018, doi: 10.1109/ted.2018.2864544.

- [2] D.-H. Ahn, S.-H. Yoon, K. Kato, T. Fukui, M. Takenaka, and S. Takagi, "Effects of ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate-stack on the performance of planar-type InGaAs TFET," *IEEE Trans. Electron Devices*, vol. 66, no. 4, pp. 1862–1867, Apr. 2019, doi: 10.1109/ted.2019.2897821.

- [3] J. H. Kim, S. Kim, and B.-G. Park, "Double-gate TFET with vertical channel sandwiched by lightly doped Si," *IEEE Trans. Electron Devices*, vol. 66, no. 4, pp. 1656–1661, Apr. 2019, doi: 10.1109/ted.2019.2899206.

- [4] H. Lu, B. Lu, Y. Zhang, Y. Zhang, and Z. Lv, "Drain current model for double gate tunnel-FETs with InAs/Si heterojunction and sourcepocket architecture," *Nanomaterials*, vol. 9, no. 2, p. 181, Feb. 2019, doi: 10.3390/nano9020181.

- [5] B. Lu, H. Lu, Y. Zhang, Y. Zhang, X. Cui, Z. Lv, S. Yang, and C. Liu, "A charge-based capacitance model for double-gate tunnel fets with closed-form solution," *IEEE Trans. Electron Devices*, vol. 65, no. 1, pp. 299–307, Jan. 2018, doi: 10.1109/ted.2017.2775341.

- [6] M. Shrivastava, "Drain extended tunnel FET—A novel power transistor for RF and switching applications," *IEEE Trans. Electron Devices*, vol. 64, no. 2, pp. 481–487, Feb. 2017, doi: 10.1109/ted.2016.2636920.

- [7] Q. Huang, R. Huang, C. Wu, H. Zhu, C. Chen, J. Wang, L. Guo, R. Wang, L. Ye, and Y. Wang, "Comprehensive performance reassessment of TFETs with a novel design by gate and source engineering from device/circuit perspective," in *Proc. IEEE Int. Electron Devices Meeting*, San Francisco, CA, USA, Dec. 2014, pp. 13.3.1–13.3.4, doi: 10.1109/iedm.2014.7047044.

- [8] S. W. Kim, J. H. Kim, T.-J. King Liu, W. Y. Choi, and B.-G. Park, "Demonstration of L-shaped tunnel field-effect transistors," *IEEE Trans. Electron Devices*, vol. 63, no. 4, pp. 1774–1778, Apr. 2016, doi: 10.1109/TED.2015.2472496.

- [9] Q. Huang, R. Huang, Z. Zhan, Y. Qiu, W. Jiang, C. Wu, and Y. Wang, "A novel Si tunnel FET with 36mV/dec subthreshold slope based on junction depleted-modulation through striped gate configuration," in *Proc. Int. Electron Devices Meeting*, San Francisco, CA, USA, Dec. 2012, pp. 8.5.1–8.5.4, doi: 10.1109/iedm.2012.6479005.

- [10] S. L. Noor, S. Safa, and M. Z. R. Khan, "Dual-material double-gate tunnel FET: Gate threshold voltage modeling and extraction," *J. Comput. Electron.*, vol. 15, no. 3, pp. 763–769, Sep. 2016, doi: 10.1007/s10825-016-0816-3.

- [11] S. Chen, S. Wang, H. Liu, W. Li, Q. Wang, and X. Wang, "Symmetric U-shaped gate tunnel field-effect transistor," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 1343–1349, Mar. 2017, doi: 10.1109/ted.2017.2647809.

- [12] D. Verreck, A. S. Verhulst, M. L. Van De Put, B. Soree, N. Collaert, A. Mocuta, A. Thean, and G. Groeseneken, "Uniform strain in heterostructure tunnel field-effect transistors," *IEEE Electron Device Lett.*, vol. 37, no. 3, pp. 337–340, Mar. 2016, doi: 10.1109/led.2016.2519681.

- [13] H. Wang, G. Han, X. Jiang, Y. Liu, C. Zhang, J. Zhang, and Y. Hao, "Performance enhancement in uniaxially tensile stressed GeSn n-channel fin tunneling field-effect transistor: Impact of stress direction," *Jpn. J. Appl. Phys.*, vol. 56, no. 4S, Apr. 2017, Art. no. 04CD07, doi: 10.7567/jjap.56.04cd07.

- [14] U. E. Avci and I. A. Young, "Heterojunction TFET Scaling and resonant-TFET for steep subthreshold slope at sub-9nm gate-length," in *Proc. IEEE Int. Electron Devices Meeting*, Washington, DC, USA, Dec. 2013, pp. 3–4, doi: 10.1109/iedm.2013.6724559.

- [15] J. Z. Huang, P. Long, M. Povolotskyi, G. Klimeck, and M. J. W. Rodwell, "Scalable GaSb/InAs tunnel FETs with nonuniform body thickness," *IEEE Trans. Electron Devices*, vol. 64, no. 1, pp. 96–101, Jan. 2017, doi: 10.1109/ted.2016.2624744.

- [16] Y. Balaji, D. Mocuta, G. Groeseneken, Q. Smets, C. J. L. De La Rosa, A. K. A. Lu, D. Chiappe, T. Agarwal, D. H. C. Lin, C. Huyghebaert, and I. Radu, "Tunneling Transistors Based on MoS<sub>2</sub>/MoTe<sub>2</sub> Van der Waals Heterostructures," *IEEE J. Electron Devices Soc.*, vol. 6, no. 1, pp. 1048–1055, 1st Quart., 2018, doi: 10.1109/jeds.2018.2815781.

- [17] N. Bagga, A. Kumar, and S. Dasgupta, "Demonstration of a novel two source region tunnel FET," *IEEE Trans. Electron Devices*, vol. 64, no. 12, pp. 5256–5262, Dec. 2017, doi: 10.1109/ted.2017.2759898.

- [18] S. Tirkey, D. Sharma, D. S. Yadav, and S. Yadav, "Analysis of a novel metal implant junctionless tunnel FET for better DC and analog/RF electrostatic parameters," *IEEE Trans. Electron Devices*, vol. 64, no. 9, pp. 3943–3950, Sep. 2017, doi: 10.1109/ted.2017.2730922.

- [19] P.-C. Shih, W.-C. Hou, and J.-Y. Li, "A U-gate InGaAs/GaAsSb heterojunction TFET of tunneling normal to the gate with separate control over ON- and OFF-state current," *IEEE Electron Device Lett.*, vol. 38, no. 12, pp. 1751–1754, Dec. 2017, doi: 10.1109/led.2017.2759303.

- [20] B. Gopireddy, D. Skarlatos, W. Zhu, and J. Torrellas, "HetCore: TFET-CMOS hetero-device architecture for CPUs and GPUs," in *Proc. ACM/IEEE 45th Annu. Int. Symp. Comput. Archit. (ISCA)*, Los Angeles, CA, USA, Jun. 2018, pp. 802–815, doi: 10.1109/isca.2018.00072.

- [21] N. Gupta, A. Makosiej, O. Thomas, A. Amara, A. Vladimirescu, and C. Anghel, "Ultra-low leakage sub-32nm TFET/CMOS hybrid 32kb pseudo DualPort scratchpad with GHz speed for embedded applications," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, Lisbon, Portugal, May 2015, pp. 597–600, doi: 10.1109/iscas.2015.7168704.

- [22] J. Wu, J. Min, and Y. Taur, "Short-channel effects in tunnel FETs," *IEEE Trans. Electron Devices*, vol. 62, no. 9, pp. 3019–3024, Sep. 2015, doi: 10.1109/ted.2015.2458977.

- [23] Y.-C. Li, H.-M. Zhang, Y.-M. Zhang, H.-Y. Hu, B. Wang, Y.-L. Lou, and C.-Y. Zhou, "Two-dimensional threshold voltage model of a nanoscale silicon-on-insulator tunneling field-effect transistor," *Chin. Phys. B*, vol. 22, no. 3, Mar. 2013, Art. no. 038501, doi: 10.1088/1674-1056/22/3/038501.

- [24] C. Wu, R. Huang, Q. Huang, J. Wang, and Y. Wang, "Design guideline for complementary heterostructure tunnel FETs with steep slope and improved output behavior," *IEEE Electron Device Lett.*, vol. 37, no. 1, pp. 20–23, Jan. 2016, doi: 10.1109/led.2015.2499183.

- [25] G. D. Das, G. P. Mishra, and S. Dash, "Impact of source-pocket engineering on device performance of dielectric modulated tunnel FET," *Superlattices Microstruct.*, vol. 124, pp. 131–138, Dec. 2018, doi: 10.1016/j.spmi.2018.10.014.

- [26] A. Dubey, R. Narang, M. Saxena, and M. Gupta, "Investigation of total ionizing dose effect on SOI tunnel FET," *Superlattices Microstruct.*, vol. 133, Sep. 2019, Art. no. 106186, doi: 10.1016/j.spmi.2019.106186.

- [27] C.-W. Hsu, M.-L. Fan, V. P.-H. Hu, and P. Su, "Investigation and simulation of work-function variation for III–V broken-gap heterojunction tunnel FET," *IEEE J. Electron Devices Soc.*, vol. 3, no. 3, pp. 194–199, May 2015, doi: 10.1109/jeds.2015.2408356.

- [28] TCAD Sentaurus Device Manual, Synopsys, Mountain View, CA, USA, 2012.

- [29] A. M. Ionescu and H. Riel, "Tunnel field-effect transistors as energyefficient electronic switches," *Nature*, vol. 479, no. 7373, pp. 329–337, Nov. 2011, doi: 10.1038/nature10679.

- [30] K. Nomoto, K. Taira, T. Suzuki, I. Hase, H. Hiroshima, and M. Komuro, "Diameter dependence of current–voltage characteristics of ultrasmall area AlSb–InAs resonant tunneling diodes with diameters down to 20 nm," *Appl. Phys. Lett.*, vol. 70, no. 15, pp. 2025–2027, Apr. 1997, doi: 10.1063/1.118772.

- [31] J. Lin, D. A. Antoniadis, and J. A. Del Alamo, "Sub-30 nm InAs quantumwell MOSFETs with self-aligned metal contacts and Sub-1 nm EOT HfO<sub>2</sub> insulator," in *Proc. Int. Electron Devices Meeting*, San Francisco, CA, USA, Dec. 2012, pp. 32.1.1–32.1.4, doi: 10.1109/iedm. 2012.6479149.

**SHIZHENG YANG** received the B.S. degree from the School of Microelectronics, Xidian University, Xi'an, China, in 2013, where he is currently pursuing the Ph.D. degree with the School of Microelectronics. His current research includes III–V/Si heterogeneous integration and design of tunneling field-effect transistor.

**HONGLIANG LV** (Member, IEEE) was born in Tulufan, China, in 1978. She received the M.S. and Ph.D. degrees in microelectronics engineering from Xidian University, Xi'an, China, in 2003 and 2007, respectively. Since 2010, she has been a Professor with the School of Microelectronics, Xidian University, where she is currently involved in the modeling, design, and experiments on III–V/Si heterogeneous integration and tunneling field-effect transistor.

**SILU YAN** received the B.S. degree from the School of Microelectronics, Xidian University, Xi'an, China, in 2017, where she is currently pursuing the Ph.D. degree with the School of Microelectronics. Her current research includes III–V/Si heterogeneous integration and ultralarge scale integrate (ULSI) electro-thermal coupling analysis.

**BIN LU** received the B.S. and Ph.D. degrees from the School of Microelectronics, Xidian University, Xi'an, China, in 2013 and 2019, respectively. He is currently with the School of Physics and Information Engineering, Shanxi Normal University, Linfen, China. His current research includes modeling, design, and fabrication of the tunneling field-effect-transistor (TFET).

**YUMING ZHANG** (Senior Member, IEEE) received the M.S. degree from Xidian University, Xi'an, China, in 1992, and the Ph.D. degree from Xi'an Jiaotong University, Xi'an, in 1998. Since 2001, he has been a Professor with the Microelectronics Institute, Xidian University. His current research interests include design, modeling, fabrication, and electrical characterization of SiC electronic devices for high-temperature and high-power operations.

...