Received December 10, 2019, accepted January 13, 2020, date of publication January 17, 2020, date of current version January 27, 2020. Digital Object Identifier 10.1109/ACCESS.2020.2967027

# GaN Power Integration for High Frequency and High Efficiency Power Applications: A Review

RUIZE SUN<sup>®</sup>, (Member, IEEE), JINGXUE LAI, WANJUN CHEN<sup>®</sup>, (Senior Member, IEEE), AND BO ZHANG<sup>®</sup>, (Senior Member, IEEE)

State Key Laboratory of Electronic Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu 610054, China Corresponding author: Wanjun Chen (wichen@uestc.edu.cn)

This work was supported in part by the State Key Laboratory of Wide-Bandgap Semiconductor Power Electronic Devices, China, under Grant 2019KF002, and in part by the Postdoctoral Science Foundation of University of Electronic Science and Technology of China.

**ABSTRACT** High frequency and high efficiency operation is one of the premier interests in the signal and energy conversion applications. The wide bandgap GaN based devices possess superior properties and have demonstrated exceeding performance than Si or GaAs devices. In order to further exploit the potential of GaN electronics, monolithic power integration is proposed. Firstly, this paper discusses the structure and properties of GaN power devices to explain the choice of lateral integration in the view of GaN power ICs. Then the state-of-the-art performance of GaN power integration in two major application areas is reviewed, which are the microwave power amplification and DC-DC power conversion. The GaN power integration technologies in MMIC platforms are summarized in terms of the gate length, operation frequency and power added efficiency of ICs. On the other hand, the smart GaN power IC platforms have boosted the development of DC-DC power converters. Demonstrations of high frequency (>1 MHz) and high efficiency (>95 %) converters with various kinds of integration technology and topology are reviewed. Lastly novel integration schemes and methods are introduced to stimulate new thoughts on GaN power integration road.

**INDEX TERMS** GaN, HEMT, high frequency, power conversion, power integration.

# I. INTRODUCTION

In the view of minimizing power consumption and heat dissipation during signal or energy conversions, high frequency and high efficiency are most attractive among the premier interests on the power IC designers' checklist [1], [2]. The volume of magnetic energy storage components and the system conversion loss can be largely reduced under higher operation frequency [3]. Moreover, transistors, diodes and passive components can be monolithically integrated to eliminate the parasitic inductance brought by bonding wires to further push the frequency and efficiency, which leads to the wide introduction of power integrated circuits [4], [5].

Other than the development of power IC design techniques, the continuous performance evolution of power integrated devices has accelerated the adoption of novel materials [6], [7]. Compared with Si, GaN material possesses over  $\sim$ 3.1 times of energy bandgap,  $\sim$ 2.7 times of electron saturation velocity and  $\sim$ 11.6 times of critical electric field, which

The associate editor coordinating the review of this manuscript and approving it for publication was Ivona Mitrovic  $^{\bigcirc}$ .

makes GaN suitable for RF and power conversion applications [8]. Especially the GaN High Electron Mobility Transistors (HEMTs) exhibit a 2-Dimentional Electron Gas (2DEG) channel and well fit the lateral integration [9], [10], which is a promising road to fully exploit the merits of GaN material.

The Monolithic Microwave Integrated Circuit (MMIC) was proposed in the GaAs-age with the first MMIC in 1975 [11] and now is still the mainstream process for GaNbased RF and microwave applications [12], [13]. Based on single-chip air-bridge integration of HEMTs, thin film or epitaxy resistors, and metal-insulator-metal capacitors, MMIC process has supported the high frequency microwave electronics from MHz to GHz ranges [14], [15]. The critical dimensions of GaN MMIC process has been reduced from several microns to sub-micron scale of 0.5  $\mu$ m [16],  $0.25 \mu m$  [17],  $0.15 \mu m$  [18],  $0.1 \mu m$  [19],  $0.04 \mu m$  and  $0.02~\mu m$  [15]. Commercial GaN HEMT MMIC platforms include BAE Systems, Fujitsu, Fraunhofer, HRL, MACOM, Northrop Grumman Aerospace Systems and Electronic Systems, NXP, Oki, Qorvo, Raytheon, Wolfspeed and so on, together with many other foundries listing GaN on their

roadmaps. The highly scaled GaN HEMTs have formed excellent MMIC power amplifiers for 5G mobile bands with superior power added efficiency (PAE) performance.

Besides the RF and microwave applications, MMIC process can also play an important role in power conversion applications [20]–[23]. Ultra-high-frequency (UHF) DC-DC converter for on-chip power supply in Envelope Tracking (ET) application is presented at 865 MHz [21]. A buck converter switching at 100 MHz can obtain 90 % efficiency at 9 W output [22]. Other works on resonant DC-DC converters are demonstrated at approximately 1 GHz [24]. However, due to the relative low length of drift region in highly scaled GaN HEMTs in MMIC platforms, the state-of-the-art breakdown voltage is mostly below 150 V. Also the threshold voltage of HEMTs is negative, which is not fault-safe and requires specially designed gate driver. These conditions restrain GaN MMIC processes from realizing high voltage and high power DC-DC converters [25].

GaN power HEMTs or Metal-Insulator-Semiconductor (MIS) HEMTs with normally-OFF operation are introduced by means of gate recess [26], fluorine-ion implantation [27], p-type cap layer [28] or cascode structure [29]. The GaN normally-OFF power devices has ushered a new age of high-frequency and high-efficiency power conversion. Major power semiconductor companies have launched their GaN product lines, such as Cree, Infineon, Panasonic, ON-semi, Texas Instruments and TSMC, while other start-up companies are growing to key players including Efficient Power Conversion (EPC), GaN System, Navitas, Transphorm, VisIC and Wolfspeed. With the increasing availability of commercial discrete devices, the constructed power converter with GaN normally-OFF transistors have surpassed the Si-based counterparts in both output efficiency and operation frequency. It has realized over 95 % efficiency at over 1 MHz and output power over 1 kW [30], [31]. In order to minimize the converter volume for high frequency and high efficiency power conversion, normally-OFF power integration platforms are proposed [6], [9], [10], [32]–[38].

Integration schemes in power converters start from normally-OFF HEMTs with diodes for boost converters using fluorine-ion implantation technique in 2008 [39], [40] and p-type cap-layer Gate-Injection-Transistor technique in 2012 [41]. Later integrated half-bridges, full-bridges are realized with pre-gate driver to reduce the inductance of gate drive loop and a 12 V-1.8 V converter exhibits peak efficiency of 86.6 % at 2 MHz [42]. In the meantime, functional circuits such as inverter [43], comparator [44], voltage reference generator [45] and pulse-width-modulation circuit [46] are fabricated and have successfully demonstrated the analog functions of GaN integrated circuits.

The tide of high-speed GaN revolution keeps rising in industries. The consumer electronics can benefit in power density, charging speed and cost reduction with high-frequency and high-efficiency GaN power integrated converters. Firstly Navitas and Dialog have launched their System on Chip (SoC) GaN power ICs NV6115 and DA8801,

respectively. In the meantime, EPC, Infineon, Tagore Technology and Texas Instruments choose the System in Package (SiP) road. The close proximity of devices and components can greatly reduce parasitic inductance to boost the switching speed. Based on low-voltage transistors, functional subcircuits including gate driver, control and feedback circuits can be integrated as well.

In this paper, the GaN power integration for high frequency and high efficiency power applications is systematically reviewed. In the view of power ICs, the structure and property of GaN power devices are firstly discussed in section II, including the reasons why lateral integration is a choice. In section III the GaN MMIC processes are briefly presented in terms of critical dimensions and IC performance. The GaN smart power IC platforms are discussed in section IV with the development of device technology. Section V includes novel integration platforms and technologies to shed some light on future direction of the GaN integration road. Finally, Section VI summaries this review.

#### II. GAN DEVICES FOR LATERAL INTEGRATION

### A. DEVICE PHYSICS AND STRUCTURE

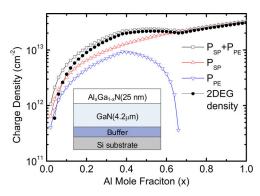

The advantages of GaN over other solid state materials are so apparent that the GaN-based electronic devices should be the better choice for high power applications including RF, microwave and power conversion applications. The GaN material has a noncentrosymmetric wurtzite structure. Due to the difference between electronegativity of Ga and N atoms, the centers of the positive and negative charge in electron cloud do not coincide, thus GaN shows spontaneous polarization. In peseudomorphically grown epitaxial AlGaN/GaN structure, there will be strains due to the lattice mismatch and dislocations, which lead to the piezoelectric polarization. For Ga-face AlGaN/GaN heterostructures, the polarization induced charge density values can be calculated [47]. Fig. 1 shows the calculated polarization charge and 2DEG density values with various Al mole fraction with an inset of basic AlGaN/GaN heterostructure.

**FIGURE 1.** Calculated spontaneous polarization ( $P_{SP}$ ), piezoelectric polarization ( $P_{PE}$ ) and 2DEG density versus Al mole fraction in a typical AlGaN/GaN heterostructure shown in inset.

The 2DEG channel conduction is the key feature of lateral GaN devices, where the electron density can be around

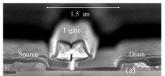

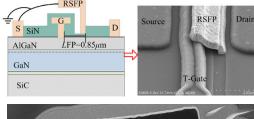

$1\times10^{13}$  cm $^{-2}$ . The source, gate and drain electrode configuration in AlGaN/GaN based devices further paves the way of integration in the same manner as Complimentary-Metal-Oxide-Semiconductor (CMOS) or Lateral-Diffusion-MOS (LDMOS) process. Fig. 2 show the SEM images of AlGaN/GaN HEMTs specially designed for MMIC [48] and power conversion application [28], respectively.

FIGURE 2. SEM images of AlGaN/GaN with (a) 0.1  $\mu$ m gate length for MMIC application [48] and (b) 2  $\mu$ m gate length for power conversion application [28].

In order to get high power-gain cutoff frequency  $f_{max}$ , the gate length can be designed as 100 nm, for example, in Fig. 2(a). While for GaN HEMTs in power applications, the gate length as well as gate-drain separation are designed to be larger, such as 2  $\mu$ m and 7.5  $\mu$ m, respectively, in Fig. 2(b). These lateral distance values, which are all larger than that of GaN HEMTs for MMIC application, can contribute to higher breakdown voltage for GaN power HEMTs. Despite the difference in in dimensions, the same heterostructure and electrode layout establish the common structure basis of lateral power integration schemes.

For a single device, the switching frequency is related with its structure. However when devices are applied with external circuits or ICs, the parasitic inductance in gate drive loop also significantly affects the maximum operation frequency [49]. The parasitic resistance and inductance in all the interconnections, through-vias, wires and pads can degenerate the high frequency switching performance of GaN ICs. This is a critical aspect that current GaN integration technology are trying to improve.

# B. CO-INTEGRATION OF GAN HEMTS FOR MMIC AND POWER SWITCHING

Monolithic co-integration of the optimal GaN HEMTs for MMIC and power switching can be the promising solution of multi-function GaN ICs. In GaN devices, the drain-side access region with length of  $L_{\rm GD}$  bears most breakdown voltage (BV). The  $L_{\rm GD}$  of the power devices is relatively large to obtain a high breakdown voltage; however, the GaN HEMTs for MMIC have very high channel carrier concentration and shorter  $L_{\rm GD}$  (typically less than 1  $\mu$ m) to improve operation frequency with the sacrifice of BV. In order to realize the trade-off between high frequency and high breakdown voltage in the co-integration, specially designed and optimized field plates (FPs) can be introduced as one of the possible solutions.

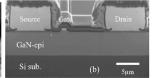

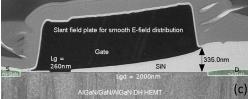

The FPs connected with source and gate can modulate the distribution of surface electric field and alleviate the high electric filed at gate corner in drain side, which contributes

to higher BV. The reported FP types in GaN HEMTs are summarized in Fig. 3. Other than the conventional source FP and gate FP, novel FP structures have been developed. Table 1 listed the reported characteristics of GaN HEMTs with several FP types. The FP techniques can offer efficient solutions to improve BV of GaN HEMTs.

FIGURE 3. Field plate types in GaN HEMTs.

**TABLE 1.** Characteristics of GaN HMETs with various FP types.

| FP type                | $L_{ m G}/L_{ m GD}/L_{ m FP}$ | $f_{ m t}/f_{ m max}$ | BV     | Author<br>s  |

|------------------------|--------------------------------|-----------------------|--------|--------------|

| Multiple gate<br>FPs   | 1/24/~1.4<br>μm                | <1 GHz/-              | 850 V  | UCSB<br>[50] |

| Air-bridge recessed FP | 0.2/1.3/0.85<br>μm             | 38.5/95<br>GHz        | 144 V  | CAS<br>[51]  |

| Asymmetric slant FPs   | 0.2/2/1.2<br>μm                | 41/100 GHz            | 138 V  | HRL<br>[52]  |

| Symmetric<br>Slant FPs | 1/15/0.25<br>μm                | 18.4/65GHz            | 1400 V | UCSB<br>[53] |

Although adding FPs could improve BV, it brings additional parasitic capacitance which limits the operation frequency of GaN HMETs. Especially for the co-integration of GaN HEMTs for MMIC and power switching, it is essential to realize high BV without increasing parasitic capacitance. As shown in Fig. 4(a) and (b), the recessed foot of FP reduce the distance between FP and 2DEG and the SiN dielectric

FIGURE 4. (a) The schematic of GaN HEMT with air-bridge recessed source FP; (b) SEM view of fabricated GaN HEMT in [51]; (c) The TEM cross-section of GaN HEMT with slant FP and slope of 6° at the drain-side gate corner.

is replaced by air-bridge with lower dielectric constant [51], which all contributing to less increase in gate capacitance. The slant FP structure in Fig. 4(c) can provide smoother electric field distribution without significant increase in gate capacitance [52].

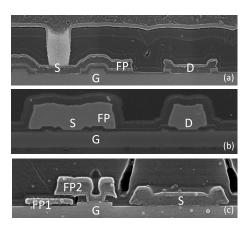

As for commercial GaN HEMTs, Fig. 5 shows the cross-sectional SEM images of EPC 2045, Panasonic-PGA26E19BA and GaN Systems GS61004B GaN transistors, where the source and discrete FPs are adopted. The possible reason can be intention of limiting the introduction of additional gate capacitance and leaving gate intact for reliability concern in commercial GaN HEMTs.

FIGURE 5. The cross-sectional images of (a) EPC2045 100V/16A GaN transistor, (b) Panasonic PGA26E19BA 600V/15A GaN transistor and (c) GaN Systems GS61004B 100V/45A GaN transistor. The contacts and field plates are labelled.

With the help of field plates, the GaN HEMTs for MMIC can have BV up to hundreds of volt with acceptable high frequency operation capability. The optimal GaN HEMTs for MMIC and power switching can probably be co-integrated.

## **III. GAN POWER INTEGRATION FOR MMICS**

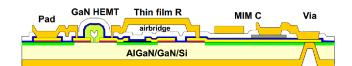

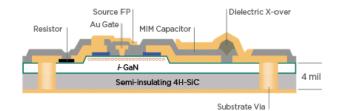

The GaN power integration processes for MMICs are the direct heritages of mature GaAs MMIC process. It features the monolithic integration of normally-ON Schottky gate AlGaN/GaN HEMTs, Schottky barrier diodes, thin-film resistors (TFRs), metal-insulator-metal (MIM) capacitors and inductors. Fig. 6 demonstrates the schematic cross-section of a typical 100 nm GaN-on-Si MMIC process from OMMIC [54].

FIGURE 6. Schematic cross-section of an example 100nm GaN-on-Si process for MMICs [54].

Generally the GaN power integration platform can offer 0.5  $\mu$ m and 0.25  $\mu$ m HEMTs to replace high power LDMOS (> 100W), or 0.1  $\mu$ m and 0.06  $\mu$ m HEMTs to replace

GaAs devices in MMICs to offer high performance wideband-gap (WBG) solutions up to 500 GHz for markets including mobile devices, communications infrastructure, and aerospace applications. The high frequency (operating frequency >50 GHz) power amplifiers (PAs) are the major category of GaN MMICs, while other categories include high linearity low noise amplifiers (LNAs), Voltage-Controlled-Oscillators (VCOs), transmitter/receiver and modulator components. In order to have a comprehensive review of the evolution of GaN MMIC process, the reported MMICs are reviewed in terms of critical gate length which represents the core technology parameter, fabrication institute, operation frequency and PAE of PAs, and other key performance.

### A. GATE LENGTH

The gate length is the determining factor for operation frequency of GaN HEMTs. Along with the scaling down of critical dimensions in IC industry, the gate length in MMIC platform has been scaled down to sub-micron level. Besides conventional optical lithography, electron-beam lithography (EBL) is used in aggressively scaled technologies. The device performance includes the maximum power-gain cutoff frequency  $f_{max}$  which is the maximum frequency at which there is still a power gain. It can be expressed as [55]

$$f_{\text{max}} \approx \frac{f_T}{2\sqrt{\left(R_i + R_s + R_g\right)/R_{ds} + (2\pi f_T)R_gC_{gd}}},$$

(1)

where  $f_T$  is the current-gain cutoff frequency;  $R_i$ ,  $R_s$ ,  $R_g$ ,  $R_{ds}$  are respectively the gate-charging, source, gate and output resistance;  $C_{gd}$  is the gate-drain capacitance. All the denominator parameters need to be reduced to realize high  $f_{max}$ . The down-scaled gate length effectively decreases  $C_{gd}$  while shorter source-drain length can bring lower  $R_{ds}$ . The parasitic components in contacts and interconnects affect the  $R_s$  and  $R_g$ , which can be suppressed in optimized integration schemes

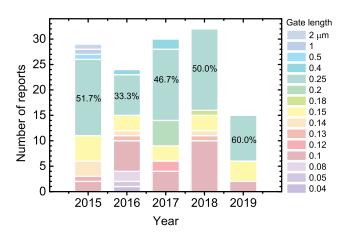

Fig. 7 shows the annual number of reports on MMICs from 2015 to August 2019 in terms of gate length values. Although the data are non-exhaustive, the 0.25  $\mu$ m gate

FIGURE 7. Annul number of reports on MMICs from 2015 to August 2019 in terms of gate length values.

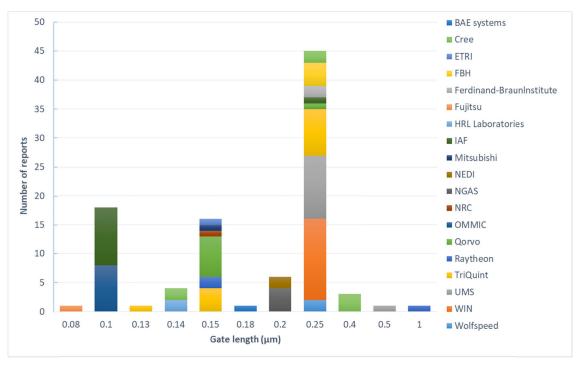

FIGURE 8. Number of reports on MMICs in term of fabrication locations. Data are retrieved from publications in IEEE Xplore and Web of Science.

length MMIC process has been the major choice among the total 130 reviewed reports in scientific research area. The percentage has been over 33.3 % throughout these years. This can be attributed to the acceptable balance between device performance and fabrication cost. Aggressively scaled process, i.e. gate length in tens of nanometers, has been demonstrated by HRL laboratory in 2016 [15]. In Fig. 7, the high proportion of the commercial 0.25  $\mu$ m processes in cited papers can reflect its popularity, accessibility and maturity in industrial companies and research institutes. Fig. 8 shows the fabrication location of the reported works.

The reviewed companies or institutes are non-exhaustive and have not included the change of company names after capital acquisitions, such as TriQuint with Qorvo. Total 19 units are counted out of 97 publications from 2015 to August 2019. It is obvious that 0.25  $\mu$ m process has drawn most attentions in companies and institutes. There are 9 units (47.4 % of total units) contributing 45 reported works (46.4 % of total reviewed publications) which adopt the 0.25  $\mu$ m process. The companies using 0.25  $\mu$ m process include WIN semi, UMS, Qorvo (with TriQuint), Wolfspeed and so on. For example, Fig. 9 demonstrates the Wolfspeed's 0.25  $\mu$ m T-gate GaN HEMT MMIC technology with source field plate. The process platform includes low resistance TFRs, MIM capacitors and 18 GHz normally-ON HEMTs (gate length of 0.25  $\mu$ m) on 4-mil SiC substrate.

# B. PERFORMANCE OF GAN MMICS

The majority type of MMICs is the microwave power amplifiers (PAs). GaN MMIC PAs are specifically designed

FIGURE 9. Schematic cross-section of Wolfspeed' 0.25  $\mu\text{m}$  GaN MMIC technology.

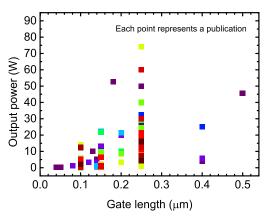

for mainstream 3G/4G/5G base station architectures, which should meet requirements of massive antenna arrays in power density and efficiency, and they can surpass the performance of LDMOS technology. The parameters of the MMIC performance mainly include operation frequency, output power and power added efficiency (PAE). Here the performance of GaN MMICs with the state-of-the-art processes is discussed in terms of gate length, which is the critical dimension of fabrication process. Fig. 10 shows the output power of reported PAs from 2015 to August 2019.

As can be seen from Fig. 10, the range of output power of reported PAs with smaller gate length ( $<0.2~\mu m$ ) is lower, while 0.25  $\mu m$  PAs have output power ranging from 1 W to 75 W. Other than the different application background of PAs with various operation frequencies, the difference of output power capability can be related with the structures of HEMTs. GaN HEMTs with smaller gate length typically have smaller source-drain distance in order to obtain high device cut-off frequency. The device breakdown voltage as well as the power handling capability is limited. For example,

FIGURE 10. Output power of reported PAs in term of gate length in publication from 2015 to August 2019.

the GaN HEMTs fabricated by Wolfspeed's 0.25  $\mu$ m process can operate under drain bias of 28-40 V with breakdown voltage larger than 120 V and power density over 6 W/mm. In comparison, GaN HEMTs using 0.15  $\mu$ m process can be biased at only 28 V, the breakdown voltage is larger than 84 V and the power density is only 3.75 W/mm.

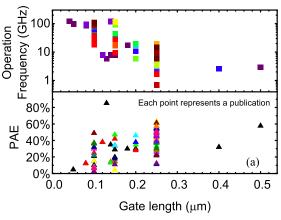

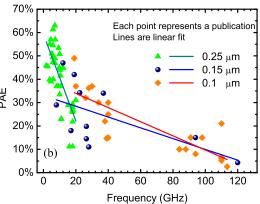

The operation frequency and efficiency of PAs are related with amplifier class. According to the operating mechanism, PAs are divided into conventional PAs (Class A, B AB and C) and switching mode PAs (Class D, E, F and so on). The Class A and AB PAs have relative higher linearity but lower efficiency, typically less than 60 %. The structure of Class AB in conventional PAs is simple and regarded as the trade-off between linearity and efficiency. However, its deterioration of linearity is large when operating at high efficiency. In comparison, switching mode PAs show high efficiency but less linearity than conventional PAs. The theoretical efficiency of Class D, E and F PAs can be 100 % while the typical value is 70 % to 90 %. For applications including wireless communication systems, phased array radars and active imagers, different demands in efficiency and linearity require different optimization of PAs. Fig. 11 shows the operation frequency and PAE of the reported PAs with different device gate length to provide an intuitive understanding of relationship between amplifier performance and device structure.

Fig. 11(a) shows that the operation frequency of PAs is obviously increasing with smaller device gate length, and can be up to several hundreds of GHz. Relatively high frequency (>100 GHz) can be achieved through process with gate length < 0.15 um. On the other hand, the PAE generally decreases with smaller gate length. Fig. 11(b) shows the decreasing trend of PAE in terms of frequency of 0.25/0.15/0.1 um processes. In early works on X-band and below, gate length is above 0.5  $\mu$ m and the device  $f_T$  is 20-40 GHz. The PAs are working in deep A/B-class and the PAE are relatively higher. With the decrease of gate length and increase of frequency, PAE decreases together with gains. From Fig. 11, the choice of process for up to hundreds of GHz application can be the 0.1  $\mu$ m and 0.15  $\mu$ m process. They are expected to provide both better frequency and PAE at the

**FIGURE 11.** (a) Operation frequency and PAE of reported PAs in term of gate length; (b) relationship between PAE and frequency of 0.25/0.15/0.1  $\mu$ m processes in publication from 2015 to August 2019.

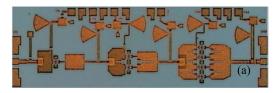

FIGURE 12. Optical images of the fabricated MMIC PAs from (a) [48] with 0.1  $\mu$ m process and (b) [56] with 0.15  $\mu$ m process.

same time compared with 0.25  $\mu$ m process. Fig. 12 shows two typical optical images of fabricated PAs. Wu et al. realize a peak output power of 1.66 W with a peak PAE of 35% in a continuous-wave mode at 93 GHz using 0.1  $\mu$ m process [48]. Youn et al. realize a peak output power of 9.03 W with a peak PAE of 35% under CW operation at 21.5 GHz using 0.15  $\mu$ m process [56].

# IV. GAN POWER INTEGRATION FOR SMART POWER CONVERSION ICS

The GaN power integration for smart power conversion ICs is expected to improve the efficiency of DC power converters by replacing the switching transistors and Schottky diodes with GaN devices. The above mentioned MMIC process can form GaN integrated converters operating at very high frequencies [21], [22], [57]. However, the Schottky gate of AlGaN/GaN HEMTs restricts the input voltage swing, and the gate leakage current could cause deterioration in analog function of integrated circuit components. The negative normally-ON threshold voltage and Schottky gate require extra matching network or off-chip Field-Programmable Gate Array (FPGA) to obtain negative control signal with proper swing. So the integration with normally-OFF MIS-HEMTs is a promising solution for high frequency and high efficiency power conversion application.

### A. INTEGRATED COMPONENTS

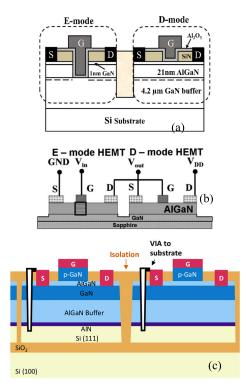

The smart power IC platforms can be categorized in terms of gate dielectric structure and normally-OFF technology. With the proposal of every normally-OFF technology, a novel platform can be formed based the integration of normally-ON and normally-OFF devices. Fig. 13 illustrates the schematic of smart power IC platforms using gate recess [58], fluorine-ion implantation [59] or p-type cap layer [60] technology.

FIGURE 13. Schematic of smart power IC integration platforms using (a) gate recess [58], (b) fluorine-ion implantation [59] and (c) p-GaN cap layer [60] technology.

The isolation is formed by deep mesa or ion-implantation to remove the 2DEG channel between devices. Mesa depth values up to 500 nm are reported [61] to reduce leakage current among devices. However, deep trench makes interconnection more difficult and brings extra surface traps. Implantation isolation uses high energy ions (Ar, F, H, He, N, O) to destroy or deplete the 2DEG channel [62], [63], which can provide flat device surface and is beneficial for lateral metal interconnection. The GaN-on-SOI (Silicon-on-Insulator, SOI) approach has been reported in [38], [64]. The devices are isolated by trench etching until the buried SiO<sub>2</sub> layer and refilling deposition of SiO<sub>2</sub> passivation in the trenches as shown in Fig. 13(c). Especially Interuniversity Microelectronics Center (IMEC) has launched their 200-nm GaN-on-SOI platform and provides Multi-Project Wafer (MPW) runs for power devices and smart power ICs.

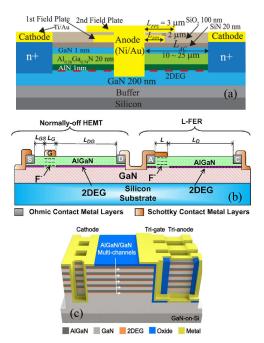

Diodes are essential devices to provide high voltage single direction blocking state in power ICs, and also can be used as voltage level shifter which takes advantage of its forward voltage drop. Most common is the Schottky barrier diode (SBD) which is formed by deposition Ni-based metal on AlGaN or GaN surface [65], [66] as shown in Fig. 14(a). Chen et al. [67] firstly introduces the Lateral Field Effect Rectifiers (L-FERs) which uses a Schottky-gate-controlled 2DEG channel between anode and cathode. The lateral device structure and process compatibility with AlGaN/GaN HEMT make the L-FER a well-qualified candidate in smart power IC platform [39], [68] as shown in Fig. 14(b). In Fig. 14(c) the tri-gate Schottky diodes are based on the tri-anode structure with Schottky contact to the multi-channels through the fin sidewalls to obtain lower turn-on voltage [69]. It also exhibits great potential in working with normally-OFF AlGaN/GaN

FIGURE 14. Schematic structure of (a) a typical Schottky barrier diode [66], (b) a L-FER with a normally-OFF HEMT [67] and (c) a tri-gated Schottky barrier diode [69].

Fin-FETs. Other reported vertical Schottky diodes are not feasible for lateral integration.

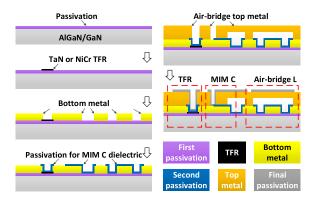

Passive components can be included in smart power IC platforms through the conventional MMIC IPD process. Thin film resistors include poly silicon, TaN and NiCr deposition. The 2DEG channel with controllable electron density can serve as a resistor but with larger temperature coefficient [29], [70]. MIM capacitors use the passivation layer (e.g. SiN<sub>x</sub>) or gate dielectric layer (e.g. Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>) as insulator. The capacitance density is usually below 1 nF/mm<sup>2</sup> for MIM structure with single or multiple SiN<sub>x</sub> passivation as insulator [71]. Generally the inductor is not preferred in ICs. However in high frequency GaN based power converters, inductance and volume can be reduced when operation frequency is at MHz range. On-chip spiral inductor which is formed by deposition of metal routes can be a practical solution. Fig. 15 illustrates the process flow of integrated passive devices in smart power IC platforms.

FIGURE 15. Schematic process flow of integrated passive devices in smart power IC platforms.

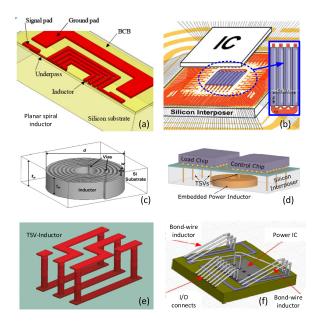

As the values of inductor required for DC-DC converters are typically in  $\mu H$  scale even for MHz power switching, onchip integration of inductor in converter ICs is challenging. Several techniques have been reported to realize integrated inductor with inductance value from nH to  $\mu H$  range.

The conventional planar integrated spiral inductor is shown in Fig. 16(a). Low resistivity Cu layer with increased thickness is adopted to reduce inductor parasitic resistance. Additional thick isolation layer, such as low  $\kappa$  BCB material, is deposited to separate inductor from substrate to reduce the losses. This method is relatively simple but the realized inductance is low to several nH [72]. Fig. 16(b) shows the integrated inductors on Si interposer, which can provide small-size inductors with inductance up to 80 nH. The capacitors can be integrated on Si interposer as well. However, the thickness of inductor metal is limited due to the interposer volume [73].

Fig. 16(c) demonstrates the silicon-embedded coreless power inductor. The inductor can be fabricated in the substrate layer and connected to the front side through vias. Alternatively the coreless spiral inductors can be embedded in a silicon interposer and connected with other chips such as

FIGURE 16. Schematics of (a) planar spiral inductor, (b) integrated inductor on Si interposer, (c) substrate embedded coreless power inductor, (d) Interposer embedded coreless inductor, (e) through silicon via (TSV) inductor and (f) bond-wire inductor.

GaN HEMTs through the front-side metal routing and vias as show in Fig. 16(d). The inductance can be up to several  $\mu$ H and the size of the system can be reduced by 5 times compared to the discrete counterparts [74]–[76].

Fig. 16(e) and (f) illustrate the reported through-siliconvia (TSV) inductor in a 3D integrated circuit and bondwire inductor, respectively. The fabrication techniques are compatible with GaN HEMT process, however, the realized inductance is still small for DC-DC converters [77], [78].

TABLE 2. Integrated converters using normally-OFF HEMT technology.

| Inductor type                                  | inductance | frequency | Quality | author                         |

|------------------------------------------------|------------|-----------|---------|--------------------------------|

|                                                |            |           | factor  |                                |

| Planar spiral inductor                         | 0.5 nH     | 2.4 GHz   | 45      | ASEI [72]                      |

| Integrated inductors on Si interposer          | 80 nH      | 36 MHz    | -       | Univ. of<br>Tokyo [73]         |

| Substrate embedded                             | 13.1 nH    | 100 MHz   | 3.9     | HKUST<br>[74]                  |

| coreless power inductor                        | 2-4 μΗ     | 2-5 MHz   | 18-23   | HKUST<br>[75]                  |

| Interposer -<br>embedded coreless<br>inductors | 4.2 μΗ     | 10 MHz    | -       | HKUST<br>[76]                  |

| TSV inductors                                  | 1.73 nH    | 200 MHz   | 6.1     | Univ. of<br>Notre<br>Dame [79] |

| Bond-wire inductors                            | 450 nH     | 5 MHz     | -       | UCF [78]                       |

The reported performance of integrated inductors is summarized in Table 2. Inductance values are still in nH to  $\mu$ H range with Q factor below 50. Especially the embedded coreless power inductor technique can realize inductance in the range of  $\mu$ H, which is a promising solution for integration of large value inductors in power converter ICs.

#### **B. INTEGRATED DC-DC CONVERTERS**

Achieving higher operation efficiency to reduce losses during power conversion is one of the key concerns in power DC-DC converters. The research groups and industry leading companies have first time switched to GaN solution to pursue higher performance. The discrete approach using discrete GaN switches has shown great improvement in converter operation frequency and efficiency. The controller, protector and driver are dedicated Si-based ICs, which are mounted on the same PCB with GaN switches and passive components. Since 2007, converters with GaN normally-ON HEMT as high-side switch and SiC-SBD as low-side switch have demonstrated efficiency up to 97.8 % at MHz range [80]. With normally-OFF HEMT as high-side switch, Transphorm realizes a 3kW, 99 % converter at 100 kHz [81]. When using GaN SBD as low-side switch, the converter shows an efficiency of 98.5 % at 500 kHz and 500 W condition [82]. Lots of works adopt normally-OFF half-bridge structure, the high efficiency of 98.8 % is realized at 50 kHz by University of Southern Denmark [83] and high output power of 3.3 kW is realized at 300 kHz by Fudan University [84]. These cases have substantially shown the advantages of GaN based discrete DC-DC converters.

Further exploiting the properties of GaN devices, the road of integration starts. The integrated GaN converters are reviewed in terms of the fabrication technology of smart power IC platforms.

# 1) COMMERCIAL MMIC TECHNOLOGY

As stated in Section I and III, DC-DC converters for onchip power supply of PAs, or for switching mode power amplification can be fabricated through the GaN MMIC technology. Table 3 lists the operation condition and performance of the reported converters using commercial MMIC process platforms.

TABLE 3. Integrated converters using commercial MMIC technology.

| Converter topology  | Technology         | Max<br>efficiency | Max<br>freq. | Max<br>power | Authors                      |

|---------------------|--------------------|-------------------|--------------|--------------|------------------------------|

| Boost               | 0.25-μm<br>GaN/SiC | 34%               | 680<br>MHz   | 2.2 W        | MIT<br>[85]                  |

| Buck                | 0.15 μm            | 78%               | 246<br>MHz   | -            | Mitsubishi<br>[86]           |

| Synchronous<br>buck | 0.15 um<br>GaN/SiC | 90%               | 100<br>MHz   | 5 W          | Univ. of<br>Colorado<br>[23] |

| Synchronous<br>buck | 0.15 μm<br>GaN/SiC | 90%               | 100<br>MHz   | 7 W          | Univ. of<br>Colorado<br>[87] |

In Table 3, the converters can operate at hundreds of MHz with high efficiency. Both buck and boost converters have been demonstrated. However the converters developed through this technology are mostly aimed at on-chip power supply for envelope tracking PAs. This limited application is related with the small gate length and relatively lower device breakdown voltage and power handling capability than

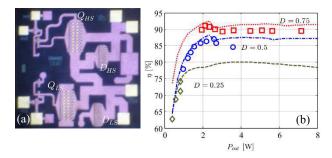

FIGURE 17. (a) Optical image of the integrated half-bridge with integrated gate driver; (b) efficiency versus output of the integrated buck converter [22].

AlGaN/GaN power MIS-HEMTs. Fig. 17 demonstrates the optical image and efficiency curves of an example integrated half-bridge converter by Zhang et al. [22]. The curvature of metal routes clearly indicates the transmission line in the MMIC process. The high efficiency over 90 % verifies the advantage of GaN based integrated converters. In order to accommodate the high power, high frequency and high efficiency power conversions, DC-DC power converter are switching to GaN smart power IC platforms with normally-OFF power devices.

# 2) NORMALLY-OFF HEMT TECHNOLOGY

The conventional normally-OFF technologies which are feasible for device integration have been discussed in Fig. 13. The normally-OFF devices provide fault-safe operation and ease the design of gate driver. Additionally the gate dielectric can be included in devices to form MIS-HEMTs, which can reduce the gate leakage and enlarge the gate voltage swing. Table 4 lists the publications with integrated converters using normally-OFF technologies.

**TABLE 4.** Integrated converters using normally-OFF HEMT technology.

| Converter topology             | Technology            | Max<br>efficiency | Max<br>freq. | Max<br>power | Authors                      |

|--------------------------------|-----------------------|-------------------|--------------|--------------|------------------------------|

| Boost                          | F-ion<br>implantation | 84%               | 1<br>MHz     | -            | HKUST<br>[39]                |

| Half-<br>bridge with<br>driver | P-AlGaN<br>cap layer  | 86.6%             | 2<br>MHz     | 10.8 W       | Panasonic<br>[42]            |

| Half-<br>bridge with<br>driver | P-AlGaN<br>cap layer  | 84.9%             | 3<br>MHz     | 10.8 W       | Panasonic<br>[88]            |

| Half-<br>bridge with<br>driver | P-GaN cap<br>layer    | -                 | 500<br>KHz   | 0.1 W        | IMEC<br>[89]                 |

| Half-<br>bridge with<br>driver | Gate recess           | 95%               | 400<br>MHz   | 16 W         | Univ. of<br>Colorado<br>[90] |

| Boost with driver              | Gate recess           | -                 | 100<br>kHz   | -            | XJTLU<br>[58]                |

| Buck with driver               | Gate recess           | -                 | 100<br>kHz   | 0.2 W        | NUS<br>[36, 91]              |

Normally-OFF technology is promising to assist GaN integrated converters to work at MHz range with efficiency up to nighty percent. The output power at current stage is less than

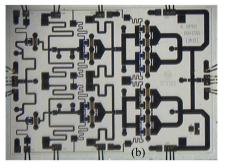

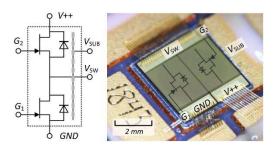

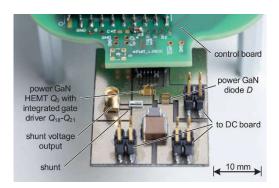

DC-DC converters with discrete GaN power switches, which could be due to the limited total gate width of integrated power stages. Larger power stages are integrated on 200-mm GaN IC platforms now. Ujita et al. has designed a fully integrated GaN-based power IC including gate drivers for highefficiency DC-DC conversion [88]. The 12-1.8 V DC-DC converter IC demonstrates a maximum 3 MHz frequency, which is far beyond the limit of Si and can reduce 60% of system volume. Fraunhofer IAF has realized an integrated half-bridge converter as shown in Fig. 18, which can be switched at 3 MHz with a input/output of 400/200 V, and a current 1.15 A [92], [93].

FIGURE 18. Schematic structure and optical image of the integrated half-bridge by Fraunhofer IAF [92], [93].

In the aspects of GaN integration in companies, Navitas and Dialog have lunched the GaN power IC products. Both of these two companies cooperated with TSMC on the practical fabrication. The high-frequency operation of GaN based circuit induces excessive parasitic from wire bonding, which has been reduced by TSMC's integration of peripheral circuits with low-voltage devices into CMOS-compatible 100/650 V enhancement GaN device platform. Functional blocks including control, clock, pre-gate driver, ESD protection circuits have been demonstrated using 12 V E/D-HEMTs, rectifiers. 2DEG resistors and capacitors [9]. Now Navitas' NV6115 can offer high-efficiency 650 V, 160 m $\Omega$ power switches with integrated gate drive and logic circuits, which can enable high switching speed, power efficiency and power density. Dialog's DA8801 can offer a half bridge of 650 V, 500 m $\Omega$  power switches with integrated analog, logic, and protection.

# V. GAN POWER INTEGRATION ROAD AHEAD

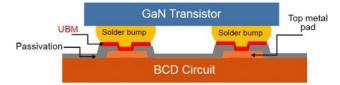

GaN integration can take the power conversion to where silicon power cannot go [94]. More technologies in Si electronics have been applied on the GaN integration. The dedicated Si CMOS gate drivers can be packaged in the same case or directly bonded with GaN in 3-dimension. The heterogeneous integration of GaN and Bipolar-CMOS-DMOS (BCD) has been shown by GLOBALFOUNDRIES "GaN2BCD" technology in [95], [96]. The driver circuits can be dedicatedly designed and fabricated in BCD process, and then integrated with GaN power devices using the die-to-wafer transfer (D2W) as shown in the schematic in Fig. 19.

FIGURE 19. Schematic cross-section of the "GaN2BCD" developed by GLOBALFOUNDRIES [95]. The UBM is the abbreviation of under-bumper-metallization.

An open-loop 3.3-70 V boost converter is demonstrated. The 70.3 % efficiency is realized at 49.5 kHz and 1.68 W [95].

Another novel approach is the CMOS gate driver flip-chip assembled with GaN devices together on the IPD substrate, which minimizes the parasitic effects caused by bonding wires [97]. The PCB embedded inductor is also a solution to low parasitic IPDs [98].

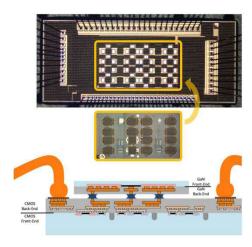

Die bonding between CMOS and GaN ICs to form the integrated converter is one of the solutions provided by [99]. The half-bridge switches are AlGaN/GaN HEMTs, while the drivers and other functional circuits are implemented in a 0.18  $\mu$ m CMOS platform. The GaN and CMOS dies are face-to-face bonded to reduce inductive parasitics. Fig. 20 shows the optical images of silicon die (top), GaN die (middle), and the face-to-face bonding illustration (bottom). The converter demonstrates the 8-to-1 V, 40 MHz and 76 % efficiency opeartion [99].

FIGURE 20. Optical images of silicon die, GaN die and face-to-face bonding illustration by Aklimi et al. [99].

The integration on Direct Bonded Copper (DBC) has the GaN power device bonded and other components soldered in the way as shown in Fig. 21 by Fraunhofer IAF in 2019 [100]. A prototype 200-to-100 V, 500 kHz, 100 W, 97% efficiency converter is designed and characterized.

More approaches are being proposed. However, the GaN integration firstly should be established on a stable platform with well calibrated and modelled active and passive components. So the performance of the GaN power ICs can be reliably predicted. The technology of discrete GaN devices

FIGURE 21. Optical image of the power module prototype with GaN power transistor, power diode and passive components mounted on the DBC substrate [100].

is improving fast and the GaN power integration should be updated simultaneously. In order to exploit the most of theoretical GaN performance, GaN power integration road follows the path of Si power IC, but on a fast lane.

### VI. CONCLUSION

GaN power integration is the intuitive and effective solution for high frequency and high efficiency power applications including microwave and power conversion. The GaN integration road is reviewed in terms of the technology and application. With the rapid development of microwave communication, the GaN power integration technology based on MMIC platforms are significantly advanced. The  $0.25/0.15/0.1~\mu m$  processes have been the major choices and highly scaled integration processes have been demonstrated. The state-of-the-art performance of the MMIC PAs is reviewed. The GaN power integration has supported the markets including mobile devices, communications infrastructure and aerospace applications.

On the other hand, smart GaN power IC platforms boost the high efficiency DC-DC power conversions. Numbers of platforms are constructed based on novel device technologies. Demonstrations of high frequency (>1 MHz) and high efficiency (>95 %) DC-DC converters with various kinds of topology have been summarized. Novel integration schemes and methods are introduced to stimulate new thoughts on GaN power integration.

The future of GaN power integration is exciting when considering the full potential of GaN electronics. However, the road is still tough. This review on GaN power integration in terms of high frequency and efficiency power applications could provide some up-to-date information and shed some light on the way.

### **REFERENCES**

- P. Gueguen, "How power electronics will reshape to meet the 21<sup>st</sup> century challenges?" in *Proc. IEEE 27th Int. Symp. Power Semiconductor Devices IC's (ISPSD)*, May 2015, pp. 17–20.

- [2] B. Murari and D. Rossi, "Power ICs in motor control," in *Proc. 8th Int. Symp. Power Semiconductor Devices ICs (ISPSD)*, Dec. 2002, pp. 29–32.

- [3] B. Murari, F. Bertotti, G. A. Vignola, and A. Andreini, *Smart Power ICs: Technologies and Applications*. Berlin, Germany: Springer, 2002.

- [4] B. Baliga, "An overview of smart power technology," *IEEE Trans. Electron Devices*, vol. 38, no. 7, pp. 1568–1575, Jul. 1991.

- [5] T. Letavic, E. Arnold, M. Simpson, R. Aquino, H. Bhimnathwala, R. Egloff, A. Emmerik, S. Wong, and S. Mukherjee, "High performance 600 V smart power technology based on thin layer silicon-on-insulator," in *Proc. 9th Int. Symp. Power Semiconductor Devices IC's*, Nov. 2002, pp. 49–52.

- [6] T. P. Chow, I. Omura, M. Higashiwaki, H. Kawarada, and V. Pala, "Smart power devices and ICs using GaAs and wide and extreme bandgap semiconductors," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 856–873, Mar 2017

- [7] K.-Y. Wong, W. Chen, X. Liu, C. Zhou, and K. J. Chen, "GaN smart power IC technology," *Phys. Status Solidi B*, vol. 247, no. 7, pp. 1732–1734, May 2010.

- [8] U. Mishra, P. Parikh, and Y.-F. Wu, "AlGaN/GaN HEMTs—An overview of device operation and applications," *Proc. IEEE*, vol. 90, no. 6, pp. 1022–1031, Jun. 2002.

- [9] C. Tsai, Y. Wang, M. Kwan, P. Chen, F. Yao, and S. Liu, "Smart GaN platform: Performance & challenges," in *IEDM Tech. Dig.*, 2017, pp. 33.1.1–33.1.4.

- [10] K. Chen, "GaN smart power chip technology," in Proc. IEEE Int. Conf. Electron Devices Solid-State Circuits (EDSSC), Dec. 2009, pp. 403–407.

- [11] R. Pengelly and J. Turner, "Monolithic broadband GaAs FET amplifiers," *Electron. Lett.*, vol. 12, no. 10, p. 251, 1976.

- [12] A. Pereira, S. Albahrani, A. Parker, G. Town, and M. Heimlich, "MMIC process for integrated power converters," in *Proc. IEEE Tencon*, Sydney, NSW, Australia, Apr. 2013.

- [13] N. Otsuka, Y. Kawai, and S. Nagai, "Recent progress in GaN devices for power and integrated circuit," in *Proc. IEEE 12th Int. Conf. ASIC* (ASICON), Oct. 2017, pp. 928–931.

- [14] R. S. Pengelly, S. M. Wood, J. W. Milligan, S. T. Sheppard, and W. L. Pribble, "A review of GaN on SiC high electron-mobility power transistors and MMICs," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 6, pp. 1764–1783, Jun. 2012.

- [15] M. Micovic, D. F. Brown, D. Regan, J. Wong, Y. Tang, F. Herrault, D. Santos, S. D. Burnham, J. Tai, E. Prophet, I. Khalaf, C. Mcguire, H. Bracamontes, H. Fung, A. K. Kurdoghlian, and A. Schmitz, "High frequency GaN HEMTs for RF MMIC applications," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, Dec. 2016, pp. 3.3.1–3.3. 4.

- [16] A. Hassan, M. Ali, A. Trigui, Y. Savaria, and M. Sawan, "A GaN-based wireless monitoring system for high-temperature applications," *Sensors*, vol. 19, no. 8, p. 1785, Apr. 2019.

- [17] H. L. X. Zhu, X. Zhu, C. C. Boon, X. Yi, M. D. Mao, and W. L. Yang, "Design of ultra-low phase noise and high power integrated oscillator in 0.25 μm GaN-on-SiC HEMT technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 24, pp. 120–122, Feb. 2014.

- [18] T. Kuwabara, N. Tawa, Y. Tone, and T. Kaneko, "A 28 GHz 480 elements digital AAS using GaN HEMT amplifiers with 68 dBm EIRP for 5G longrange base station applications," in *Proc. IEEE Compound Semiconduc*tor Integr. Circuit Symp. (CSICS), Oct. 2017, pp. 1–4.

- [19] R. Weber, D. Schwantuschke, P. Bruckner, R. Quay, F. Van Raay, and O. Ambacher, "A 92 GHz GaN HEMT voltage-controlled oscillator MMIC," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2014, pp. 1–4.

- [20] I. Ramos and Z. Popovic, "A fully monolithically integrated 4.6 GHz DC–DC converter," in *IEEE MTT-S Int. Microw. Symp. Dig.*, May 2016, pp. 1–4.

- [21] V. Mehrotra, A. Arias, C. Neft, J. Bergman, M. Urteaga, and B. Brar, "GaN HEMT-based>1-GHz speed low-side gate driver and switch monolithic process for 865-MHz power conversion applications," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 4, no. 3, pp. 918–925, Sep. 2016.

- [22] Y. Zhang, M. Rodríguez, and D. Maksimović, "Very high frequency PWM buck converters using monolithic GaN half-bridge power stages with integrated gate drivers," *IEEE Trans. Power Electron.*, vol. 31, no. 11, pp. 7926–7942, Nov. 2016.

- [23] J. A. Garcia, M. N. Ruiz, D. Vegas, M. Pampin, and A. Mediavilla, "UHF power conversion with GaN HEMT class-E<sup>2</sup> topologies," in *Proc. IEEE Compound Semiconductor Integr. Circuit Symp. (CSICS)*, Oct. 2017, pp. 1–4.

- [24] J. A. Garcia, R. Marante, and M. de las Nieves Ruiz Lavin, "GaN HEMT class-E<sup>2</sup> resonant topologies for UHF DC/DC power conversion," *IEEE Trans. Microw. Theory Techn.*, vol. 60, pp. 4220–4229, Dec. 2012.

- [25] R. Sun, Y. C. Liang, Y.-C. Yeo, Y.-H. Wang, and C. Zhao, "Design of power integrated circuits in full AlGaN/GaN MIS-HEMT configuration for power conversion," *Phys. Status Solidi A*, vol. 214, no. 3, Mar. 2017, Art. no. 1600562.

- [26] W. Saito, Y. Takada, M. Kuraguchi, K. Tsuda, and I. Omura, "Recessed-gate structure approach toward normally off high-voltage AlGaN/GaN HEMT for power electronics applications," *IEEE Trans. Electron Devices*, vol. 53, no. 2, pp. 356–362, Feb. 2006.

- [27] Y. Cai, Y. Zhou, K. Lau, and K. Chen, "Control of threshold voltage of AlGaN/GaN HEMTs by fluoride-based plasma treatment: From depletion mode to enhancement mode," *IEEE Trans. Electron Devices*, vol. 53, no. 9, pp. 2207–2215, Sep. 2006.

- [28] Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, and M. Yanagihara, "A normally-off AlGaN/GaN transistor with R<sub>on</sub>A=2.6mΩcm<sup>2</sup> and BVds=640 V using conductivity modulation," in *IEDM Tech. Dig.*, 2006, pp. 1–4.

- [29] K. J. Chen, O. Häberlen, A. Lidow, C. L. Tsai, T. Ueda, Y. Uemoto, and Y. Wu, "GaN-on-Si power technology: Devices and applications," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 779–795, Mar. 2017.

- [30] T. Ueda, M. Ishida, T. Tanaka, and D. Ueda, "GaN transistors on Si for switching and high-frequency applications," *Jpn. J. Appl. Phys.*, vol. 53, no. 10, Oct. 2014, Art. no. 100214.

- [31] E. A. Jones, F. F. Wang, and D. Costinett, "Review of commercial GaN power devices and GaN-based converter design challenges," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 4, no. 3, pp. 707–719, Sep. 2016.

- [32] G. Tang, A. M. H. Kwan, R. K. Y. Wong, J. Lei, R. Y. Su, F. W. Yao, Y. M. Lin, J. L. Yu, T. Tsai, H. C. Tuan, A. Kalnitsky, and K. J. Chen, "Digital integrated circuits on an E-mode GaN power HEMT platform," *IEEE Electron Device Lett.*, vol. 38, no. 9, pp. 1282–1285, Sep. 2017.

- [33] K.-T. Lee, C. Bayram, D. Piedra, E. Sprogis, H. Deligianni, B. Krishnan, G. Papasouliotis, A. Paranjpe, E. Aklimi, K. Shepard, T. Palacios, and D. Sadana, "GaN devices on a 200 mm Si platform targeting heterogeneous integration," *IEEE Electron Device Lett.*, vol. 38, no. 8, pp. 1094–1096, Aug. 2017.

- [34] A. Nakajima, S.-I. Nishizawa, H. Ohashi, R. Kayanuma, K. Tsutsui, S. Kubota, K. Kakushima, H. Wakabayashi, and H. Iwai, "GaN-based monolithic power integrated circuit technology with wide operating temperature on polarization-junction platform," in *Proc. IEEE 27th Int. Symp. Power Semiconductor Devices IC's (ISPSD)*, May 2015, pp. 357–360.

- [35] A. Nakajima, S.-I. Nishizawa, S. Kubota, R. Kayanuma, K. Tsutsui, H. Ohashi, K. Kakushima, H. Wakabayashi, and H. Iwai, "An overview of GaN-based monolithic power integrated circuit technology on polarization-junction platform," in *Proc. IEEE Compound Semiconduc*tor Integr. Circuit Symp. (CSICS), Oct. 2015, pp. 1–4.

- [36] R. Sun, Y. C. Liang, Y.-C. Yeo, C. Zhao, W. Chen, and B. Zhang, "Development of GaN power IC platform and all GaN DC–DC buck converter IC," in *Proc. 31st Int. Symp. Power Semiconductor Devices ICs (ISPSD)*, May 2019, pp. 271–274.

- [37] A. M. H. Kwan, Y. Guan, X. Liu, and K. J. Chen, "A highly linear integrated temperature sensor on a GaN smart power IC platform," *IEEE Trans. Electron Devices*, vol. 61, no. 8, pp. 2970–2976, Aug. 2014.

- [38] Q. Jiang, C. Liu, Y. Lu, and K. J. Chen, "1.4-kV AlGaN/GaN HEMTs on a GaN-on-SOI platform," *IEEE Electron Device Lett.*, vol. 34, no. 3, pp. 357–359, Mar. 2013.

- [39] W. Chen, K.-Y. Wong, and K. Chen, "Single-chip boost converter using monolithically integrated AlGaN/GaN lateral field-effect rectifier and normally off HEMT," *IEEE Electron Device Lett.*, vol. 30, no. 5, pp. 430–432, May 2009.

- [40] W. Chen, K.-Y. Wong, and K. J. Chen, "Monolithic integration of lateral field-effect rectifier with normally-off HEMT for GaN-on-Si switch-mode power supply converters," in *IEDM Tech. Dig.*, Dec. 2008, pp. 1–4.

- [41] T. Morita, S. Ujita, H. Umeda, Y. Kinoshita, S. Tamura, Y. Anda, T. Ueda, and T. Tanaka, "GaN gate injection transistor with integrated Si Schottky barrier diode for highly efficient DC–DC converters," in *IEDM Tech. Dig.*, Dec. 2012, pp. 7.2.1–7.2.4.

- [42] S. Ujita, Y. Kinoshita, H. Umeda, T. Morita, S. Tamura, M. Ishida, and T. Ueda, "A compact GaN-based DC-DC converter IC with high-speed gate drivers enabling high efficiencies," in *Proc. IEEE 26th Int. Symp. Power Semiconductor Devices IC's (ISPSD)*, Jun. 2014, pp. 51–54.

- [43] Y.-H. Wang, Y. C. Liang, G. S. Samudra, B.-J. Huang, Y.-C. Liao, C.-F. Huang, W.-H. Kuo, and G.-Q. Lo, "High output swing monolithic inverter with E-D mode MIS-HEMTs for GaN power integrated circuits," in *Proc. IEEE 11th Int. Conf. Power Electron. Drive Syst.*, Jun. 2015, pp. 585–588.

- [44] X. Liu and K. J. Chen, "GaN single-polarity power supply bootstrapped comparator for high-temperature electronics," *IEEE Electron Device Lett.*, vol. 32, no. 1, pp. 27–29, Jan. 2011.

- [45] K.-Y. Wong, W. Chen, and K. J. Chen, "Integrated voltage reference generator for GaN smart power chip technology," *IEEE Trans. Electron Devices*, vol. 57, no. 4, pp. 952–955, Apr. 2010.

- [46] H. Wang, A. M. H. Kwan, Q. Jiang, and K. J. Chen, "A GaN pulse width modulation integrated circuit for GaN power converters," *IEEE Trans. Electron Devices*, vol. 62, no. 4, pp. 1143–1149, Apr. 2015.

- [47] O. Ambacher, J. Smart, J. R. Shealy, N. G. Weimann, K. Chu, M. Murphy, W. J. Schaff, L. F. Eastman, R. Dimitrov, L. Wittmer, M. Stutzmann, W. Rieger, and J. Hilsenbeck, "Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- and Ga-face AlGaN/GaN heterostructures," J. Appl. Phys., vol. 85, no. 6, pp. 3222–3233, Mar. 1999.

- [48] W. Shaobing, G. Jianfeng, W. Weibo, and Z. Junyun, "W-band MMIC PA with ultrahigh power density in 100-nm AlGaN/GaN technology," *IEEE Trans. Electron Devices*, vol. 63, no. 10, pp. 3882–3886, Oct. 2016.

- [49] Y. Xin, W. Chen, R. Sun, Y. Shi, C. Liu, Y. Xia, F. Wang, M. Li, J. Li, Q. Zhou, X. Deng, T. Chen, Z. Li, and B. Zhang, "Analytical switching loss model for GaN-based control switch and synchronous rectifier in low-voltage buck converters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 3, pp. 1485–1495, Sep. 2019.

- [50] X. Huili, Y. Dora, A. Chini, S. Heikman, S. Keller, and U. K. Mishra, "High breakdown voltage AlGaN-GaN HEMTs achieved by multiple field plates," *IEEE Electron Device Lett.*, vol. 25, no. 4, pp. 161–163, Apr. 2004.

- [51] S. Zhang, K. Wei, X. Ma, Y. Zhang, M. Asif, G. Liu, S. Huang, Y. Zheng, X. Wang, J. Niu, T. Lei, and X. Liu, "Millimeter-wave AlGaN/GaN HEMTs breakdown voltage enhancement by an air-bridge recessed source field plate (RSFP)," *Solid-State Electron.*, vol. 160, Oct. 2019, Art. no. 107629.

- [52] J. Wong, K. Shinohara, A. L. Corrion, D. F. Brown, Z. Carlos, A. Williams, Y. Tang, J. F. Robinson, I. Khalaf, H. Fung, A. Schmitz, T. Oh, S. Kim, S. Chen, S. Burnham, A. Margomenos, and M. Micovic, "Novel asymmetric slant field plate technology for high-speed low-dynamic ron E/D-mode GaN HEMTs," *IEEE Electron Device Lett.*, vol. 38, no. 1, pp. 95–98, Jan. 2017.

- [53] Y. Dora, A. Chakraborty, L. Mccarthy, S. Keller, S. Denbaars, and U. Mishra, "High breakdown voltage achieved on AlGaN/GaN HEMTs with integrated slant field plates," *IEEE Electron Device Lett.*, vol. 27, no. 9, pp. 713–715, Sep. 2006.

- [54] M. Rocchi, "Advanced III/V MMIC process roadmaps for terahertz applications," in *Proc. IEEE MTT-S Int. Microw. Workshop Ser. Adv. Mater. Process. RF THz Appl. (IMWS-AMP)*, Jul. 2016, pp. 1–2.

- [55] S. M. Sze and K. K. Ng, Physics of Semiconductor Devices. Hoboken, NJ, USA: Wiley, 2006.

- [56] Y. S. Noh and I. B. Yom, "A linear GaN high power amplifier MMIC for Ka-band satellite communications," *IEEE Microw. Wireless Compon. Lett.*, vol. 26, no. 8, pp. 619–621, Aug. 2016.

- [57] H. Kattelus, J. Tandon, and M.-A. Nicolet, "Characterization of reacted ohmic contacts to GaAs," *Solid-State Electron.*, vol. 29, no. 9, pp. 903–905, Sep. 1986.

- [58] M. Cui, Q. L. Bu, Y. T. Cai, R. Z. Sun, W. Liu, and H. Q. Wen, "Monolithic integration design of GaN-based power chip including gate driver for high-temperature DC–DC converters," *Jpn. J. Appl. Phys.*, vol. 58, p. 11, May 2019, Art. no. 056505.

- [59] Y. Cai, Z. Q. Cheng, W. C. W. Tang, K. M. Lau, and K. J. Chen, "Monolithically integrated enhancement/depletion-mode AlGaN/GaN HEMT inverters and ring oscillators using CF<sub>4</sub> plasma treatment," *IEEE Trans. Electron Devices*, vol. 53, no. 9, pp. 2223–2230, Sep. 2006.

- [60] Y. Yamashita, S. Stoffels, N. Posthuma, S. Decoutere, K. Kobayashi, and Ieee, "Monolithically integrated E-mode GaN-on-SOI gate driver with power GaN-HEMT for MHz-switching," in *Proc. IEEE 6th Work-shop Wide Bandgap Power Devices Appl. (WiPDA)*, Atlanta, GA, USA, Oct./Nov. 2018.

- [61] D. Visalli, M. Van Hove, J. Derluyn, K. Cheng, S. Degroote, M. Leys, M. Germain, and G. Borghs, "High breakdown voltage in AlGaN/GaN/AlGaN double heterostructures grown on 4 inch Si substrates," *Phys. Status Solidi C*, vol. 6, no. S2, pp. S988–S991, Jun. 2009.

- [62] H. Boudinov, S. O. Kucheyev, J. S. Williams, C. Jagadish, and G. Li, "Electrical isolation of GaN by MeV ion irradiation," *Appl. Phys. Lett.*, vol. 78, no. 7, pp. 943–945, Feb. 2001.

- [63] C. F. Lo, T. S. Kang, L. Liu, C. Y. Chang, S. J. Pearton, I. I. Kravchenko, O. Laboutin, J. W. Johnson, and F. Ren, "Isolation blocking voltage of nitrogen ion-implanted AlGaN/GaN high electron mobility transistor structure," *Appl. Phys. Lett.*, vol. 97, no. 26, Dec. 2010, Art. no. 262116.

- [64] X. Li, M. Van Hove, M. Zhao, K. Geens, V.-P. Lempinen, J. Sormunen, G. Groeseneken, and S. Decoutere, "200 V enhancement-mode p-GaN HEMTs fabricated on 200 mm GaN-on-SOI with trench isolation for monolithic integration," *IEEE Electron Device Lett.*, vol. 38, no. 7, pp. 918–921, Jul. 2017.

- [65] L. S. Yu, D. J. Qiao, Q. J. Xing, S. S. Lau, K. S. Boutros, and J. M. Redwing, "Ni and Ti Schottky barriers on n-AlGaN grown on SiC substrates," Appl. Phys. Lett., vol. 73, no. 2, pp. 238–240, Jul. 1998.

- [66] M. Zhu, B. Song, M. Qi, Z. Hu, K. Nomoto, X. Yan, Y. Cao, W. Johnson, E. Kohn, D. Jena, and H. G. Xing, "1.9-kV AlGaN/GaN lateral Schottky barrier diodes on silicon," *IEEE Electron Device Lett.*, vol. 36, no. 4, pp. 375–377, Apr. 2015.

- [67] W. Chen, K.-Y. Wong, W. Huang, and K. J. Chen, "High-performance AlGaN/GaN lateral field-effect rectifiers compatible with high electron mobility transistors," *Appl. Phys. Lett.*, vol. 92, no. 25, Jun. 2008, Art. no. 253501.

- [68] Q. Zhou, Y. Jin, Y. Shi, J. Mou, X. Bao, B. Chen, and B. Zhang, "High reverse blocking and low onset voltage AlGaN/GaN-on-Si lateral power diode with MIS-gated hybrid anode," *IEEE Electron Device Lett.*, vol. 36, no. 7, pp. 660–662, Jul. 2015.

- [69] J. Ma, G. Kampitsis, P. Xiang, K. Cheng, and E. Matioli, "Multi-channel tri-gate GaN power Schottky diodes with low ON-resistance," *IEEE Electron Device Lett.*, vol. 40, no. 2, pp. 275–278, Feb. 2019.

- [70] A. M. H. Kwan, L. Xiaosen, and K. J. Chen, "Integrated gate-protected HEMTs and mixed-signal functional blocks for GaN smart power ICs," in *IEDM Tech. Dig.*, 2012, pp. 7.3.1–7.3.4.

- [71] S. Han, S. Park, J. Lee, J. Lim, and H. Cha, "AlGaN/GaN metal-oxide-semiconductor heterojunction field-effect transistor integrated with clamp circuit to enable normally-off operation," *IEEE Electron Device Lett.*, vol. 36, no. 6, pp. 540–542, Jun. 2015.

- [72] H.-A. Yang, C.-C. Wang, P.-J. Zheng, and W.-C. Wang, "On-chip high-Q inductor using wafer-level chip-scale package technology," in *Proc. Int. Microsyst., Packag., Assem. Circuits Technol.*, 2007, pp. 173–176.

- [73] K. Ishida, K. Takemura, K. Baba, M. Takamiya, and T. Sakurai, "3D stacked buck converter with 15μm thick spiral inductor on silicon interposer for fine-grain power-supply voltage control in SiP's," in *Proc. IEEE Int. 3D Syst. Integr. Conf. (DIC)*, Nov. 2010, pp. 1–4.

- [74] R. Wu and J. K. O. Sin, "A novel silicon-embedded coreless inductor for high-frequency power management applications," *IEEE Electron Device Lett.*, vol. 32, no. 1, pp. 60–62, Jan. 2011.

- [75] R. Wu, J. K. O. Sin, and C. P. Yue, "High-Q backside silicon-embedded inductor for power applications in μH and MHz Range," *IEEE Trans. Electron Devices*, vol. 60, no. 1, pp. 339–345, Jan. 2013.

- [76] Y. Ding, X. Fang, Y. Gao, Y. Cai, X. Qiu, P. K. T. Mok, S. W. R. Lee, K. M. Lau, and J. K. O. Sin, "A power inductor integration technology using a silicon interposer for DC–DC converter applications," in *Proc. IEEE 30th Int. Symp. Power Semiconductor Devices IC's (ISPSD)*, May 2018, pp. 347–350.

- [77] U. R. Tida, C. Zhuo, and Y. Shi, "Single-inductor-multiple-tier regulation: TSV-inductor-based on-chip buck converters for 3-D IC power delivery," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 27, no. 10, pp. 2305–2316, Jun. 2019.

- [78] H. Jia, J. Lu, X. Wang, K. Padmanabhan, and Z. J. Shen, "Integration of a monolithic buck converter power IC and bondwire inductors with ferrite epoxy glob cores," *IEEE Trans. Power Electron.*, vol. 26, no. 6, pp. 1627–1630, Jun. 2011.

- [79] U. R. Tida, C. Zhuo, and Y. Shi, "Novel through-silicon-via inductor-based on-chip DC–DC converter designs in 3D ICs," ACM J. Emerg. Technol. Comput. Syst., vol. 11, pp. 1–14, Nov. 2014.

- [80] Y. Wu, M. Jacob-Mitos, M. L. Moore, and S. Heikman, "A 97.8% efficient GaN HEMT boost converter with 300-W output power at 1 MHz," IEEE Electron Device Lett., vol. 29, no. 8, pp. 824–826, Aug. 2008.

- [81] Y.-F. Wu, J. Gritters, L. Shen, R. P. Smith, and B. Swenson, "KV-class GaN-on-Si HEMTs enabling 99% efficiency converter at 800 V and 100 kHz," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2634–2637, Jun. 2014.

- [82] R. Mitova, R. Ghosh, U. Mhaskar, D. Klikic, M.-X. Wang, and A. Dentella, "Investigations of 600-V GaN HEMT and GaN diode for power converter applications," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2441–2452, May 2014.

- [83] R. Ramachandran and M. Nymand, "A 98.8% efficient bidirectional full-bridge isolated DC–DC GaN converter," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Mar. 2016, pp. 609–614.

- [84] G. Liu, D. Li, Y. Jang, and J. Zhang, "Over 300 kHz GaN device based resonant bidirectional DCDC converter with integrated magnetics," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Mar. 2016, pp. 595–600.

- [85] P. Choi, U. Radhakrishna, C.-C. Boon, D. Antoniadis, and L.-S. Peh, "A fully integrated inductor-based GaN boost converter with self-generated switching signal for vehicular applications," *IEEE Trans. Power Electron.*, vol. 31, no. 8, pp. 5365–5368, Aug. 2016.

- [86] A. Seidel, B. Wicht, and Ieee, "A 1.3 A gate driver for GaN with fully integrated gate charge buffer capacitor delivering 11nC enabled by highvoltage energy storing," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, p. 432.

- [87] D. Maksimovic, Y. Zhang, and M. Rodriguez, "Monolithic very high frequency GaN switched-mode power converters," presented at the IEEE Custom Integr. Circuits Conf., New York, NY, USA, Sep. 2015.

- [88] S. Ujita, Y. Kinoshita, H. Umeda, T. Morita, K. Kaibara, S. Tamura, M. Ishida, and T. Ueda, "A fully integrated GaN-based power IC including gate drivers for high-efficiency DC–DC Converters," in *Proc. IEEE Symp. VLSI Circuits (VLSI-Circuits)*, Jun. 2016, pp. 1–2.

- [89] X. Li, K. Geens, W. Guo, S. You, M. Zhao, and D. Fahle, "Demonstration of GaN integrated half-bridge with on-chip drivers on 200-mm engineered substrates," *IEEE Electron Device Lett.*, vol. 40, no. 9, pp. 1499–1502, Sep. 2019.

- [90] A. Sepahvand, Y. Z. Zhang, and D. Maksimovic, "High efficiency 20–400 MHz PWM converters using air-core inductors and monolithic power stages in a normally-off GaN process," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Mar. 2016, pp. 580–586.

- [91] R. Sun, Y. C. Liang, Y.-C. Yeo, Y.-H. Wang, and C. Zhao, "Design of DC–DC buck converter with integrated over-current protection based on power AlGaN/GaN MIS-HEMT configuration," in Proc. Compound Semiconductor Week (CSW), 28th Int. Conf. Indium Phosph. Rel. Mater. (IPRM), 43rd Int. Symp. Compound Semiconductors (ISCS), Jun. 2016, p. 1.

- [92] R. Reiner, P. Waltereit, B. Weiss, S. Moench, M. Wespel, S. Müller, R. Quay, and O. Ambacher, "Monolithically integrated power circuits in high-voltage GaN-on-Si heterojunction technology," *IET Power Electron.*, vol. 11, pp. 681–688, Sep. 2018.

- [93] B. Weiss, R. Reiner, P. Waltereit, R. Quay, O. Ambacher, A. Sepahvand, and D. Maksimovic, "Soft-switching 3 MHz converter based on monolithically integrated half-bridge GaN-chip," in *Proc. IEEE 4th Workshop Wide Bandgap Power Devices Appl. (WiPDA)*, Nov. 2016, pp. 215–219.

- [94] A. Lidow, "Gallium nitride integration: Going where silicon power can't go [expert view]," *IEEE Power Electron. Mag.*, vol. 5, no. 3, pp. 70–72, Sep. 2018.

- [95] F. Meng, D. Disney, B. Liu, Y. B. Volkan, A. Zhou, and Z. Liang, "Heterogeneous integration of GaN and BCD technologies and its applications to high conversion-ratio DC–DC boost converter IC," *IEEE Trans. Power Electron.*, vol. 34, no. 3, pp. 1993–1996, Mar. 2019.

- [96] M. Soh, T. Teo, S. Selvaraj, L. Peng, D. Disney, and K. Yeo, "Heterogeneous integration of GaN and BCD technologies," *Electronics*, vol. 8, no. 3, p. 351, Mar. 2019.

- [97] K. Joshin, K. Makiyama, S. Ozaki, T. Ohki, N. Okamoto, Y. Niida, M. Sato, S. Masuda, and K. Watanabe, "Millimeter-wave GaN HEMT for power amplifier applications," *IEICE Trans. Electron.*, vol. E97.C, no. 10, pp. 923–929, 2014.

- [98] R. Chen and S.-Y. Yu, "A high-efficiency high-power-density 1 MHz LLC converter with GaN devices and integrated transformer," in Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC), Mar. 2018, pp. 791–796.

- [99] E. Aklimi, D. Piedra, K. Tien, T. Palacios, and K. L. Shepard, "Hybrid CMOS/GaN 40-MHz maximum 20-V input DC–DC multiphase buck converter," *IEEE J. Solid-State Circuits*, vol. 52, no. 6, pp. 1618–1627, Mar. 2017.

[100] M. Basler, S. Moench, R. Reiner, P. Waltereit, R. Quay, and I. Kallfass, "A GaN-on-Si-based logic, driver and DC-DC converter circuit with closed-loop peak current-mode control," in *Proc. Int. Exhib. Conf. Power Electron., Intell. Motion, Renew. Energy Energy Manage.*, 2019, pp. 1–6.

**RUIZE SUN** (Member, IEEE) received the B.S. and M.S. degrees from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2011 and 2014, respectively, and the Ph.D. degree in electrical and computer engineering from the National University of Singapore, Singapore, in 2018. He is currently a Postdoctoral Research Fellow with UESTC. His current research interests include GaN devices and power integration technology.

**JINGXUE LAI** received the B.S. degree in microelectronics and solid-state electronics from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2019, where she is currently pursuing the M.S. degree in electronic science and technology. Her current research interests include GaN electronics and integration technologies.

**WANJUN CHEN** (Senior Member, IEEE) received the Ph.D. degree in microelectronics and solid-state electronics from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2007. He is currently a Professor with UESTC, where he is also the Vice Dean of the School of Electronic Science and Engineering. His current research interests include novel power semiconductor devices and technologies.

**BO ZHANG** (Senior Member, IEEE) received the B.S. degree in electronic engineering from the Beijing Institute of Technology, Beijing, China, in 1985, and the M.S. degree in electronic engineering from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 1988. He was the Vice Dean with the School of Microelectronics and Solid-State Electronics, UESTC. He is currently a Professor with UESTC, where he is also the Director with the

Center for Integrated Circuits. He has authored or coauthored over 400 publications in peer-reviewed journals and international conference. He was the TPC member of International Symposium of Power Semiconductor Devices and ICs (ISPSD), from 2010 to 2014. He was awarded the Second Prize of State Scientific and Technological Progress of China, in 2010. He was the Vice Chair of ISPSD, in 2015 and 2019. He is an Associate Editor of the IEEE Transactions on Electron Devices.

. . .