Received September 11, 2019, accepted October 4, 2019, date of publication October 18, 2019, date of current version October 30, 2019. *Digital Object Identifier* 10.1109/ACCESS.2019.2948231

# A Seizure-Based Power Reduction SoC for Wearable EEG in Epilepsy

# SAAM IRANMANESH<sup>10</sup>, GEORGE RAIKOS<sup>2</sup>, SYED ANAS IMTIAZ<sup>10</sup>, AND ESTHER RODRIGUEZ-VILLEGAS<sup>1</sup>

<sup>1</sup>Department of Electrical and Electronic Engineering, Imperial College London, London SW7 2AZ, U.K.

<sup>2</sup>Power Integrations Ltd., Cambridge, U.K.

Corresponding author: Saam Iranmanesh (s.iranmanesh10@imperial.ac.uk)

This work was supported by the European Research Council through the European Community's Seventh Framework Programme (FP7/2007-2013)/ERC under Grant 239749.

**ABSTRACT** Epilepsy is one of the most common serious brain disorders affecting 1% of the world population. Epileptic seizure events are caused by abnormal excessive neuronal activity in the brain, which may be associated with behavioural changes that severely affect the patients' quality of life. These events are manifested as abnormal activity in electroencephalography (EEG) recordings of individuals with epilepsy. This paper presents the on-chip implementation of an algorithm that, operating on the principle of data selection applied to seizures, would be able to reduce the power consumption of EEG devices, and consequently their size, thereby significantly increasing their usability. In order to reduce the power consumed by the on-chip implementation, resulting in the power consumed by the system to be negligible in comparison to other blocks in an EEG device. The system has been fabricated in a 0.18  $\mu$ m CMOS process, consumes 1.14  $\mu$ W from a 1.25 V supply and achieves a sensitivity of 98.5% while only selecting 52.5% of the EEG data for transmission.

**INDEX TERMS** Seizure, epilepsy, electroencephalography (EEG), System-on-Chip (SoC), seizure detection.

#### I. INTRODUCTION

Epilepsy is a serious neurological condition affecting more than 1% of the world population. It is characterized by seizure episodes resulting from abnormal brain activity that affects quality of life of patients. Recurring seizures can result in reduced activities related to the patient's work, educational and social life [1]. Despite the significant consequences of epilepsy, almost 25% of patients are misdiagnosed [2].

The diagnosis of epilepsy often involves the use of electroencephalography (EEG) to monitor the brain activity of patients. Seizures can be infrequent events, occuring in the space of weeks or months, and about two-thirds of patients have between 1 and 12 seizures a year [3]. Long-term EEG monitoring is therefore desirable in order to capture epileptic traces and to increase the diagnostic yield [4]. Continuous EEG recordings carried out in hospital settings are costly and the secluded setup reduces the patient exposure to seizure provoking factors that may have otherwise resulted in seizures being recorded. Recordings can be carried out in a home setting using Ambulatory EEG (AEEG) units. However, AEEG units in their current form have a number of shortcomings [5], [6], including their bulkiness, heaviness (over 500 g) and short battery lifetime (less than 3 days).

The creation of truly Wearable EEG (WEEG) systems would allow for the long term monitoring of patients in the comfort of their natural environment. By monitoring patients in their own environment, as opposed to a clinical setup, patients can be exposed to stimuli that would provoke the seizure activity under investigation.

The WEEG system must maintain key features including wireless connectivity, miniature size, light-weight and low power consumption, while complying with medical regulatory standards such as those provided by the International Federation of Clinical Neurophysiology (IFCN) [7] and International Electrotechnical Commission (IEC) [8] to ensure the clinical-grade gathering of EEG signals and patient safety. Wireless connectivity of the WEEG system to a base station (e.g. mobile phone or tablet) is desirable to avoid long wired connections that may limit patient movement during the monitoring period. The WEEG system ergonomics and wireless connectivity features are also important from a privacy standpoint, since wearing a larger device with long wires may make apparent the user's health condition. Low-power operation of

The associate editor coordinating the review of this manuscript and approving it for publication was Berdakh Abibullaev.

the WEEG system is essential in order to achieve long-term monitoring, without interruption, from miniature batteries limited by the mentioned size and weight considerations. Extending the battery lifetime through low-power operation of the WEEG system would also mitigate the inconvenience and risks associated with recharging or replacement of batteries by untrained users.

The WEEG system architecture would at least contain an Instrumentation Amplifier (IA), Analog to Digital Converter (ADC) and a transmitter [9]. A power analysis carried out in [10] for a 32 channel EEG system using state-of-the-art IAs, ADCs and transmitter modules revealed that due to the continuous transmission of raw EEG signals, the power consumed by the transmitter would account for 97% of the total power consumption of the EEG system. In the context of epilepsy monitoring, a number of recently published works, focusing on treatment rather than diagnosis, targeted a reduction on the communication cost by detecting seizures locally. A reduction of 14× in system power consumption has been achieved in the work of [11]. This system transmits feature-vectors, rather than raw EEG signals, and seizure detection is performed in the software domain using the extracted features. Feature Extraction (FE) is carried out in the seizure detection System-on-Chip (SoC) of [12] by deriving the spectral energy distribution of the input EEG signal prior to the classification stage. The SoC utilizes a Non-Linear Support Vector Machine (NLSVM) classifier to perform the patient-specific seizure classification, while consuming 19.6  $\mu$ W/channel (FE + classification). The implantable seizure detection system of [13] is designed based on counters that detect high frequency activity while consuming 1.5  $\mu$ W/channel. The system uses parameters that must be tuned specifically to each patient. An implantable seizure detector utilizing signal entropy and frequency spectrum based feature extraction together with a Linear Least Square (LLS) classifier has been reported in [14]. The SoC requires patient-specific training and achieves a power consumption figure of 162.31  $\mu$ W/channel. The patient-specific and implantable seizure detector of [15] uses the line length feature to discriminate between seizures and background activity, subsequent to compressive sensing and digitization stages, while performing seizure classification using a thresholding scheme. The SoC consumes 0.85  $\mu$ W/channel. Seizure events are detected in the implantable seizure counting system of [16] by deriving the input signal energy in different frequency bands. A lookup table is also generated during a patient-specific training phase, and is used to match the measured energy values with the probability of seizure occurrence. The power consumed by the seizure detector is 0.45  $\mu$ W/channel. All these patient-specific approaches to detect seizure occurrence ([11]-[16]) focus on the realtime treatment of epilepsy through closed-loop instantaneous seizure suppression and symptom alleviation. Patient-specific approaches can be utilized in systems intended for epilepsy treatment since patients requiring such systems have already been diagnosed with epilepsy and therefore the gathered EEG

VOLUME 7, 2019

data, which is known to contain seizure activity, can be used for training the seizure detection algorithms.

This paper presents a scalable EEG data selection SoC targeting a different aspect of epilepsy, which is the diagnosis stage, for which the previously mentioned approaches are unsuitable. The mentioned seizure detection systems require a training phase using patient-specific EEG data containing marked seizure events, which may be available during the post-diagnosis stage. Such patient-specific data is, however, not readily available during the diagnosis stage.

The system presented in this paper reduces the amount of data to be transmitted by a WEEG device by continuously selecting sections of EEG data containing likely seizure activity. In other words, the system aims not to 'lose' seizure related sections of recorded signal that are important for the neurologist to see to make a diagnosis; whilst at the same time still reducing the amount of data that needs to be transmitted in order to significantly reduce the overall power consumed by the WEEG device. Note that reviewing raw and relevant EEG data is currently considered to be important for neurologists during the diagnostic process. As an illustration, a survey of neurologists, carried out in [5], revealed that the majority of respondents would not trust systems performing 'automated diagnosis', i.e. systems that would automatically mark clinical events without the intervention of neurologists during the diagnosis stage. In contrast, a large portion of the surveyed neurologists were in favour of systems that would reduce the amount of EEG data presented to them. It is also important to note that the process of manually reviewing raw EEG data by neurologists is time consuming, taking approximately 2 h per 24 h of recordings [17]. Hence, this approach, has the advantages of simultaneously reducing the power of the EEG system, but also the amount of time required by neurologists to review the transmitted EEG data, since it still gives them access to the clinically relevant seizure information, whilst eliminating large amounts of recorded brain signal that has nothing diagnostically important in them. Furthermore, because of its very low power consumption, the system presented in this paper could also be used in the WEEG system in combination with others which focus on selecting other relevant but also, in some cases, important diagnostic biomarkers, such as interictal spikes [10].

The remainder of this paper has been organised as follows. The concept of data selection in WEEG devices and epilepsy monitoring has been explained in Section II. This is followed by Section III, in which the system architecture together with the circuits blocks used in the system have been presented. The front-end and control circuitry are discussed in Section IV. Subsequently, measurement and performance results of the fabricated chip have been presented in Section V.

#### **II. SEIZURE SELECTION**

The complexity of the data selection system should be kept to a minimum to allow for the power consumed by this stage to remain negligible compared to the other blocks in the WEEG

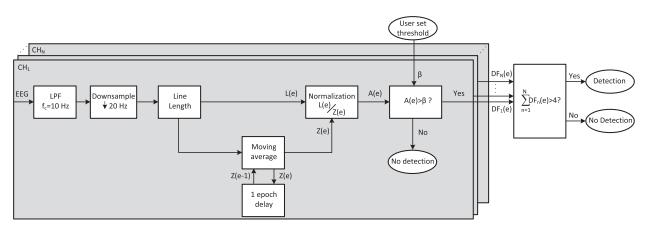

FIGURE 1. Overview of data selection algorithm.

unit. The system presented in this work utilizes the algorithm proposed in [18], as a foundation. The algorithm operates based on the concept of discontinuous recording [5], in which sections of raw EEG data containing clinically interesting events are selected while background EEG is discarded. The main operation of the algorithm has been illustrated in Fig. 1. The EEG input to each channel of the algorithm is initially high pass filtered with a cutoff frequency of 0.16 Hz. The following decimation block includes a third order low pass filter to strongly attenuate the signal frequency components above 10 Hz and allow for downsampling the input signal to 20 Hz, while avoiding distortion resulting from aliasing. The downsampled signal is used during the line length feature extraction in the form of 2 s non-overlapping windows of EEG data. The mentioned windows of data are hereon referred to as 'epochs'. The line length is calculated over each epoch as

$$L(e) = \sum_{k=1}^{S} |x(k-1) - x(k)|$$

(1)

where e is the epoch number being processed and L(e), x, k and S are the line length calculated within the epoch, downsampled signal, sample number and total number of samples in the epoch, respectively. Signal normalization is performed in the next stage of the algorithm to correct for changes in signal amplitude between different patients or due to the quality of the electrodes. Normalization is performed using the median decaying memory calculated as

$$z(e) = (1 - \lambda) \times \text{median}\{L(e - 1) \dots L(e - B_1)\}$$

$$+ \lambda \times z(e - 1) \quad (2)$$

where z(e) represents the estimated background activity calculated for the current epoch. The number of epochs used in the median calculation (searching window) is  $B_1$  and  $\lambda$  is a decay constant which controls the effect of previously derived values of z.

A start-up time of 2 min was chosen for the algorithm in the work of [18] to allow for the background estimate

\_

151684

z(e) to reach the same range of values as L(e), during which the median is derived using all available epochs and  $\lambda = 0.92$ . The value of  $\lambda$  is increased to 0.99 after the initial 2 min period to reduce the effect of erroneous values of the median calculation likely caused by seizure events [18]. The normalization estimate is calculated over a 120 s period and therefore  $B_1 = 60$  for 2 s epochs.

Hardware implementations of median filters, not specifically designed for processing EEG signals, have been previously reported in the literature and proven to be power hungry. A 3 input median filter has been proposed in [19] consuming 14 mW and the work of [20] reports a 9 input median circuit consuming 1.25 mW. Since in (2), the median operation is performed on the input signal and its time-shifted copies, the required delay elements (60 in the case of (2)) would only add to the hardware implementation complexity and power consumption. Due to the limited power budget for the algorithm hardware implementation in this work, a moving average filter was used to estimate the background activity instead of the median decaying memory. The moving average (MAV) is calculated as

$$MAV(e) = \frac{1}{B_2} \sum_{i=0}^{B_2 - 1} L(e - i)$$

(3)

where  $B_2$  is the window length of the filter and which was set to 60, similar to  $B_1$  in the median decaying memory calculation of (2). For  $B_2 \gg 1$ , the moving average of (3) can be approximated in the less computationally expensive recursive form, that was used in this work to estimate the backgroud activity (z(e)) as in (4) [21].

$$z(e) = \frac{B_2 - 1}{B_2} \times z(e - 1) + \frac{L(e)}{B_2}.$$

(4)

It should be noted that equation (4) is specific to processing discrete time signals. Considering the epoch duration of 2 s ( $f_s = 500$  mHz), the transfer function of the moving average corresponds to a single-pole recursive low pass filter with a cutoff frequency ( $f_c$ ) of 1.3 mHz calculated using (5), allowing for a continuous time analog domain approximation

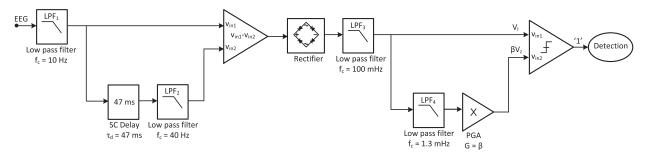

FIGURE 2. System-level implementation of the data selection algorithm.

which was used in the hardware implementation, shown later in Section III.

$$f_c = \frac{-f_s}{2\pi} \ln\left(\frac{B_2 - 1}{B_2}\right). \tag{5}$$

The normalization stage is completed by dividing the output of the line length calculation by the background estimate as:

$$A(e) = L(e)/z(e).$$

(6)

A detection flag for the channel being analysed (represented by  $DF_n(e)$  in Fig. 1) will be set to '1' if the normalized feature A(e) is greater than a user set threshold ( $\beta$ ). Candidate seizure events are selected using a multichannel approach and therefore, a section of EEG data is selected for containing likely seizure activity only if the number of channels with a detection of '1' is higher than a threshold of 4 (chosen empirically).

#### **III. SYSTEM ARCHITECTURE**

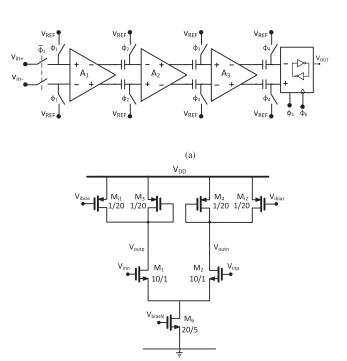

The system level implementation of the algorithm is shown in Fig. 2. An initial low-pass filtering stage strongly attenuates the signal frequency components above 10 Hz to ensure that the signal can be subsequently sampled during the line length feature calculation at a reasonable sampling rate. The filter was created by cascading three first order  $G_mC$  low-pass filters with cutoff frequencies of 21 Hz, achieved by a biasing current of 200 pA for each filter OTA and an integrated capacitance of 20 pF.

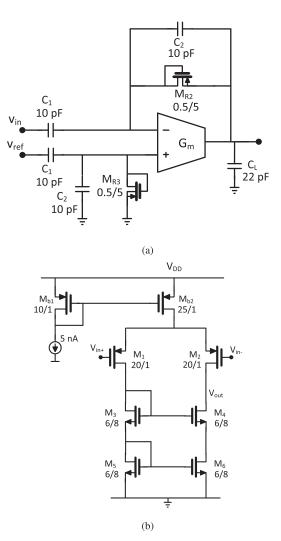

The line length equation of (1) was implemented by subtracting the original signal from a delayed copy of itself, followed by a rectifier and integrator. The delay line was created by cascading six of the delay cells proposed in [22], each consisting of two SC stages and controlled by complementary clock signals. The delay cells were clocked at 128 Hz with a duty cycle of 50%, resulting in an overall delay of 47 ms for the six cascaded delay cells. A single stage  $G_mC$  low-pass filter with a cutoff frequency of 40 Hz, placed after the delay circuit, effectively attenuates the distortion resulting from the clock signal frequency component and its harmonics. As shown in Fig. 3a, the subtractor circuit utilizes quasiinfinite resistors ( $M_{R2-R3}$ ) and capacitors ( $C_{1-2}$ ) to block the DC offset resulting from the previous circuitry. The circuit

FIGURE 3. Subtractor circuit to subtract the low-pass filtered input signal from a delayed copy of itself (a) subtractor top-level design (b) OTA circuit.

was designed to have a gain  $(-C_1/C_2)$  of -1 by choosing a capacitance of 10 pF for both  $C_1$  and  $C_2$ . The negative sign is of no consequence since the subtractor output is subsequently passed through a full-wave rectifier. A PMOS input stage was used in the subtractor OTA (Fig. 3b) to reduce the effect of low frequency noise on the subtractor output. The biasing current of the OTA was set to 12.5 nA, and cascoded devices  $(M_3 - M_6)$  were used to maintain the DC operating point.

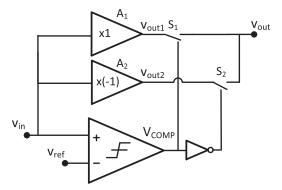

**FIGURE 4.** Rectifier circuit topology. The input signal is passed through an amplifier (A<sub>1</sub> or A<sub>2</sub>) based on the comparison result against V<sub>ref</sub>.

The design of the full-wave rectification stage was influenced by the concept proposed in [23], in which comparison results of the input signal ( $V_{in}$ ) against a DC reference voltage ( $V_{ref}$ ) is used to discriminate between the positive and negative signal polarities (see Fig. 4). A low impedance path is provided to the outputs of the non-inverting and inverting amplifiers ( $A_1$  and  $A_2$ ) upon selection based on the comparator output, through the switches ( $S_1$  and  $S_2$ ) which were implemented using minimum sized NMOS devices. The following SC low-pass filter, implemented based on the work of [24], effectively integrates the rectified signal to approximate the line length behaviour.

The low-pass filter clock frequency was set to 128 Hz with a duty cycle of 4% to achieve a filter cutoff frequency of 100 mHz.

The transfer function of the recursive moving average of (4) results in a filter with a cut off frequency of 1.3 mHz. The low-pass filter of [24], was also used to approximate the moving average filter using a 128 Hz clock with a duty cycle of 0.5%. A Programmable Gain Amplifier (PGA) behaving as a multiplier was implemented using the Operational Transconductance Amplifier (OTA) based amplifier topology of [25], to apply the user-set threshold values ( $\beta$ ) to the background estimate. The PGA consists of two OTAs and the gain of the amplifier represents the user set threshold values. The gain of the amplifier is set, by the ratio of the biasing currents of the two OTAs, to achieve a desired system performance after deciding on the specific tradeoff between sensitivity and amount of data reduction.

A comparator detects the time periods for which the line length output  $V_L$  is greater than the modulated background estimate ( $\beta V_Z$ ). As can be seen in Fig. 5a, three pre-amplification stages ( $A_1 - A_3$ ) were used prior to the dynamic latch for an output offset cancellation scheme (OOS) implementation to reduce the effect of the comparator offset [26]. Due to the low speed requirement of the comparator, the devices in the pre-amplifiers shown in Fig. 5b were biased in the weak inversion region. Current injecting devices ( $M_{i1} - M_{i2}$ ) were used to increase the transconductance of the input transistors compared to the diode connected load transistors ( $g_{m1} > g_{m3}$ ), resulting in a moderate gain of 5.5 for each of

FIGURE 5. Comparator producing the system output detection flag (a) top-level architecture (b) pre-amplifier schematic.

(b)

the pre-amplifiers. The comparator output was sampled in 2 s intervals to create the effect of non-overlapping epochs inline with the epoch duration of the data selection algorithm.

#### **IV. SYSTEM FRONT END AND CONTROL CIRCUITRY**

The IA, which was designed based on the topology reported in [27], achieves a mid-band gain of 37 dB and input referred noise of 4  $\mu$ V<sub>rms</sub> integrated from 0.5-100 Hz. A proportional to absolute temperature current generation circuit was used to draw a reference current of 366 nA from the 1.25 V power supply. The currents required by the circuits in the data selection system were generated using scaled copies of the reference current. An 8b counter circuit using JK flip-flops followed by D flip-flops and combinational digital logic was used to scale-down a 32.6 KHz clock provided by an off-chip oscillator and to generate the low duty cycle pulses required for the circuits in the system.

#### **V. FABRICATION AND TESTING**

#### A. CHIP FABRICATION

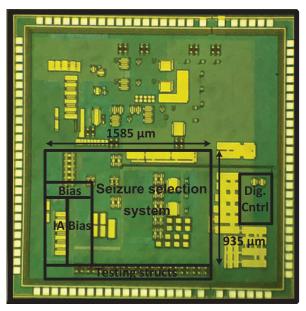

The chip was fabricated in a 0.18  $\mu$ m, tripple well 6 metal AMS CMOS technology. The chip padring was split into the two separate padrings to isolate sensitive analog circuitry from the noisy digital stages. The chip micrograph is shown in Fig. 6. The active area consumed by the seizure selection system is 1.48 mm<sup>2</sup>.

#### **B. EXPERIMENTAL RESULTS**

A National Instruments NI USB-6259 data acquisition board (DAQ) was used to feed the input signals to the chip and to gather the output results and intermediate test-points.

FIGURE 6. Micograph of fabricated chip.

The DAQ board introduces a capacitive load of 15 pF to its analog input signals and the implemented circuits generally have a low driving ability not suitable for driving the offchip load. Single stage analog buffer circuits with a biasing current of 40  $\mu$ A, provided through a separate 1.8 V supply and ground pad, were placed on-chip after the analog testpoints for testing purposes. A digital buffer was also placed at the decision flag output.

The EEG dataset used for testing the system performance contains over 168 h of recordings from 21 patients and 34 marked seizure events from the Epilepsy Society (UK), Freiburg University Hospital (Germany) and Katholieke Universiteit Leuven (Belgium) [28], [29]. A summary of the dataset is provided in Table 1 together with the number of events per patient. The 16 channels used for testing the system performance are chosen as the channels common to all recordings in the dataset and are: C3, C4, CZ, F3, F4, FZ, F7, F8, FP1, FP2, O1, O2, T3, T4, T5, and T6.

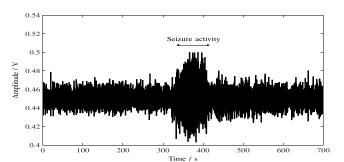

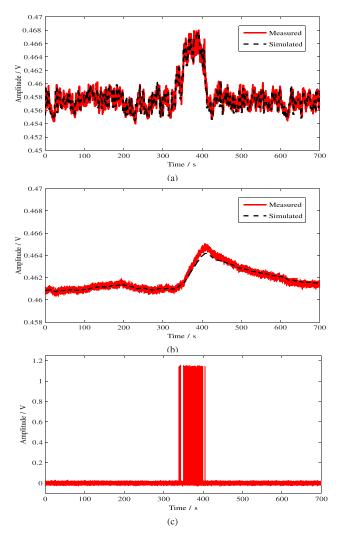

A 700 s trace of EEG data from patient 5 (channel C3), shown in Fig. 7, includes a marked seizure event (from 341 s to 416 s time marks) and has been used to illustrate the system behaviour. The modelled and measured line length signal ( $V_L$ ) and background estimate output ( $V_Z$ ) in response to the input data trace is presented in Fig. 8a and Fig. 8b respectively. It can be seen that the measured signals (solid) are inline with the shape of the modelled (dashed) results. The system detection flag output ( $V_{DF}$ ) is also shown in Fig. 8c.

The indices used to report the system performance are sensitivity and specificity. In order to distinguish between the number of seizure events correctly identified by the system and the number of identified seizure epochs, two variants of sensitivity have been used which are event sensitivity and epoch sensitivity. Event sensitivity is calculated as

Event Sensitivity =

$$\frac{TP_{ev}}{TP_{ev} + FN_{ev}} \times 100\%$$

(7)

FIGURE 7. A 700 s section of EEG containing a seizure event with a duration of 75 s (from 341 s to 416 s time marks).

**FIGURE 8.** System outputs in response to the input EEG trace (a) Line length calculation  $(V_L)$  (b) Output of moving average approximation  $(V_Z)$  (c) Detection flag output.

where  $TP_{ev}$  is the number of True Positives and is equal to the number of correctly identified seizure events. The number of seizure events that have not been identified by the system has been considered as False Negatives ( $FN_{ev}$ ). The calculation of epoch sensitivity follows the general form of (7), as

Epoch Sensitivity =

$$\frac{TP_{ep}}{TP_{ep} + FN_{ep}} \times 100\%$$

(8)

| Patient | Age at test | Gender  | Marked seizure events | Seizure duration (s) | <b>Recording duration</b> |  |

|---------|-------------|---------|-----------------------|----------------------|---------------------------|--|

| 1       | 33          | Female  | 3                     | 293                  | 34:02:07                  |  |

| 2       | 53          | Female  | 1                     | 118                  | 02:20:50                  |  |

| 3       | 56          | Female  | 7                     | 827                  | 66:59:38                  |  |

| 4       | 41          | Female  | 5                     | 2029                 | 19:54:17                  |  |

| 5       | 35          | Male    | 1                     | 75                   | 10:45:20                  |  |

| 6       | 35          | Male    | 1                     | 102                  | 12:04:50                  |  |

| 7       | 60          | Male    | 1                     | 45                   | 03:23:44                  |  |

| 8       | 33          | Male    | 1                     | 97                   | 04:08:57                  |  |

| 9       | 23          | Female  | 1                     | 38                   | 01:08:00                  |  |

| 10      | 34          | Male    | 0                     | 0                    | 02:00:11                  |  |

| 11      | Unknown     | Male    | 0                     | 0                    | 04:00:22                  |  |

| 12      | 22          | Female  | 1                     | 94                   | 00:49:59                  |  |

| 13      | 35          | Female  | 6                     | 109                  | 00:31:55                  |  |

| 14      | 46          | Female  | 1                     | 148                  | 00:06:12                  |  |

| 15      | Unknown     | Unknown | 3                     | 98                   | 00:26:42                  |  |

| 16      | Unknown     | Female  | 2                     | 85                   | 00:21:39                  |  |

| 17      | 47          | Female  | 0                     | 0                    | 02:00:11                  |  |

| 18      | 45          | Female  | 0                     | 0                    | 00:46:19                  |  |

| 19      | 43          | Male    | 0                     | 0                    | 00:15:15                  |  |

| 10      | 47          | Male    | 0                     | 0                    | 02:00:11                  |  |

| 21      | 28          | Female  | 0                     | 0                    | 02:00:11                  |  |

| Total   | -           | -       | 34                    | 4158                 | 168:57:31                 |  |

TABLE 1. Dataset used for testing the system performance.

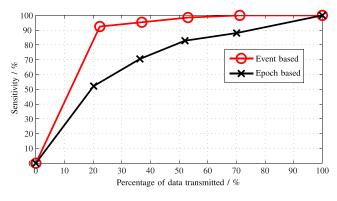

FIGURE 9. System performance tradeoff curve.

where  $TP_{ep}$  and  $FN_{ep}$  are the number of correctly detected seizure epochs and incorrectly rejected seizure epochs respectively.

Considering the 75 s seizure event of Fig. 7 and the epoch duration of 2 s used in this work, a single detection by the system during any of the 37 epochs will result in an event sensitivity of 100%. However, to achieve an epoch sensitivity of 100%, the system must correctly identify all present epochs as seizure epochs resulting in 37 detections. The detection flag output (Fig. 8c) indicates that the system is able to identify the seizure event (event sensitivity of 100%) while correctly detecting 29 out of the 37 seizure epochs present, resulting in an epoch sensitivity of 78.3%.

When testing the system performance on data obtained from patients during long recording periods, where the duration of seizure events is insignificant compared to the overall duration of the recordings, the percentage of data transmitted is very close to 100% – specificity [18]. The specificity of the system is calculated using (9), where  $TN_{ep}$

#### TABLE 2. System performance summary.

| CMOS Process                 | 0.18 μm<br>1.48 mm <sup>2</sup><br>1.25 V |     |  |  |

|------------------------------|-------------------------------------------|-----|--|--|

| Area                         |                                           |     |  |  |

| Supply Voltage               |                                           |     |  |  |

| Sensitivity                  | 98.5%                                     |     |  |  |

| Fraction of data transmitted | 52.5%                                     |     |  |  |

| Current consumption (nA)     | $LPF_1$                                   | 2   |  |  |

| -                            | SC delay line                             | 622 |  |  |

|                              | $LPF_2$                                   | 5   |  |  |

|                              | Subtractor                                | 32  |  |  |

|                              | Rectifier                                 | 172 |  |  |

|                              | LPF <sub>3</sub>                          | 5   |  |  |

|                              | $LPF_4$                                   | 5   |  |  |

|                              | PGA ( $\beta = 1.1$ )                     | 56  |  |  |

|                              | Comparator                                | 5.5 |  |  |

|                              | Digital circuitry                         | 5   |  |  |

|                              | Total                                     | 910 |  |  |

and  $FP_{ep}$  are the number of correctly rejected non-seizure epochs (True Negatives) and the number of incorrectly detected non-seizure epochs (False Positives) respectively.

Specificity =

$$\frac{TN_{ep}}{TN_{ep} + FP_{ep}} \times 100\%$$

(9)

In order to keep the duration of the measurement process across the dataset of Table 1 reasonable, the values of the sensitivity and percentage of data transmitted indices were calculated and averaged across all epochs using four threshold ( $\beta$ ) values of 0.9, 1.1, 1.3 and 1.5. The system performance tradeoff curve is shown in Fig. 9. It can be seen that the system is able to achieve an epoch sensitivity of 82.8% and an event sensitivity of 98.5% for a percentage of data transmitted of 52.5%. In comparison, for the same percentage of data transmitted, the mathematical model of the

|                     | Verma [11]<br>JSSC 2010 | Bin Atlaf [12]<br>TBCAS 2016 | Mirzaei [13]<br>TBCAS 2013 | Chen [14]<br>JSSC 2014 | Shoaran [15]<br>TCAS 2015 | Do Valle [16]<br>TBCAS 2016 | Imtiaz [30]<br>Access 2019 | This work             |

|---------------------|-------------------------|------------------------------|----------------------------|------------------------|---------------------------|-----------------------------|----------------------------|-----------------------|

| Signal              | Wearable<br>EEG         | Wearable<br>EEG              | Implantable<br>EEG         | Implantable<br>EEG     | Implantable<br>EEG        | Implantable<br>EEG          | Wearable<br>EEG            | Wearable<br>EEG       |

| Application         | Epilepsy<br>management  | Epilepsy management          | Epilepsy management        | Epilepsy<br>management | Epilepsy management       | Epilepsy management         | Epilepsy<br>diagnosis      | Epilepsy<br>diagnosis |

| Technology (µm)     | 0.18                    | 0.18                         | 0.13                       | 0.18                   | 0.18                      | 0.18                        | 0.18                       | 0.18                  |

| Supply (V)          | 1                       | 1                            | -                          | 1.8                    | 0.8                       | 0.9                         | 1.8                        | 1.25                  |

| Patient specificity | -                       | 0                            | 0                          | 0                      | 0                         | 0                           | ×                          | ×                     |

| Seizure detection   | -                       | 95.1%                        | 100%                       | 92%                    | 100%                      | 98.5%                       | 97%                        | 98.5%                 |

| Power (µW/Ch)       | 48.1                    | 19.6                         | 1.5                        | 162.3                  | 0.85                      | 0.45                        | 23                         | 1.14                  |

#### TABLE 3. Comparison with published works.

data selection algorithm achieves an event sensitivity of 100% and epoch sensitivity of 85%. The difference in the results is due to the mathematical approximations carried out in the original algorithm in order to aid the analog implementation.

The performance metrics must be considered in the context of the system aim, namely power reduction for a WEEG unit to aid with the diagnosis of epilepsy. It is expected that performance results achieved for the system event sensitivity will be higher than that of epoch sensitivity since it is easier to detect a single seizure event as opposed to detecting all seizure epochs. Event sensitivity is an important metric for real-time treatment systems that require a seizure event to be detected to allow for focal treatment and prevent seizure progression. However, epoch sensitivity is also an essential metric for the system of this work since a higher number for this metric would indicate that a larger percentage of interesting EEG data has been successfully selected for transmission, resulting in increased accuracy in the diagnosis.

A summary of the chip performance is shown in Table 2. The fabricated chip consumes 910 nA from a 1.25 V supply resulting in a power consumption figure of 1.14  $\mu$ W. A comparison of this work with other published seizure detection SoCs has been shown in Table III. It should be noted that the previously published seizure detection systems mentioned in Table 3 require patient-specific training and the EEG data required to train these systems on a patient-by-patient basis is already marked as corresponding to seizure or nonseizure. This training data may be available once a patient is diagnosed with epilepsy, however, such data is not readily available during the diagnosis stage, rendering the mentioned systems unsuitable for use during this stage, unlike the system proposed in this paper. It is also difficult to directly compare the performance of the system presented in this paper, which is intended to aid the diagnosis of epilepsy, with works that focus on the real-time treatment (management) aspect of epilepsy and are designed based on different requirements. For example, the delay in seizure detection (latency) is an important metric in seizure detectors operating in real-time [31], but not so in the proposed system as the transmitted sections of data will ultimately be reviewed by a neurologist after being gathered, and not in real time. Instead, the ability of the system to identify the entire duration of seizure events (epoch sensitivity), in addition to the ability of the system to identify the occurrence of seizures (event sensitivity), are important performance indices in a system intended to be used to aid the diagnosis of epilepsy. Furthermore, the selection of false positives by the proposed system does not affect the overall EEG analysis as it is the neurologist, and not the presented system, who makes the final decision on the clinical relevance of the transmitted sections of data and rejects incorrect features. This is unlike systems performing seizure event quantification, where any false detections result in the overall result to be fundamentally incorrect, resulting in a very low false positive rate requirement. The SoC proposed in [30], which is a fully digital on-chip implementation of the algorithm of [18] and also operates based on the concept of discontinuous recording, can aid neurologists in the diagnosis stage of epilepsy. However, the power figure of 23  $\mu$ W reported for the SoC of [30] is almost 23 times larger than the power consumed by the SoC presented in this paper, which is 1.14  $\mu$ W.

To put numbers into context, assuming a conventional wireless EEG unit (32 channels) with no data reduction and created using an array of 32 IAs, ADCs and a single transmitter module based on previously reported low-power works with power consumption figures of 1.62  $\mu$ W [31], 200 nW ([32]) and 2.112 mW ([33]), respectively, will result in a overall power consumption of 2.171 mW for the EEG system. Including an array of 32 data selection stages in the EEG system will result in an added power figure of 36.5  $\mu$ W while effectively reducing the power consumed by the transmitter by a factor of 2 (for a data reduction of 50%), resulting in a reduced overall power consumption figure of 1.15 mW for the EEG system. This power figure translates to over 213 h ( $\sim$  9 days) of operation from a miniature battery typically used in hearing aids [34]. The achieved power savings could also be capitalized on by using the system proposed in this work in combination with other data reduction stages that select inter-ictal sections of EEG data, such as [10], to obtain a complete WEEG system for the purpose of epilepsy diagnosis.

# **VI. CONCLUSION**

This paper presented the design and experimental results for a low-power seizure focused power reduction SoC. The mapping of the mathematical model of the seizure selection algorithm to an analog-based SoC, together with the hardware design procedure and implementation are discussed. The analog based seizure selection circuitry are implemented using a 0.18  $\mu$ m CMOS process. A power analysis presented as part of this paper shows the potential of the power reduction SoC in extending the battery lifetime of a EEG system to over 9 days of operation. The seizure focused power reduction SoC, which is tested with over 168 hours of EEG data from 21 patients and 34 marked seizure events, is able achieve a sensitivity of 98.5% while selecting 52.5% of the EEG data for transmission and consuming 1.14  $\mu$ W.

## Acknowledgment

G. Raikos was with the Department of Electrical and Electronic Engineering, Imperial College London, London SW7 2AZ, U.K.

### REFERENCES

- R. S. Fisher, B. G. Vickrey, P. Gibson, B. Hermann, P. Penovich, A. Scherer, and S. Walker, "The impact of epilepsy from the patient's perspective I. Descriptions and subjective perceptions," *Epilepsy Res.*, vol. 41, no. 1, pp. 39–51, 2000.

- [2] D. Smith, B. A. Defalla, and D. W. Chadwick, "The misdiagnosis of epilepsy and the management of refractory epilepsy in a specialist clinic," *QJM, Int. J. Med.*, vol. 92, pp. 15–23, Jan. 1999.

- [3] S. Brown, T. Betts, P. Crawford, B. Hall, S. Shorvon, and S. Wallace, "Epilepsy needs revisited: A revised epilepsy needs document for the UK," *Seizure*, vol. 7, no. 6, pp. 435–446, 1998.

- [4] E. Waterhouse, "New horizons in ambulatory electroencephalography," IEEE Eng. Med. Biol. Mag., vol. 22, no. 3, pp. 74–80, May 2003.

- [5] A. J. Casson, D. C. Yates, S. J. M. Smith, J. S. Duncan, and E. Rodriguez-Villegas, "Wearable electroencephalography," *IEEE Eng. Med. Biol. Mag.*, vol. 29, no. 3, pp. 44–56, May/Jun. 2010.

- [6] U. Seneviratne, A. Mohamed, M. Cook, and W. D'Souza, "The utility of ambulatory electroencephalography in routine clinical practice: A critical review," *Epilepsy Res.*, vol. 105, pp. 1–12, Jul. 2013.

- [7] M. R. Nuwer, G. Comi, R. Emerson, A. Fuglsang-Frederiksen, J.-M. Guérit, H. Hinrichs, A. Ikeda, F. J. C. Luccas, and P. Rappelsburger, "IFCN standards for digital recording of clinical EEG," *Electroencephalogr. Clin. Neurophysiol.*, vol. 106, no. 3, pp. 259–261, 1998.

- [8] Particular Requirements for the Basic Safety and Essential Performance of Electroencephalographs, document IEC 60601-2-26:2012, 2015.

- [9] J. J. Estrada-López, A. Abuellil, A. Costilla-reyes, and E. Sánchez-Sinencio, "Technology enabling circuits and systems for the Internet-of-Things: An overview," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2018, pp. 1–5.

- [10] S. Iranmanesh and E. Rodriguez-Villegas, "A 950 nW analog-based data reduction chip for wearable EEG systems in epilepsy," *IEEE J. Solid-State Circuits*, vol. 52, no. 9, pp. 2362–2373, Sep. 2017.

- [11] N. Verma, A. Shoeb, J. Bohorquez, J. Dawson, J. Guttag, and A. P. Chandrakasan, "A micro-power EEG acquisition SoC with integrated feature extraction processor for a chronic seizure detection system," *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 804–816, Apr. 2010.

- [12] M. A. B. Altaf and J. Yoo, "A 1.83 μ J/classification, 8-channel, patient-specific epileptic seizure classification SoC using a non-linear support vector machine," *IEEE Trans. Biomed. Circuits Syst.*, vol. 10, no. 1, pp. 49–60, Feb. 2016.

- [13] M. Mirzaei, M. T. Salam, D. K. Nguyen, and M. Sawan, "A fullyasynchronous low-power implantable seizure detector for self-triggering treatment," *IEEE Trans. Biomed. Circuits Syst.*, vol. 7, no. 5, pp. 563–572, Oct. 2013.

- [14] W.-M. Chen, H. Chiueh, T.-J. Chen, C.-L. Ho, C. Jeng, M.-D. Ker, C.-Y. Lin, Y.-C. Huang, C.-W. Chou, T.-Y. Fan, M.-S. Cheng, Y.-L. Hsin, S.-F. Liang, Y.-L. Wang, F.-Z. Shaw, Y.-H. Huang, C.-H. Yang, and C.-Y. Wu, "A fully integrated 8-channel closed-loop neural-prosthetic CMOS SoC for real-time epileptic seizure control," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 232–247, Jan. 2014.

- [15] M. Shoaran, C. Pollo, K. Schindler, and A. Schmid, "A fully integrated IC with 0.85 μW/channel consumption for epileptic iEEG detection," *IEEE Trans. Circuits Syst.*, *II, Exp. Briefs*, vol. 62, no. 2, pp. 114–118, Feb. 2015.

- [16] B. G. D. Valle, S. S. Cash, and C. G. Sodini, "Low-power, 8-channel EEG recorder and seizure detector ASIC for a subdermal implantable system," *IEEE Trans. Biomed. Circuits Syst.*, vol. 10, no. 6, pp. 1058–1067, Dec. 2016.

- [17] J. Gotman, "Automatic detection of seizures and spikes," J. Clin. Neurophysiol., vol. 16, no. 2, pp. 130–140, Mar. 1999.

- [18] S. A. Imtiaz, L. Logesparan, and E. Rodriguez-Villegas, "Performancepower consumption tradeoff in wearable epilepsy monitoring systems," *IEEE J. Biomed. Health Inform.*, vol. 19, no. 3, pp. 1019–1028, Jul. 2015.

- [19] A. Diaz-Sanchez, J. Ramirez-Angulo, A. Lopez-Martin, and E. Sanchez-Sinencio, "A fully parallel CMOS analog median filter," *IEEE Trans. Circuits Syst., II, Exp. Briefs*, vol. 51, no. 3, pp. 116–123, Mar. 2004.

- [20] W. Jendernalik, G. Blakiewicz, J. Jakusz, and S. Szczepański, "A nineinput 1.25 mW, 34 ns CMOS analog median filter for image processing in real time," *Analog Integr. Circuits Signal Process.*, vol. 76, no. 2, pp. 233–243, Aug. 2013.

- [21] S. M. Kuo, B. H. Lee, and W. Tian, *Real-Time Digital Signal Processing: Implementations and Applications*, 2nd ed. Chichester, U.K.: Wiley, 2006.

- [22] E. Rodriguez-Villegas, L. Logesparan, and A. J. Casson, "A low power linear phase programmable long delay circuit," *IEEE Trans. Biomed. Circuits Syst.*, vol. 8, no. 3, pp. 432–441, Jun. 2014.

- [23] A. Arnaud and C. Galup-Montoro, "Fully integrated signal conditioning of an accelerometer for implantable pacemakers," *Analog Integr. Circuits Signal Process.*, vol. 49, no. 3, pp. 313–321, Dec. 2006.

- [24] E. Rodriguez-Villegas, A. J. Casson, and P. Corbishley, "A subhertz nanopower low-pass filter," *IEEE Trans. Circuits Syst.*, *II, Exp. Briefs*, vol. 58, no. 6, pp. 351–355, Jun. 2011.

- [25] R. L. Geiger and E. Sanchez-Sinencio, "Active filter design using operational transconductance amplifiers: A tutorial," *IEEE Circuits Devices Mag.*, vol. 1, no. 2, pp. 20–32, Mar. 1985.

- [26] B. Razavi and B. A. Wooley, "Design techniques for high-speed, highresolution comparators," *IEEE J. Solid-State Circuits*, vol. 27, no. 12, pp. 1916–1926, Dec. 1992.

- [27] R. R. Harrison and C. Charles, "A low-power low-noise CMOS amplifier for neural recording applications," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 958–965, Jun. 2003.

- [28] W. De Clercq, A. Vergult, B. Vanrumste, W. Van Paesschen, and S. Van Huffel, "Canonical correlation analysis applied to remove muscle artifacts from the electroencephalogram," *IEEE Trans. Biomed. Eng.*, vol. 53, no. 12, pp. 2583–2587, Nov. 2006.

- [29] A. Vergult, W. De Clercq, A. Palmini, B. Vanrumste, P. Dupont, S. Van Huffel, and W. Van Paesschen, "Improving the interpretation of ictal scalp EEG: BSS–CCA algorithm for muscle artifact removal," *Epilepsia*, vol. 48, no. 5, pp. 950–958, May 2007.

- [30] S. A. Imtiaz, S. Iranmanesh, and E. Rodriguez-Villegas, "A low power system with EEG data reduction for long-term epileptic seizures monitoring," *IEEE Access*, vol. 7, pp. 71195–71208, 2019.

- [31] M. A. B. Altaf, C. Zhang, and J. Yoo, "A 16-channel patient-specific seizure onset and termination detection SoC with impedance-adaptive transcranial electrical stimulator," *IEEE J. Solid-State Circuits*, vol. 50, no. 11, pp. 2728–2740, Nov. 2015.

- [32] N. Verma and A. P. Chandrakasan, "An ultra low energy 12-bit rate-resolution scalable SAR ADC for wireless sensor nodes," *IEEE J. Solid-State Circuits*, vol. 42, no. 6, pp. 1196–1205, Jun. 2007.

- [33] Texas Instruments. (2017). SimpleLink Bluetooth Low Energy Wireless MCU. [Online]. Available: http://www.ti.com/product/cc2640r2f

- [34] Varta Microbattery GmbH. (2017). Zinc Air Wireless Approved Mercury-Free P312. [Online]. Available: http://www.powerone-batteries. com/en/products/zinc-air-mercury-free-batteries/p312/

# **IEEE**Access

**SAAM IRANMANESH** received the B.Sc. degree in computer engineering from Shahid Beheshti University, Tehran, Iran, in 2009, and the M.Sc. degree in electrical engineering with a focus on analog and digital integrated circuit design and the Ph.D. degree in electrical and electronic engineering from Imperial College London, London, U.K., in 2011 and 2018, respectively. As a Researcher at Imperial College London, he is currently developing novel wearable brain—computer interfaces to

aid the long-term monitoring of neurological disorders. His current research interests include the development of wearable medical devices for diagnostic and remote monitoring applications, low complexity signal processing algorithms for use in wearable systems, biomedical signal analysis, and lowpower mixed-signal electronics.

**SYED ANAS IMTIAZ** received the B.Eng. degree from the National University of Sciences and Technology, Pakistan, in 2008, and the M.Sc. and Ph.D. degrees from the Imperial College London, London, U.K., in 2009 and 2015, respectively. From 2009 to 2010, he was a Digital Design Engineer with the Imagination Technologies, U.K. He is currently a Postdoctoral Research Fellow and focuses on creating novel wearable technologies to aid long-term monitoring and the diagnosis of

different medical conditions. His current research interests include developing low-complexity signal processing algorithms and their low-power mixed signal circuit design, particularly for use in sleep and respiratory medicine and epilepsy monitoring.

**ESTHER RODRIGUEZ-VILLEGAS** received the Ph.D. degree from the University of Seville, Spain, in 2002. She has been a Faculty Member with the Imperial College London, U.K., since 2002. She was the Chair of Low Power Electronics with the Department of Electrical and Electronic Engineering, in 2015. She is also the Director of the Wearable Technologies Laboratory. She is specialized in ultra low-power electronic circuits and systems for wearable medical devices. She was a recipient

of a number of awards and honors, including being recognized twice by the European Research Council as a Research Leader in Europe for Starting and Consolidator Awards, in 2010 and 2016; being recognized as the Top Young Scientist/Engineer in Spain for the Complutense Award, in 2009; the Institution of Engineering and Technology, U.K., Innovation Award, in 2009; and the XPRIZE, USA, Award, in 2014. She is also the Founder of two life sciences companies, including Acurable Ltd., and TainiTec Ltd., where she currently holds the positions of Co-CEO and CSO. She has trained over 700 engineers from all around the world, at the master's or Ph.D. level, in ultra low-power electronic design.

**GEORGE RAIKOS** received the B.Sc. degree in physics, and the M.Sc. and Ph.D. degrees in electrical engineering from the University of Patras, Greece, in 2005, 2007, and 2011, respectively. As a Research Associate with the Imperial College London, from 2012 to 2015, his research focused on creating new signal processing techniques to prolong the battery life of wearable EEG systems. He is currently with Power Integrations Ltd., Cambridge, U.K., as an Analog IC Design

Engineer. His current research interests include low-power analog-to-digital conversion and mixed-signal circuit design.

. . .