Received September 21, 2019, accepted October 6, 2019, date of publication October 11, 2019, date of current version October 23, 2019.

Digital Object Identifier 10.1109/ACCESS.2019.2946617

# **An Improved Harmonics Mitigation Scheme for a Modular Multilevel Converter**

A. RAKESH KUMAR<sup>®</sup><sup>1</sup>, (Member, IEEE), MAHAJAN SAGAR BHASKAR<sup>®</sup><sup>2</sup>, (Member, IEEE), UMASHANKAR SUBRAMANIAM<sup>®</sup><sup>2</sup>, (Senior Member, IEEE), DHAFER ALMAKHLES<sup>®</sup><sup>2</sup>, (Member, IEEE), SANJEEVIKUMAR PADMANABAN<sup>®</sup><sup>3</sup>, (Senior Member, IEEE), AND JENS BO-HOLM NIELSEN<sup>3</sup>, (Senior Member, IEEE)

<sup>1</sup>School of Electrical Engineering, Vellore Institute of Technology, Chennai 603210, India

Corresponding Author: A. Rakesh Kumar (rakesh9490@gmail.com)

This work was financially supported by the Renewable Energy Laboratory, Department of Communications and Networks Engineering, Prince Sulltan University, Riyadh, Saudi Arabia.

**ABSTRACT** Modular Multilevel Converters (MMC) are gaining importance because of their flexible structure, re-configurable property, and simplicity of operation. The operation of MMC at a low-switching frequency (LSF) helps in enhancing the performance of the converter. This paper proposes an improved harmonics mitigation scheme for a Multilevel DC-Link Inverter (MLDCLI), which is a variant of MMC. The proposed scheme is a modified version of the conventional Nearest Level Modulation (NLM) scheme, termed as modified Nearest Level Modulation (mNLM) Scheme. The proposed scheme is effective compared to NLM because of the choice of the switching angles obtained by the use of the algorithm proposed. The MLDCLI topology is operated for twelve different configurations, and mNLM is implemented on all the configurations. Using MATLAB software, the simulation results are validated, and the same is extended to a hardware prototype. The simulation and experimental results of NLM and mNLM schemes are compared. The effectiveness of the proposed scheme is evident by the reduced voltage THD, increased rms voltage, increased rms current, and increased output power.

**INDEX TERMS** Modular multilevel converters, DC-AC power converters, pulse width modulation converters, power conversion harmonics, nearest level modulation, total harmonics distortion.

#### I. INTRODUCTION

A multilevel inverter (MLI) is a combination of power semiconductor switches and dc voltage sources to generate ac output voltage in a stepped waveform. The proper commutation of the power semiconductor switches helps in adding the dc voltage sources to produce the ac output. The presence of multiple switches also helps to reduce voltage sharing among the switches to generate high power output [1], [2]. These converters can synthesize the output waveform with reduced harmonics content. Hence, they are used to attain high voltage levels in high power conversion [3], [4]. The other applications of MLI involve integration with renewable sources, use in motor drives, and power systems [5]–[9].

The associate editor coordinating the review of this manuscript and approving it for publication was Sze Sing Lee.

The most common and conventional multilevel inverter topologies are neutral point clamped inverter (NPC), flying capacitor clamped inverter (FC), and cascaded h-bridge inverter (CHB) [10]–[14]. In recent years many new topologies have evolved, which can generate a higher number of levels with a reduced number of switches than the conventional inverter topologies [15]–[18]. This has given rise to a new classification of MLI based on the symmetry of the input dc sources of the MLI [19]. An MLI with equal magnitude dc sources is classified as symmetrical MLI. On the other hand, an asymmetrical MLI has an unequal magnitude of dc sources. An asymmetrical MLI is preferred over the symmetrical MLI for numerous advantages such as reduced THD, improved ac waveshape, higher output power etc, [20], [21].

Modular Multilevel Converters (MMC) are a variant of MLIs which carry a modular and reconfigurable structure. Multilevel DC-Link inverters (MLDCLI) form a very

<sup>&</sup>lt;sup>2</sup>Renewable Energy Laboratory, Department of Communications and Networks Engineering, Prince Sultan University, Riyadh 11586, Saudi Arabia

<sup>&</sup>lt;sup>3</sup>Department of Energy Technology, Aalborg University, 6700 Esbjerg, Denmark

| TABLE 1.  | Advantages of low-switching frequency over high-switching |

|-----------|-----------------------------------------------------------|

| frequency | modulation schemes.                                       |

| Sl. | Performance Parameters      | HSF       | LSF       |  |

|-----|-----------------------------|-----------|-----------|--|

|     |                             | Schemes Ӿ | Schemes 🧭 |  |

| 1   | Device switching stress     | high      | low       |  |

| 2   | Device switching losses     | high      | low       |  |

| 3   | Device cooling requirements | high      | low       |  |

| 4   | Device manufacturing cost   | high      | low       |  |

| 5   | Device utilization          | low       | high      |  |

| 6   | Converter efficiency        | low       | high      |  |

significant topology among the existing MMC topologies. The MLDCLI is a combination of cascaded half-bridge cells as well as a full-bridge inverter. The cascaded half-bridge cells operate to increase the levels at the output of the MMC, whereas the full-bridge plays the part of generating the negative polarity of the ac output. The striking feature of the MLDCLI is the reduced switch count as compared to the conventional MLI topologies [22]. The MLDCLI can also operate under symmetrical as well as asymmetrical configurations and applications includes renewable energy sources and battery electric vehicles [23], [24].

Even though numerous research is carried on the MLI topologies by academicians and industrialists, the efficient operation of MLI also depends on the way of operation of the switches. Hence, there are many modulation schemes used and developed to operate an MLI efficiently [25]–[30]. For the sake of simplicity, modulation schemes may be classified into high-switching frequency (HSF) and low-switching frequency (LSF) modulation schemes. In an HSF scheme, the switches are operated in several kHz to reduce the harmonics at the output [31]–[34]. The switches in LSF modulation schemes are operated at less than 1kHz [4], [35], [36].

Switching losses in a power semiconductor switch is a vital parameter in medium-voltage high-power applications. When switching loss is reduced, it leads to a reduction in the manufacturing and operating costs of a converter. It also helps in better device utilization, higher converter efficiency, and reduced cooling requirements [37]–[39]. Hence, LSF modulation schemes are often most preferred to HSF modulation schemes. The advantages of LSF schemes over HSF are tabulated in Table 1.

NLM falls under the category of LSF schemes. The switching frequency of the power semiconductor switches depends on the line frequency of the MLI. This paper proposes a modified version of the NLM to reduce the THD content at the ac output of the MLI. The NLM scheme has outstanding advantages over the other LSF modulation schemes. The drawbacks of all the LSF modulation schemes and the advantages of NLM scheme are discussed a follows:

1) Equal-Phase Method (EPM) and Half-Equal-Phase Method (HEPM):

- ⊗ The EPM and HEPM schemes carry equal duty cycles and, hence, they yield a very high voltage and current THD.

- ⊗ Since the THD is very high, it reduces the output rms voltage and rms current. This, in turn, offers a poor power conversion efficiency, and hence, they are not a recommended PWM scheme.

- 2) Selective Harmonics Elimination (SHE):

- ⊗ SHE is a useful scheme for the elimination of the lower order harmonics, but it comes at the cost of increased higher order harmonics [40].

- $\otimes$  Any improvement in the SHE scheme requires an increase in the switching frequency which is undesirable

- ⊗ The SHE scheme is also highly dependent on the modulation index, and hence, for getting the maximum efficiency of the SHE scheme, it is important to calculate the exact modulation index.

- 3) Space Vector Control (SVC):

- ⊗ For a lower number of MLI levels, the working principles of SVC and NLM are almost the same. However, when the MLI levels increases, the SVC becomes increasingly complex [37].

- ⊗ The SVC scheme is ideal for use when a particular switching pattern is necessary with respect to varying input voltages.

- 4) Nearest Level Modulation (NLM):

- ∅ The striking feature of NLM is the simplicity in its execution. A simple equation is sufficient to calculate the switching angles enabling ease of execution [40].

- With the NLM equation, it is very easy to extend it to any number of MLI levels.

- There is enough scope for improving NLM without increasing the switching frequency.

Hence, it can be observed that the NLM scheme offers good advantages over its counterpart LSF schemes. This paper proposes an improved version of the NLM scheme by following an algorithm to obtain a new set of switching angles. The new set of switching angles helps in improving the performance parameters of the inverters such as THD, rms voltage, rms current, and output power.

#### **II. MULTILEVEL DC-LINK INVERTER**

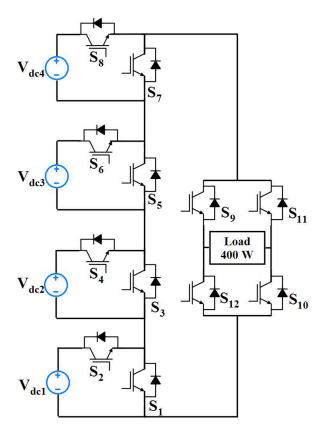

Figure 1 shows the circuit diagram of a MLDCLI. It consists of four dc sources and twelve switches. Four of the switches act as an h-bridge, and the remaining eight switches are part of cascaded half-bridge cells. A single half-bridge cell consists of two switches. Thus, four such half-bridge cells are cascaded to generate various levels. The operation of the switches in the half-bridge cell determines whether the associated dc sources should be added in the circuit or not. The switches in the half-bridge operate in a toggle fashion.

When the pair of switches  $S_1$ - $S_2$  are considered, turning on switch  $S_2$  and turning off switch  $S_1$  provides a current path which add the voltage source  $V_{dc1}$  to the main circuit.

FIGURE 1. Circuit of multilevel DC-Link inverter.

However, turning on switch  $S_1$  and turning off switch  $S_2$  disassociates  $V_{dc1}$ . The other switch pairs  $S_3$ – $S_4$ ,  $S_5$ – $S_6$  and  $S_7$ – $S_8$  operate similarly to associate or disassociate with their respective dc voltage sources. The switch pair  $S_9$ – $S_{10}$  on operation will provide the positive half cycle of the ac output. The negative half of the ac output is provided by the switch pair  $S_{11}$ – $S_{12}$ . Hence, for a single cycle, the switching frequency of the half-bridge cells is twice the switching frequency of the h-bridge. The h-bridge is operated at a switching frequency of 50 Hz to generate a 50 Hz ac output.

#### A. SYMMETRIC CONFIGURATION

In the symmetric configuration, all the voltage sources carry equal voltage magnitude. This leads to four possible voltage levels i.e,  $V_{dc1}$ ,  $V_{dc1} + V_{dc2}$ ,  $V_{dc1} + V_{dc2} + V_{dc3}$  and  $V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$  [41]. Hence, a 9-level output is generated. This is the first configuration of the twelve possible configurations presented in this paper. This symmetrical configuration can be extended to any number of levels using the following equations.

By adding the number of voltage sources, the MLI levels will increase. The values of all the dc sources are the same, which is shown in equation (1).

$$V_{dc,j} = V_{dc}$$

for  $j = 1, 2, 3, 4...$  (1)

The number of MLI levels at the output and the number of switches in MLDCLI circuit are related as equation (2).

$$N_{level} = n - 3$$

for  $n = 6, 8, 10, 12...$  (2)

As the number of switches increase, the number of input sources also increases, which is shown in equation (3).

$$N_{source} = \frac{n-4}{2}$$

for  $n = 6, 8, 10, 12...$  (3)

# **B. ASYMMETRIC CONFIGURATION**

In the asymmetric configurations, the magnitudes of input de voltages are unequal. In general, an asymmetrical configuration generates a greater number of levels than symmetrical configurations. This helps in improving the ac output voltage waveform quality and the associated THD. However, with the increase in MLI levels, the number of modes of operation of the MLI increases for a single cycle, which results in an increase in the switching frequency. The switching pattern also increases in complexity with higher MLI levels. Nevertheless, a higher MLI level is always preferred. In this section, there are 11 asymmetrical configurations considered to generate levels starting from 11-level to 31-level.

In configuration 2, the  $4^{th}$  dc voltage source is twice in voltage magnitude of the other three voltage sources generating an 11-level output. Configuration 3 carries input dc voltage sources of ratio 1:1:2:2 and generates 13-level. To generate a 15-level, the  $2^{nd}$ ,  $3^{rd}$  and  $4^{th}$  are chosen with a twice the magnitude of the 1st input dc voltage source. The 17-level and 19-level MLI are generated with the input dc voltage sources of 1:2:2:3 and 1:2:2:4, respectively. A natural number sequence is followed by the dc voltage source to generate 21-level MLI output. To generate a 23-level MLI output, a dc voltage ratio of 1:2:3:5 is used, which resembles a Fibonacci series. With the input dc voltage sources of 1:2:3:6, 25-level MLI is generated. 27-level and 29-level MLI are generated using the dc voltage source ratios of 1:2:4:6 and 1:2:4:7, respectively. A binary sequence dc voltage source is employed to generate 31-level. Table 2 shows the consolidated modes of operations for all the configurations.

# III. CONVENTIONAL AND PROPOSED MODULATION SCHEME

#### A. NEAREST LEVEL MODULATION SCHEME

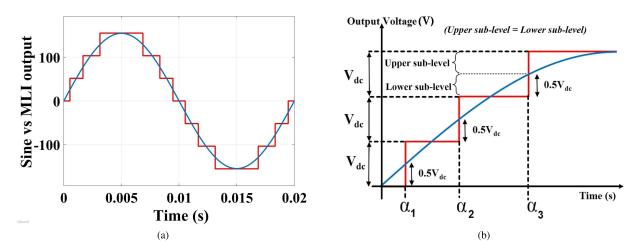

Figure 2 presents the graphical diagram of the NLM scheme. A single cycle is shown where a 7-level MLI output is compared with a sinusoidal waveform. Besides it, a quarter cycle of the full cycle is shown, which provides deep insight into the working of the conventional scheme. For the ease of understanding, the sinusoidal waveform cutting the rising edge of the MLI level can be divided into two parts. The upper part is called Upper sub-level (USL), while the lower part is called the Lower sub-level (LSL). For NLM scheme the, the magnitude of USL and LSL are the same. This is applicable to all the rising edges of the MLI levels. With the

TABLE 2. Various configurations of operation of MLDCLI.

| Configuration | No. of Levels | Ratio of DC Sources          | Possible Voltage Combinations                                                                                        |

|---------------|---------------|------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 1             | 9             | 1:1:1:1                      | $V_{dc1}, V_{dc1} + V_{dc2}, V_{dc1} + V_{dc2} + V_{dc3},$                                                           |

|               |               | (39 V, 39 V, 39 V, 39 V)     | $V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$                                                                              |

| 2             | 11            | 1:1:1:2                      | $V_{dc1}, V_{dc1} + V_{dc2}, V_{dc1} + V_{dc2} + V_{dc3},$                                                           |

|               |               | (31 V, 31 V, 31 V, 62 V)     | $V_{dc2} + V_{dc3} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$                                                 |

| 3             | 13            | 1:1:2:2                      | $V_{dc1}, V_{dc1} + V_{dc2}, V_{dc2} + V_{dc3}, V_{dc1} + V_{dc2} + V_{dc3},$                                        |

|               |               | (26 V, 26 V, 52 V, 52 V)     | $V_{dc2} + V_{dc3} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$                                                 |

| 4             | 15            | 1:2:2:2                      | $V_{dc1}, V_{dc2}, V_{dc1} + V_{dc2}, V_{dc2} + V_{dc3}, V_{dc1} + V_{dc2} + V_{dc3},$                               |

|               |               | (22 V, 44 V, 44 V, 44 V)     | $V_{dc2} + V_{dc3} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$                                                 |

| 5             | 17            | 1:2:2:3                      | $V_{dc1}, V_{dc2}, V_{dc1} + V_{dc2}, V_{dc2} + V_{dc3}, V_{dc1} + V_{dc2} + V_{dc3}, V_{dc1} + V_{dc2} + V_{dc4},$  |

|               |               | (19 V, 38 V, 38 V, 58 V)     | $V_{dc2} + V_{dc3} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$                                                 |

| 6             | 19            | 1:2:2:4                      | $V_{dc1}, V_{dc2}, V_{dc1} + V_{dc2}, V_{dc2} + V_{dc3}, V_{dc1} + V_{dc2} + V_{dc3}, V_{dc2} + V_{dc4},$            |

|               |               | (17 V, 34 V, 34 V, 68 V)     | $V_{dc1} + V_{dc2} + V_{dc4}, V_{dc2} + V_{dc3} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$                    |

| 7             | 21            | 1:2:3:4                      | $V_{dc1}, V_{dc2}, V_{dc3}, V_{dc4}, V_{dc1} + V_{dc4}, V_{dc2} + V_{dc4}, V_{dc3} + V_{dc4},$                       |

|               |               | (15.5 V, 31 V, 46.5 V, 62 V) | $V_{dc1} + V_{dc3} + V_{dc4}, V_{dc2} + V_{dc3} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$                    |

| 8             | 23            | 1:2:3:5                      | $V_{dc1}, V_{dc2}, V_{dc3}, V_{dc1} + V_{dc3}, V_{dc4}, V_{dc1} + V_{dc4}, V_{dc2} + V_{dc4}, V_{dc3} + V_{dc4},$    |

|               |               | (14 V, 28 V, 42 V, 70 V)     | $V_{dc1} + V_{dc3} + V_{dc4}, V_{dc2} + V_{dc3} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$                    |

| 9             | 25            | 1:2:3:6                      | $V_{dc1}, V_{dc2}, V_{dc3}, V_{dc1} + V_{dc3}, V_{dc2} + V_{dc3}, V_{dc1} + V_{dc2} + V_{dc3},$                      |

|               |               | (13 V, 26 V, 39 V, 78 V)     | $V_{dc1} + V_{dc4}, V_{dc2} + V_{dc4}, V_{dc3} + V_{dc4}, V_{dc1} + V_{dc3} + V_{dc4},$                              |

|               |               |                              | $V_{dc2} + V_{dc3} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$                                                 |

| 10            | 27            | 1:2:4:6                      | $V_{dc1}, V_{dc2}, V_{dc1} + V_{dc2}, V_{dc3}, V_{dc1} + V_{dc3}, V_{dc2} + V_{dc3}, V_{dc1} + V_{dc2} + V_{dc3},$   |

|               |               | (12 V, 24 V, 48 V, 72 V)     | $V_{dc2} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc4}, V_{dc3} + V_{dc4}, V_{dc1} + V_{dc3} + V_{dc4},$                    |

|               |               |                              | $V_{dc2} + V_{dc3} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$                                                 |

| 11            | 29            | 1:2:4:7                      | $V_{dc1}, V_{dc2}, V_{dc1} + V_{dc2}, V_{dc3}, V_{dc1} + V_{dc3}, V_{dc2} + V_{dc3}, V_{dc1} + V_{dc2} + V_{dc3},$   |

|               |               | (11 V, 22 V, 44 V, 77 V)     | $V_{dc1} + V_{dc4}, V_{dc2} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc4}, V_{dc3} + V_{dc4}, V_{dc1} + V_{dc3} + V_{dc4},$ |

|               |               |                              | $V_{dc2} + V_{dc3} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$                                                 |

| 12            | 31            | 1:2:4:8                      | $V_{dc1}, V_{dc2}, V_{dc1} + V_{dc2}, V_{dc3}, V_{dc1} + V_{dc3}, V_{dc2} + V_{dc3}, V_{dc1} + V_{dc2} + V_{dc3},$   |

|               |               | (10 V, 21 V, 41 V, 83 V)     | $V_{dc4}, V_{dc1} + V_{dc4}, V_{dc2} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc4}, V_{dc3} + V_{dc4},$                     |

|               |               |                              | $V_{dc1} + V_{dc3} + V_{dc4}, V_{dc2} + V_{dc3} + V_{dc4}, V_{dc1} + V_{dc2} + V_{dc3} + V_{dc4}$                    |

help of equation (4), the firing angles  $\alpha_i$  are calculated [39].

$$\alpha_i = \sin^{-1}(\frac{i - 0.5}{n}); \quad \text{for } i = 0, 1, 2, 3, \dots, n$$

(4)

# B. MODIFIED NEAREST LEVEL MODULATION SCHEME

An improved low switching frequency modulation scheme needs the THD to be calculated properly. Then the switching angles are substituted in the THD equation to find whether the newer set is increasing or decreasing the THD. Hence, equation (5) is used to calculate the THD [42].

$$THD = \frac{\sqrt{\frac{\pi^2 n^2}{8} - \frac{\pi}{4} \sum_{i=0}^{n-1} (2i+1)\alpha_{i+1} - (\sum_{i=1}^{n} \cos(\alpha_i))^2}}{\sum_{i=1}^{n} \cos(\alpha_i)}$$

(5)

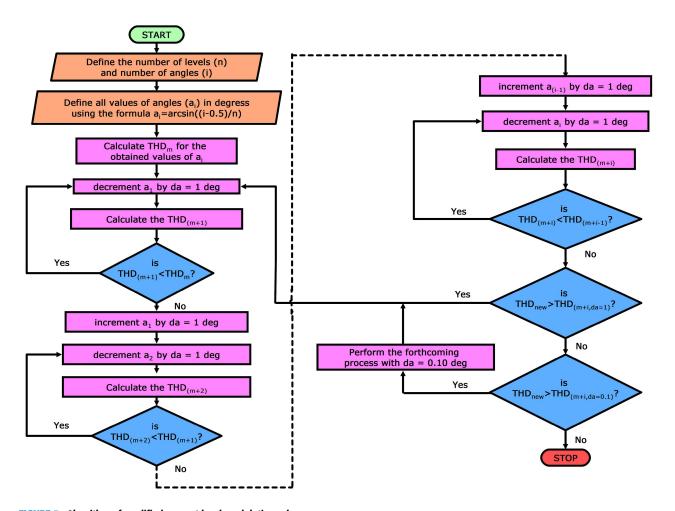

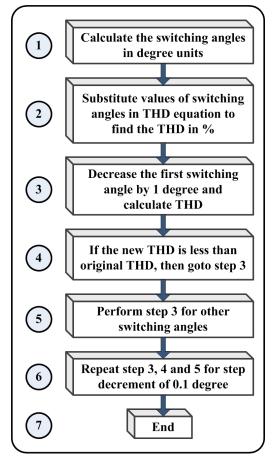

A nine-level configuration is taken up for the study of the algorithm of mNLM. The nine-level configuration has four switching angles. The algorithm begins by calculating the THD with the initial set of switching angles. The first switching angle  $(\alpha_1)$  was reduced by 1 degree, keeping  $\alpha_2$ ,  $\alpha_3$  and  $\alpha_4$  unchanged. The revised THD was calculated with these updated switching angles. When the revised THD was found less than the previous one, the first switching angle  $(\alpha_1)$  was further reduced by 1 degree. This led to the second iteration, and the revised THD was compared with the previous THD. This iteration process continued until there was no further reduction in the THD content when compared to the previous one. When the revised THD was greater than the previous one during the first iteration,  $(\alpha_1)$  was kept the same, and the second switching angle  $(\alpha_2)$  was proceeded with a decrease by 1 degree. With the least THD obtained by varying the first switching angle  $(\alpha_1)$  alone, the second switching  $(\alpha_2)$  was decreased by 1-degree till

FIGURE 2. NLM scheme (a) Comparison of sine wave and MLI output for a one cycle (b) Quarter cycle of the waveform.

FIGURE 3. Algorithm of modified nearest level modulation scheme.

the least THD was obtained. This process continued for all the switching angles. This constitutes the first cycle. Once the last switching angle  $(\alpha_4)$  was varied, and the least THD obtained, the entire process starting from  $(\alpha_1)$  was again repeated for the same 1-degree variation. This formed

the second cycle. The cycles are repeated until the least THD content was obtained. The process undergone so far was again repeated for a change in the switching angle  $\alpha_1$ ,  $\alpha_2$ ,  $\alpha_3$ , and  $\alpha_4$  value of 0.10 degree. This helped to fine-tune the angles.

FIGURE 4. Simplified block diagram of mNLM scheme.

Based on the number of switching angles  $(\alpha_i)$ , the number of cycles required to complete the mNLM algorithm varies. The number of cycles required to complete the algorithm increases as the number of switching angles increases. Figure 3 is the flowchart of the mNLM algorithm. Table 3 shows the significant results for the nine-level configuration. The difference in THD among the various iterations are seen from the iteration number 1, 10, 16, 25, 37, and 42. The difference in THD for the nine-level configuration is due to the equation 5, which takes in to account the sinusoidal nature of MLI output. Table 3 leads to the observation of any absence of any decrease in the THD contents following a decrease in  $\alpha_1$ , and thereby maintained at the same level, between iterations 1 and 10. However, there was a decrease in THD following a decrease of  $\alpha_2$ . There was no further decrease in the THD following a continued decrease in the  $\alpha_2$  after the 10th iteration till the 25th iteration. Hence, the value of  $\alpha_3$ was decreased to enable observation of the change in THD content. The process continues by varying the angle of  $\alpha_4$ .

An interesting observation to note from Table 3 is a significant impact on the THD content seen as a result of variations in angle  $\alpha_4$ . A significant variation was therefore seen in  $\alpha_4$  among the switching angles. The switching angle  $\alpha_1$  was also seen as having the least impact among the switching

**TABLE 3.** Modified NLM (Results of significant iterations).

| Iteration        | 1      | 10     | 16     | 25     | 37     | 42     |

|------------------|--------|--------|--------|--------|--------|--------|

| $\alpha_1$ (deg) | 7.18   | 7.18   | 7.18   | 6.78   | 6.78   | 6.78   |

| $\alpha_2$ (deg) | 22.02  | 21.02  | 21.02  | 21.02  | 20.82  | 20.82  |

| $\alpha_3$ (deg) | 38.68  | 37.68  | 36.68  | 36.68  | 36.28  | 36.28  |

| $\alpha_4$ (deg) | 61.04  | 57.04  | 56.04  | 56.04  | 55.74  | 55.84  |

| THD(%)           | 9.3627 | 8.9813 | 8.9181 | 8.9109 | 8.9028 | 8.9025 |

angles on the THD content. Table 3 leads to the inference of 42 iterations being taken for arriving at the least THD content of 8.9025%, which provides the final switching angles. Iterations 1, 10, and 16 were done with an accuracy of 1 degree whereas, iterations 25, 37, and 42 were done with an accuracy of 0.10 degree. A similar attempt can be made by the above-explained process for the other asymmetric configurations. While implementing mNLM for all the symmetric and asymmetric configurations, it is necessary to redefine the number of levels (n) and the number of angles (i) for each configuration. This is because the number of levels is different for each configuration, and so is the number of angles. Hence, the number of iterations increases with a higher number of switching angles. The algorithm is then repeated from the start to the end. The entire process is an offline implementation where equation 4 and equation 5 are used in the form of a simple MATLAB code. The switching angles are revised to obtain the final mNLM switching angles and programmed into the microcontroller before operating the MLDCLI. The MLDCLI circuits run on the preprogrammed microcontroller program and do not require any further monitoring.

### IV. RESULTS AND ANALYSIS

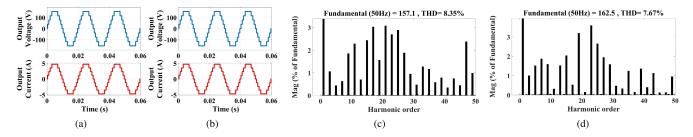

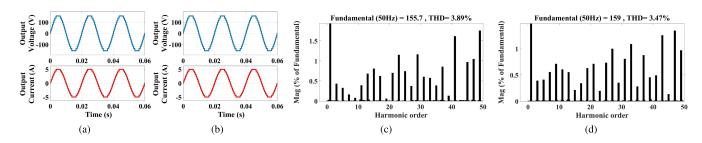

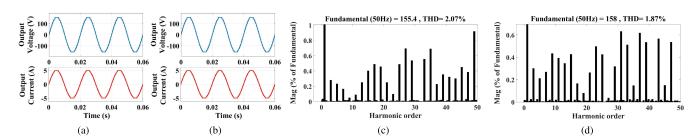

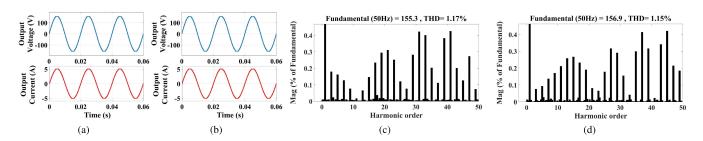

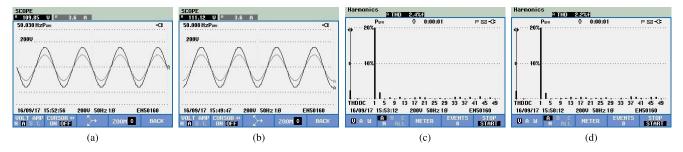

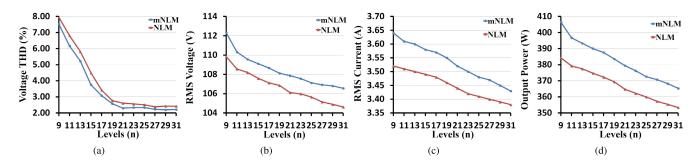

The simulation output is shown from Figure 5 to Figure 8. The MLDCLI was operated to generate 110  $V_{rms}$ , 50 Hz and 400 W output. The results of four critical configurations are shown i.e., 9-level, 17-level, 23-level and 31-level.

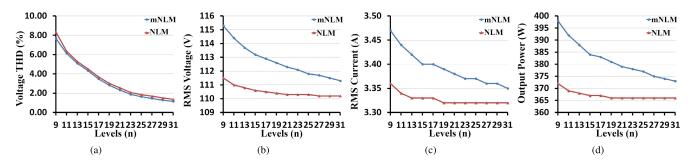

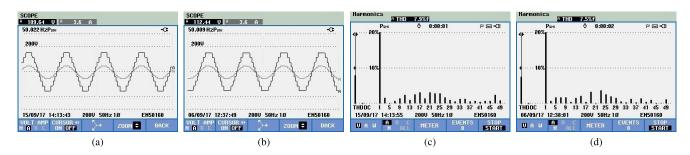

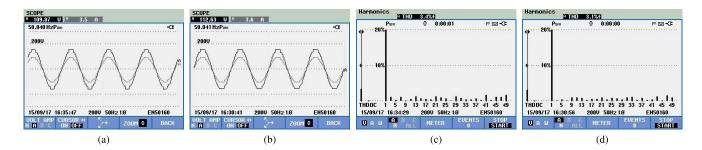

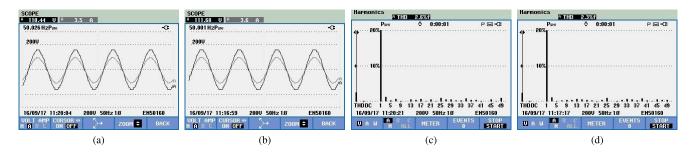

Figure 5 shows the V, and I output for 9-level configuration using NLM and mNLM scheme. It can be observed that the THD generated using NLM scheme was 8.35% while it was 7.67% using mNLM scheme. The V and I waveform for the 17-level configuration is shown in Figure 6 along with the voltage THD. The proposed scheme was found to generate a lesser THD of 3.47%. The 23-level configuration V and I output is shown in Figure 7. The NLM and mNLM schemes were found to generate a THD of 2.07% and 1.87%, respectively. The last configuration is a 31-level output, where the waveform is observed to be nearly sinusoidal shown in Figure 8. The THD associated with NLM and mNLM schemes is also less. Figure 9 represents the performance comparison of various inverter parameters such as V<sub>THD</sub>, V<sub>RMS</sub>, I<sub>RMS</sub>, Output Power from 9-level to 31-level. The graph voltage THD of mNLM is found to be tracing a parallel path to that of NLM with a good margin of difference. Similarly,

FIGURE 5. Simulation output using 9-level configuration (a) NLM V & I waveforms (b) mNLM V & I waveforms (c) THD of voltage output using mLM.

(d) THD of voltage output using mNLM.

FIGURE 6. Simulation output using 17-level configuration (a) NLM V & I waveforms (b) mNLM V & I waveforms (c) THD of voltage output using NLM (d) THD of voltage output using mNLM.

FIGURE 7. Simulation output using 23-level configuration (a) NLM V & I waveforms (b) mNLM V & I waveforms (c) THD of voltage output using NLM (d) THD of voltage output using mNLM.

FIGURE 8. Simulation output using 31-level configuration (a) NLM V & I waveforms (b) mNLM V & I waveforms (c) THD of voltage output using NLM (d) THD of voltage output using mNLM.

the rms voltage and rms current had a difference of range between 1.5 V to 4 V and 0.10 A, respectively, between NLM and mNLM scheme. The output power is the product of voltage and current had shown very good improvement by the use of the proposed modulation scheme over the conventional modulation scheme. Thus, it was concluded from the comparison that the proposed scheme is performed better

than the conventional scheme in all the important inverter parameters.

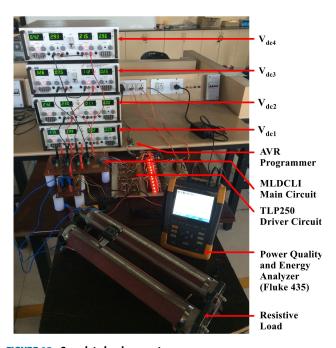

The experimental setup is shown in Figure 15, where the entire setup is demonstrated, which was carried out at the laboratory. The experimental results were carried out using four regulated power supplies; the main MLDCLI circuited fabricated on a PCB with twelve H15R1203 IGBTs,

FIGURE 9. Comparison of simulated NLM and mNLM outputs (a) V<sub>THD</sub> (b) V<sub>RMS</sub> (c) I<sub>RMS</sub> (d) Output power.

FIGURE 10. Experimental output using 9-level configuration (a) NLM V & I waveforms (b) mNLM V & I waveforms (c) THD of voltage output using NLM (d) THD of voltage output using mNLM.

FIGURE 11. Experimental output using 17-level configuration (a) NLM V & I waveforms (b) mNLM V & I waveforms (c) THD of voltage output using NLM (d) THD of voltage output using mNLM.

FIGURE 12. Experimental output using 23-level configuration (a) NLM V & I waveforms (b) mNLM V & I waveforms (c) THD of voltage output using NLM (d) THD of voltage output using mNLM.

AVR Atmega32 microcontroller to generate the gate pulses, TLP250 as driver IC, a rheostat as a resistive load and Fluke435b power quality analyzer to measure the THD. The microcontroller was programmed using a USBasp

programmer, and Fluke 435 power quality analyzer provides a precise THD. Figure 10 to Figure 13 shows the experimental results of the four critical configurations. The experimental results were found to be similar to that of simulation results.

FIGURE 13. Experimental output using 31-level configuration (a) NLM V & I waveforms (b) mNLM V & I waveforms (c) THD of voltage output using NLM (d) THD of voltage output using mNLM.

FIGURE 14. Comparison of experimental NLM and mNLM outputs (a) V<sub>THD</sub> (b) V<sub>RMS</sub> (c) I<sub>RMS</sub> (d) Output power.

FIGURE 15. Complete hardware setup.

The experimental results confirm that the mNLM scheme is superior to the NLM scheme in all the inverter parameters. The comparison of experimental results for all the configurations is shown in Figure 14. The interesting observation from the experimental results is that the reduction in THD at higher MLI levels is large compared to that of the simulation results. It is also noted that with an increase in the number of levels,

TABLE 4. Comparison of THD using mNLM for 9-level configuration (8.35%) with other recent references on NLM.

| Sl. | Reference | THD as per the Reference |

|-----|-----------|--------------------------|

| 1   | [43]      | 9.27%                    |

| 2   | [44]      | 9.12%                    |

| 3   | [45]      | 9.32%                    |

**TABLE 5.** Simulation and experimental results of implementing mNLM for 9-level symmetric configuration on RL load.

| Inverter         | Simulation Results |       | <b>Experimental Results</b> |        |

|------------------|--------------------|-------|-----------------------------|--------|

| Parameters       | NLM                | mNLM  | NLM                         | mNLM   |

| Voltage THD (%)  | 8.57               | 7.89  | 8.3                         | 7.9    |

| Current THD (%)  | 1.81               | 1.28  | 1.9                         | 1.4    |

| RMS Voltage (V)  | 111.5              | 115.3 | 107.44                      | 111.28 |

| RMS Current (A)  | 3.39               | 3.50  | 3.5                         | 3.6    |

| Output Power (W) | 332                | 355   | 330                         | 352    |

the output voltage and current reduced slightly on account of a slightly higher voltage drop across the switches [32]. The same can be observed for the special application of MLI, such as railway transportation electrification [34]. Hence, the mNLM is highly suitable to improve the experimental performance of MMCs.

Table 4 presents the THD generated by some of the recent works using NLM for a 9-level configuration. The proposed mNLM scheme generated 8.35% THD, whereas the NLM in

TABLE 6. Hardware parameters of MLDCLI topology.

| 1  | Output Voltage         | 110 V <sub>rms</sub>             |

|----|------------------------|----------------------------------|

| 2  | Output Current         | 3.6 A <sub>rms</sub>             |

| 3  | Output Power           | 400 W                            |

| 4  | Output ac frequency    | 50 Hz                            |

| 5  | DC sources             | Aplab (64 V / 5 A, 4 nos)        |

| 6  | IGBT                   | H15R1203 (1200 V / 30 A, 12 nos) |

| 7  | Opto-isolator          | TLP250 (12 nos)                  |

| 8  | Controller             | AVR Atmega32 Microcontroller     |

| 9  | Loading Rheostat       | 29 ohms / 5 A                    |

| 10 | Inductive Load         | 50 mH / 5 A                      |

| 11 | Power Quality Analyzer | Fluke 435b                       |

other research work had generated a higher THD. The simulation and experimental results of the proposed modulation scheme on the RL load are presented in Table 5. Table 6 consolidated the hardware parameters for carrying out the experiment on MLDCLI topology.

#### **V. CONCLUSION**

This paper has proposed a modified Nearest Level Modulation scheme for a Multilevel DC-Link Inverter, which is a variant of MMC. The proposed scheme is implemented for twelve different configurations, from 9-level to 31-level in the MLDCLI. The simulation is carried out using the MATLAB Simulink 2015b version, and a hardware prototype of the same is presented. To assess the effectiveness of the proposed modulation scheme, four different inverter output parameters are taken. The analysis is carried out for all the MLDCLI configurations. From the analysis carried out for all the parameters, it is found that the voltage THD has decreased to a very good extent. On the other hand, the output rms voltage, output rms current, and output power are also found to have increased. A promising application of mNLM is to integrate with the renewable energy sources for fundamental switching frequency modulation.

#### **ACKNOWLEDGMENT**

The authors are thankful to the Smart Grid Lab, School of Electrical Engineering, Vellore Institute of Technology, Chennai, India, for the successful completion of the hardware prototype. The authors like to express their sincere gratitude to the Renewable Energy Lab, College of Engineering, Prince Sultan University, Riyadh, Saudi Arabia, for giving the technical guidance for the project. The authors are also grateful to the Department of Energy Technology, Aalborg University, Denmark, for the analysis of the results obtained from the experiment.

# **REFERENCES**

[1] P. R. Bana, K. P. Panda, R. T. Naayagi, P. Siano, and G. Panda, "Recently developed reduced switch multilevel inverter for renewable energy integration and drives application: Topologies, comprehensive analysis and comparative evaluation," *IEEE Access*, vol. 7, pp. 54888–54909, 2019.

- [2] R. M. Sekar, D. Nelson Jayakumar, K. Mylsamy, U. Subramaniam, and S. Padmanaban, "Single phase nine level inverter using single DC source supported by capacitor voltage balancing algorithm," *IET Power Electron.*, vol. 11, no. 14, pp. 2319–2329, Nov. 2018.

- [3] M. D. Manjrekar, P. K. Steimer, and T. A. Lipo, "Hybrid multilevel power conversion system: A competitive solution for high-power applications," *IEEE Trans. Ind. Appl.*, vol. 36, no. 3, pp. 834–841, May/Jun. 2000.

- [4] M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, A. Iqbal, and M. A. Memon, "A new multilevel inverter topology with reduce switch count," *IEEE Access*, vol. 7, pp. 58584–58594, 2019.

- [5] S. Shuvo, E. Hossain, T. Islam, A. Akib, S. Padmanaban, and M. Z. R. Khan, "Design and hardware implementation considerations of modified multilevel cascaded h-bridge inverter for photovoltaic system," *IEEE Access*, vol. 7, pp. 16504–16524, 2019.

- [6] U. Subramaniam, S. Ganesan, M. S. Bhaskar, S. Padmanaban, F. Blaabjerg, and D. J. Almakhles, "Investigations of AC microgrid energy management systems using distributed energy resources and plug-in electric vehicles," *Energies*, vol. 12, no. 14, p. 2834, Jul. 2019.

- [7] Z. Liu, Y. Zhang, S. Zhao, and J. Gong, "A power distribution control strategy between energy storage elements and capacitors for cascaded multilevel inverter with hybrid energy sources," *IEEE Access*, vol. 7, pp. 16880–16891, 2019.

- [8] M. N. Bhukya, V. R. Kota, and S. R. Depuru, "A simple, efficient, and novel standalone photovoltaic inverter configuration with reduced harmonic distortion," *IEEE Access*, vol. 7, pp. 43831–43845, 2019.

- [9] S. Vavilapalli, S. Umashankar, P. Sanjeevikumar, V. Fedák, L. Mihet-Popa, and V. K. Ramachandaramurthy, "A buck-chopper based energy storage system for the cascaded H-bridge inverters in PV applications," *Energy Procedia*, vol. 145, pp. 534–541, Jul. 2018.

- [10] B. Chokkalingam, M. S. Bhaskar, S. Padmanaban, V. K. Ramachandaramurthy, and A. Iqbal, "Investigations of multi-carrier pulse width modulation schemes for diode free neutral point clamped multilevel inverters," *J. Power Electron.*, vol. 19, no. 3, pp. 702–713, May 2019.

- [11] P. Madasamy, V. Suresh Kumar, P. Sanjeevikumar, J. B. Holm-Nielsen, E. Hosain, and C. Bharatiraja, "A three-phase transformerless T-type-NPC-MLI for grid connected PV systems with common-mode leakage current mitigation," *Energies*, vol. 12, no. 12, p. 2434, Jun. 2019.

- [12] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518–523, Sep. 1981.

- [13] T. A. Meynard and H. Foch, "Multi-level conversion: High voltage choppers and voltage-source inverters," in *Proc. 23rd Annu. IEEE Power Elec*tron. Spec. Conf., Jul. 1992, pp. 397–403.

- [14] V. Sridhar, S. Umashankar, P. Sanjeevikumar, V. K. Ramachandaramurthy, L. Mihet-Popa, and V. Fedák, "Control architecture for cascaded Hbridge inverters in large-scale PV systems," *Energy Procedia*, vol. 145, pp. 549–557, Jul. 2018.

- [15] M. D. Siddique, S. Mekhilef, N. M. Shah, and M. A. Memon, "Optimal design of a new cascaded multilevel inverter topology with reduced switch count," *IEEE Access*, vol. 7, pp. 24498–24510, 2019.

- [16] M. M. Zaid and J.-S. Ro, "Switch Ladder modified H-bridge multilevel inverter with novel pulse width modulation technique," *IEEE Access*, vol. 7, pp. 102073–102086, 2019.

- [17] C. Zhang and Z. Gao, "A novel multilevel DC/AC inverter based on three-level half bridge with voltage vector selecting algorithm," *IEEE Access*, vol. 7, pp. 88733–88742, 2019.

- [18] M. G. Prakash, M. Balamurugan, and S. Umashankar, "A new multilevel inverter with reduced number of switches," *Int. J. Power Electron. Drive Syst.*, vol. 5, no. 1, pp. 63–70, 2014.

- [19] N. Prabaharan and K. Palanisamy, "A comprehensive review on reduced switch multilevel inverter topologies, modulation techniques and applications," *Renew. Sustain. Energy Rev.*, vol. 76, pp. 1248–1282, Sep. 2017.

- [20] J. J. Nedumgatt, D. V. Kumar, A. Kirubakaran, and S. Umashankar, "A multilevel inverter with reduced number of switches," in *Proc. IEEE Students' Conf. Electr., Electron. Comput. Sci.*, Mar. 2012, pp. 1–4.

- [21] V. Sridhar and S. Umashankar, "A comprehensive review on CHB MLI based PV inverter and feasibility study of CHB MLI based PV-STATCOM," Renew. Sustain. Energy Rev., vol. 78, pp. 138–156, Oct. 2017.

- [22] G.-J. Su, "Multilevel DC-link inverter," *IEEE Trans. Ind. Appl.*, vol. 41, no. 3, pp. 848–854, May 2005.

- [23] I. Abdalla, J. Corda, and L. Zhang, "Multilevel DC-link inverter and control algorithm to overcome the PV partial shading," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 14–18, Jan. 2013.

- [24] M. Quraan, P. Tricoli, S. D'Arco, and L. Piegari, "Efficiency assessment of modular multilevel converters for battery electric vehicles," *IEEE Trans. Power Electron.*, vol. 32, no. 3, pp. 2041–2051, Mar. 2017.

- [25] S. Sabyasachi, V. B. Borghate, R. R. Karasani, S. K. Maddugari, and H. M. Suryawanshi, "Hybrid control technique-based three-phase cascaded multilevel inverter topology," *IEEE Access*, vol. 5, pp. 26912–26921, 2017.

- [26] M. B. Satti and A. Hasan, "Direct model predictive control of novel h-bridge multilevel inverter based grid-connected photovoltaic system," *IEEE Access*, vol. 7, pp. 62750–62758, 2019.

- [27] M. S. Bhaskar, S. Padmanaban, F. Blaabjerg, D. M. Ionel, and M. H. Rashid, "A novel calculus based unipolar double reference single carrier PWM for single phase t-multilevel inverter with under modulation (<1) for renewable energy applications: Hardware implementation," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Sep. 2018, pp. 1287–1292.

- [28] M. S. Bhaskar, S. Padmanaban, V. Fedák, F. Blaabjerg, and P. Wheeler, "Transistor clamped five-level inverter using non-inverting double reference single carrier PWM technique for photovoltaic applications," in Proc. Int. Conf. Optim. Electr. Electron. Equip. (OPTIM) Intl Aegean Conf. Elect. Mach. Power Electron. (ACEMP), May 2017, pp. 777–782.

- [29] R. Kiran, M. S. Bhaskar, S. Padmanaban, F. Blaabjerg, P. Wheeler, and M. H. Rashid, "Unipolar single reference multicarrier sinusoidal pulse width modulation based 7-level inverter with reduced number of semiconductor switches for renewable energy applications," in *Proc. IEEE* 18th Int. Power Electron. Motion Control Conf. (PEMC), Aug. 2018, pp. 1043–1048.

- [30] T. V. V. S. Lakshmi, N. George, S. Umashankar, and D. P. Kothari, "Cascaded seven level inverter with reduced number of switches using level shifting PWM technique," in *Proc. Int. Conf. Power, Energy Control* (ICPEC), Feb. 2013, pp. 676–680.

- [31] A. A. Gandomi, S. Saeidabadi, S. H. Hosseini, E. Babaei, and M. Sabahi, "Transformer-based inverter with reduced number of switches for renewable energy applications," *IET Power Electron.*, vol. 8, no. 10, pp. 1875–1884, 2015.

- [32] A. Farakhor, R. R. Ahrabi, H. Ardi, and S. N. Ravadanegh, "Symmetric and asymmetric transformer based cascaded multilevel inverter with minimum number of components," *IET Power Electron.*, vol. 8, no. 6, pp. 1052–1060, Jun. 2015.

- [33] J. S. Choi and F. S. Kang, "Seven-level PWM inverter employing seriesconnected capacitors paralleled to a single DC voltage source," *IEEE Trans. Ind. Electron.*, vol. 62, no. 6, pp. 3448–3459, Jun. 2015.

- [34] M. Z. Youssef, K. Woronowicz, K. Aditya, N. A. Azeez, and S. S. Williamson, "Design and development of an efficient multilevel DC/AC traction inverter for railway transportation electrification," *IEEE Trans. Power Electron.*, vol. 31, no. 4, pp. 3036–3042, Apr. 2016.

- [35] C. Dhanamjayulu, G. Arunkumar, B. J. Pandian, C. V. R. Kumar, M. P. Kumar, A. R. A. Jerin, and P. Venugopal, "Real-time implementation of a 31-level asymmetrical cascaded multilevel inverter for dynamic loads," *IEEE Access*, vol. 7, pp. 51254–51266, 2019.

- [36] A. R. Kumar, D. Thangavelusamy, S. Padmanaban, and D. P. Kothari, "A modified PWM Scheme to improve AC power quality for MLIs using PV Source," *Int. J. Power Energy Syst.*, vol. 39, no. 1, pp. 34–41, 2019.

- [37] A. Edpuganti and A. K. Rathore, "A survey of low switching frequency modulation techniques for medium-voltage multilevel converters," *IEEE Trans. Ind. Appl.*, vol. 51, no. 5, pp. 4212–4228, Sep./Oct. 2015.

- [38] P. Hu and D. Jiang, "A level-increased nearest level modulation method for modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 30, no. 4, pp. 1836–1842, Apr. 2015.

- [39] E. Babaei, M. F. Kangarlu, and M. Sabahi, "Dynamic voltage restorer based on multilevel inverter with adjustable dc-link voltage," *IET Power Electron.*, vol. 7, no. 3, pp. 576–590, Mar. 2014.

- [40] M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, A. Iqbal, M. Tayyab, and M. K. Ansari, "Low switching frequency based asymmetrical multi-level inverter topology with reduced switch count," *IEEE Access*, vol. 7, pp. 86374–86383, 2019.

- [41] R. L. Maurya and M. Rajeev, "Implementation of multilevel DC-link inverter for standalone application," in *Proc. Int. Conf. Nascent Technol. Eng. (ICNTE)*, Jan. 2017, Pp. 1–6.

- [42] M. Qi and O. P. Malik, "Apply STATCOM with a novel topology to the power sub grid," in *Proc. Elect. Power Energy Conf. (EPEC)*, Nov. 2014, pp. 242–247.

- [43] R. ShalchiAlishah, D. Nazarpour, S. H. Hosseini, and M. Sabahi, "Novel multilevel inverter topologies for medium and high-voltage applications with lower values of blocked voltage by switches," *IET Power Electron.*, vol. 7, no. 12, pp. 3062–3071, Dec. 2014.

- [44] J. S. M. Ali and R. Kannan, "Investigation of novel symmetric and asymmetric multilevel converter topology with reduced power switches," *Int. J. Power Electron.*, vol. 7, nos. 3–4, pp. 226–242, 2015.

- [45] R. S. Alishah, D. Nazarpour, S. H. Hosseini, and M. Sabahi, "Switched-diode structure for multilevel converter with reduced number of power electronic devices," *IET Power Electron.*, vol. 7, no. 3, pp. 648–656, Mar 2014

A. RAKESH KUMAR (M'14) received the B.E. degree (Hons.) in electrical and electronics engineering from the DMI College of Engineering, Anna University, Chennai, India, in 2011, and the M.Tech. degree (Hons.) in power electronics and drives from the Jerusalem College of Engineering, Anna University, in 2013. He is currently pursuing the Ph.D. degree with the Vellore Institute of Technology, Chennai. He was an Assistant Professor with the Department of EEE, Rajalakshmi

Engineering College, from 2013 to 2015. He had handled various subjects, including power electronics, control system, basic EEE, and digital logic control. He is currently a Teaching Cum Research Assistant with the School of Electrical Engineering, Vellore Institute of Technology. His research interests include electric vehicles, multilevel inverters, inverter modulation techniques, and smart grid and its applications. He is also a member the IEEE PES Society and the IEEE PEL Society.

MAHAJAN SAGAR BHASKAR (M'15) received the bachelor's degree in electronics and telecommunication engineering from the University of Mumbai, Mumbai, India, in 2011, the master's degree in power electronics and drives from the Vellore Institute of Technology, VIT University, India, in 2014, and the Ph.D. degree from the University of Johannesburg, South Africa, in 2019. He was a Researcher Assistant with the Department of Electrical Engineering, Qatar University, Doha,

Qatar. He was as an Assistant Professor and a Research Coordinator with the Department of Electrical and Electronics Engineering, Marathwada Institute of Technology (MIT), Aurangabad, India. He is currently with the Renewable Energy Lab, Department of Communications and Networks Engineering, Prince Sultan University, Riyadh, Saudi Arabia, as an Assistant Professor. He has published scientific articles in the field of power electronics, with particular reference to XY converter family, multilevel dc/dc and dc/ac converter, and high gain converter. He has authored 100 plus scientific articles. He is also a member of the IEEE Industrial Electronics, Power Electronics, Industrial Application, and Power and Energy, Robotics and Automation, and Vehicular Technology Societies, Young Professionals, and various IEEE Councils and Technical Communities. He is also a Reviewer Member of various international journals and conferences, including IEEE and IET. He received IEEE Access Award "Reviewer of Month," in January 2019, for his valuable and thorough feedback on manuscripts and for his quick turnaround on reviews.

UMASHANKAR SUBRAMANIAM (M'09–SM'18) has over 15 years of teaching, research, and industrial Research and Development experience. He was an Associate Professor and the Head of VIT Vellore and a Senior Research and Development and Senior Application Engineer in the field of power electronics, renewable energy, and electrical drives. He is currently an Associate Professor with the Renewable Energy Laboratory, College of Engineering, Prince Sul-

tan University, Saudi Arabia. He has published more than 250 research articles in national and international journals and conferences. He has authored/coauthored/contributed 12 books/chapters and 12 technical articles on power electronics applications in renewable energy, and allied areas. He is also involved in collaborative research projects with various internationaland national-level organizations and research institutions. He is also a member of IACSIT, IDES, and ISTE. He received the Danfoss Innovator Award-Mentor, from 2014 to 2015 and 2017 to 2018, and the Research Award from VIT University, from 2013 to 2018. He also received the INAE Summer Research Fellowship for the year 2014. Under his guidance, 24 P.G. students and more than 25 U.G. students completed the senior design project work, as well as six Ph.D. scholars completed doctoral thesis as a Research Associate. He has taken charge as the Vice Chair of the IEEE Madras Section and the Chair of the IEEE Student Activities, from 2018. He was an Executive Member, from 2014 to 2016, and has been the Vice Chair of the IEEE MAS Young Professional, since 2017, for the IEEE Madras Section. He is also an Editor of Heliyon (Elsevier).

**SANJEEVIKUMAR PADMANABAN** (M'12–SM'15) received the bachelor's degree in electrical engineering from the University of Madras, India, in 2002, the master's degree (Hons.) in electrical engineering from Pondicherry University, India, in 2006, and the Ph.D. degree in electrical engineering from the University of Bologna, Italy, in 2012. He was an Associate Professor with VIT University, from 2012 to 2013. In 2013, he joined the National Institute of Technology, India, as a

Faculty Member. In 2014, he was invited as a Visiting Researcher with the Department of Electrical Engineering, Qatar University, Qatar, funded by the Qatar National Research Foundation (Government of Qatar). He continued his research activities with the Dublin Institute of Technology, Ireland, in 2014. He was an Associate Professor with the Department of Electrical and Electronics Engineering, University of Johannesburg, South Africa, from 2016 to 2018. Since 2018, he has been a Faculty Member with the Department of Energy Technology, Aalborg University, Esbjerg, Denmark. He has authored over 300 scientific articles. He is also a Fellow the Institution of Engineers (FIE), India, the Institution of Telecommunication and Electronics Engineers (FIETE), India, and the Institution of Engineering and Technology (IET), U.K. He received the Best Paper Cum Most Excellence Research Paper Award from IET-SEISCON'13 and IET-CEAT'16 and five Best Paper Awards from ETAEERE'16 sponsored Lecture note in Electrical Engineering, Springer Book Series. He serves as an Editor/Associate Editor/Editorial Board for refereed journals, in particular the IEEE Systems Journal, the IEEE Access journal, the IET Power Electronics, and Journal of Power Electronics (South Korea) and the Subject Editor of the IET Renewable Power Generation, the IET Generation, Transmission & Distribution, and the FACTS journal (Canada).

**DHAFER ALMAKHLES** (M'13) received the B.E. degree in electrical engineering from the King Fahd University of Petroleum and Minerals, Dhahran, Saudi Arabia, in 2006, and the master's (Hons.) and Ph.D. degrees from The University of Auckland, New Zealand, in 2011 and 2016, respectively. Since 2016, he has been with Prince Sultan University, Saudi Arabia, where he is currently the Chairman of the Communications and Networks Engineering Department and the Direc-

tor of Science and Technology Unit. He is also the Leader of the renewable energy research team and the laboratory at Prince Sultan University. His research interests include the hardware implementation of control theory, signal processing, networked control systems, and sliding mode.

JENS BO-HOLM NIELSEN is currently with the Department of Energy Technology, Aalborg University, and the Head of the Esbjerg Energy Section. On these research activities, he established the Center for Bioenergy and Green Engineering, in 2009, for which he serves as the Head. He has vast experience in the field of biorefinery concepts and biogas production—anaerobic digestion. He is also involved in the implementation projects of bio-energy systems in Denmark with

provinces and European states. He has authored more than 300 scientific articles. His research interests include renewable energy, sustainability, and green jobs for all. He was a member on invitation with various capacities in the committee for over 500 various international conferences and an Organizer of international conferences, workshops, and training program in Europe, Central Asia, and China. He has served as the Technical Advisory for many industries in this field. He has executed many large-scale European Union and United Nation projects in research aspects of bioenergy, biorefinery processes, the full chain of biogas, and green engineering.

• • •