Received March 25, 2019, accepted April 19, 2019, date of publication May 6, 2019, date of current version July 25, 2019.

Digital Object Identifier 10.1109/ACCESS.2019.2914854

# **Application of Barycentric Coordinates in Space Vector PWM Computations**

PAWEŁ SZCZEPANKOWSKI, (Member, IEEE), AND JANUSZ NIEZNAŃSKI<sup>®</sup>, (Senior Member, IEEE)

Faculty of Electrical and Control Engineering, Gdańsk University of Technology, 80-233 Gdańsk, Poland

Corresponding author: Janusz Nieznański (janusz.nieznanski@pg.edu.pl)

This work was supported in part by the LINTE<sup>2</sup> Laboratory, Gdańsk University of Technology.

**ABSTRACT** This paper proposes the use of barycentric coordinates in the development and implementation of space-vector pulse-width modulation (SVPWM) methods, especially for inverters with deformed space-vector diagrams. The proposed approach is capable of explicit calculation of vector duty cycles, independent of whether they assume ideal positions or are displaced due to the DC-link voltage imbalance. The use of barycentric coordinates also permits a well-defined and universal approach to the problem of identifying the region in which the reference vector is located. It completely avoids the use of angles, trigonometric functions, and inverse trigonometric functions and is chiefly based on matrix operations which are well suited for digital signal processor implementation. The proposed approach is exposed and validated for the special case of three-level neutral-point clamped (NPC) inverter controlled by a discontinuous space-vector PWM.

**INDEX TERMS** Space-vector PWM, three-level NPC inverter, barycentric coordinates.

## I. INTRODUCTION

The Voltage source inverter topologies become more and more complex with the increasing number of voltage levels and inverter legs. The increase in topological complexity entails exponential increase in the complexity of PWM modulation methods suitable for these inverters. This paper addresses the above problem by proposing the use of barycentric coordinates as a convenient and transparent computational idea applicable to PWM computations. To fix attention, the space-vector type of modulation is assumed throughout the paper (SVPWM). The SVPWM involves selecting appropriate subsets of inverter voltage vectors and computing the application times of those vectors in every modulation period. The aim is to synthesize a sequence of inverter vectors whose average value equals the reference vector. The relative application times of component vectors are usually called duty cycles, and so the SVPWM chiefly deals with selecting the component vectors and computing their duty cycles. The component vectors used in the SVPWM synthesis are usually the inverter voltage vectors corresponding directly to the on/off states of inverter switches. Such vectors will here be called the basic vectors. In some cases it may be advantageous to predefine some sequences of basic vectors, usually called

The associate editor coordinating the review of this manuscript and approving it for publication was Sumant Kadwane.

*virtual vectors*, and use the latter as component vectors in the PWM synthesis.

In the case of two-level inverters, the selection of component vectors usually reduces to a simple task of finding the 60° sector in the space-vector diagram in which the reference vector currently resides. For the three-level NPC inverter and more complex topologies, however, the number of regions to select from is much greater, especially when the DC link voltages are unbalanced. This means that the selection of region (and thus the corresponding component vectors) is no longer a trivial task.

The literature overview below starts by presenting the ideas for SVPWM computations under balanced DC-link voltages. Then, the methods used for active balancing of the DC-link voltages are briefly discussed. And finally, the few concepts for SVPWM computations under DC-link voltage imbalance are outlined.

Several classes of methods of SVPWM for multilevel inverters have been proposed and discussed in the literature. Most of them rely on the nearest three vectors (NTV) approach, meaning that the component vectors used in the synthesis form a triangle comprising the endpoint of the reference vector (*modulation triangle*) on the space–vector diagram. One of the methods, here referred to as the *small reference vectors method*, was proposed in [1]–[3] for the three–level inverters. In this method, the large space–vector

hexagon of the three-level inverter is decomposed into six small hexagons characteristic of two-level inverters. As the first step in the method, the small hexagon containing the reference voltage vector is found, based on the angular position of that vector. This step effectively means determining the 60° angular sector containing the reference vector and the center of the appropriate small hexagon. Then, the original reference vector is replaced by a *small reference vector* whose origin is at the center of the small hexagon. This is done by subtracting the coordinates of the center from the original reference vector. Once this is done, the selection of basic vectors (or the target modulation triangle) can be based on the angular position of the small reference vector, and the duty cycle calculations can proceed as for the two-level inverter. A similar approach is proposed in [4]. A generalization of the considered method to inverters with more levels than three was proposed in [5]. The original reference vector is again replaced by one whose origin is at the center of the appropriate small hexagon; this vector is called the remainder vector. The target small hexagon is found by gradual reduction of the complete space-vector hexagon to smaller ones. In each step the smaller hexagon corresponds to the space-vector diagram of an inverter with number of levels reduced by one. The consecutive centers of smaller hexagons, called vertex vectors, are subtracted from the corresponding consecutive values of modified reference vectors. The main limitation of all variants of the small hexagon method is that they rely on perfect geometry of the space-vector diagrams. That means that the PWM computations under DC-link voltage imbalance can be far from accurate.

References [6]–[9] propose and discuss a method that can be considered a variety of the small reference vectors method. The method is discussed in detail for the three–level inverter. It also reduces the problem of multilevel PWM computations to the two-level case. Just like the previous method, it starts by determining the 60° angular sector containing the reference vector (again, using the current angular position of that vector). Then, the modulation triangle is found based on two integers  $k_1$  and  $k_2$  computed from the Cartesian  $(\alpha\beta)$ coordinates of the reference vector. The combination of the integers may directly indicate the target modulation triangle or a rhombus made of two target triangles. In the latter case an additional test is necessary to decide which of the two triangles should be selected (the test is based on the  $\alpha\beta$  coordinates of the reference vector and the above mentioned integers). Once the modulation triangle is determined, the small reference vector can be evaluated and the basic vector duty cycles can be computed from the local  $\alpha\beta$  coordinates of the small reference vector, just like for the two-level inverter. This approach also assumes perfect geometry of the spacevector diagrams and thus can be affected by DC-link voltage imbalance.

A number of references propose transformations of the space-vector diagrams from the Cartesian (or  $\alpha\beta$ ) coordinates to other frames. One of them is the gh coordinate system proposed in [10], also referred to as the gh frame [11],

the  $60^{\circ}$  coordinate system [12], [13] or mn coordinates [14]. The transformation results in all basic vectors having integer coordinates, which simplifies the determination of the modulation triangle and computation of the component vector duty cycles. The 60° sector of the space-vector diagram containing the reference vector is determined from the angular position of that vector, while the rest of computations are freed from angles and cumbersome trigonometry. Similarly to the small reference vectors method, the main drawback of the method is its reliance on the assumed regularity of space-vector diagram. The method in its basic form does not address the problem of DC-link voltage imbalance. Another transformation of the space-vector coordinate system is proposed in [15]. The new coordinate system is denoted as the  $\alpha'\beta'$  coordinate frame and the main feature of that system is that all state vectors have integer coordinates. Unlike the gh frame, which leaves the geometry of the space-vector diagram unchanged, the  $\alpha'\beta'$  coordinate system changes the shape of the diagram (e.g. transforming circular trajectories of reference vector to elliptic trajectories). Other than this, the properties of this coordinate system are similar to the gh frame. The selection of modulation triangle and duty cycle calculations are again based on implicit assumption of undistorted space-vector diagram.

The problem of balancing the DC-link voltages has quite rich literature. In general, the balancing actions can be based on appropriately changing the switch state sequences and/or adjusting the application times of the switch states representing the redundant (i.e. short) voltage vectors [2], [3], [9], [16]–[18]. To reduce undesired effect on the DC-link voltages, some solutions ([9], [19]) suppress the use of medium vectors (i.e. vectors that do not have alternative switch state options) for higher modulation indexes. Considered in [20]–[22] is the modulation of the three–level NPC inverter using virtual vectors. In all of the above approaches the duty cycles are only calculated under the assumption of balanced DC-link voltages. Obviously, the use of ideal vector positions under DC-link voltage imbalance means imprecise voltage synthesis, which translates into distortion of load currents.

One of the few attempts to compute the duty cycles of the actual (i.e. non-ideal) component vectors for the three-level NPC inverter was presented in [23]. The authors proposed an extension of the gh frame method of [10] to include accurate duty cycle calculations under DC-link imbalance. The idea, called the *method of projections*, is quite complex and derived after a complex analysis of geometric relationships between the basic vectors displaced by the DC-link voltage imbalance. The approach is hardly extendable to other cases, for instance a different type of component vectors (e.g. virtual vectors) or different inverter topologies (e.g. four-leg inverters or inverters with more than three levels). A more universal method was proposed in [24]. The calculations of duty cycles are performed in a frame called abc coordinates. This frame is made of three axes -a, b and c – corresponding to the respective three phases of the inverter, but forming a

three–dimensional orthogonal system rather than the standard planar system with the abc axes rotated by multiples of  $2\pi/3$ . It permits quite simple representation of DC–link voltage imbalance and computation of duty cycles under imbalance. The method can be used for multilevel three–leg and four–leg inverters.

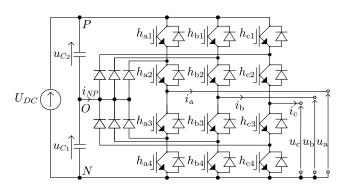

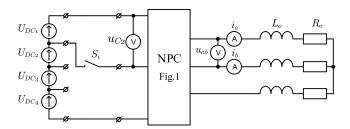

This paper also proposes a computational approach supporting explicit space-vector PWM computations for multilevel inverters with possible DC-link voltage imbalance. The key idea in the proposed arithmetic is the use of barycentric coordinates for the duty cycle computations and selection of the modulation triangle. The first attempt to put the idea forth was [25], where it was rather unfortunately related to finite element shape functions (the idea passed unnoticed). In this paper the presentation of the idea is completely redesigned and uses a new case study for illustration. Unlike the method of [24], which uses a special coordinate frame, the proposed method is applicable directly to the space-vector diagrams in the natural Cartesian coordinates  $(\alpha\beta)$ . The method can be applied to all types of multilevel NPC inverters (and other types of power converters, notably the matrix converters), but here its potential is presented and discussed using the threelevel NPC inverter (Fig. 1) and a particular type of modulation (discontinuous modulation with switch commutations occurring only in two phases in each modulation period).

FIGURE 1. Three-level NPC inverter.

It is important to underline that the proposed use of barycentric coordinates is only a useful and helpful mathematical aid for both the development and implementation of particular SVPWM solutions. The very fact that vector selections and duty cycle computations are based on barycentric coordinates does not entail any effect on the properties of the modulation (like THD, switching frequency and so on).

Section II explains the general idea of PWM computations based on barycentric coordinates. Section III presents the proposed discontinuous SVPWM modulation. Section IV provides laboratory test results of the algorithm and Section V concludes the paper.

# II. PWM COMPUTATIONS BASED ON BARYCENTRIC COORDINATES

In the case of three-leg inverters the voltage vectors used in the PWM synthesis can be considered points on a

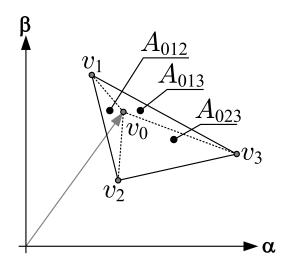

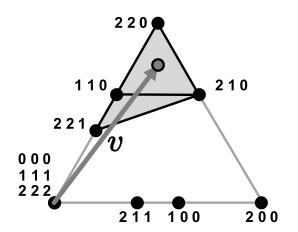

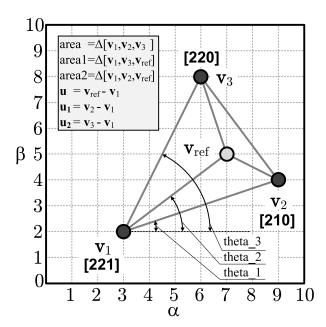

**FIGURE 2.** Illustration of the representation of an arbitrary reference vector  $v_0$  as a point inside a triangle.

two-dimensional  $\alpha\beta$  plane. In most cases considered in the literature, the reference vector is synthesized using the three nearest component vectors, and this approach is also assumed here to fix attention. Consider an arbitrary reference vector  $v_0$  on the  $\alpha\beta$  plane and arbitrary three nearest component voltage vectors  $v_1$ ,  $v_2$  and  $v_3$  (Fig. 2). The computation of vector duty cycles amounts to expressing the reference vector position as a linear combination of the component vectors. It is exactly the same problem as expressing the Cartesian coordinates of a point inside a triangle in terms of the barycentric coordinates (or area coordinates) of that point [26]. Thus, the coordinates of vector  $v_0$  in Fig. 2 can be expressed using the coordinates of  $v_1$ ,  $v_2$  and  $v_3$  as follows:

$$\begin{bmatrix} v_{0\alpha} \\ v_{0\beta} \end{bmatrix} = \begin{bmatrix} v_{1\alpha} & v_{2\alpha} & v_{3\alpha} \\ v_{1\beta} & v_{2\beta} & v_{3\beta} \end{bmatrix} \begin{bmatrix} N_1 \\ N_2 \\ N_3 \end{bmatrix}$$

(1)

where  $N_1$ ,  $N_2$  and  $N_3$  are the barycentric coordinates of  $v_0$  which can be evaluated by

$$\begin{bmatrix} N_1 & N_2 & N_3 \end{bmatrix} = \begin{bmatrix} \frac{A_{023}}{A_{123}} & \frac{A_{013}}{A_{123}} & \frac{A_{012}}{A_{123}} \end{bmatrix}$$

(2)

with the  $A_{ijk}$  symbols representing the areas of the triangles defined by vertices  $v_i$ ,  $v_j$  and  $v_k$ . In other words, the barycentric coordinates are equal to the normalized areas of their corresponding triangles. The areas can be computed straight from the  $\alpha\beta$  coordinates of the appropriate component vectors by

$$A_{ijk} = \frac{1}{2} \cdot \begin{bmatrix} v_{i\alpha} & v_{i\beta} & 1\\ v_{j\alpha} & v_{j\beta} & 1\\ v_{k\alpha} & v_{k\beta} & 1 \end{bmatrix}$$

(3)

From the viewpoint of PWM, the barycentric coordinates can be interpreted as duty cycles of the component vectors required to synthesize the reference vector. It is worth noting that the computation of duty cycles in terms of barycentric coordinates can be based directly on the actual positions of the component vectors rather than their ideal positions

without affecting the ease of computations. What is more, the proposed computing approach readily extends to more complex problems of PWM synthesis (e.g. inverters with more levels, four-leg inverters, matrix converters and others).

The above considerations lead to the following general conclusion about the use of barycentric coordinates in the PWM computations:

Conclusion 1: The use of barycentric coordinates in the PWM computations permits effective and uniform evaluation of the duty cycles of component voltage vectors, independent of the possible displacements of these vectors from their ideal positions.

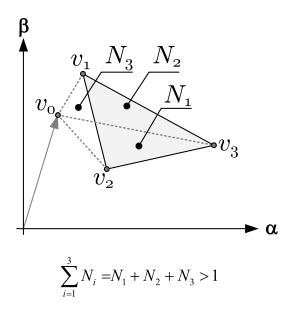

FIGURE 3. Illustration of a vector  $v_0$  lying outside the considered triangle.

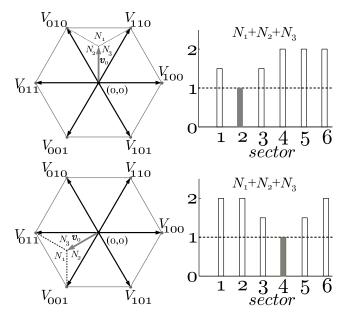

The barycentric coordinates have a very useful additional property that their sum equals unity if they are computed for a point inside the triangle (as in Fig. 2), but it is greater than unity if the point lies outside the triangle (as illustrated in Fig. 3). Thus, a uniform and effective method to find the triangle or triangles containing the reference vector can be to compute some candidate sums of barycentric coordinates and then select the smallest one (ideally equal to 1). This idea is illustrated in Fig. 4 for the case of two-level inverter. The lowest sum of barycentric coordinates computed for all triangular regions in which the reference vector may lie (here equivalent to sectors) appropriately indicates the actual reference vector location. The illustrated case is very simple, but for more complex space-vector diagrams the localization of reference vector in the appropriate region can be a complex task (cf. the considerations in Section III). Thus, a second general conclusion about the use of barycentric coordinates in the PWM computations can be formulated as follows:

Conclusion 2: Barycentric coordinates can be used as the basis of a universal method for locating the region comprising the reference vector.

The above general conclusions will be illustrated and supported by the discussions and results presented in the sequel.

FIGURE 4. Illustrative example of how the lowest sum of barycentric coordinates indicates the triangular region containing the reference vector.

FIGURE 5. Basic vectors of the three-level NPC inverter for balanced DC-link voltages.

# CALCULATION OF THE $\alpha\beta$ COORDINATES OF BASIC VECTORS

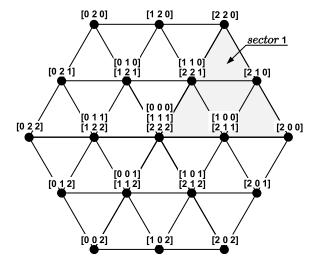

Fig. 5 shows the basic vectors of the three-level NPC inverter for the case of balanced DC-link voltages. The three-digit vectors next to the basic vectors of general form

$$\mathbf{H} = \begin{bmatrix} h_a & h_b & h_c \end{bmatrix} \tag{4}$$

represent the switch states according to the following convention:  $h_x = 0$  if the corresponding phase is connected to the DC-link potential N,  $h_x = 1$  if the corresponding phase is connected to the DC-link potential O, and  $h_x = 2$  if the corresponding phase is connected to the DC-link potential P, with the subscript x standing for a, b or c.

Any imbalance in the DC link, here expressed in terms of the neutral point (NP) imbalance index

$$\upsilon_{\Delta} = \frac{u_{C2} - u_{C1}}{U_{DC}} \tag{5}$$

will result in the medium vectors being displaced and the short vectors being split and displaced (as illustrated in Fig. 6 for sector 1).

FIGURE 6. Basic vectors of the 3-level NPC inverter for unbalanced DC-link voltages ( $v_{\Delta}=0.1$ ); only sector 1 shown.

Whether the DC link is balanced or unbalanced, the  $\alpha\beta$  coordinates of the inverter basic vectors can be computed by applying the Clarke transformation to their corresponding vectors of inverter leg voltages

$$\mathbf{v} = \begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = \begin{bmatrix} 2/3 & -1/3 & -1/3 \\ 0 & 1/\sqrt{3} & -1/\sqrt{3} \end{bmatrix} \mathbf{u}$$

(6)

where

$$\mathbf{u} = \begin{bmatrix} u_a \\ u_b \\ u_c \end{bmatrix} \tag{7}$$

The leg voltages  $u_a$ ,  $u_b$  and  $u_c$  are defined in Fig. 1. It is easily verified by inspection that they can be evaluated using the matrix formula below

$$\mathbf{u} = \mathbf{C} \cdot \mathbf{u}_{DC} \tag{8}$$

where  $\mathbf{u}_{DC}$  is the following vector of DC-link potentials

$$\mathbf{u}_{DC} = \begin{bmatrix} u_P \\ u_O \\ u_N \end{bmatrix} = \begin{bmatrix} U_{DC} \\ u_{C1} \\ 0 \end{bmatrix} \tag{9}$$

and  ${\bf C}$  is the following DC-link-to-leg-voltage conversion matrix

$$\mathbf{C} = \begin{bmatrix} c_{aP} & c_{aO} & c_{aN} \\ c_{bP} & c_{bO} & c_{bN} \\ c_{cP} & c_{cO} & c_{cN} \end{bmatrix}$$

(10)

Each row in the above matrix represents the inverter switch states in the corresponding leg as follows

$$\begin{bmatrix} c_{xP} & c_{xO} & c_{xN} \end{bmatrix} = \begin{cases} \begin{bmatrix} 0 & 0 & 1 \end{bmatrix} \Leftrightarrow h_x = 0 \\ 0 & 1 & 0 \end{bmatrix} \Leftrightarrow h_x = 1 \\ 1 & 0 & 0 \end{bmatrix} \Leftrightarrow h_x = 2 \end{cases}$$

(11)

# III. PROPOSED DISCONTINUOUS SVPWM

The discontinuous space–vector PWM has been chosen for the case study in this paper. This kind of modulation is used to reduce the switching frequency of the inverter and thus the switching losses [27], [28]. The reason for developing such a modulation scheme by the authors was a demanding coal mine application. This section briefly discusses the sequences of switch states to be used in the proposed modulation algorithm and presents the algorithm itself.

**TABLE 1.** Sequences of switch states used in the proposed PWM (sector 1).

| Switch<br>sequence<br>symbol | $\begin{array}{lll} Switch & sequence & contents \\ (shortened & to & H_1-H_2-H_3 \\ format) & \end{array}$ |

|------------------------------|-------------------------------------------------------------------------------------------------------------|

| $\mathbf{S_1}$               | [0 0 0] - [1 0 0] - [1 1 0]                                                                                 |

| $\mathbf{S_2}$               | [1 1 1] - [1 1 0] - [1 0 0]                                                                                 |

| $S_3$                        | [2 2 2] - [2 2 1] - [2 1 1]                                                                                 |

| $S_4$                        | [1 1 1] - [2 1 1] - [2 2 1]                                                                                 |

| $S_5$                        | [2 1 1] - [1 1 1] - [1 1 0]                                                                                 |

| $S_6$                        | [1 0 0] - [2 0 0] - [2 1 0]                                                                                 |

| $S_7$                        | [2 1 1] - [2 1 0] - [2 0 0]                                                                                 |

| $S_8$                        | [1 1 0] - [2 1 0] - [2 2 0]                                                                                 |

| $S_9$                        | [2 2 1] - [2 2 0] - [2 1 0]                                                                                 |

| $S_{10}$                     | [1 0 0] - [1 1 0] - [2 1 0]                                                                                 |

| $S_{11}$                     | [2 2 1] - [2 1 1] - [2 1 0]                                                                                 |

| $S_{12}$                     | [2 1 1] - [2 1 0] - [1 1 0]                                                                                 |

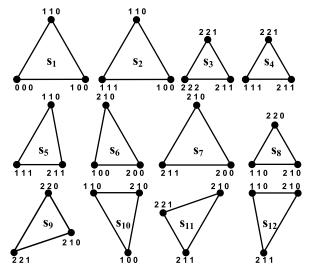

# A. SEQUENCES OF SWITCH STATES

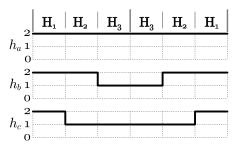

The proposed discontinuous PWM uses three different switch states arranged in symmetric  $\mathbf{H_1}$ – $\mathbf{H_2}$ – $\mathbf{H_3}$  |  $\mathbf{H_3}$ – $\mathbf{H_2}$ – $\mathbf{H_1}$  state sequences. The sequences are each designed in such a way as to minimize the number of transistor state changes per PWM period, and thus to minimize the switching frequency and switching losses. To each sequence of switch states there corresponds a triangular region defined by the switch states  $h_a$ ,  $h_b$  and  $h_c$ . The collection of sequences to be used in the modulation is such that for any reference vector there are two candidate regions (triangles) and state sequences. This redundancy allows active balancing of the DC-link voltages (as explained in the following section). Table 1 shows all sequences of switch states to be used in the case of reference vector residing in sector 1 (only the left halves of the sequences are explicitly specified). For illustration, Fig. 7

FIGURE 7. Timing diagram of an example switch state sequence (S<sub>3</sub>) of the considered discontinuous PWM.

FIGURE 8. Vector triangles corresponding to switch state sequences listed in Table 1.

FIGURE 9. Example reference vector and candidate modulation triangles.

shows the timing diagram of switch state sequence  $S_3$ . The triangular regions corresponding to the sequences in Table 1 are shown in Fig. 8.

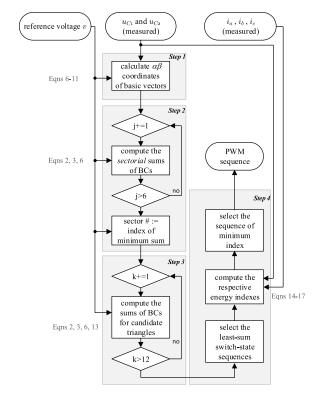

## B. THE ALGORITHM

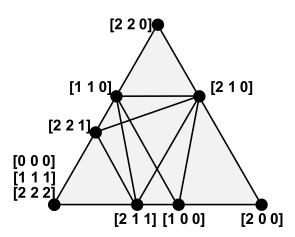

The proposed modulation algorithm will be explained assuming that the reference voltage vector has coordinates  $v_{\alpha}=0.3$  and  $v_{\beta}=0.4$  (in pu), which corresponds to the vector location shown in Fig. 9. To select the appropriate triangle of basic vectors, it is convenient first to find the main angular sector

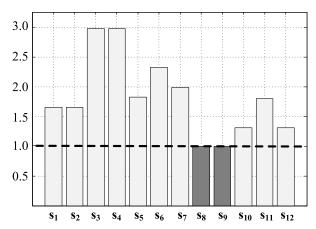

FIGURE 10. Triangles in sector 1 and the corresponding sums of barycentric coordinates.

in which the reference vector is located. This task can be accomplished based on Conclusion 2, that is, by computing the sums of barycentric coordinates corresponding to the six triangles defining the sectors (i.e. triangles whose vertices are zero vectors and the longest vectors 200, 220, 020, 022, 002 and 202).

The next step is finding the small triangle embracing the reference vector. Again, this can be based on Conclusion 2. To this end, consider the following  $12 \times 3$  matrix of barycentric coordinates:

$$\mathbf{N}_{SECTOR1} = \begin{bmatrix} \mathbf{N}_1 \\ \mathbf{N}_2 \\ \dots \\ \mathbf{N}_8 \\ \mathbf{N}_9 \\ \dots \\ \mathbf{N}_{12} \end{bmatrix} = \begin{bmatrix} N_{000} & N_{100} & N_{110} \\ N_{111} & N_{110} & N_{100} \\ \dots \\ N_{110} & N_{210} & N_{220} \\ N_{221} & N_{220} & N_{210} \\ \dots \\ N_{211} & N_{210} & N_{110} \end{bmatrix}$$

(12)

where each row corresponds to one triangle in Fig. 8. The barycentric coordinates in (12) can be computed using (2) and (3), with the  $\alpha\beta$  coordinates evaluated from (6). By summing up the coordinates in each row one obtains the following 12–by–1 matrix:

$$\mathbf{N}_{\Sigma} = \begin{bmatrix} N_{000} + N_{100} + N_{110} \\ N_{111} + N_{110} + N_{100} \\ \dots \\ N_{110} + N_{210} + N_{220} \\ N_{221} + N_{220} + N_{210} \\ \dots \\ N_{211} + N_{210} + N_{110} \end{bmatrix}$$

(13)

The sums of barycentric coordinates corresponding to the considered location of reference vector are shown in Fig. 10. Note that the results corresponding to sequences  $S_1$  and  $S_2$  will be identical, and the same applies to sequences  $S_3$  and  $S_4$ . This can either be exploited in the arrangement of computations or disregarded – for the sake of simplicity and effectiveness of the code (the latter is the suggested solution). The results indicate that two small triangles corresponding to

sequences  $S_8$  and  $S_9$  contain the considered reference vector. As observed earlier, the redundancy of candidate triangles and sequences can be used in active balancing of DC-link voltages. The ultimate choice can be based on the predicted influence of the choice on the NP imbalance index. It should be noted that the computation of barycentric coordinates and location of their lowest sums is very well supported by modern DSP technology and thus proceeds very fast. For inverters with more levels than three the process can be further sped up (if necessary) by grouping the candidate modulation triangles into smaller sets; this can be easily done based on the criterion of magnitude of the reference vector.

A simple analysis of the four possible combinations of the signs of the imbalance voltage and the average neutral point current leads to the conclusion that it is sufficient to compare the following capacitor energy indexes

$$\varepsilon_8 = i_{NP8} \cdot sign(\upsilon_{\Delta})$$

$$\varepsilon_9 = i_{NP9} \cdot sign(\upsilon_{\Delta})$$

(14)

where  $i_{NP8}$  and  $i_{NP9}$  are estimates of the expected average neutral point currents corresponding to the respective switch state sequences. If  $\varepsilon_8$  is greater than  $\varepsilon_9$ , sequence  $\mathbf{S}_9$  should be selected; otherwise, the better choice is sequence  $\mathbf{S}_8$ . The evaluation of  $i_{NP8}$  and  $i_{NP9}$  is explained below.

To fix attention, assume again the location of reference vector as shown in Fig. 9. For algebraic convenience the sequences listed in Table 1 can be represented by the following matrices (shown for  $S_8$  and  $S_9$  only):

$$\mathbf{S}_{8} = \begin{bmatrix} 1 & 1 & 0 \\ 2 & 1 & 0 \\ 2 & 2 & 0 \end{bmatrix} \quad \mathbf{S}_{9} = \begin{bmatrix} 2 & 2 & 1 \\ 2 & 2 & 0 \\ 2 & 1 & 0 \end{bmatrix} \quad (15)$$

Based on the ideas for *NP* current calculation presented in [16], the estimates corresponding to both sequences can be obtained by

$$i_{NP8} = \mathbf{N}_8 \cdot (\mathbf{J} - abs (\mathbf{S}_8 - \mathbf{J})) \cdot \mathbf{i}^T$$

$$i_{NP9} = \mathbf{N}_9 \cdot (\mathbf{J} - abs (\mathbf{S}_9 - \mathbf{J})) \cdot \mathbf{i}^T$$

(16)

where  $N_8$  and  $N_9$  are 1-by-3 vectors of barycentric coordinates as defined in (12), **J** denotes an all-ones 3-by-3 matrix, **i** is the vector of inverter output currents defined by

$$\mathbf{i} = \begin{bmatrix} i_a & i_b & i_c \end{bmatrix} \tag{17}$$

and abs(.) represents componentwise absolute value. The flowchart of the proposed algorithm is presented in Fig. 11.

#### **IV. EXPERIMENTAL RESULTS**

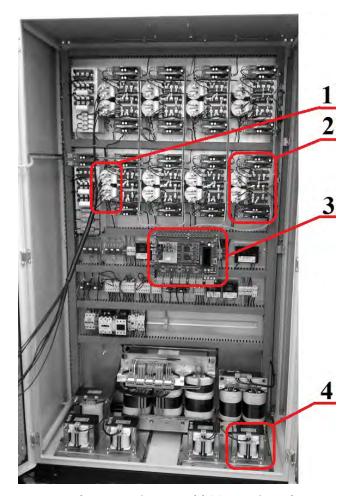

A simplified schematic diagram of the laboratory setup is presented in Fig. 12, while the parameters of the schematic are presented in Table 2. The converter used in the laboratory tests is shown in Fig. 13. As anticipated in Section II, the use of actual component vectors rather than ideal component vectors in the PWM computations permits undistorted current generation despite possible DC–link voltage imbalance.

FIGURE 11. Flowchart of the proposed algorithm (BCs stands for barycentric coordinates).

FIGURE 12. Simplified schematic diagram of the laboratory setup.

TABLE 2. Basic parameters of the laboratory setup.

| symbol           | value                  | description                        |

|------------------|------------------------|------------------------------------|

| $U_{DC1-4}$      | 200V                   | DC voltage supply (4x30V)          |

| $C_1$            | $400\mu F$             | upper capacitor (Fig.1)            |

| $C_2$            | $400\mu F$             | lower capacitor (Fig.1)            |

| $R_o$            | $25\Omega$             | load resistor                      |

| $\overline{L_o}$ | 6mH                    | load inductor                      |

| $f_c$            | 10kHz                  | PWM frequency                      |

| $f_n$            | 50Hz                   | fundamental frequency              |

| $S_1$            | ON/OFF                 | neutral point additional switch    |

| $V_{ref}$        | 0.8 pu                 | reference voltage ratio            |

| $v_{\alpha o}$   | $V_{ref}cos(2\pi f_n)$ | reference voltage in $\alpha$ axis |

| $v_{\beta o}$    | $V_{ref}sin(2\pi f_n)$ | reference voltage in $\beta$ axis  |

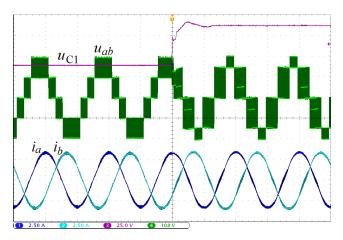

Fig. 14 shows sample experimental results demonstrating this capability of the proposed algorithm. Initially the converter works with balanced DC-link voltages, whereupon a

FIGURE 13. Laboratory NPC inverter model: (1) connection to the DC supplies, (2) one three level leg, (3) DSP control card with TMS320C6713 and FPGA device, (4) load Lo inductor.

FIGURE 14. Output currents of the inverter controlled by the proposed SVPWM for a negative 50% step change in the NP imbalance.

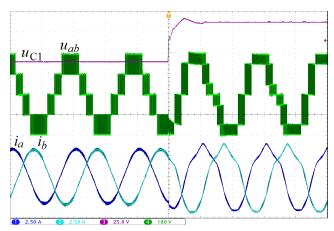

step change in the NP voltage is forced by the contactor  $S_1$ . The quality of currents is unaffected by the huge imbalance. By contrast, Fig. 15 shows how the current quality is affected by the imbalance in the case of using ideal vector positions in the PWM computations.

FIGURE 15. Output currents of the inverter controlled by SVPWM neglecting the DC-link imbalance (for a negative 50% step change in the NP imbalance).

FIGURE 16. Active balancing of the DC-link voltage imbalance.

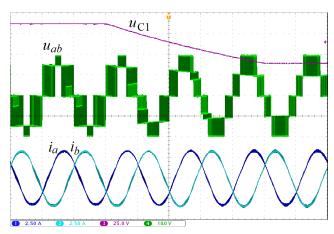

Another important advantage of the proposed modulation is its ability to actively compensate the DC-link voltage imbalance. Fig. 16 shows sample results obtained for the proposed modulation in the case of a large initial imbalance. The  $u_{C1}$  voltage, initially elevated to 150% of its nominal value, quickly returns to the correct value thanks to the appropriate use of redundant sequences. Again, the currents remain undistorted all along the balancing process.

As already observed, the use of barycentric coordinates can greatly help in the development of PWM computations, but it does not influence the results of computations (that is, the duty cycles). Therefore, there is no point in comparing the properties of particular modulation methods (e.g. THD) using the proposed arithmetic with ones based on other mathematical recipes. What can be assessed comparatively is computational effectiveness of the proposed approach and conventional approaches. To this end, the duty cycle computation time of a routine based on barycentric coordinates was compared with the time used by a routine based on trigonometric functions (the latter can be classified as the method of projections presented in [23]). Both routines, contained in the code listing presented in the appendix, compute the

FIGURE 17. Definition of variables used in the benchmarking code.

**TABLE 3.** Benchmarking conditions.

| parameter                                              | description                                           |

|--------------------------------------------------------|-------------------------------------------------------|

| processor type                                         | DSP Texas Instruments                                 |

| model                                                  | TMS320C6672                                           |

| clock                                                  | 1GHz                                                  |

| format of numbers                                      | single precision IEEE 754                             |

| library of trigonometric func-<br>tions                | dedicated DSP Math Library for Floating Point Devices |

| compiler optimization level (Code Composer Studio 8.0) | O-2                                                   |

| DSP core usage                                         | computations performed by CORE1 only                  |

**TABLE 4.** Benchmarking results.

| parameter                                      | description                    |

|------------------------------------------------|--------------------------------|

| duty cycle d1_trig                             | 0.5                            |

| duty cycle d2_trig                             | 0.333                          |

| duty cycle d1_new                              | 0.5                            |

| duty cycle d2_new                              | 0.333                          |

| total DSP cycles for the method of projections | 859 (program code lines 57-71) |

| total DSP cycles for the proposed method       | 61 (program code lines 84-89)  |

duty cycles of vector  $\mathbf{v}_{ref}$  shown in Fig. 17. The modulation triangle corresponds to sequence  $\mathbf{S_9}$  (see Fig. 8). Because of the DC-link voltage imbalance ( $\upsilon_{\Delta}=0.1$ ) the triangle is not equilateral. This complicates the trigonometric computations and is completely insignificant for the arithmetic using barycentric coordinates. The test conditions are specified in Table 3, while the test results are given in Table 4. As can

be seen, the proposed arithmetic is many times faster than the conventional approach.

#### V. CONCLUSION

The use of barycentric coordinates is proposed as a tool for space–vector PWM computations, especially for complex and unbalanced lattices of inverter vectors. The use of these coordinates can facilitate both the development and implementation of particular SVPWM algorithms. The proposed approach completely avoids calculations based on angles, trigonometric functions and inverse trigonometric functions. It is well suited for implementation on digital signal processors.

The general idea of SVPWM computations based on the barycentric coordinates was exposed and validated for the special case of the three–level NPC inverter controlled by a discontinuous SVPWM, but the idea easily extends to more complex converters.

## **REFERENCES**

- J.-H. Suh, C.-H. Choi, and D.-S. Hyun, "A new simplified space-vector PWM method for three-level inverters," in *Proc. 14th Annu. Appl. Power Electron. Conf. Expo.*, vol. 1, Mar. 1999, pp. 515–520.

- [2] J. H. Seo, C. H. Choi, and D.-S. Hyun, "A new simplified space-vector PWM method for three-level inverters," *IEEE Trans. Power Electron.*, vol. 16, no. 4, pp. 545–550, Jul. 2001.

- [3] H. Zhang, A. V. Jouanne, S. Dai, A. K. Wallace, and F. Wang, "Multilevel inverter modulation schemes to eliminate common-mode voltages," *IEEE Trans. Ind. Appl.*, vol. 36, no. 6, pp. 1645–1653, Nov. 2000.

- [4] A. Bellini and S. Bifaretti, "Comparison between sinusoidal PWM and space vector modulation techniques for NPC inverters," in *Proc. IEEE Russia Power Tech*, Jun. 2005, pp. 1–7.

- [5] Y. Deng, K. H. Teo, and R. G. Harley, "A fast and generalized space vector modulation scheme for multilevel inverters," in *Proc. 28th Annu. IEEE Appl. Power Electron. Conf. Exposit.* (APEC), Mar. 2013, pp. 1239–1243.

- [6] A. K. Gupta and A. M. Khambadkone, "A space vector PWM scheme for multilevel inverters based on two-level space vector PWM," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1631–1639, Oct. 2006.

- [7] A. K. Gupta and A. M. Khambadkone, "A general space vector PWM algorithm for multilevel inverters, including operation in overmodulation range," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 517–526, Mar. 2007.

- [8] A. K. Gupta and A. M. Khambadkone, "A general space vector PWM algorithm for a multilevel inverter including operation in overmodulation range, with a detailed modulation analysis for a 3-level NPC inverter," in *Proc. IEEE 36th Power Electron. Spec. Conf.*, Jun. 2005, pp. 2527–2533.

- [9] A. K. Gupta and A. M. Khambadkone, "A simple space vector PWM scheme to operate a three-level NPC inverter at high modulation index including overmodulation region, with neutral point balancing," *IEEE Trans. Ind. Appl.*, vol. 43, no. 3, pp. 751–760, May 2007.

- [10] N. Celanovic and D. Boroyevich, "A fast space-vector modulation algorithm for multilevel three-phase converters," *IEEE Trans. Ind. Appl.*, vol. 37, no. 2, pp. 637–641, Mar. 2001.

- [11] F. Bishuang, T. Guanzhenga, and F. Shaosheng, "Comparison of three different 2-D space vector PWM algorithms and their FPGA implementations," *J. Power Technol.*, vol. 94, no. 3, pp. 176–189, May 2014.

- [12] S. Wei, B. Wu, F. Li, and C. Liuand, "A general space vector PWM control algorithm for multilevel inverters," in *Proc. 18th Annu. IEEE Appl. Power Electron. Conf. Exposit.*, vol. 1, Feb. 2003, pp. 562–568.

- [13] L. Hu, H. Wang, V. Deng, and X. He, "A simple SVPWM algorithm for multilevel inverters," in *Proc. IEEE 35th Annu. Power Electron. Spec. Conf.*, vol. 5, Jun. 2004, pp. 3476–3480.

- [14] B. Jacob and M. R. Baiju, "A new space vector modulation scheme for multilevel inverters which directly vector quantize the reference space vector," *IEEE Trans. Ind. Electron.*, vol. 62, no. 1, pp. 88–95, Jan. 2015.

- [15] Z. Shu, N. Ding, J. Chen, H. Zhu, and X. He, "Multilevel SVPWM with DC-link capacitor voltage balancing control for diode-clamped multilevel converter based STATCOM," *IEEE Trans. Ind. Electron.*, vol. 60, no. 5, pp. 1884–1896, May 2013.

- [16] N. Celanovic and D. Boroyevich, "A comprehensive study of neutral-point voltage balancing problem in three-level neutral-point-clamped voltage source PWM inverters," *IEEE Trans. Power Electron.*, vol. 15, no. 2, pp. 242–249, Mar. 2000.

- [17] H. Zhang, S. J. Finney, A. Massoud, and B. W. Williams, "An SVM algorithm to balance the capacitor voltages of the three-level NPC active power filter," *IEEE Trans. Power Electron.*, vol. 23, no. 6, pp. 2694–2702, Nov. 2008.

- [18] G. I. Orfanoudakis, M. A. Yuratich, and S. M. Sharkh, "Nearest-vector modulation strategies with minimum amplitude of low-frequency neutralpoint voltage oscillations for the neutral-point-clamped converter," *IEEE Trans. Power Electron.*, vol. 28, no. 10, pp. 4485–4499, Oct. 2013.

- [19] C. Li, T. Yang, P. Kulsangcharoen, G. L. Calzo, S. Bozhko, C. Gerada, and P. Wheeler, "A modified neutral point balancing space vector modulation for three-level neutral point clamped converters in high-speed drives," *IEEE Trans. Ind. Electron.*, vol. 66, no. 2, pp. 910–921, Feb. 2019.

- [20] S. Busquets-Monge, J. Bordonau, D. Boroyevich, and S. Somavilla, "The nearest three virtual space vector PWM—A modulation for the comprehensive neutral-point balancing in the three-level NPC inverter," *IEEE Power Electron. Lett.*, vol. 2, no. 1, pp. 11–15, Mar. 2004.

- [21] J. Pou, P. Rodriguez, V. Sala, S. Busquets-Monge, and D. Boroyevich, "Algorithm for the virtual vectors modulation in three-level inverters with a voltage-balance control loop," in *Proc. Eur. Conf. Power Electron. Appl.*, Sep. 2005, pp. 1–9.

- [22] S. B. Monge, S. Somavilla, J. Bordonau, and D. Boroyevich, "Capacitor voltage balance for the neutral-point-clamped converter using the virtual space vector concept with optimized spectral performance," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1128–1135, Jul. 2007.

- [23] J. Pou, D. Boroyevich, and R. Pindado, "New feedforward space-vector pwm method to obtain balanced ac output voltages in a three-level neutralpoint-clamped converter," *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 1026–1034, Oct. 2002.

- [24] J. I. Leon, S. Vazquez, R. Portillo, L. G. Franquelo, J. M. Carrasco, P. W. Wheeler, and A. J. Watson, "Three-dimensional feedforward space vector modulation applied to multilevel diode-clamped converters," *IEEE Trans. Ind. Electron.*, vol. 56, no. 1, pp. 101–109, Jan. 2009.

- [25] P. Szczepankowski and J. Nieznanski, "Virtual space vector pulse width modulation algorithm for three-level NPC converters based on the final element shape functions," in *Proc. 39th Annu. Conf. IEEE Ind. Electron.* Soc., Nov. 2013, pp. 3824–3829.

- [26] M. S. Floater, K. Hormann, and G. Kós, "A general construction of barycentric coordinates over convex polygons," *Adv. Comput. Math.*, vol. 24, no. 1, pp. 311–331, 2006.

- [27] S. An, X. Sun, Q. Zhang, Y. Zhong, and B. Ren, "Study on the novel generalized discontinuous SVPWM strategies for three-phase voltage source inverters," *IEEE Trans. Ind. Inform.*, vol. 9, no. 2, pp. 781–789, May 2013.

- [28] U.-M. Choi, H.-H. Lee, and K.-B. Lee, "Simple neutral-point voltage control for three-level inverters using a discontinuous pulse width modulation," *IEEE Trans. Energy Convers.*, vol. 28, no. 2, pp. 434–443, Jun. 2013.

**PAWEŁ SZCZEPANKOWSKI** (M'18) received the Ph.D. degree in electrical engineering from the Gdańsk University of Technology, Poland, in 2009. He has authored or coauthored more than 30 scientific and technical papers. His research interests include design, control, diagnostics, modeling and simulation of power electronic converters, including multilevel and matrix topologies, and signal processing with the use of advanced DSP nad FPGA devices. He is a member of the

Research and Development team of the Electrotechnical Institute, Warsaw, and the  ${\rm LINTE}^2$  Laboratory.

JANUSZ NIEZNAŃSKI (A'93–SM'03) received the M.Sc., Ph.D., and D.Sc. (habilitation) degrees in electrical engineering from the Gdańsk University of Technology, Poland, in 1981, 1990, and 1999, respectively. Since 1982, he has been with the Gdańsk University of Technology, where he is currently a Full Professor and the Dean of the Faculty of Electrical and Control Engineering. He was a Visiting Professor with the French higher education institutions, namely the Institut

National Polytechnique de Toulouse, in 2001, and the Ecole Centrale de Lille, in 2005 and 2006, respectively, and as a Visiting Researcher at the R&D Center of Alstom Transport SA, Semeac, France, in 2006 and 2007, respectively. He has authored or coauthored more than 120 scientific and technical papers and was the Project Leader in many national and international Research and Development projects. His research and teaching interests include control, diagnostics, modeling, and simulation of power electronic converters and electrical drives, digital signal processing for power electronic applications, digital frequency synthesis, and vibroacoustics of inverter-fed AC machines.

• • •