Received March 22, 2019, accepted April 9, 2019, date of publication April 23, 2019, date of current version May 3, 2019. *Digital Object Identifier* 10.1109/ACCESS.2019.2912858

# Analysis and Design of a Controller for an Input-Saturated DC–DC Buck Power Converter

## OCTAVIO GARCÍA-ALARCÓN<sup>®</sup> AND JAVIER MORENO-VALENZUELA<sup>®</sup>, (Member, IEEE)

Instituto Politécnico Nacional-CITEDI, Tijuana 22435, México

Corresponding author: Javier Moreno-Valenzuela (moreno@citedi.mx)

This work was supported in part by the CONACyT Project A1-S-24762 and in part by the Secretaría de Investigación y Posgrado del IPN, México.

**ABSTRACT** In this paper, a novel controller for an input-saturated direct current to direct current (DC–DC) buck power converter has been proposed. The control scheme guarantees global asymptotic stability, even though the input to the power converter is affected by a hard saturation nonlinearity that results from the fact that in practice the duty cycle can only take continuous values between zero and one. Specifically, asymptotic stability is ensured by using a special quadratic-type Lyapunov function and LaSalle's invariance principle. In addition, to prevent inductor current's noisy measurements, an observer is proposed together with the proposed control law. Stability is also discussed rigorously for the resulting observer-based scheme. The real-time experimental comparisons with respect to a known approach are presented. Better performance is obtained with the novel observer-based controller.

**INDEX TERMS** Buck power converter, input saturation, Lyapunov's stability, observer-based controller, real-time experiments.

## I. INTRODUCTION

Most applications that require regulation of direct current to direct current (DC-DC) use a switched power converter [1]. This is why there is an increasing demand for a market with more efficient power converters. Power converters are susceptible to present non-linear phenomena, which are usually undesirable and should be avoided as they are detrimental to the normal operation of converters and result in instability [2]. Therefore, refining the existing analysis techniques can lead to performance improvements in power converters [3].

Duty cycle percentage is the control input of the power converter, which ideally accepts continuous values between zero and one. Commonly, the control action can be out of the physically admissible limits in that the PWM signal is produced. This is usually not considered for the design and closed-loop system analyses of the control system [4]. Saturation input is one of the most common non-linearities in physical systems and is rarely considered in the analysis and design of controllers for power converters because the complexity of the stability analysis of the closed loop system [5]

The associate editor coordinating the review of this manuscript and approving it for publication was Ludovico Minati.

increases. In addition to the saturation problem, the noise in inductor current measurements and the imprecise knowledge of the supply voltage further complicate the problem of output voltage regulation.

A buck converter produces an output voltage lower than its input power voltage and finds its use in a wide range of applications, such as regulated voltage sources, battery-powered handheld devices, battery chargers for electric vehicles [6], photovoltaic systems [7], LED illumination [1], drivers for DC motors and, more recently, DC microgrids [8] and renewable sources [9], to name a few. Textbooks introducing theoretical concepts on the history and technical development of power converters are [1], [4], [10], [11].

In order to achieve output voltage control and compensate for an unknown number of perturbations in the power converter parameters (measurable or non-measurable), many control algorithms have been designed; however, only a few have considered the input restriction introduced by the PWM duty cycle percentage. First, the literature review on the control of unrestricted DC-DC power converters is presented. Lyapunov theory was used in [12] to design a controller for a DC-DC boost power converter. In [13], a constructive control approach was employed to study the current-mode control problem in a boost converter, yielding a cascade control design methodology. The work in [14] presented the control design for a buck converter driven DC motor. Using Lyapunov's direct method, an observer-based sensorless control for boost power converters was presented in [15]. In [16], a nonlinear current-mode controller was presented for DC-DC boost power converters. In the works [17] and [18], the terminal sliding mode control was applied with the aim of compensating for the parasite effects in the buck power converter. In [19], a finite-time controller converter was introduced, where an adaptive integral terminal sliding mode control scheme was developed by combining fuzzy inference and an adaptive mechanism. In [20], a constant current-mode method for boost DC-DC converters with synchronous rectifiers was presented. In [21], a sliding mode controller was developed to deal with the chattering problem and regulate the output voltage of a boost converter. More recently, [22] presented a second-order sliding mode controller for a buck converter while [23] introduced a time-delay feedback controller to stabilize the buck converter output voltage. In the work [24], a technique for the control of a DC-DC buck power converter with a switching technique that guarantees both good performance and global stability was introduced. In [25], by assuming a more complex model for the buck power converter, a controller that fully eliminates spurs from the switching noise spectrum was presented. In the work of [26], a new direct sliding mode voltage controller based on parabolic modulation was proposed and applied to a buck converter.

A review of the literature on the control of restricted DC-DC power converters is presented below. An example where the saturation of the duty cycle is considered in the control of power converters can be found in [27], where simulations were presented. In [28], an  $H_{\infty}$  controller of a DC-DC converter with saturated input was introduced. A stability analysis of a two-cell DC-DC converter in the presence of a saturating duty cycle was introduced in [29]. In [30], the control of a boost power converter by using only measurements of the output voltage and estimating the supply voltage was addressed. By using the theory of stability for cascade systems, the controller-observer given by [30] was revisited in [31] and [32]. In [33], an adaptive neural network controller was presented. However, its scheme was based on the inversion of the saturation function, which can only be achieved locally. Simulations of a nonlinear controller with current limiting capability were presented in [34], where the proposed control strategy offers an inherent protection property as the power of the converter is limited. The work in [35] focused on the output voltage control of a buck power converter in the presence of an input limitation. Sufficient conditions for  $L_2$  stability were given. More recently, in [36] and [37], regional pole placement with saturated control for a DC-DC buck converter was presented.

The goal of this work is to present the analysis and design of a linear controller for improving the performance of an input-saturated buck power converter. Specifically, the contributions of this paper are as follows:

- The introduction of a controller for a DC-DC buck power converter with a constrained input.

- The introduction of an observer for the estimation of the inductor current and its application in the proposed control structure, giving a novel observer-based controller.

- The presentation of an extensive real-time experimental evaluation, which includes the comparison with respect to the scheme given in [35].

None of the proposed controllers require the exact value of the input voltage; instead, a simple positive estimate is used. Thus, the given controllers are robust to the input saturation, to variations of the input voltage, and under the incorporation of an observer to current measurements.

This document is organized as follows: Section II deals with the modeling of the DC-DC buck power converter and the control goal. Section III presents a novel controller for the DC-DC buck power converter subject to saturated input. Besides, the asymptotic convergence of the output voltage error is proven even though the power converter is affected by the input saturation. Section IV introduces an observer to estimate the inductor current, which is then combined with the control structure expressed in Section 3. As result, a novel observer-based scheme is given. Section V shows a real-time experimental study that validates the advantages of the proposed scheme, giving better results than a known controller reported in the literature. Finally, the conclusions are presented in Section VI.

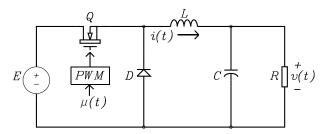

FIGURE 1. Schematic diagram of the buck circuit.

## II. BUCK DC-DC POWER CONVERTER MODEL AND CONTROL GOAL

The structure of the DC-DC buck power converter is shown in Figure 1, where *E* represents the input voltage, i(t) the current through the inductor *L*, and v(t) is the output voltage loaded at a certain time in capacitor *C*, which is consumed by the load resistance *R*. The scalar quantity  $\mu(t)$  corresponds to the duty cycle of a PWM signal introduced in the gate terminal of the transistor *Q*. Specifically, for the system shown in Figure 1, the average model is given by [10], [11], and [38],

$$L\frac{d}{dt}i = -v + \mu E,\tag{1}$$

$$C\frac{d}{dt}v = i - \frac{v}{R}.$$

(2)

where  $\mu(t)$  is the control input. The model (1)–(2) is obtained under the assumption that the buck power converter is operating in a continuous conduction mode.

At this point, the average model in (1)-(2) is linear and ideal but, in practice, a different phenomena may occur. Usually, physical plants are subjected to constrained variables, the most common of which are those of the saturation type. Ignoring these constraints can be detrimental to the stability and performance of the control system [37]. Hereafter, the following consideration is made:

$$\mu = sat(u), \tag{3}$$

where

2

$$sat(u) = \begin{cases} u_{max}, & \text{for } u > u_{max}, \\ u, & \text{for } u_{min} \le u \le u_{max}, \\ u_{min}, & \text{for } u < u_{min}, \end{cases}$$

(4)

with saturation limits  $u_{min}$  and  $u_{max}$  such that

$$0 \le u_{min} < \frac{v_d}{E} < u_{max} \le 1, \tag{5}$$

where  $v_d > 0$  is a constant that denotes the desired output voltage. The control problem is based on design u(t) so that

$$\lim_{t \to \infty} v(t) = v_d$$

is satisfied. The goal of this work is to achieve stability of the system given the constrained input of the DC-DC buck power converter.

#### **III. PROPOSED CONTROLLER**

In this section, a new control law is introduced in order to stabilize the DC-DC buck power converter in equations (1)-(3). The proposed controller is given by

$$u = \frac{v_d}{E^\star} - k_i e_i - k_v e_v + k_o \phi, \qquad (6)$$

$$\frac{d}{dt}\phi = -k_{f1}e_i - k_{f2}e_\nu,\tag{7}$$

where  $k_i, k_v, k_o, k_{f1}, k_{f2} > 0$  are constants,  $E^* > 0$  is a constant estimate of the supply voltage *E*, and the signals

$$e_i = i - i_d, \tag{8}$$

$$e_v = v - v_d, \tag{9}$$

define the current and voltage errors, respectively. In particular,  $v_d$  denotes the desired output voltage and  $i_d = \frac{v_d}{R}$  defines the desired current through the inductance. Noteworthy is that  $v_d$  and  $i_d$  denoting the desired states of the buck power converter actually coincide with the open-loop equilibrium of (1)–(2) for  $\mu = \frac{v_d}{E}$ . By using the relationship

$$\mu = u + \delta(u), \tag{10}$$

with

$$\delta(u) = sat(u) - u, \tag{11}$$

substituting the control law (6)-(7) into the buck power converter equations (1)-(2), and using equations (8)-(9), the closed-loop system can be written as

$$L\frac{d}{dt}e_{i} = -(1 + Ek_{v})e_{v} - Ek_{i}e_{i} + Ek_{o}\phi$$

$$+ E\delta(u) + E\left(\frac{v_{d}}{E^{\star}} - \frac{v_{d}}{E}\right), \qquad (12)$$

$$C\frac{d}{dt}e_{\nu} = e_i - \frac{e_{\nu}}{R},\tag{13}$$

$$\frac{d}{dt}\phi = -k_{f1}e_i - k_{f2}e_v. \tag{14}$$

Given that  $\delta(\frac{v_d}{E}) = 0$  (assumption (5)), the state-space origin  $[e_i \ e_v \ \phi]^T = [0 \ 0 \ \phi^*]^T$ , with

$$\phi^{\star} = \frac{1}{k_o} \left( \frac{v_d}{E} - \frac{v_d}{E^{\star}} \right), \tag{15}$$

is an equilibrium point. The system (12)-(14) can also be rewritten as

$$\frac{d}{dt} \begin{bmatrix} e_i \\ e_v \\ \phi \end{bmatrix} = \begin{bmatrix} -\frac{Ek_i}{L} & -\left(\frac{1}{L} + \frac{Ek_v}{L}\right) & \frac{Ek_o}{L} \\ \frac{1}{C} & -\frac{1}{RC} & 0 \\ -k_{f1} & -k_{f2} & 0 \end{bmatrix} \begin{bmatrix} e_i \\ e_v \\ \phi \end{bmatrix} + \begin{bmatrix} \frac{E}{L}\delta(u) + E\left(\frac{v_d}{E^{\star}} - \frac{v_d}{E}\right) \\ 0 \end{bmatrix}.$$

(16)

By using the change of variable

$$\bar{\phi} = \phi - \phi^{\star},\tag{17}$$

with  $\phi^{\star}$  defined in (15), the state-space equation (16) is rewritten as

$$\frac{d}{dt} \begin{bmatrix} e_i \\ e_v \\ \bar{\phi} \end{bmatrix} = \begin{bmatrix} -\frac{Ek_i}{L} & -\left(\frac{1}{L} + \frac{Ek_v}{L}\right) & \frac{Ek_o}{L} \\ \frac{1}{C} & -\frac{1}{RC} & 0 \\ -k_{f1} & -k_{f2} & 0 \end{bmatrix} \begin{bmatrix} e_i \\ e_v \\ \bar{\phi} \end{bmatrix} + \begin{bmatrix} \frac{E}{L} \delta(u) \\ 0 \\ 0 \end{bmatrix}. \quad (18)$$

The next step is to propose a Lyapunov function candidate as follows:

$$W(e_i, e_{\nu}, \bar{\phi}) = \alpha \left[ \frac{L}{2} e_i^2 + \frac{C}{2} e_{\nu}^2 \right] + \frac{\beta}{2} \left[ \left( u - \frac{v_d}{E} \right)^2 - \delta(u)^2 \right],$$

(19)

with constants  $\alpha$ ,  $\beta > 0$ . After some algebra, it is possible to show that

$$k_o E \bar{\phi} e_i + E \delta(u) e_i = E \left[ sat(u) - \frac{v_d}{E} \right] e_i + k_i E e_i^2 + k_v E e_i e_v,$$

(20)

which is obtained by the direct substitution of  $\delta(u)$  in (11), *u* in (6), and the change of variable  $\overline{\phi}$  in (17). Besides, it is possible to prove that

**IEEE**Access

-

$$\frac{d}{dt}u = -\frac{k_i}{L}E\left[sat(u) - \frac{v_d}{E}\right] - \left[\frac{k_v}{C} + k_ok_{f1}\right]e_i + \left[\frac{k_i}{L} + \frac{k_v}{RC} - k_ok_{f2}\right]e_v.$$

(21)

By using (20)-(21), the time derivative of  $W(e_i, e_v, \bar{\phi})$  along the closed-loop system (18) can be expressed as

$$\begin{split} \dot{W}(e_i, \ e_v, \ \bar{\phi}) \\ &= \alpha E \left[ sat(u) - \frac{v_d}{E} \right] e_i - \alpha \frac{e_v^2}{R} \\ &+ \beta \left[ sat(u) - \frac{v_d}{E} \right] \left[ -\frac{k_i E}{L} \left( sat(u) - \frac{v_d}{E} \right) \\ &- \left( \frac{k_i}{L} + \frac{k_v}{L} - k_o k_{f2} \right) e_v - \left( \frac{k_v}{C} + k_o k_{f1} \right) e_i \right]. \end{split}$$

(22)

By defining the parameter  $\alpha$  involved in the Lyapunov function candidate as

$$\alpha = \frac{\beta}{E} \left( \frac{k_v}{C} + k_o k_{f1} \right), \tag{23}$$

the expression of  $\dot{W}(e_i, e_v, \bar{\phi})$  in (22) can be rewritten as

$$\dot{W}(e_i, e_v, \bar{\phi}) = -\alpha \frac{e_v^2}{R} - \beta \frac{k_i}{L} E \left( sat(u) - \frac{v_d}{E} \right)^2 + \beta \left( \frac{k_i}{L} + \frac{k_v}{RC} - k_o k_{f2} \right) \left( sat(u) - \frac{v_d}{E} \right) e_v.$$

(24)

Finally, by using the definition of  $\alpha$  in (23), the equation (24) is written in the form of a vector-matrix-vector product as follows:

$$\dot{W}(e_i, e_v, \bar{\phi}) = -\beta \left[ \frac{e_v}{sat(u) - \frac{v_d}{E}} \right]^I Q \left[ \frac{e_v}{sat(u) - \frac{v_d}{E}} \right],$$

(25)

where

$$Q = \begin{bmatrix} \frac{1}{R} \frac{1}{E} \left( \frac{k_{\nu}}{C} + k_{o} k_{f1} \right) & -\frac{1}{2} \left( \frac{k_{i}}{L} + \frac{k_{\nu}}{RC} - k_{o} k_{f2} \right) \\ -\frac{1}{2} \left( \frac{k_{i}}{L} + \frac{k_{\nu}}{RC} - k_{o} k_{f2} \right) & \frac{k_{i}E}{L} \end{bmatrix}.$$

(26)

In agreement with Sylverster's criterion, the matrix Q in 26 is positive definite provided that

$$\frac{1}{R} \left( \frac{k_{\nu}}{C} + k_o k_{f1} \right) \frac{k_i}{L} - \left( \frac{k_i}{L} + \frac{k_{\nu}}{RC} - k_o k_{f2} \right)^2 > 0, \quad (27)$$

which can always be satisfied with  $k_{f1} > 0$  sufficiently large. Thus, there are sufficient conditions for  $\dot{W}(e_i e_v \bar{\phi})$  in (25) to be negative semidefinite, implying the state-space origin  $[e_i e_v \bar{\phi}]^T = [0 \ 0 \ 0]^T$  is globally stable in Lyapunov's sense. In addition, direct application of LaSalle's invariance principle ensures that the state-space origin is globally asymptotically stable [39]-[41].

## **IV. NEW PROPOSED CONTROLLER WITH INDUCTOR CURRENT ESTIMATION**

#### A. PROPOSED OBSERVER

The controller proposed in the previous Section considers the measurement of the inductor current i(t), the voltage output v(t), and the constant estimate of the input voltage  $E^*$ . An observer for the inductor current i(t) is proposed to reduce the noise in the signal u(t) that is usually introduced by the current sensor. Keeping this in mind, we consider the observation errors given by

$$\tilde{i} = \hat{i} - i, \tag{28}$$

$$\tilde{v} = \hat{v} - v, \tag{29}$$

where  $\hat{i}$  and  $\hat{v}$  are the current and voltage estimations, respectively. The observation error dynamics is obtained by using the buck power converter equations in (1)–(3)

$$L\frac{d}{dt}\tilde{i} = L\frac{d}{dt}\hat{i} + v - Esat(u), \tag{30}$$

$$C\frac{d}{dt}\tilde{v} = C\frac{d}{dt}\hat{v} - i + \frac{v}{R},$$

(31)

which allow proposing the observer given by

$$L\frac{d}{dt}\hat{i} = -v + E^{\star}sat(u) - k_{v1}\tilde{v} - k_{i1}\zeta, \qquad (32)$$

$$C\frac{d}{dt}\hat{v} = \frac{v}{R} + \hat{i} - k_{v2}\tilde{v},\tag{33}$$

$$\frac{d}{dt}\zeta = \tilde{v},\tag{34}$$

where  $E^{\star} > 0$  is a constant estimate of the supply voltage E,  $k_{v1}$ ,  $k_{v2}$ , and  $k_{i1}$  strictly positive observer gains that need to be defined. By substituting the equations (32)-(34) in equations (30)–(31), the observation error becomes

$$L\frac{d}{dt}\tilde{i} = -k_{\nu 1}\tilde{\nu} - k_{i1}\zeta + (E^{\star} - E)sat(u), \qquad (35)$$

$$C\frac{d}{dt}\tilde{v} = \tilde{i} - k_{v2}\tilde{v},\tag{36}$$

$$\frac{d}{dt}\zeta = \tilde{v},\tag{37}$$

which can be written in the form

$$\frac{d}{dt}\begin{bmatrix}\tilde{i}\\\tilde{v}\\\tilde{\zeta}\end{bmatrix} = \begin{bmatrix}0 & -\frac{k_{v1}}{L} & -\frac{k_{i1}}{L}\\\frac{1}{C} & -\frac{k_{v2}}{C} & 0\\0 & 1 & 0\end{bmatrix}\begin{bmatrix}\tilde{i}\\\tilde{v}\\\tilde{\zeta}\end{bmatrix} + \begin{bmatrix}\left(\frac{E^{\star}-E}{L}\right)\left(sat(u)-\frac{v_d}{E}\right)\\0\end{bmatrix}, \quad (38)$$

where

$$\bar{\zeta} = \zeta - \frac{1}{k_{i1}} \frac{v_d}{E} (E^* - E).$$

(39)

Neglecting the second term of (38), the characteristic polynomial of the resulting system is given by

$$\lambda^3 + \frac{k_{\nu 2}}{C}\lambda^2 + \frac{k_{\nu 1}}{LC}\lambda + \frac{k_{i1}}{LC}.$$

(40)

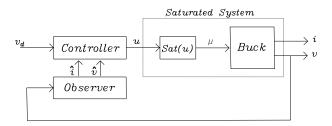

**FIGURE 2.** Block diagram implementation of the proposed controller plus observer scheme.

In agreement to the Routh-Hurwitz criterion [42], the characteristic polynomial (40) has roots with a negative real part if

$$k_{\nu 1} > 0, \quad k_{\nu 2} > 0, \quad \frac{k_{\nu 1}k_{\nu 2}}{C} > k_{i1}.$$

(41)

In other words, if  $k_{v1}$ ,  $k_{v2}$ , and  $k_{i1}$  are selected to satisfy the conditions in (41) and the fact that the second term of (38) is bounded for all time  $t \ge 0$ , then the solutions  $[\tilde{i}(t), \tilde{v}(t), \bar{\zeta}(t)]^T \in \mathbb{R}^3$  of the observation error dynamics (38) are uniformly ultimately bounded. Furthermore, if *u* is constant, the solutions  $[\tilde{i}(t), \tilde{v}(t), \bar{\zeta}(t)]^T$  converge exponentially to  $[0, 0, \frac{[E^*-E][sat(u)-\frac{v_d}{E}]}{k_{i1}}]^T$  as time *t* increases.

## **B. PROPOSED OBSERVER-BASED SCHEME**

The result of using the estimated signals  $\hat{i}(t)$  and  $\hat{v}(t)$  into the proposed controller (6)–(7) is given by

$$u = \frac{v_d}{E^\star} - k_i \tilde{e}_i - k_v \tilde{e}_v + k_o \phi, \qquad (42)$$

$$\frac{d}{dt}\phi = -k_{f1}\tilde{e}_i - k_{f2}\tilde{e}_v, \tag{43}$$

where, as mentioned earlier,  $E^* > 0$  is a constant estimate of the supply voltage *E*, and

$$\tilde{e}_i = \hat{i} - i_d, \tag{44}$$

$$\tilde{e}_v = \hat{v} - v_d. \tag{45}$$

The block diagram of the implementation of the observerbased controller defined by equations (32)–(34) and (42)–(43) is shown in Figure 2. By using the definitions of  $e_i$ and  $e_v$  in equations (8) and (9), respectively, the expressions of  $\tilde{i}$  and  $\tilde{v}$  in (28) and (29), respectively, and the change of variable  $\bar{\phi}$  in (17), the observer-based controller in equations (42)–(43) can be rearranged as

$$u = \frac{v_d}{E} - k_i e_i - k_v e_v + k_o \bar{\phi} - k_i \tilde{i} - k_v \tilde{v} \qquad (46)$$

$$\frac{d}{dt}\bar{\phi} = -k_{f1}e_i - k_{f2}e_v - k_{f1}\tilde{i} - k_{f2}\tilde{v},$$

(47)

By using the procedure used to obtain the state-space equations in (18) and the equations of the observation error dynamics in (35)–(37), the closed-loop system obtained from using the controller (42)–(43) in the DC-DC buck power converter (1)–(2) can be given by

$$\frac{d}{dt} \begin{bmatrix} e_i \\ e_v \\ \bar{\phi} \end{bmatrix} = \begin{bmatrix} -\frac{Ek_i}{L} & -\left(\frac{1}{L} + \frac{Ek_v}{L}\right) & \frac{Ek_o}{L} \\ \frac{1}{C} & -\frac{1}{RC} & 0 \\ -k_{f1} & -k_{f2} & 0 \end{bmatrix} \begin{bmatrix} e_i \\ e_v \\ \bar{\phi} \end{bmatrix} \\

+ \begin{bmatrix} \frac{E}{L}\delta(u) \\ 0 \\ 0 \end{bmatrix} + \begin{bmatrix} -\frac{Ek_i}{L} - \frac{Ek_v}{L} & 0 \\ 0 & 0 & 0 \\ -k_{f1} & -k_{f2} & 0 \end{bmatrix} \begin{bmatrix} \tilde{i} \\ \tilde{v} \\ \bar{\zeta} \end{bmatrix},$$

$$\frac{d}{dt} \begin{bmatrix} \tilde{i} \\ \tilde{v} \\ \bar{\zeta} \end{bmatrix} = \begin{bmatrix} 0 & -\frac{k_{v1}}{L} & -\frac{k_{i1}}{L} \\ \frac{1}{C} & -\frac{k_{v2}}{C} & 0 \\ 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} \tilde{i} \\ \tilde{v} \\ \bar{\zeta} \end{bmatrix} \\

+ \begin{bmatrix} \begin{bmatrix} \frac{E^*-E}{L} \\ 0 \\ 0 \end{bmatrix} \begin{bmatrix} sat(u) - \frac{v_d}{E} \end{bmatrix} \\$$

$$(49)$$

where the dynamics of the observer (38) has been rewritten for better appreciation.

The properties

and

$$sat\left(\frac{v_d}{E}\right) - \frac{v_d}{E} = 0$$

$\delta\left(\frac{v_d}{F}\right) = 0$

ensure that the state-space origin

$$[e_i \, e_v \, \bar{\phi} \, \tilde{i} \, \tilde{v} \, \bar{\zeta}]^T = [0 \, 0 \, 0 \, 0 \, 0 \, 0 \, 0]^T \in \mathbb{R}^6,$$

is an equilibrium point of the system (48)-(49). In order to facilitate this analysis, the matrix

$$A_{o} = \begin{bmatrix} 0 & -\frac{k_{\nu 1}}{L} & -\frac{k_{i1}}{L} \\ \frac{1}{C} & -\frac{k_{\nu 2}}{C} & 0 \\ 0 & 1 & 0 \end{bmatrix} \in \mathbb{R}^{3 \times 3}$$

and the vector

$$z = \begin{bmatrix} \tilde{i} \\ \tilde{v} \\ \bar{\zeta} \end{bmatrix} \in \mathbb{R}^3$$

are defined. Let us assume that  $A_o$  is Hurwitz, which can always be achieved by using the conditions in (41). Thus, there exist  $P_0$  and  $Q_o$  as  $3 \times 3$  symmetric positive definite matrices such that Lyapunov equation

$$\frac{1}{2}[P_oA_o + A_o^T P_o] = -Q_o$$

is satisfied.

The following Lyapunov function candidate is proposed:

$$W_o(e_i, e_v, \bar{\phi}, \tilde{i}, \tilde{v}, \bar{\zeta}) = \epsilon_1 W(e_i, e_v, \bar{\phi}) + \frac{\epsilon_2}{2} z^T P_o z, \qquad (50)$$

where  $\epsilon_1$  and  $\epsilon_2$  are strictly positive constants, and  $W(e_i, e_v, \bar{\phi})$  has been defined in (19). Now, consider the property

**IEEE**Access

$$Ek_{o}\bar{\phi}e_{i} + E\delta(u)e_{i} - Ek_{i}\tilde{i}e_{i} - Ek_{v}\tilde{v}e_{i}$$

$$= E[sat(u) - \frac{v_{d}}{E}]e_{i} + k_{i}Ee_{i}^{2} + k_{v}Ee_{i}e_{v}, \quad (51)$$

which can be proven by using the definition of  $\delta(u)$  in (11) and the signal *u* in the expression (46). In addition, we note

$$\dot{u} = -\frac{k_i}{L} E^* \left[ sat(u) - \frac{v_d}{E} \right] - \left[ \frac{k_v}{C} + k_o k_{f1} \right] e_i + \left[ \frac{k_i}{L} + \frac{k_v}{RC} - k_o k_{f2} \right] e_v - \left[ k_o k_{f1} + \frac{k_v}{C} \right] \tilde{i} - \left[ k_o k_{f2} - k_i \frac{k_{v1}}{L} - k_v \frac{k_{v2}}{C} \right] \tilde{v} + k_i \frac{k_{i1}}{L} \tilde{\zeta},$$

(52)

which can be computed using the control input (46)-(47) and the closed-loop system (48)-(49).

By employing the properties of (51) and (52), the definition (23), which relates the positive constants  $\alpha$  and  $\beta$  related to  $W(e_i, e_v, \bar{\phi})$  in (19), and after some algebra, the time derivative of  $W_o(e_i, e_v, \bar{\phi}, \tilde{i}, \tilde{v}, \bar{\zeta})$  in (50) along the closed-loop system trajectories (48)-(49) can be written as

$$\begin{split} \dot{W}_{o}(e_{i}, e_{v}, \bar{\phi}, \tilde{i}, \tilde{v}, \bar{\zeta}) \\ &= -\epsilon_{1}\beta \begin{bmatrix} e_{v} \\ sat(u) - \frac{v_{d}}{E} \end{bmatrix} Q_{e} \begin{bmatrix} e_{v} \\ sat(u) - \frac{v_{d}}{E} \end{bmatrix} \\ &+ \epsilon_{1}\beta [sat(u) - \frac{v_{d}}{E}] c^{T} z \\ &- \epsilon_{2} z^{T} Q_{o} z + \epsilon_{2} z^{T} P_{o} \begin{bmatrix} \frac{E^{*} - E}{L} [sat(u) - \frac{v_{d}}{E}] \\ 0 \end{bmatrix}, \end{split}$$

(53)

where  $\beta > 0$  is a free constant related to the function  $W(e_i, e_v, \bar{\phi})$  in (19),

$$= \begin{bmatrix} \frac{1}{R} \frac{1}{E} \left[ \frac{k_v}{C} + k_o k_{f1} \right] & -\frac{1}{2} \left[ \frac{k_i}{L} + \frac{k_v}{RC} - k_o k_{f2} \right] \\ -\frac{1}{2} \left[ \frac{k_i}{L} + \frac{k_v}{RC} - k_o k_{f2} \right] & \frac{k_i}{L} E^* \end{bmatrix},$$

and

$\sim$

$$\boldsymbol{c} = \begin{bmatrix} c_1 \\ c_2 \\ c_3 \end{bmatrix},$$

$$c_1 = -\left[k_o k_{f1} + \frac{k_v}{C}\right],$$

$$c_2 = -\left[k_o k_{f2} - k_i \frac{k_{v1}}{L} - k_v \frac{k_{v2}}{C}\right],$$

$$c_3 = k_i \frac{k_{i1}}{L}.$$

Note that the difference between the matrix  $Q_e$  and the matrix Q in (26) is in the second diagonal element of  $Q_e$ , where the estimated supply voltage  $E^*$  is seen. In a similar form to the

analysis shown in Section III, the condition for  $Q_e$  to be a positive definite is given by

$$\frac{1}{RE} \left[ \frac{k_{\nu}}{C} + k_o k_{f1} \right] \frac{k_i}{L} E^* - \frac{1}{4} \left[ \frac{k_i}{L} + \frac{k_{\nu}}{RC} - k_o k_{f2} \right]^2 > 0,$$

(54)

which can always be satisfied with  $k_{f1} > 0$  and  $E^* > 0$  as sufficiently large. Interestingly, the parameter  $E^*$  helps in the stabilization of the overall closed-loop system (48)–(49) because the observer (32)–(34) acts as an anti-windup extension [43].

By defining

$$\boldsymbol{e} = \begin{bmatrix} e_v \\ sat(u) - \frac{v_d}{E} \end{bmatrix},$$

an upper bound on the function  $\dot{W}_0$  in (53) can be computed as follows:

$$\begin{split} \dot{W}_{o}(e_{i}, e_{v}, \bar{\phi}, \tilde{i}, \tilde{v}, \bar{\zeta}) \\ &\leq -\epsilon_{1}\beta\lambda_{min}\{Q_{e}\}\|\boldsymbol{e}\|^{2} \\ &+ \epsilon_{1}\beta\|\boldsymbol{c}\|\|\boldsymbol{e}\|\|\boldsymbol{z}\| - \epsilon_{2}\lambda_{min}\{Q_{o}\}\|\boldsymbol{z}\|^{2} \\ &+ \epsilon_{2}\frac{|\boldsymbol{E}^{*} - \boldsymbol{E}|}{L}\lambda_{max}\{P_{o}\}\|\boldsymbol{z}\|\|\boldsymbol{e}\|, \end{split}$$

(55)

where the notation  $\lambda_{min}\{A\}$  and  $\lambda_{max}\{A\}$  denote the minimum and maximum eigenvalues of a symmetric matrix  $A \in \mathbb{R}^{3\times 3}$ , respectively, and  $||\mathbf{x}||$  stands for the Euclidean norm of a vector  $\mathbf{x} \in \mathbb{R}^3$ . The upper bound (55) can be rearranged so that

$$\dot{W}_o(e_i, e_v, \bar{\phi}, \tilde{i}, \tilde{v}, \bar{\zeta}) \leq -\frac{1}{2} \begin{bmatrix} \|\boldsymbol{e}\| \\ \|\boldsymbol{z}\| \end{bmatrix}^T [DS + S^T D] \begin{bmatrix} \|\boldsymbol{e}\| \\ \|\boldsymbol{z}\| \end{bmatrix},$$

where

$$D = \begin{bmatrix} \epsilon_1 & 0 \\ 0 & \epsilon_2 \end{bmatrix}$$

and

$$S = \begin{bmatrix} \beta \lambda_{min} \{Q_e\} & -\beta \| \boldsymbol{c} \| \\ -\frac{|E^* - E|}{L} \lambda_{max} \{P_o\} & \lambda_{min} \{Q_o\} \end{bmatrix}.$$

In agreement with Lemma 9.7 in [41], the matrix  $DS + S^T D$  is a positive definite if and only if S is an *M*-matrix, that is, the leading principal minors of S are positive,

$$\beta \lambda_{min} \{Q_e\} > 0$$

which can always be satisfied since  $Q_e$  is a symmetric positive definite matrix under (54), and

$$\beta \lambda_{\min}\{Q_e\} \lambda_{\min}\{Q_o\} - \beta \|\boldsymbol{c}\| \frac{|E^* - E|}{L} \lambda_{\max}\{P_o\} > 0,$$

which can be always satisfied with an adequate selection of the control and observer gains. Therefore, there are conditions for the function  $\dot{W}_o(e_i, e_v, \bar{\phi}, \tilde{i}, \tilde{v}, \bar{\zeta})$  to be globally negative semidefinite. It follows the invoking of LaSalle's invariance principle to prove that the state-space origin of the closed-loop system (48)–(49) is globally asymptotically stable [39], [40], and [41].

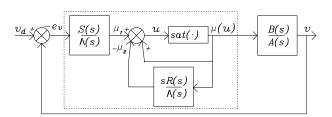

FIGURE 3. Closed-loop system with saturation function reported in [35].

#### **V. EXPERIMENTAL RESULTS**

In this section, we first describe the mathematical characterization of a controller reported in the literature, which is used to asses the performance of the proposed observerbased controller (42)–(43). Then, the experimental results are presented.

#### A. SATURATED CONTROLLER FOR COMPARISON

A controller deserving much attention is the one reported by El Fadil *et al.* [35], which can conduct an output voltage regulation under the assumption that the system is affected by the input saturation  $\mu(t)$  in (3).

The buck equation systems in (1)–(2) are redefined by the input–output representation

$$A(s)v = B(s)u, \tag{56}$$

where

$$A(s) = s^{2} + \frac{1}{RC}s + \frac{1}{LC}, \quad B(s) = \frac{E}{LC},$$

with *s* the Laplace operator, which also denotes the differentiation operator  $s = \frac{d}{dt}$ . The controller reported in [35] is the following:

$$u = \left(1 - \frac{sR(s)}{\Lambda(s)}\right)\mu(u) - \frac{S(s)}{\Lambda(s)}e_{\nu},$$

(57)

where  $\mu$  is the saturation of *u* in equation (3). The closedloop system obtained with the nonlinear controller (57) and the system equations in (1)–(3) is described in Figure 3.  $\Lambda(s)$ , R(s), S(s), and C(s) are differential operators and are defined by

$$\Lambda(s) = s^2 + \lambda_1 s + \lambda_0, \quad R(s) = s + \alpha_0,$$

$$S(s) = \beta_2 s^2 + \beta_1 s + \beta_0,$$

where  $e_v$  is the output voltage error (9). The coefficients  $\alpha_0$ ,  $\beta_0$ ,  $\beta_1$ , and  $\beta_2$  are defined by

$$\begin{aligned} \alpha_0 &= \lambda_1 + c_1 - \frac{1}{RC}, \\ \beta_0 &= \frac{LC}{E} \lambda_0 c_0, \\ \beta_1 &= \frac{LC}{E} \left[ \lambda_0 c_1 + \lambda_1 c_0 - \frac{1}{LC} (\lambda_1 + c_1 - \frac{1}{RC}) \right], \\ \beta_2 &= \frac{LC}{E} \left[ \lambda_0 + c_0 + \lambda_1 c_1 - \frac{1}{LC} - \frac{1}{RC} (\lambda_1 + c_1 - \frac{1}{RC}) \right], \end{aligned}$$

with

and

$$c_1 = 2\gamma + \frac{1}{RC}.$$

$c_0 = \gamma^2 + \frac{1}{RC}\gamma + \frac{1}{IC},$

Finally,  $u = \mu_1 - \mu_2 + \mu(u)$ , which in fact contains an algebraic loop; whereby, in practice, the signal *u* should be delayed by a small time in order to avoid it. As reported in [35], the inequality

$$\frac{1}{RC}c_1 - \frac{1}{LC} - c_0 + 2\sqrt{\frac{1}{LC}c_0} > 0,$$

with  $c_0 > 0$ ,  $c_1 > 0$  and  $\gamma > 0$ , must be accomplished to guarantee a closed-loop stability.

#### **B. EXPERIMENTAL PLATFORM DESCRIPTION**

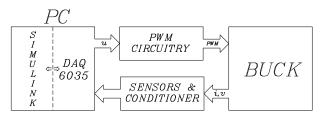

An experimental platform is designed and built using an NTE2984 power MOSFET and an NTE598 silicon rectifier diode as semiconductors in the buck circuit. The IR2110 is used as a high-speed power MOSFET driver. For the measurement of the inductor current i(t), an NT-5 current sensor from F.W. Bell is used while a conditioning circuit to measure the output voltage v(t) is implemented. The controllers are programmed in *Simulink/Matlab* with *Real Time Windows Target* installed in a PC with *Windows XP* that manages the data flowing through the data acquisition board NI-DAQ6035E by means of analog-to-digital and digital-to-analog conversions at 10 [kHz]. This arrangement is represented in Figure 4 and allows featuring the implementation of the controllers in real-time.

FIGURE 4. Block diagram of the experimental platform.

TABLE 1. Parameters of the buck converter for experiments.

| Parameter | Value | Unit       |

|-----------|-------|------------|

| L         | 5     | m[H]       |

| C         | 1000  | $\mu$ [F]  |

| R         | 63.25 | $[\Omega]$ |

Figure 5 shows a picture of the used experimental platform. A switching circuit is used to change the input voltage source E(t). For the implemented controllers, the used saturation limits are  $u_{\min} = 0.3$  and  $u_{\max} = 0.7$ . Therefore, in agreement to (3), the duty cycle percentage remains bounded as  $0.3 \le \mu(t) \le 0.7$ . The buck parameters used in the

**FIGURE 5.** Experimental platform equipped with circuits for output voltage and inductor current measurements, a circuit for an online modification of the input voltage E(t), a PWM circuit, and a DC–DC buck power converter with a replaceable capacitor, inductor, and resistor.

TABLE 2. Gain values used for the EGCE controller in equation (57).

| Gain        | Value  |

|-------------|--------|

| $\lambda_0$ | 1200   |

| $\lambda_1$ | 30     |

| $\gamma$    | 0.7    |

| $c_0$       | 200011 |

| $c_1$       | 16.96  |

**TABLE 3.** Gain values used for the proposed controller in equations (42)–(43), which satisfy the condition (27).

| Gain     | Value  |

|----------|--------|

| $k_v$    | 0.0002 |

| $k_o$    | 0.09   |

| $k_i$    | 0.01   |

| $k_{f1}$ | 2      |

| $k_{f2}$ | 80     |

experiments are shown in Table 1. The gain values of the EGCE controller are shown in Table 2 and the gain values of the proposed controller (42)–(43) in Table 3, which satisfy the condition (27) for the closed-loop stability. Besides,  $E^* = 17 [V]$  in all implementations. The observer gains used in both experiments are shown in Table 4, which satisfy the conditions in (41).

TABLE 4. Gain values of the proposed observer (32)–(34).

| Gain     | Value |

|----------|-------|

| $k_{v1}$ | 0.025 |

| $k_{v2}$ | 0.2   |

| $k_{i1}$ | 0.15  |

## C. EXPERIMENT 1: OUTPUT VOLTAGE REGULATION WITH VARIABLE SUPPLY VOLTAGE

In this experiment, the buck converter is affected by a periodic supply voltage E(t) given by

$E(t) = \begin{cases} 17 \ [V], & \text{for } 0 \le t < 5, \\ 14 \ [V], & \text{for } 5 \le t < 10, \\ 17 \ [V], & \text{for } 10 \le t < 15. \end{cases}$

The desired output voltage is given by  $v_d = 9[V]$ .

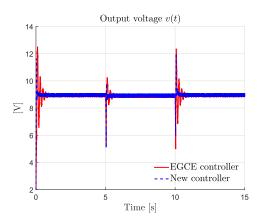

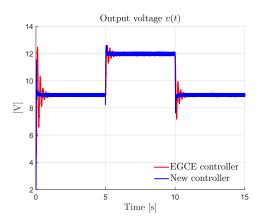

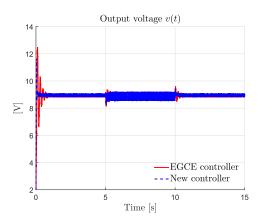

**FIGURE 6.** Experimental results: Output voltage v(t) obtained with the EGCE controller (57) and the proposed controller (42)–(43).

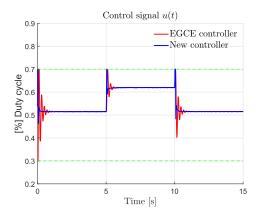

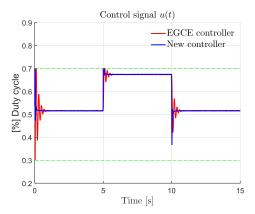

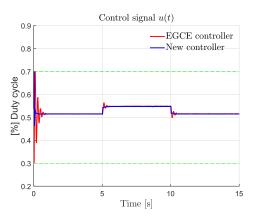

**FIGURE 7.** Experimental results: Duty cycle percentage  $\mu(t)$  obtained with the EGCE controller (57) and the proposed controller (42)–(43). Dotted lines represent the saturation limits  $u_{min}$  and  $u_{max}$ .

The output voltage regulation is achieved, as shown in Figure 6. It is relevant to mention that in spite of the fact that the action control  $\mu(t)$  is saturated for short intervals of time, as shown in Figure 7, the control objective is fulfilled by

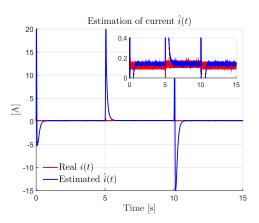

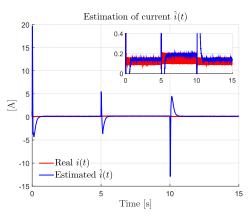

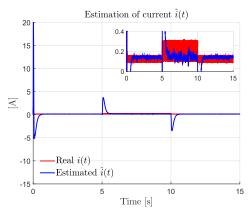

**FIGURE 8.** Experimental results: Comparison of the actual current i(t) and the estimated current  $\hat{i}(t)$  obtained using the proposed observer (32)–(34) and controller (42)–(43).

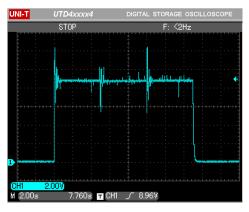

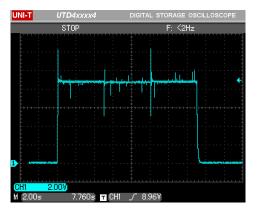

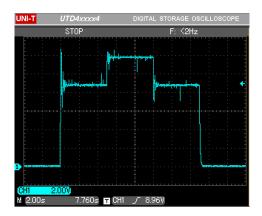

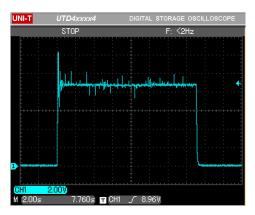

**FIGURE 9.** Experimental results: Output voltage v(t) measured with oscilloscope using the EGCE controller (57).

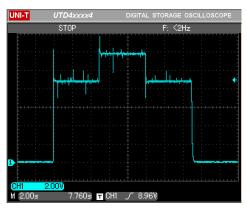

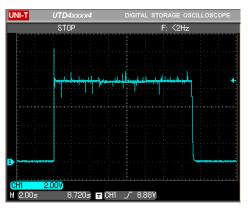

using the EGCE controller in (57) and the proposed scheme in (42)–(43). Using the proposed observer (32)–(34), the estimated current  $\hat{i}(t)$  converges to the measured current i(t), as shown in Figure 8. Peaks in the time evolution of  $\hat{i}(t)$  appear and disappear quickly when the source voltage *E* switches. However, convergence is accomplished, and the peaks in  $\hat{i}(t)$ do not affect the performance of the controller. The UNI-T UTD4204C desktop digital storage oscilloscope was used to observe the output voltage v(t) for comparison purposes. Figures 9 and 10 show the output voltage v(t) using the oscilloscope for the implementation of the EGCE controller (57) and the new controller (42)–(43), respectively. Results are in line with the ones displayed in Figure 6.

## D. EXPERIMENT 2: OUTPUT VOLTAGE REGULATION WITH VARIABLE DESIRED OUTPUT VOLTAGE

In this set of experiments, we considered the voltage source to be fixed to E(t) = 17[V] for all the experiment times and the desired output voltage  $v_d(t)$  as follows

$$v_d(t) = \begin{cases} 9 \ [V], & \text{for } 0 \le t < 5, \\ 12 \ [V], & \text{for } 5 \le t < 10, \\ 9 \ [V], & \text{for } 10 \le t < 15. \end{cases}$$

**FIGURE 10.** Experimental results: Output voltage v(t) measured with oscilloscope by using the proposed scheme (42)–(43).

**FIGURE 11.** Experimental results: Output voltage v(t) obtained with the EGCE controller (57) and the new controller (42)–(43). Dotted lines represent the desired output voltage  $v_d$ .

For the implementation of the proposed controller in (42)–(43) and the ECGE scheme in (57), the time evolution of the output voltage v(t) is shown in Figure 11. Similar to the previous experiments, saturation of the action control  $\mu(t)$  occurs for short intervals of time as seen in Figure 12. However, the control objective is fulfilled by using both the controllers as shown Figure 11. Similar to the previous experiment, the observer accomplishes the estimation of current  $\hat{i}(t)$ . It converges to the actual value of i(t), as shown in Figure 13. The convergence is achieved without affecting the performance of the proposed controller (42)–(43). Figures 14 and 15 show the output voltage v(t) using the oscilloscope for the implementation of the EGCE controller (57) and the new controller (42)–(43), respectively. Results are in line with the ones displayed in Figure 11.

## E. EXPERIMENT 3: OUTPUT VOLTAGE REGULATION WITH VARIABLE LOAD RESISTANCE

In this set of experiments, the voltage source and the desired output voltage set to E(t) = 17[V] and  $v_d(t) = 9[V]$ , respectively, for all experiment times. The load resistance is

**FIGURE 12.** Experimental results: Duty cycle percentage u(t) obtained with the EGCE controller (57) and the new controller (42)–(43). Dotted lines represent the saturation limits  $u_{min}$  and  $u_{max}$ .

**FIGURE 13.** Experimental results: Comparison of the actual current i(t) and the estimated current  $\hat{i}(t)$  using the proposed observer (32)–(34) and controller (42)–(43).

**FIGURE 14.** Experimental results: Output voltage v(t) measured with oscilloscope by using the EGCE controller (57).

switched as follows:

$$R = \begin{cases} 64.25 \ [\Omega], & \text{for } 0 \le t < 5, \\ 25 \ [\Omega], & \text{for } 5 \le t < 10, \\ 64.25 \ [\Omega], & \text{for } 10 \le t < 15. \end{cases}$$

**FIGURE 15.** Output voltage v(t) measured with oscilloscope by using the proposed scheme (42)–(43).

**FIGURE 16.** Experimental results: Output voltage v(t) obtained with the EGCE controller (57) and the proposed controller (42)–(43) varying the load resistance.

The output voltage regulation is achieved as is shown in Figure 16. The control objective is fulfilled by using the EGCE controller in (57) and the proposed scheme in (42)–(43). However, the output voltage v(t) in the time interval 5 < t < 10 is noisy, mainly because the load resistance is decreased, which implies at the same time that the inductor current increases, producing the switching noise. Using the proposed observer (32)–(34), the estimated current  $\hat{i}(t)$  converges to the measured current i(t), as shown in Figure 18. Similar to the output voltage v(t), in Figure 18, the current i(t)is more noisy when the load resistance is decreased; however, convergence is accomplished. The peaks and noises in i(t) do not affect the performance of the controller. Figures 19 and 20 show the output voltage v(t) using the oscilloscope for the implementation of the EGCE controller (57) and the proposed controller (42)-(43), respectively. Results are in line with the ones displayed in Figure 16.

#### F. DISCUSSIONS

The Figures 6, 11, and 16 displayed better results with the proposed controller. More specifically, the settling time is smaller for the novel scheme. Table 5 shows a comparison of the settling time produced by each controller in each

**FIGURE 17.** Experimental results: Duty cycle percentage  $\mu(t)$  obtained with the EGCE controller (57) and with the proposed controller (42)–(43) varying the load resistor. Dotted lines represent the saturation limits  $u_{min}$  and  $u_{max}$ .

**FIGURE 18.** Experimental results: Comparison of the actual current i(t) and the estimated current  $\hat{i}(t)$  using the proposed observer (32)–(34) and controller (42)–(43).

**FIGURE 19.** Experimental results: Output voltage v(t) measured with oscilloscope by using the EGCE controller (57).

one of the three experiments. Besides, as appreciated in Figures 6, 11, and 16, the implementation of the new controller presented the lower voltage peaks during the transients

**FIGURE 20.** Experimental results: Output voltage v(t) measured with oscilloscope using the proposed scheme (42)–(43).

**TABLE 5.** Settling times of the output voltage v(t) by using the EGCE scheme (57) and using the novel controller (42)–(43) in experiments.

|                   | EGCE       | New        |             |  |  |  |

|-------------------|------------|------------|-------------|--|--|--|

| Time range        | controller | controller | Improvement |  |  |  |

| Experiment 1      |            |            |             |  |  |  |

| $0 \le t < 5$     | 0.2399[s]  | 0.0516 [s] | 78.49%      |  |  |  |

| $5 \le t \le 10$  | 0.06 [s]   | 0.05 [s]   | 16.66%      |  |  |  |

| $10 \le t \le 15$ | 0.21 [s]   | 0.09 [s]   | 57.14%      |  |  |  |

| Experiment 2      |            |            |             |  |  |  |

| $0 \le t < 5$     | 0.241[s]   | 0.048[s]   | 80.08%      |  |  |  |

| $5 \le t \le 10$  | 0.039[s]   | 0.002 [s]  | 94.87%      |  |  |  |

| $10 \le t \le 15$ | 0.13 [s]   | 0.04 [s]   | 96.92%      |  |  |  |

| Experiment 3      |            |            |             |  |  |  |

| $0 \le t < 5$     | 0.239[s]   | 0.05 [s]   | 79.07%      |  |  |  |

| $5 \le t \le 10$  | 0.005 [s]  | 0.004 [s]  | 20%         |  |  |  |

| $10 \le t \le 15$ | 0.006 [s]  | 0.004 [s]  | 33.33%      |  |  |  |

at the beginning of the experiments and at the commutation time of either the supply voltage E, the desired voltage  $v_d$ , or the load resistance R.

## **VI. CONCLUSIONS**

Voltage regulation of a buck power converter under input saturation was addressed in this paper and achieved using a novel controller that is robust to the saturation of the duty cycle. Analysis of the closed-loop trajectories was theoretically supported by Lyapunov's theory. Even though the buck power converter was seen to be affected by the input saturation, the convergence of the output voltage error was guaranteed. The problem of unmeasurable current was also addressed. Derived from the proposed full-state feedback controller, a novel observer-based scheme was introduced. Three sets of experiments were presented. Experimental comparisons with respect to a known controller showed that the proposed observer-based algorithm not only works well but also presents a better performance. Further research suggests considering parasitic effects in the buck power converter model and the input saturation, which result in a very complicated problem.

#### REFERENCES

IEEE Access

- C. Chang, "Commercial power electronics controllers," in *Dynamics and* Control of Switched Electronic Systems. London, U.K.: Springer-Verlag, 2012, pp. 63–131.

- [2] A. El Aroudi, "A new approach for accurate prediction of subharmonic oscillation in switching regulators—Part I: Mathematical derivations," *IEEE Trans. Power Electron.*, vol. 32, no. 7, pp. 5651–5665, Jul. 2017.

- [3] W. Wang, A. R. Tell, and D. Nesić, "Averaging results pertaining to the implementation of hybrid feedback via PWM control," in *Dynamics and Control of Switched Electronic Systems*. London, U.K.: Springer-Verlag, 2012, pp. 275–297.

- [4] S. Bacha, I. Munteanu, and A. I. Bratcu, Power Electronic Converters Modeling and Control: With Case Studies. London, U.K.: Springer-Verlag, 2014.

- [5] J. Guzman-Guemez and J. Moreno-Valenzuela, "Saturated control of boost DC-to-DC power converter" *Electron. Lett.*, vol. 49, no. 9, pp. 613–615, Apr. 2013.

- [6] A. Tani, M. B. Camara, and B. Dakyo, "Energy management based on frequency approach for hybrid electric vehicle applications: Fuel-cell/lithium-battery and ultracapacitors," *IEEE Trans. Veh. Technol.*, vol. 61, no. 8, pp. 3375–3386, Oct. 2012.

[7] F. Bonanno, G. Capizzi, and G. L. Sciuto, "Improved SMPS modeling for

- [7] F. Bonanno, G. Capizzi, and G. L. Sciuto, "Improved SMPS modeling for photovoltaic applications by a novel neural paradigm with Hamiltonianbased training algorithm," in *Proc. Int. Conf. Clean Elect. Power (ICCEP)*, Jun. 2015, pp. 723–730.

- [8] A. Martinelli, P. Nahata, and G. Ferrari-Trecate, "Voltage stabilization in MVDC microgrids using passivity-based nonlinear control," in *Proc. 57th IEEE Annu. Conf. Decis. Control (CDC)*, Dec. 2018, pp. 7022–7027.

- [9] A. Iovine and F. Mazenc, "Bounded control for DC/DC converters: Application to renewable sources," in *Proc. IEEE Conf. Decis. Control (CDC)*, Dec. 2018, pp. 3415–3420.

- [10] J. P. Agrawal, Power Electronic Systems: Theory and Design. Upper Saddle River, NJ, USA: Prentice-Hall, 2001.

- [11] H. Sira-Ramirez and R. Silva-Ortigoza, Control Design Techniques in Power Electronics Devices. London, U.K.: Springer-Verlag, 2006.

- [12] M. Spinetti, E. Fossas, and D. Biel, "Stability analysis of a Lyapunovbased controlled boost converter," in *Proc. 48th IEEE Conf. Decis. Control*, Dec. 2009, pp. 6544–6548.

- [13] J. Alvarez-Ramirez, G. Espinosa-Pérez, and D. Noriega-Pineda, "Currentmode control of DC–DC power converters: A backstepping approach," *Int. J. Robust Nonlinear Control*, vol. 13, no. 5, pp. 421–442, 2003.

- [14] M. A. Ahmad, R. M. T. R. Ismail, and M. S. Ramli, "Control strategy of buck converter driven DC motor: A comparative assessment," *Austral. J. Basic Appl. Sci.*, vol. 4, no. 10, pp. 4893–4903, 2010.

[15] H. Cho, S. J. Yoo, and S. Kwak, "State observer based sensor less control

- [15] H. Cho, S. J. Yoo, and S. Kwak, "State observer based sensor less control using Lyapunov's method for boost converters," *IET Power Electron.*, vol. 8, no. 1, 11–19, Jan. 2015.

- [16] Z. Wu and C.-H. Liu, "Nonlinear current-mode controller for DC/DC boost power converters," *Electron. Lett.*, vol. 47, no. 3, pp. 209–211, Feb. 2011.

[17] C.-S. Chiu, Y.-T. Lee, and C.-W. Yang, "Terminal sliding mode control

- [17] C.-S. Chiu, Y.-T. Lee, and C.-W. Yang, "Terminal sliding mode control of DC-DC Buck converter," in *Control and Automation*. Berlin, Germany: Springer, 2010, pp. 79–86.

- [18] Y.-T. Lee, C.-S. Chiu, and C.-T. Shen, "Adaptive fuzzy terminal sliding mode control of DC-DC buck converters via PSoC," in *Proc. IEEE Int. Conf. Control Appl.*, Sep. 2010, pp. 1205–1209.

- [19] C.-S. Chiu and C.-T. Shen, "Finite-time control of DC–DC buck converters via integral terminal sliding modes," *Int. J. Electron.*, vol. 99, no. 5, pp. 643–655, 2012.

- [20] H. Du, X. Lai, and C. Liu, "Design of a synchronous boost DC–DC converter with constant current mode control in MPP," *Analog Integr. Circuits Signal Process.*, vol. 84, no. 2, pp. 223–235, 2015.

- [21] Y. Massaoudi, D. Elleuch, D. Mehdi, T. Damak, and G. Hashim, "Comparison between non linear controllers applied to a DC-DC boost converter," *Int. J. Innov. Comput., Inf. Control*, vol. 11, no. 3, pp. 935–947, 2015.

- [22] L. Ma, Y. Zhang, X. Yang, S. Ding, and L. Dong, "Quasi-continuous second-order sliding mode control of buck converter," *IEEE Access*, vol. 6, pp. 17859–17867, 2018.

- [23] W. Ma et al., "Stabilizing the buck converter with a first-order-filter-based time delay feedback controller," *IEEE Access*, vol. 6, pp. 1967–1973, 2017.

- [24] D. Angulo-Garcia, F. Angulo, G. Osorio, and G. Olivar, "Control of a DC-DC buck converter through contraction techniques," *Energies*, vol. 11, no. 11, p. 3086, 2018.

- [25] M. Nashed and A. A. Fayed, "Current-mode hysteretic buck converter with spur-free control for variable switching noise mitigation," *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 650–664, Jan. 2018.

[26] W. Qi, S. Li, S.-C. Tan, and S. Y. R. Hui, "Parabolic-modulated sliding-

- [26] W. Qi, S. Li, S.-C. Tan, and S. Y. R. Hui, "Parabolic-modulated slidingmode voltage control of a buck converter," *IEEE Trans. Ind. Electron.*, vol. 65, no. 1, pp. 844–854, Jan. 2018.

- [27] C. Olalla, I. Queinnec, R. Leyva, and A. El Aroudi, "Robust optimal control of bilinear DC–DC converters," *Control Eng. Pract.*, vol. 19, no. 7, pp. 688–699, 2011.

[28] C. Olalla, R. Leyva, A. El Aroudi, I. Queinnec, and S. Tarbouriech, "H<sub>∞</sub>

- [28] C. Olalla, R. Leyva, A. El Aroudi, I. Queinnec, and S. Tarbouriech, " $H_{\infty}$  control of DC-DC converters with saturated inputs" in *Proc. 35th Annu. Conf. IEEE Ind. Electron. (IECON)*, Nov. 2009, pp. 548–553.

- [29] M. Feki, A. El Aroudi, B. G. M. Robert, and N. Derbel, "Control of a two-cell DC/DC converter in presence of saturating duty cycle" in *Proc. 13th Int. Power Electron. Motion Control Conf.*, Sep. 2008, pp. 2120–2125.

[30] D. Karagiannis, A. Astolfi, and R. Ortega, "Two results for adaptive output

- [30] D. Karagiannis, A. Astolfi, and R. Ortega, "Two results for adaptive output feedback stabilization of nonlinear systems," *Automatica*, vol. 39, no. 5, pp. 857–866, 2003.

- [31] J. Guzman-Guemez and J. Moreno-Valenzuela, "Stability analysis of a controller/observer for input–constrained DC–DC boost power converters," in *Proc. Conf. Control Appl.*, 2013, pp. 75–82.

- [32] J. Moreno-Valenzuela and J. Guzman-Guemez, "Experimental evaluations of voltage regulators for a saturated boost DC-to-DC power converter," *Trans. Inst. Meas. Control*, vol. 38, no. 3, pp. 327–337, 2016.

[33] Q. Chen, X. Ren, and J. A. Oliver, "Identifier-based adaptive neural

- [35] Q. Chen, X. Ren, and J. A. Oliver, "Identifier-based adaptive neural dynamic surface control for uncertain DC–DC buck converter system with input constraint," *Commun. Nonlinear Sci. Numer. Simul.*, vol. 17, no. 4, pp. 1871–1883, 2012.

- [34] G. C. Konstantopoulos and Q.-C. Zhong, "Nonlinear control of DC/DC power converters with inherent current and power limitation," in *Proc. 24th Medit. Conf. Control Automat.*, Jun. 2016, pp. 949–954.

- [35] H. El Fadil, F. Giri, F.-Z. Chaoui, and O. El Magueri, "Accounting for input limitation in the control of buck power converters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 6, pp. 1260–1271, Jun. 2009.

- [36] A. Benzaouia, H. M. Soliman, and A. Saleem, "Regional pole placement with saturated control for DC-DC buck converter through hardware-in-theloop," *Trans. Inst. Meas. Control*, vol. 38, no. 9, pp. 1041–1052, 2016.

- [37] A. Benzaouia, F. Mesquine, and M. Benhayoun, *Saturated Control of Linear Systems*. Cham, Switzerland: Springer International Publishing AG, 2018.

- [38] B. L. Dokić and B. Blanuša, Power Electronics: Converters and Regulators. Berlin, Germany: Springer-Verlag, 2015.

- [39] J.-J. E. Slotine and W. Li, *Applied Nonlinear Control*. Englewood Cliffs, NJ, USA: Prentice-Hall, 1991.

- [40] M. Krstić, I. Kanellakopoulos, and P. Kokotović, Nonlinear and Adaptive Control Design. New York, NY, USA: Wiley, 1995.

- [41] H. K. Khalil, Nonlinear System, 3rd ed. Upper Saddle River, NJ, USA: Prentice-Hall, 2002.

- [42] K. Ogata and Y. Yang, *Modern Control Engineering*, 3rd ed. Upper Saddle River, NJ, USA: Prentice-Hall, 2002, pp. 710–717.

- [43] J. Moreno-Valenzuela and O. García-Alarcón, "On control of a boost DC-DC power converter under constrained input," *Complexity*, vol. 2017, Art. no. 4143901.

**OCTAVIO GARCÍA-ALARCÓN** received the B.Sc. degree in electronics and instrumentation from Universidad Veracruzana, Xalapa, Mexico, in 2002, and the M.Sc. degree in digital systems from Instituto Politécnico Nacional-CITEDI, Tijuana, Mexico, in 2013, where he is currently pursuing the Ph.D. degree in digital systems. His research interests include power electronics systems, robotics, and electronic instrumentation systems.

JAVIER MORENO-VALENZUELA received the Ph.D. degree in automatic control from the CICESE Research Center, Ensenada, Mexico, in 2002. He was a Postdoctoral Fellow with the Université de Liége, Belgium, from 2004 to 2005. He is currently with Instituto Politécnico Nacional-CITEDI, Tijuana, Mexico. He is the author of many peer-reviewed journals and international conference papers and the book *Motion Control* of Underactuated Mechanical Systems (Springer-

Verlag, 2018). His research interests include nonlinear systems, mechatronics, and intelligent systems. He has served as a Reviewer of a number of prestigious scientific journals. He is also an Associate Editor of the IEEE LATIN AMERICA TRANSACTIONS and *Mathematical Problems in Engineering*.