Received July 20, 2018, accepted August 19, 2018, date of publication August 27, 2018, date of current version October 17, 2018. Digital Object Identifier 10.1109/ACCESS.2018.2867227

# A 5-Gb/s 66 dB CMOS Variable-Gain Amplifier With Reconfigurable DC-Offset Cancellation for Multi-Standard Applications

ZHIQING LIU<sup>1</sup>, (Student Member, IEEE), YUNQIU WU<sup>©1</sup>, (Member, IEEE), CHENXI ZHAO<sup>®1</sup>, (Member, IEEE), JOHANNES BENEDIKT<sup>2</sup>, AND KAI KANG<sup>®1</sup>, (Member, IEEE)

<sup>1</sup>School of Electronic Engineering, University of Electronic Science and Technology of China, Chengdu 611731, China <sup>2</sup>School of Engineering, Cardiff University, Cardiff CF10 3AT, U.K.

Corresponding author: Kai Kang (kangkai@uestc.edu.cn)

This work was supported in part by the National Natural Science Foundation of China under Grant 61331006 and Grant 61771115, in part by the National Science and Technology Major Project of the Ministry of Science and Technology of China under Grant 2016ZX03001015-004, and in part by the Fundamental Research Funds for the Central Universities under Grant ZYGX2016J036.

**ABSTRACT** This paper proposes a variable gain amplifier (VGA) with reconfigurable DC-offset cancellation (DCOC) for multi-standard applications. In this design, a cell-based design method and some bandwidth extension technologies are adopted to achieve a high data rate and a wide gain control range simultaneously. In addition, the DCOC having a tunable lower-cutoff frequency can make an optimum compromise between BER and SNR according to the specified baseband standard. The measurements show that the VGA achieves a gain control range from -6 dB to 60 dB, a bandwidth beyond 3 GHz, and a tunable lower-cutoff frequency from 0 to 300 kHz. When entering a 2<sup>23</sup>-1 pseudo-random bit sequence signal at 5 Gb/s, the VGA consumes 17 mW from a 1.2-V supply and the output data peak-to-peak jitter is less than 40 ps. The VGA is fabricated in a 90-nm CMOS process with a chip size (including all pads) of 0.52 × 0.5 mm<sup>2</sup>.

**INDEX TERMS** CMOS VGA, cell-based design, high data rate, reconfigurable, multi-standard applications.

#### I. INTRODUCTION

RCENTLY, the development of wireless transceivers with high data transfer rate has attracted increasing attention from both the industry and the academia [1]. Among them, the variable-gain amplifier (VGA) as a key module is allocated between RF front-end and baseband circuit to maintain the input signal amplitude within a reasonable range, which can effectively enhance the entire system dynamic range and linearity. In most broadband receivers, the VGA usually operates at low frequency but high data rate (Gb/s). For such applications, a thoughtful circuit design is needed for the VGA to ensure sufficient gain range and wide bandwidth

Fabrication of VGAs in CMOS process remains attractive for low price and ease of integration. However, compared with the high-speed III-V processes such as GaAs or InP, the inferior driving capability and the intrinsic large substrate loss of CMOS severely restrict the design of a high-gain broadband amplifier [2]. For the VGA, these drawbacks have greater impact. Particular limitations are the gain and control range in a broadband VGA. Besides, the dc offset at the input of the VGA is another critical issue, which needs to be eliminated to avoid saturating the following stages [3]. Therefore, a dc-offset cancellation (DCOC) is required, especially for high gain VGAs [4]. In DCOC, the lower-cutoff frequency  $(f_{\rm L})$  is a key specification for baseband standards [5]. For example, some signals (i.e., random binary or *M*-ary data) gather the most of energy at dc of the spectrum, they may be corrupted if filtered with a high  $f_{\rm L}$  [6]. However, a low  $f_{\rm L}$ close to dc may also cause temporary data loss under wrong initial conditions and a long loop settling time [5]. To solve this contradiction,  $f_{\rm L}$  should better be adjusted according to the given system requirements. Until now, studies have rarely focused on the DCOC tuning scheme in the VGA design. In [7]–[9], digitally-assisted DCOC methods are provided with an adjustable  $f_{\rm L}$ . Nevertheless, an ADC and a DAC are indispensable in the DCOC loop, which makes them unsuitable for high-speed (multi-Gb/s) applications and often consumes a relatively high dc power with increased data rate. Although there are some reconfigurable RF front-end techniques for broadband interface, some insufficiencies have

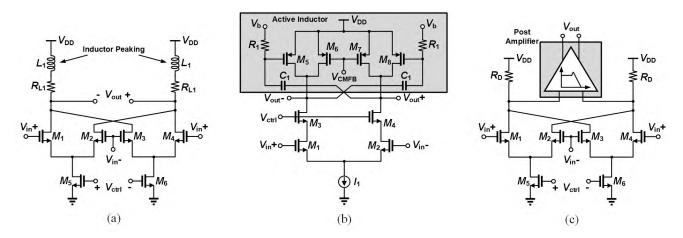

FIGURE 1. (a) Gilbert core with peaking inductor load, (b) differential cascode structure using active inductor load, and (c) Gilbert core using gain-peaking post amplifier for a fast speed.

not been solved. In [10], an active RC filter with an array of switched binary-weighted capacitors is adopted. However, it needs a lot of duplicated components to ensure a certain degree of redundancy and thus occupies a large chip area. To resolve this problem, a dual-mode complex filter [11] is realized by the opamp-based RC filter, which only requires less than 20% area occupation for the tuning components. However, it causes a more complex circuit implementation due to the high-order filters. In [12], a programmable complex integrator based on the current division network (CDN) is proposed. It has wider tuning range and higher tuning resolution, but at cost of additional power consumption and more loss in signal path owing to the use of two opamps per integrator.

In this paper, a CMOS VGA with reconfigurable DCOC is presented. By adopting a cell-based design method [13], the limitation on gain-bandwidth product (GBW) of each cascaded variable gain cell is alleviated. Thus, the gain and bandwidth of the whole VGA can be improved simultaneously. Meanwhile, other broadband technologies like the second-order active feedback and the neutralization capacitance are incorporated in the unit variable gain cell (VGC) to further enhance the bandwidth. Besides, the VGA features a reconfigurable DCOC with a voltage controlled lower-cutoff frequency, making it suitable for multi-standard applications.

## **II. CIRCUIT DESIGN AND ANALYSIS**

Conventionally, most of wideband VGAs [14]–[16] are realized in a single variable gain stage with cascading one or several fixed gain stages. In this way, the gain range and the bandwidth are mainly determined by the variable gain stage. Besides, in order to make a gain control more efficient and not affecting the common-mode output voltage, the variable gain stage often adopts the Gilbert structure. However, it suffers from a high parasitic capacitance at the output node owing to the cross-coupled differential transistors. To eliminate this effect, Fig. 1 reviews some high-speed Gilbert structures. In Fig.1 (a), a pair of series inductors is adopted as an inductive peaking at the output load terminal [14]. This method can significantly improve the bandwidth. However, an excessive chip area may be required due to the introduction of onchip inductors, especially when cascading multi-stage of such amplifier. To alleviate the area problem, the active inductor is an alternative to suppress the affect of the parasitic capacitance by introducing impedance peaking at the -3 dBfrequency [17]. Fig. 1(b) shows the typical implementation.  $R_1$  and  $C_1$  together construct a high-pass network so that the high-frequency signal can be bypassed to the gate of transistors  $M_{5-8}$ , leading to positive feedback in this active load and thus a gain compensation at high frequency. Although the active inductor can save chip area, it introduces large noise, nonlinearity and additional load capacitance. In addition, since the gain-control transistors  $M_{1-2}$  operate in the triode region, extra nonlinearity may be brought when there is a large signal input, particularly at low-gain state [16]. Fig. 1(c) shows another way to make up the gain loss in high frequency. By introducing peaking in the post amplifiers rather than in the load of the gain core itself [15], a flat frequency response can be achieved if the compensated peaking is situated right in the -3 dB frequency of the variable gain core. However, due to the existence of process and temperature variations, there may be an intolerable peaking for cascaded stages of post amplifiers. Therefore, it is difficult to realize a large gain and gain control range while maintaining a high-speed operation only by using a single variable gain stage.

## A. ANALYSIS OF THE CELL-BASED DESIGN METHOD

For any active device, its GBW is inherently fixed. In other words, if a single-stage amplifier achieves a high gain, then its bandwidth is limited. To solve this contradiction, the single-stage amplifier can be regarded as an individual cell for compromising its gain and bandwidth. Then, making several identical cells cascaded to obtain a high gain and a wide bandwidth simultaneously. Generally, such a cell-based

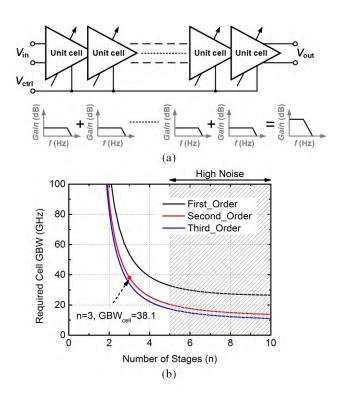

**FIGURE 2.** (a) The architecture of the cell-based VGA, and (b) the required GBW vs. the number of stages for  $A_{\text{tot}} = 50$  dB and  $BW_{\text{tot}} = 4$  GHz.

design method has often been employed in an amplifier requiring a wide bandwidth [18]. If this method is applied to the design of a broadband VGA, there is more space for implementation of a large gain control range by adopting a multi-stage structure. Fig. 2 shows the architecture of this cell-based VGA. Assuming that the VGA consists of *n* VGCs with *m*th-order Butterworth frequency response, the required GBW of each VGC is [2]

$$GBW_{VGC} = \frac{BW_{tot}}{\sqrt[2m]{\sqrt[n]{2} - 1}} \sqrt[n]{A_{tot}}$$

(1)

where  $A_{tot}$  is the overall gain of the cascaded VGCs,  $BW_{tot}$  is the overall bandwidth. If  $A_{tot} = 50$  dB and  $BW_{tot} = 4$  GHz are targeted, the required  $GBW_{VGC}$  under m = 1, 2, 3 is a decreasing function of stage n as shown in Fig. 2(b). Note that the required  $GBW_{VGC}$  can be alleviated rapidly if using large n and m. However, with the maximum number of stage and order, some practical factors also need to be considered, i.e., power consumption and noise. Power consumption increases with the large n and m. In addition, it results in a reduced gain per stage due to a fixed total gain and thus makes a rapid noise accumulation from the gain stages. As a result, the input-referred noise figure (NF) of the whole VGC stage is significantly degraded. This effect can be quantified by [19]

$$\frac{NF_{\infty} - 1}{NF_p - 1} = \frac{1}{1 - 1/A_p}$$

(2)

where  $NF_{\infty}$  denotes the NF of an infinite number of cascaded gain stages,  $NF_{\rm p}$  is the NF of each gain stage and  $A_{\rm p}$  is the

It is significant to note that the gain range of the VGA can be enlarged effectively by cascading multiple VGCs, but there still exists some challenges in implementation of such a cell. Firstly, the gain error of each cell must be as small as possible to keep the whole accumulated error not exceed the accepted value. Secondly, since a very wideband cell is required due to the gain-bandwidth tradeoff, then some broadband techniques are indispensable for the cell design. Thirdly, the cell should be designed with low power consumption and minimum chip occupation, or else that the total cost of the entire VGA will be excessive. Accordingly, a simple topology is preferred while it is helpful to achieve a wide bandwidth owning to the inherently less parasitic capacitance.

**B. DESIGN OF THE VGC WITH EXTENDED BANDWIDTH** The bandwidth of the overall cascaded VGCs is given by

$$BW_{tot} = BW_{cell} \sqrt[2m]{n/2} - 1 \tag{3}$$

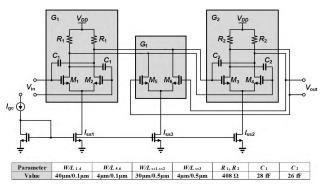

where  $BW_{cell}$  is the bandwidth of unit VGC. Note that the total bandwidth of the VGA will decrease with the number of *n*. Thus, each VGC should have a sufficient bandwidth space to allow for this shrinkage. To enhance the bandwidth of the VGC without sacrificing large chip area or voltage headroom, a second-order gain structure with active feedback is employed. Fig. 3 shows the schematic, where  $G_1$ ,  $G_2$  are the gain stages and  $G_f$  is the feedback stage. The  $G_f$  consists of a differential pair ( $M_5 \sim M_6$ ) with a shared resistive load  $R_1$  to make a trade-off between bandwidth and gain.

FIGURE 3. Schematic of the 2-order VGC using active feedback.

For the convenience of analysis, both the gain and feedback stages can be expressed by the single-pole response functions:

$$G_1(s) = G_2(s) = \frac{G_m R}{1 + sRC}$$

(4)

$$G_f(s) = \frac{G_{mf}R}{1 + sRC}$$

(5)

where *R* is the resistive load, *C* is the parasitic capacitance of the differential pairs, and the corresponding transconductances of the stages are  $G_m$  and  $G_{mf}$ . Since a fraction of

output signal is returned to the input of  $G_1$  by  $G_f$ , the transfer function of the second-order VGC is thus given by

$$H_{2nd}(s) = \frac{G_m^2 R^2}{(1 + sRC)^2 + G_m G_{mf} R^2}$$

$$= \frac{A_0^2}{(1 + s/\omega_0)^2 + A_0 \beta}$$

(6)

where  $\omega_0 = 1/RC$ ,  $A_0 = G_m R$  and  $\beta = G_{mf} R$ . So the first dominant pole is

$$\omega_{p1} = -\omega_0 (1 + \sqrt{A_0 \beta}) \tag{7}$$

Since the -3 dB bandwidth is determined by the first dominant pole, the bandwidth can be effectively enhanced by using a large feedback gain  $\beta$ . However, considering that the associated gain peaking is also in proportion with the feedback gain  $\beta$  [2], the ratio of feedback should be selected within a reasonable range. Otherwise, the accumulated gain peaking (when multiply VGCs are cascaded) becomes serious, which will cause system instability. Thus, other methods need to be employed to further optimize the bandwidth. Note that the  $\omega_0$  is inversely proportional to capacitive loads C. By reducing the input capacitance of  $G_1$ ,  $G_2$  can reduce the capacitive load of the previous stage and then enhance the bandwidth. Therefore, two pairs of neutralization capacitance are placed in parallel with the differential transistors  $M_1 \sim M_2/M_3 \sim M_4$ . These neutralization capacitances are realized by exploiting the Miller-effect. The effective input capacitance seen at the input of  $G_1$ ,  $G_2$  is given by

$$C'_{eff-in} = C_{in} + (1-A)C_1 \tag{8}$$

where *A* is the gain of  $G_1$ ,  $G_2$ ,  $C_{in}$  is the original input capacitance of  $G_1$ ,  $G_2$ ,  $C'_{eff-in}$  is the effective input capacitance. If A > 1, the Miller capacitance  $(1-A)C_1$  becomes negative, leading to a reduced  $C'_{eff-in}$ .

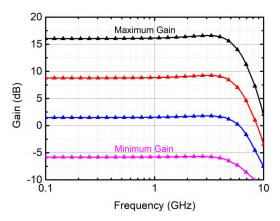

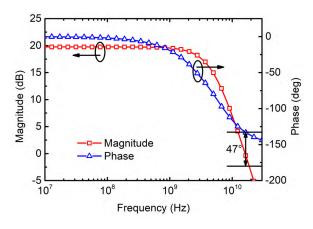

FIGURE 4. Simulated frequency response of the optimized VGC.

Fig. 4 shows the simulated frequency response of the optimized VGC, where the bandwidth is beyond 5 GHz with a maximum gain of 16 dB. Besides, the stability problem of each VGC also needs to be considered due to the introduction of the feedback structure. The simulated open-loop phase

FIGURE 5. Simulated frequency response of the VGC at maximum gain.

margins of the VGC at all gain states are beyond 45 degrees while the maximum gain is about 47 degree as shown in Fig. 5, which can ensure a sufficient stability.

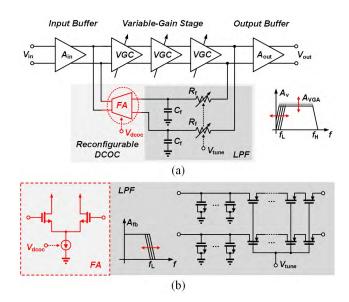

**FIGURE 6.** (a) Block diagram of the proposed VGA and (b) sub-circuits of the reconfigurable DCOC.

## C. PROPOSED DCOC WITH TUNABLE LOW-CUTOFF FREQUENCY

Fig. 6(a) shows the block diagram of the proposed VGA, including an input buffer, a three-stage VGC, a reconfigurable DCOC and an output buffer. The input buffer employs a differential common-source amplifier with a gain of 13.1 dB. The output buffer is designed for the practical application and measurement requirements with a gain of 0 dB. Since it needs to provide a large current to keep an adequate output swing for an input impedance of  $50-\Omega$ , a  $f_{\rm T}$  doubler topology [18] is adopted to relax the limited bandwidth owing to using large-size transistors. The reconfigurable DCOC in this VGA comprises a LPF and a feedback amplifier (FA)

as shown in Fig. 6(b). The LPF extracts the dc component from output of the variable gain stage and then transfers it to the FA for generating a correction current. Generally, the values of components  $C_{\rm f}$  and  $R_{\rm f}$  in LPF design are very large as the frequencies tend to dc. To avoid excessive chip size and facilitate control, multiple NMOS transistors in parallel are used to construct a large shunt capacitor and several PMOS transistors operating in triode region are also cascaded to realize an adjustable resistor that can cover the required frequency range. The large shunt capacitance  $C_{\rm f}$  is designed to have a fixed value. The source and drain of the NMOS transistor are connected to ground as the bottom plate of the equivalent capacitor while the gate is used as the top plate. The channel resistance  $R_{on}$  from drain to source in the PMOS transistor is linear and can be controlled by its gate voltage  $V_{\text{tune}}$  [20]. It follows that,

$$R_{on} = \frac{1}{\mu_p C_{ox} \frac{W}{L} (V_{DD} - V_{tune} - |V_{TH}|)} \tag{9}$$

where  $\mu_p$  is the electron mobility,  $C_{ox}$  is the gate oxide capacitance per unit area, W/L is the aspect ratio of the PMOS transistors and  $V_{TH}$  is the threshold voltage. By changing the control voltage  $V_{tune}$ , the value of  $R_{on}$  changes and then the  $f_L$  of the VGA can be varied.

In addition, the DCOC function is controlled by a MOS switch. When  $V_{dcoc} = 1.2$  V, the DCOC does not work. The VGA exhibits a low-pass characteristic and thus the dc component is permitted to enter the baseband. When  $V_{dcoc} = 0$  V, the DCOC function is enabled. By tuning the  $f_L$ , the receiver front-end interface can be configured flexibly according to the specified baseband standard. As a result, the whole circuit can achieve an improved SNR and a high efficiency in baseband processing without sacrificing the BER specification.

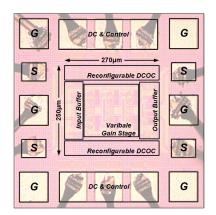

FIGURE 7. Die photo of the fabricated VGA.

## **III. MEASUREMENT RESULTS**

Fig. 7 shows a die microphotograph of the proposed design. Fabricated in a 90-nm CMOS process, the chip size of the VGA is  $0.52 \times 0.5 \text{ mm}^2$ , including all the measurement pads. The circuit has been measured by Chip-on-Board (COB). Under a 1.2-V supply voltage, the VGA consumes a total dc power of 17 mW.

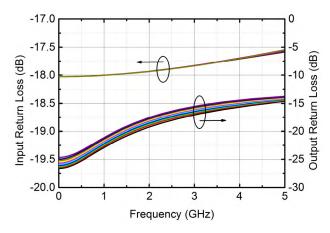

FIGURE 8. Measured return loss vs. various control currents *I*<sub>gc</sub> at input and output ports.

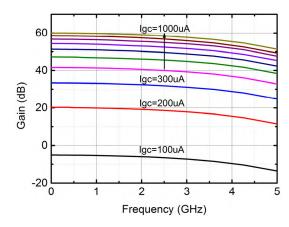

**FIGURE 9.** Measured voltage gain in various control currents *I<sub>gc</sub>* vs. frequency.

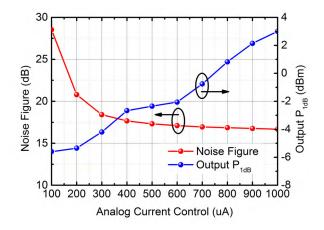

**FIGURE 10.** Measured NF and  $OP_{1dB}$  at 1 GHz vs. various control currents  $I_{qc}$ .

Fig. 8 shows the measured return loss vs. control current  $I_{gc}$  at input and output ports. The values of these two ports are better than 10 dB within the entire operating frequency range. Fig. 9 shows the measured tunable gain range from -6 to 60 dB with a -3 dB bandwidth beyond 3 GHz.

TABLE 1. Performance comparison of the state-of-the-art VGAs.

| Ref.              | Tech.                  | Control<br>mode    | Freq.<br>(GHz)     | Gain range<br>(dB) | Data rate<br>(Gb/s) | NF<br>(dB) | Jitter<br>(pp) | OP <sub>1dB</sub><br>(dBm) | Reconfig.<br>DCOC | Power<br>(mW)    | Chip Area<br>(mm <sup>2</sup> ) |

|-------------------|------------------------|--------------------|--------------------|--------------------|---------------------|------------|----------------|----------------------------|-------------------|------------------|---------------------------------|

| [15]<br>2012 JSSC | 0.13-μm<br>SiGe BiCMOS | Analog<br>voltage  | 0.0002-7.5         | -10 to 30          | 5                   |            | 40 ps          | -                          | Ν                 | 72*@1.2V         | 1*                              |

| [21]<br>2012 TCSI | 90-nm<br>CMOS          | Analog<br>voltage  | 0.0002-2.2         | -10 to 50          | -                   | 17 to 30   | -              | -3                         | Ν                 | 2.5 @1.0V        | 0.7                             |

| [22]<br>2013 RFIC | 65-nm<br>CMOS          | Digital<br>current | 0.02-1             | +3 to +31          | -                   | 6 to 21    | -              | 0                          | Ν                 | 48 @1.1V         | 1**                             |

| [23]<br>2014 TMTT | 0.18-μm<br>SiGe BiCMOS | Digital<br>current | 0.003-1.17         | -1.4 to 30.2       | 2                   | 24 to 52   | -              | -10                        | Ν                 | 35 @1.8V         | 0.25***                         |

| [24]<br>2016 MWCL | 65-nm<br>CMOS          | Analog<br>current  | (0~0.0002)<br>-4   | -39.4 to 20.2      | -                   | 10 to 27   | -              | -9.8                       | Y                 | 26 @1.2V         | 0.32                            |

| [16]<br>2016 JSSC | 0.13-μm<br>CMOS        | Analog<br>voltage  | 0.0001-5           | -15 to 25          | 10                  | -          | 44 ps          | -                          | N                 | 50 @1.2V         | 1.07                            |

| [25]<br>2016 TMTT | 65-nm<br>CMOS          | Analog<br>voltage  | 0.0004-2           | 2 to 24            | -                   | 24 to 29   | -              | 1.8                        | Ν                 | 3.5*** @<br>1.2V | 0.01***                         |

| This work         | 90-nm<br>CMOS          | Analog<br>current  | (0~0.0003)<br>-3.3 | -6 to 60           | 5                   | 15.2 to 29 | 39 ps          | 3                          | Y<br>(0-300kHz)   | 17 @1.2V         | 0.26                            |

\*=With Temperature Compensation Block; \*\*=With Digital Control; \*\*\*= VGA core only

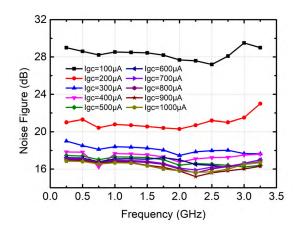

FIGURE 11. Measured NF vs. frequency under various control currents Igc.

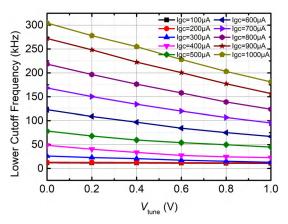

**FIGURE 12.** Measured  $f_{\rm L}$  of the reconfigurable DCOC vs.  $V_{\rm tune}$  at different gains.

Fig. 10 shows the NF and output  $P_{1dB}$  with control current  $I_{gc}$  ranging from 100  $\mu$ A to 1000  $\mu$ A in 100  $\mu$ A steps at 1 GHz. The NF is from 16.7 to 33.5 dB and the OP<sub>1dB</sub> is 3 dBm at maximum gain ( $I_{gc} = 1000 \ \mu$ A). Moreover, Fig. 11 shows

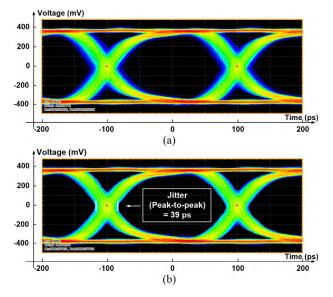

**FIGURE 13.** Measured output eye diagram at (a) 5 mVpp, (b) 20 mV<sub>pp</sub>, 5 Gb/s 2<sup>23</sup>-1 PRBS input data (Horizontal scale: 50 ps/div, Vertical scale: 100 mV/div).

the NF vs. frequency under various control currents  $I_{gc}$ . The lower cutoff frequency  $f_{\rm L}$  of the reconfigurable DCOC is verified by varying the  $V_{\rm tune}$  from 0 to 1 V after activating this function ( $V_{\rm dcoc} = 0$  V). The obtained  $f_{\rm L}$  at different gains are shown in Fig. 12. The output eye diagram and data jitter of the VGA are characterized by a Tektronix AWG7000 arbitrary waveform generator and a Tektronix MSO71604C oscilloscope. Fig. 13 shows the output eye diagrams under 5 Gb/s 2<sup>23</sup>-1 PRBS signals with different input swings. Both of them have a vertical eye opening larger than 300 mV. Under an input signal level of 20 mV, the peak-to- peak jitter for 5 Gb/s is 39 ps.

Table 1 summarizes and compares the performance of this VGA with other previous reported works [15]–[16], [21]–[24]. The proposed VGA has wider bandwidth,

larger gain and gain control range as compared to the works [21]–[24]. Although the design in [15] and [16] has an excellent data rate than the proposed VGA design, they occupy a relatively large power consumption and chip area. Moreover, this work realizes a reconfigurable DCOC, attaining a tunable lower cutoff frequency range.

#### **IV. CONCLUSION**

A CMOS variable gain amplifier with reconfigurable DCOC for multi-standard applications has been demonstrated in this work. Since a cell-based design method and some bandwidth extension technologies are adopted, a gain control range of 66 dB and a data rate up to 5 Gb/s are achieved simultaneously with a small data jitter of 39 ps. Moreover, the reconfigurable DCOC with tunable  $f_{\rm L}$  from 0 to 300 kHz provides an optimum compromise between BER and SNR requirements of the specified baseband standard. Accordingly, the VGA can be well utilized in high-speed transceiver systems sustaining multiple baseband standards. Meanwhile, its design concepts with non-passive inductor topology can be also easily migrated to more advanced CMOS technologies (e.g., 40 nm or 28 nm) for further improving bandwidth and data rate without robustness concerns and sacrificing other performances.

#### REFERENCES

- Y. Yu, H. Liu, Y. Wu, and K. Kang, "A 54.4–90 GHz low-noise amplifier in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 52, no. 11, pp. 2892–2904, Nov. 2017.

- [2] H. Y. Huang, J. C. Chien, and L. H. Lu, "A 10-Gb/s inductorless CMOS limiting amplifier with third-order interleaving active feedback," *IEEE J. Solid-State Circuits*, vol. 42, no. 5, pp. 1111–1120, May 2007.

- [3] K. Kang et al., "A 60-GHz OOK receiver with an on-chip antenna in 90 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 45, no. 9, pp. 1720–1731, Sep. 2010.

- [4] Y. Wang, B. Afshar, T.-Y. Cheng, V. Gaudet, and A. Niknejad, "A 2.5 mW inductorless wideband VGA with dual feedback DC-offset correction in 90 nm CMOS technology," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2008, pp. 91–94.

- [5] A. A. Emira et al., "Chameleon: A dual-mode 802.11b/Bluetooth receiver system design," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 53, no. 5, pp. 992–1003, May 2006.

- [6] B. Razavi, "Design considerations for direct-conversion receivers," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 44, no. 6, pp. 428–435, Jun. 1997.

- [7] G. Retz *et al.*, "A highly integrated low-power 2.4 GHz transceiver using a direct-conversion diversity receiver in 0.18 μm CMOS for IEEE802.15.4 WPAN," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2009, pp. 414–415.

- [8] H. Okuni, R. Ito, H. Yoshida, and T. Itakura, "A direct conversion receiver with fast-settling DC offset canceller," in *Proc. IEEE 18th Int. Symp. Pers.*, *Indoor Mobile Radio Commun.*, Sep. 2007, pp. 1–5.

- [9] H. Yoshida, H. Tsurumi, and Y. Suzuki, "DC offset canceller in a direct conversion receiver for QPSK signal reception," in *Proc. IEEE 18th Int. Symp. Pers., Indoor Mobile Radio Commun.*, Sep. 1998, pp. 1314–1318.

- [10] H. Darabi et al., "A dual-mode 802.11b/bluetooth radio in 0.35-μm CMOS," IEEE J. Solid-State Circuits, vol. 40, no. 3, pp. 698–706, Mar. 2005.

- [11] T. B. Cho, D. Kang, C.-H. Heng, and B. S. Song, "A 2.4-GHz dual-mode 0.18-µm CMOS transceiver for Bluetooth and 802.11b," *IEEE J. Solid-State Circuits*, vol. 39, no. 11, pp. 1916–1926, Nov. 2004.

- [12] H. A. Alzaher, "A CMOS highly linear digitally programmable active-RC design approach," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 11, pp. 2636–2646, Nov. 2011.

- [13] H. Liu, X. Zhu, C. C. Boon, and X. He, "Cell-based variable-gain amplifiers with accurate dB-linear characteristic in 0.18 μm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 50, no. 2, pp. 586–596, Feb. 2015.

- [15] C. Liu, Y.-P. Yan, W.-L. Goh, Y.-X. Xiong, L.-J. Zhang, and M. Madihian, "A 5-Gb/s automatic gain control amplifier with temperature compensation," *IEEE J. Solid-State Circuits*, vol. 47, no. 6, pp. 1323–1333, Jun. 2012.

- [16] S. Ray and M.-M. Hella, "A 10 Gb/s inductorless AGC amplifier with 40 dB linear variable gain control in 0.13 μm CMOS," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 440–456, Feb. 2016.

- [17] H. D. Lee, K. A. Lee, and S. Hong, "A wideband CMOS variable gain amplifier with an exponential gain control," *IEEE Trans. Microw. Theory Techn.*, vol. 55, no. 6, pp. 1363–1373, Jun. 2007.

[18] S. Galal and B. Razavi, "10-Gb/s limiting amplifier and laser/modulator

- [18] S. Galal and B. Razavi, "10-Gb/s limiting amplifier and laser/modulator driver in 0.18-µm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 38, no. 12, pp. 2138–2146, Dec. 2003.

- [19] R. P. Jindal, "Gigahertz-band high-gain low-noise AGC amplifiers in fine-line NMOS," *IEEE J. Solid-State Circuits*, vol. SSC-22, no. 4, pp. 512–521, Aug. 1987.

- [20] B. Razavi, Design of Analog CMOS Integrated Circuits. Xi'an, China: Xian Jiaotong Univ. Press, 2002.

- [21] Y. Wang, B. Afshar, L. Ye, V. C. Gaudet, and A. M. Niknejad, "Design of a low power, inductorless wideband variable-gain amplifier for high-speed receiver systems," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 4, pp. 696–707, Apr. 2012.

- [22] Y. Wang, C. Hull, G. Murata, and S. Ravid, "A linear-in-dB analog baseband circuit for low power 60 GHz receiver in standard 65 nm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Seattle, WA, USA, Jun. 2013, pp. 225–228.

- [23] T. B. Kumar, K. Ma, K. S. Yeo, and W. Yang, "A 35-mW 30-dB gain control range current mode linear-in-decibel programmable gain amplifier with bandwidth enhancement," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 12, pp. 3465–3475, Dec. 2014.

- [24] T. B. Kumar, K. Ma, and K. S. Yeo, "A 4 GHz 60 dB variable gain amplifier with tunable DC offset cancellation in 65 nm CMOS," *IEEE Microw. Wireless Compon. Lett.*, vol. 25, no. 1, pp. 37–39, Jan. 2015.

- [25] H. Liu et al., "A wideband analog-controlled variable-gain amplifier with dB-linear characteristic for high-frequency applications," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 2, pp. 533–540, Feb. 2016.

**ZHIQING LIU** was born in Jiangxi, China. He received the B.S. degree in electronic engineering from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2011, where he is currently pursuing the Ph.D. degree.

His research interests include CMOS RF and mm-wave integrated circuits design.

**YUNQIU WU** (M'11) received the B.S. and Ph.D. degrees from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2004 and 2009, respectively.

She was with the Technical University of Denmark, Kongens Lyngby, Denmark, from 2012 to 2013. She is currently with UESTC as an Associate Professor. Her current research interests include characterizing the microwave parameters of materials and IC device de-embedding and modeling.

**CHENXI ZHAO** was born in Sichuan, China, in 1981. He received the B.S. and M.S. degrees from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2004 and 2007, respectively, and the Ph.D. from the Pohang University of Science and Technology, Pohang, Gyungbuk, South Korea, in 2014, all in electrical engineering.

From 2008 to 2009, he was with the 10th Insti-

tute of China Electronic and Technological Group, Chengdu, China, where he was involved with the design and research of pulse power amplifier for wireless communication applications. Since 2014, he has been a Lecturer with the School of Electronic Engineering, UESTC.

His major research interests include RF CMOS device modeling, CMOS RF transceivers, and power amplifier design for millimeter wave application.

**JOHANNES BENEDIKT** received the Dipl.Ing. degree in electrical engineering from the University of Ulm, Ulm, Germany, in 1997, and the Ph.D. degree from Cardiff University, Cardiff, U.K., in 2002. During this time, he took on an additional position as a Senior Research Associate with Cardiff University in 2000, where he supervised a research program with Nokia on RFPAs. In 2003, he was appointed a Lecturer with Cardiff University, where he was responsible for further-

ing research in the high-frequency area. His main research focus is on the development of systems for the measurement and engineering of RF current and voltage waveforms and their application in complex PA designs.

**KAI KANG** (M'08) received the B.Eng. degree from Northwestern Polytechnical University, China, in 2002, and the joint Ph.D. degree from the National University of Singapore, Singapore, and Ecole Supérieure D'électricité, France, in 2008.

From 2006 to 2011, he was successively with the Institute of microelectronics, A\*STAR, Singapore, as a Senior Research Engineer, with the National University of Singapore as an Adjunct Assistant Professor, and with Global Foundries as

a Principle Engineer, respectively. Since 2011, he has been a Professor with the University of Electronic Science and Technology of China. His research interests are RF and mm-wave integrated circuits design and modeling of on-chip devices.

He has authored and co-authored over 150 international referred journal and conference papers. He was a co-recipient of several best paper or best student paper awards in IEEE conference, including the Silkroad Award in ISSCC 2018. He serves as the Chapter Chair of the IEEE Solid State Circuits Society Chengdu Chapter.