Received August 30, 2017, accepted September 28, 2017, date of publication October 4, 2017, date of current version November 7, 2017. *Digital Object Identifier* 10.1109/ACCESS.2017.2759164

# A Design Strategy for AM/PM Compensation in GaN Doherty Power Amplifiers

VITTORIO CAMARCHIA<sup>1</sup>, (Senior Member, IEEE), PAOLO COLANTONIO<sup>2</sup>, (Member, IEEE), FRANCO GIANNINI<sup>2</sup>, ROCCO GIOFRÈ<sup>2</sup>, (Senior Member, IEEE), TAO JIANG<sup>1</sup>, MARCO PIROLA<sup>1</sup>, (Member, IEEE), ROBERTO QUAGLIA<sup>®3</sup>, (Member, IEEE), AND CHIARA RAMELLA<sup>1</sup>

<sup>1</sup>Department of Electronics and Telecommunications, Politecnico di Torino, 10129 Torino, Italy <sup>2</sup>Electronic Engineering Department, University of Roma Tor Vergata, 00133 Roma, Italy <sup>3</sup>Centre for High Frequency Engineering, Cardiff University, Cardiff CF10 3XQ, U.K.

Corresponding author: Roberto Quaglia (quagliar@cardiff.ac.uk)

**ABSTRACT** This paper presents the theoretical analysis of phase distortion (AM/PM) mechanisms in Gallium Nitride (GaN) Doherty power amplifiers (DPAs) and a novel approach to optimize the tradeoff between linearity and efficiency. In particular, it is demonstrated how it is possible to mitigate the AM/PM by designing a suitable mismatch at the input of the active devices, based on the identification of constant AM/PM and gain contour circles. The proposed theory is experimentally confirmed by source- and load-pull measurements and further validated through the design and realization of a 7 GHz 10 W DPA based on GaN monolithic technology.

**INDEX TERMS** Doherty power amplifiers, gallium nitride, linearity, electronically tunable networks.

#### **I. INTRODUCTION**

Power amplifiers (PAs) are the most critical components in microwave radios, since their linearity strongly affects the quality of the transmitted signal, and their power consumption strongly influences the overall system power budget [1], [2].

To cope with the users' demand for increasingly higher data-rates, modern wireless communication systems adopt complex digital modulation schemes that pose severe linearity constraints on the PA forcing the operation at an average output power that is far from the maximum, i.e. in back-off (BO) condition. This in turns poses challenging requirements on efficiency that should be maintained as high as possible also in BO, in contrast with the usually poor BO efficiency of classical class-AB PAs. To overcome this limitation, the Doherty Power Amplifier (DPA) architecture has emerged as the most suitable solution to achieve high BO efficiency [3]–[6]. Since fabricated DPAs are rather non-linear [7]-[10], they are typically employed in conjunction with digital predistortion (DPD), in order to fulfill linearity constraints [11]. In particular, while amplitude distortion (AM/AM) can be effectively modelled with static models [12] and thus compensated by simple memoryless DPDs (e.g. look-up-table), phase distortion (AM/PM) is a major issue of DPA [10] and leads to the adoption of complex and powerful DPDs.

Such combination of DPD and DPA techniques proved to effectively yield notable BO efficiency enhancement with respect to class-AB solutions in the base-station market, where the required power levels are in the order of hundreds of watts. However, a very different scenario occurs instead in point-to-point microwave links, where power levels are usually limited to tens of watts. In this framework, the adoption of complex DPD-based linearizers could be not convenient in terms of overall power budget and, as a consequence, the effective advantages of DPAs with respect to class-AB PAs are still questionable [13].

The development of efficient DPAs topologies with minimal distortions, allowing for minimum-complexity DPD schemes to be employed, is therefore crucial to enable the widespread adoption of the DPA architecture in this field of applications. Moreover, the need of lowdistortion DPAs is expected to be further emphasized by the introduction of the 5G mobile standard, due to the foreseen adoption of antenna arrays based on a large number of low power integrated PAs working at carrier frequencies in the microwave and millimetre-wave range [14].

This work proposes a novel design approach to optimize the trade-off between power gain and linearity in Gallium Nitride (GaN [15]) DPAs. The theoretical analysis, based on a simplified representation of the DPA architecture, led to a novel formulation for the amplitude to phase modulation distortion (AM/PM) generation mechanism, underlying its relationship with the input matching condition of the devices. Based on this result, constant AM/PM contours can be derived and used, in conjunction with constant gain ones, to find an optimum mismatching condition for AM/PM reduction. The proposed approach is experimentally validated with source- and load-pull measurements on a GaN device, and tested by the design and characterization of a demonstrator, a GaN Microwave Monolithic Integrated Circuit (MMIC) DPA, first presented by Giofrè et al. [16]. The MMIC is equipped with electronically controlled switches, which also provide the possibility to modify the input matching conditions of the devices and thus to verify the effect of mismatch on the amplifier behavior. Both MMICs are designed at 7 GHz targeting 10W output power, in accordance with microwave backhaul specifications [17]. They include only one stage: this choice, even if yielding to low power gain, was made to avoid any possible cross-effect that a driver stage may introduce, affecting the validity of the results in terms of theory verification.

#### **II. PHASE DISTORTION IN GaN DPAs**

Amplitude (AM/AM) and phase distortion (AM/PM) are two key parameters, defining the linearity of a power amplifier. While in class-AB PAs both AM/AM and AM/PM can be minimized simultaneously, for example by proper choice of bias point [9], in Doherty PAs this becomes difficult, or even impossible, due to the effect of load modulation [10]. As a consequence, in DPAs, AM/PM represents the major issue from the linearization point of view, since, contrary to AM/AM, it requires non-static DPD schemes [18].

#### A. AM/PM ANALYSIS

The proposed approach is based on some results available in literature [7]–[10], [19]–[23], of which a brief compendium is reported in the following for sake of clarity. Then, a novel formulation, underlying the relationship between AM/PM and the active devices' input matching conditions, is reported. Finally, based on this theoretical analysis, an effective design tool to trade-off between AM/PM and gain is introduced.

The theoretical analysis relies on a simplified device model similar to that presented in [8] and [10]. The simplifying assumptions follow the results obtained in [21], where, through a rigorous Volterra-series-based analysis, it was demonstrated that the sources of AM/PM distortion in a device can be mainly ascribed to the device intrinsic non-linear capacitors and the variation of the gain (i.e. of the transconductance  $g_m$ ) from expansion to compression as input power increases.

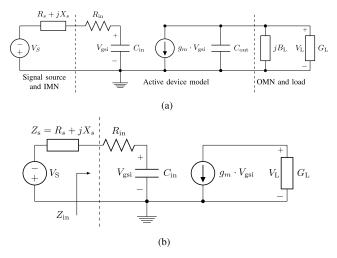

The simplified PA scheme of Fig. 1(a) can be adopted for both the Main and the Auxiliary amplifiers of a DPA.

**FIGURE 1.** Power amplifier model: (a) first circuit, with Miller approximation applied and (b) final circuit.

The active device is modelled through a voltage controlled current source  $g_{\rm m} \cdot V_{\rm gsi}$ , while an input resistance  $R_{\rm in}$  is inserted to account for both the device resistive parasitics and the losses introduced by the stabilization network. The device intrinsic capacitances are represented with an input and output equivalent capacitances,  $C_{\rm in}$  and  $C_{\rm out}$ , obtained according to Miller's approximation as [8], [24]:

$$C_{\rm in} = C_{\rm gs} + C_{\rm gd} \left( 1 + \frac{g_{\rm m}}{G_{\rm L}} \right) \tag{1}$$

$$C_{\rm out} = C_{\rm ds} + C_{\rm gd} \left( 1 + \frac{G_{\rm L}}{g_{\rm m}} \right) \tag{2}$$

where  $G_{\rm L}$  is the equivalent load conductance, and  $C_{\rm GS}$ ,  $C_{\rm DS}$ , and  $C_{\rm GD}$  are the intrinsic device capacitances. The output matching network (OMN) is assumed to be lossless and is represented by a susceptance  $B_{\rm L}$  in parallel to the load  $G_{\rm L}$ . The input matching network (IMN) is modeled by a complex impedance  $Z_{\rm S} = (R_{\rm S} + jX_{\rm S})$  in series with the input RF source  $V_{\rm S}$ .

A further model approximation can be achieved by considering linear capacitances and transconductance. This assumption allows to directly figure out the link between causes and effects in the AM/PM mechanisms, with negligible loss in accuracy with respect to a complete non-linear model, as demonstrated in [7] and [25]. Moreover, at the operating frequency, and under the linear approximation assumption, it is possible to find the proper value of  $B_L$  that compensates the reactive behavior of  $C_{out}$ . This assumption is supported by the fact that the  $G_L/g_m$  ratio is much lower than unity in the frequency range where device acts as an amplifier [8]. The resulting simplified model to be considered is shown in Fig. 1(b).

By applying Kirchhoff's voltage law (KVL) at the circuit in Fig. 1(b) the phase of the output voltage  $V_L$  (with respect to the input signal  $V_{\rm S}$ ) is obtained as:

Any element of (3) that varies with the applied input power generates AM/PM distortion. In particular, it is possible to classify the sources of phase distortion in two categories:

- 1) *Technological*: These contributions are related to the active device physics, and thus common in all kind of current-mode amplifiers and mainly related to the variation of  $g_{\rm m}$ ,  $C_{\rm gs}$ , and  $C_{\rm gd}$  with the input power level.

- 2) *Behavioral*: these contributions are related to the particular PA architecture considered. In the specific case of the DPA, the load  $G_L$  is not constant, but modulated as a function of input power by the interaction between the main and auxiliary currents summing at the common node [3]. In particular, the load of the Main device swings from  $G_{Lopt}/2$  to  $G_{Lopt}$ , while that of the Auxiliary device from infinity to  $G_{Lopt,Aux}$ . Therefore, in contrast with what happens in classical current mode class AB PA, a DPA would be still affected by a remarkable AM/PM, even if the adopted active devices were devoid of nonlinearities.

In [8] and [10], it was shown that the AM/PM of a DPA can be studied considering the AM/PM of the Main device alone.

Furthermore, according to the proposed model, the phase of the output voltage given by (3) shows an increasing monotonic behavior with respect to the load conductance  $G_L$ , that is in agreement with what experimentally shown in [20].

On these bases, the maximum AM/PM variation in a DPA can be evaluated as the difference between the phase of the output voltage at saturation and that in small-signal condition:

$$AM/PM = \angle V_{\rm L}|_{G_{\rm L}=G_{\rm Lopt}} - \angle V_{\rm L}|_{G_{\rm L}=G_{\rm Lopt}/2}$$

(4)

which is function of  $Z_S$  (see (3)), i.e., of the input matching network.

#### B. AM/PM VS. INPUT MATCHING FORMULATION

Referring to Fig. 1(b), the input impedance of the Main device is given by:

$$Z_{\rm in}(G_{\rm L}) = R_{\rm in} - j \frac{G_{\rm L}}{\omega[(C_{\rm gs} + C_{\rm gd})G_{\rm L} + C_{\rm gd}g_{\rm m}]} \qquad (5)$$

In a DPA such input impedance varies as the output conductance  $G_L$  is actively modulated by the Auxiliary device. Therefore, when designing the input matching network, it is possible to assure a conjugate matching condition only for a

22246

predefined value of  $G_L$ , i.e., only for a certain level of modulation. Assuming that the device is matched at saturation, that is when  $G_L = G_{Lopt}$ , then the impedance  $Z_S$  required to fulfill the complex conjugate matching condition is:

$$Z_{\rm S}|_{\rm match} = R_{\rm in} + j \frac{G_{\rm Lopt}}{\omega[(C_{\rm gs} + C_{\rm gd})G_{\rm Lopt} + C_{\rm gd}g_{\rm m}]}$$

(6)

Substituting this value into (3) and then evaluating (4), the following equation can be obtained to describe the maximum AM/PM variation of a DPA:

AM/PM|match

$$= \operatorname{atan}\left(\frac{\frac{G_{\text{Lopt}}}{(C_{\text{gs}}+C_{\text{gd}})G_{\text{Lopt}}+C_{\text{gd}}g_{\text{m}}} - \frac{G_{\text{Lopt}}}{(C_{\text{gs}}+C_{\text{gd}})G_{\text{Lopt}}+2C_{\text{gd}}g_{\text{m}}}}{2R_{\text{in}}\omega}\right)$$

$$= \operatorname{atan}\left(\frac{\frac{C_{\text{gd}}g_{\text{m}}G_{\text{Lopt}}}{4R_{\text{in}}\omega}}{\frac{(C_{\text{gs}}+C_{\text{gd}})^2G_{\text{Lopt}}^2}{2} + \frac{3}{2}(C_{\text{gs}}+C_{\text{gd}})C_{\text{gd}}g_{\text{m}}G_{\text{Lopt}}+C_{\text{gd}}^2g_{\text{m}}^2}}\right) (7)$$

Now, if a certain amount of mismatch with respect to the case of (6) is tolerated, two more degrees of freedom to improve the AM/PM distortion are gained. Introducing the additive quantity  $Z_{\rm m} = R_{\rm m} + jX_{\rm m}$  to represent the amount of mismatch,  $Z_{\rm S}$  becomes

$$R_{\rm S} = R_{\rm in} + R_{\rm m}$$

$$X_{\rm S} = \frac{G_{\rm Lopt}}{\omega[(C_{\rm gs} + C_{\rm gd})G_{\rm Lopt} + C_{\rm gd}g_{\rm m}]} + X_{\rm m} \qquad (8)$$

Then, by using these values in (3) and (4) and after some algebra rearrangement, the maximum AM/PM variation accounting for the presence of  $Z_m$  (i.e., in the mismatch case) turns out to be:

$$AM/PM|_{\text{mismatch}} = \operatorname{atan}\left(\frac{2R_{\text{in}}(2R_{\text{in}}+R_{\text{m}})\tan\Phi}{(2R_{\text{in}}+R_{\text{m}})^2 + X_{\text{m}}(X_{\text{m}}+2R_{\text{in}}\tan\Phi)}\right) \quad (9)$$

where  $\Phi = AM/PM|_{\text{match}}$  is the AM/PM value resulting from (7), when the input of the Main device is matched at saturation.

The quantity resulting from (9) can be either higher or lower than  $\Phi$ : this AM/PM formulation highlights the existing link between phase distortion and input matching condition of the Main device. It also allows to evaluate the achievable AM/PM improvement by accepting some mismatch (i.e., gain reduction).

## C. EXPERIMENTAL VALIDATION OF THE PROPOSED FORMULATION

To validate the theoretical analysis, a dedicated source-pull measurement campaign was carried out. A single  $8 \times 150 \,\mu$ m GaN HEMT device from United Monolithic Semiconductors (more details in Section III), was experimentally characterized emulating the loading condition and hence the behavior of the Main stage of a DPA [9]. To this aim, two source-pull characterizations of the device were performed (at 7 GHz): the first with constant  $G_{\text{Lopt}}/2$  load and

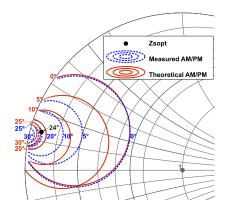

#### the second with constant $G_{Lopt}$ load. In both cases, the phase of the output voltage with respect to the phase of the source was measured and the maximum AM/PM distortion was evaluated according to (4). The values of the device smallsignal model, $R_{in} = 1.9 \Omega$ , $C_{gs} = 2.1 \text{ pF}$ , $C_{gd} = 0.1 \text{ pF}$ and $g_{\rm m} = 220 \,{\rm mS}$ , extracted from Scattering parameter measurements, were then used to calculate the theoretical AM/PM distortion. The real part of the optimum output conductance is $G_{\text{Lopt}} = 22 \text{ mS}$ and, using (7), the AM/PM when the device is matched at the input to this value is 24°. In Fig. 2, the comparison between the measured and calculated constant AM/PM contours for different input impedances is shown: despite the simplifications adopted to extract the mathematical model, the agreement between the theoretical and the experimental curves is remarkable, thus indicating that the proposed theoretical approach is able to well approximate the actual evolution of the AM/PM in a DPA either with or without mismatch.

FIGURE 2. Comparison between measured and theoretical constant AM/PM curves for different input matching conditions.

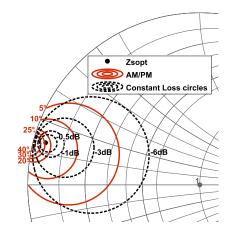

#### D. AM/PM vs. MATCHING CONTOURS

Fig. 3 reports the same theoretical constant AM/PM contours of Fig. 2, together with the constant mismatch (i.e., constant insertion loss *IL*) contour curves, calculated as

$$IL = 10 \log_{10} \left( 1 - \left| \frac{Z_{\rm S} - Z_{\rm Sopt}}{Z_{\rm S} + Z_{\rm Sopt}^*} \right|^2 \right)$$

(10)

*IL* quantifies the gain reduction resulting from mismatching the input impedance with respect to the matched case. As can be seen from Fig. 3, the proposed AM/PM formulation represents an effective design tool to identify the input mismatch that provides an optimum trade-off between AM/PM reduction and gain. For example, by accepting a gain reduction of 0.5 dB or 1 dB, the AM/PM can be reduced of 7° or 10°, respectively, while with 3 dB loss the AM/PM can be lowered down to  $7.5^{\circ}$ .

#### E. MATCHING IMBALANCE COMPENSATION

The introduction of some input mismatch in the Main path, if not properly compensated, leads to some drawback onto

FIGURE 3. Constant AM/PM and mismatch contour curves. These contours can be used in the design phase to optimize the trade off between AM/PM and gain.

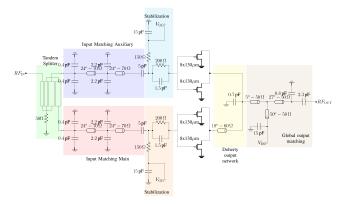

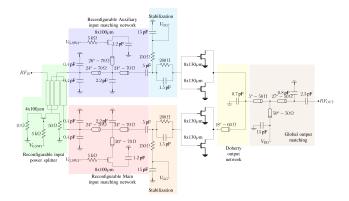

FIGURE 4. Electrical scheme of the DPA-F [13].

the other DPA features. In particular, it can cause either a worse load modulation, due to an early turning-on of the Auxiliary amplifier, or a phase imbalance between Main and Auxiliary paths. Both effects can be prevented by adding the same amount of mismatch at the input of the Auxiliary device. Therefore, once selected the input impedance for the best trade-off between AM/PM distortion and gain reduction, also the Auxiliary input matching network must be carefully optimized to keep the proper phase relation between the Main and Auxiliary output currents.

#### **III. DPA DEMONSTRATORS**

In order to validate the theoretical results at MMIC level, two GaN MMIC DPA modules based on the same technology were designed and characterized. The first (in the following referred as DPA-F), is a standard AB-C DPA, first presented by Giofrè *et al.* [13]. The second (referred as DPA-R), presented in [16], is a modified version of the same DPA, that includes electronically reconfigurable elements (HEMT switches) in the input network. In the following, the major design features of both DPAs are summarized.

The electrical schemes of the two modules are reported in Fig. 4 and Fig. 5. For both DPAs the 0.25  $\mu$ m gate-length GaN

FIGURE 5. Electrical scheme of the DPA-R [16].

FIGURE 6. Reconfigurable IMN.

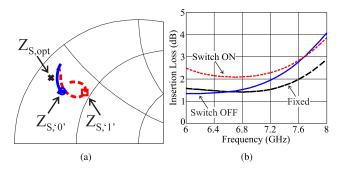

**FIGURE 7.** Reconfigurable IMN: (a) simulated impedance  $Z_S$  (see Fig. 6) and (b) simulated insertion loss (IL) in the OFF (blue) and ON (red dashed) state of the switch. In (b) the IMN IL of DPA-F is also reported (black long-dash), demonstrating that the switch does not introduce additional losses.

on SiC HEMT process (GH25-10) [26] from United Monolithic Semiconductors (UMS) was adopted, targeting a center frequency of 7 GHz and an output power of 10 W (40 dBm). Being the focus of this work the experimental verification of the presented theory, only the power stage has been designed, with a resulting low gain (7 dB). Accounting for the losses introduced by the output combiner, and for the available foundry models, the basic device selected was a  $8 \times 130 \,\mu$ m HEMT, showing at 7 GHz an output power of  $\sim 3$  W in class-AB bias condition ( $V_{\text{DD}} = 25$  V,  $I_{\text{D}} = 33$  mA

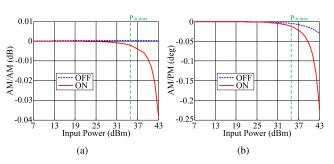

**FIGURE 8.** Simulated AM/AM (a) and AM/PM (b) of the reconfigurable IMN in the OFF (blue) and ON (red dashed) state of the switch.

FIGURE 9. Microscope picture of the implemented DPAs: (a) DPA-F and (b) DPA-R. Chip size is 3 mm  $\times$  3 mm for both MMICs.

for  $V_{GG} = -3.2 \text{ V}$ ). Thus, to achieve the required output power, two of these devices are combined in a  $2 \times 8 \times 130 \,\mu\text{m}$ macro-cell, adopted to implement both the Main and the Auxiliary stages, for a total DPA active periphery of  $4 \times 8 \times 130 \,\mu\text{m} = 4.16 \,\text{mm}$ .

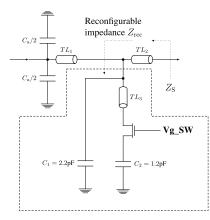

Concerning DPA-R, the reconfigurable elements adopted in the input networks are GaN HEMT switches, directly integrated in the same monolithic circuit of the DPA. Both the Main and Auxiliary IMNs can be independently modified by acting on two switches according to the structure shown

**FIGURE 10.** CW measurement results at 7 GHz. Reconfigurable DPA with no mismatch (black and squares) and fixed DPA (green and diamonds).

in Fig. 6: the two shunting capacitances of 2.2 pF, already present in DPA-F (see Fig. 4), are replaced with the structure reported in the dotted box in Fig. 6, implementing a reconfigurable capacitor.

When the switch is open (OFF state), the impedance  $Z_{\text{rec}}$  is given by the parallel of the fixed capacitance  $C_1$  and the equivalent capacitance of the open-terminated transmission line  $TL_3$ . When the switch is closed (ON state), the equivalent capacitance changes due to the loading effect of  $C_2$ .

The adoption of such a variable capacitor allows to mismatch independently the Main and/or the Auxiliary devices of roughly 1 dB, by changing the impedance seen by the devices ( $Z_S$  in Fig. 6), as shown in Fig. 7. From the device point of view, when the switch is OFF, the matching network synthesizes a gate termination ( $Z_S$ ,  $0^{\circ}$ ) close to optimum impedance  $Z_{S,opt}$ . Conversely, when the switch is turned ON, the synthesized termination ( $Z_S$ ,  $1^{\circ}$ ) is shifted toward the centre of the Smith Chart, hence mismatching the corresponding stage.

For the switch implementation, an  $8 \times 100 \,\mu$ m HEMT was selected, while the ON and OFF states are set providing 0 V and -25 V at the gate terminal, respectively. The device size and bias were properly selected to minimize distortion and losses introduced by the input network, which results negligible for the whole input power range, as reported in Fig. 8.

#### **IV. EXPERIMENTAL RESULTS**

The fabricated MMICs, shown in Fig. 9, were characterized with single-tone CW stimulus at 7 GHz, in order to verify the proposed design method and the agreement between measured and simulated results, the latter obtained exploiting the device foundry models. In all tests, the drain bias of the Main amplifier is 25 V, 80 mA, while that of the Auxiliary is 25 V, with gate voltage of -6.5 V.

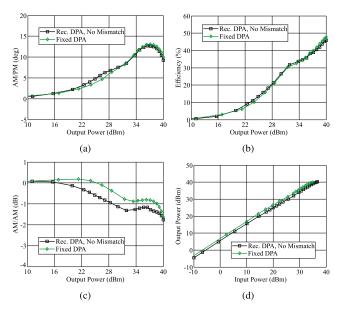

Fig. 10 compares the measured AM/PM and efficiency vs. output power for both DPA-F and DPA-R, the latter in the matched configuration (all switches OFF, same conditions of DPA-F). The two MMICs show very similar performance, confirming that the introduction of the switches enables to test the proposed theory with a negligible degradation of performance.

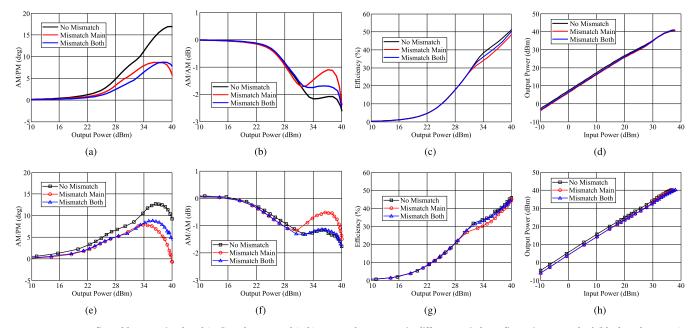

FIGURE 11. Reconfigurable DPA. Simulated (a-d) and measured (e-h) CW results at 7 GHz in different switch configurations: matched (black and squares), main mismatched (red and circles), main and auxiliary mismatched (blue and triangles).

Fig. 11 reports a summary of the CW results (measured and simulated) obtained on DPA-R in the three switch configurations of interest: 1) with no mismatch, 2) with 1 dB of mismatch introduced on the Main PA only (Main IMN switch ON, Auxiliary IMN switch OFF), and 3) with the same amount of mismatch on both Main and Auxiliary PAs (both IMN switches ON). A third switch, not discussed in this paper, controls the input splitting and it is in OFF state in these measurements, corresponding to equal splitting. Moreover, the case with mismatch on the Auxiliary only is also not discussed, because it is not related to a clear theoretical advantage in terms of linearity. More details on these other states can be found in [16].

The agreement between measurements and simulations is rather good, confirming the proposed theoretical approach relating input mismatch to DPA performance.

Phase distortion, reported in Fig. 11(a) and Fig. 11(e), is effectively reduced by input mismatch: the measured maximum value with no mismatch is around 13°, while it is reduced to 8° by introducing mismatch in the input path of the Main stage, corresponding to a relative AM/PM reduction of more than 30%. However, the mismatch applied to the Main PA only, significantly changes the AM/AM and reduces the back-off efficiency of around 4%-points, as shown in Fig. 11(b, f) and Fig. 11(c, g), respectively. Mismatching, instead, both the Main and Auxiliary PA leads to AM/AM and efficiency levels very similar to the condition without any mismatch, while AM/PM reduction is still presents, as it is 9° (see Fig. 11(e)). Evaluating the effect of this AM/PM reduction in terms of modulated signal measurement is a difficult task, because other effects comes into play especially with wideband modulations: further work is being done to address this aspect.

Finally, Fig. 11(d, h) show the output power vs. input power: in all configurations, the 10 W output power target is achieved, while the gain decreases, as expected, of around 1.5 dB when mismatch is applied.

#### **V. CONCLUSIONS**

A novel theoretical formulation of the AM/PM distortion in GaN DPAs has been presented, showing its relation with the input matching condition of the devices. Based on the proposed theoretical analysis, a design strategy for AM/PM reduction has been introduced and demonstrated by source-pull measurements on a real GaN device. To further confirm the theoretical results, two 7 GHz 10 W GaN MMIC DPA were fabricated and characterized: a switchbased reconfigurable module, to assess the effect of introducing input mismatch on the Main and Auxiliary stages, and an equivalent standard module to prove that the impact of the switches on DPA performances is negligible. CW characterization results demonstrate the effectiveness of the proposed strategy in improving the DPA linearity, significantly reducing the AM/PM distortion, and thus relaxing predistortion requirements.

#### ACKNOWLEDGMENT

Dr. L. Piazzon is warmly acknowledged for the fruitful discussion and helpful contribution. Ericsson AB is also acknowledged for founding the present research.

#### REFERENCES

- F. H. Raab *et al.*, "Power amplifiers and transmitters for RF and microwave," *IEEE Trans. Microw. Theory Techn.*, vol. 50, no. 3, pp. 814–826, Mar. 2002.

- [2] S. Cripps, RF Power Amplifiers for Wireless Communications (Artech House Microwave Library). Norwood, MA, USA: Artech House, 2006.

- [3] V. Camarchia, M. Pirola, R. Quaglia, S. Jee, Y. Cho, and B. Kim, "The Doherty power amplifier: Review of recent solutions and trends," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 2, pp. 559–571, Feb. 2015.

- [4] A. Grebennikov and S. Bulja, "High-efficiency Doherty power amplifiers: Historical aspect and modern trends," *Proc. IEEE*, vol. 100, no. 12, pp. 3190–3219, Dec. 2012.

- [5] B. Kim, J. Kim, I. Kim, and J. Cha, "The Doherty power amplifier," *IEEE Microw. Mag.*, vol. 7, no. 5, pp. 42–50, Oct. 2006.

- [6] W. H. Doherty, "A new high efficiency power amplifier for modulated waves," *Proc. Inst. Radio Eng.*, vol. 24, no. 9, pp. 1163–1182, Sep. 1936.

- [7] L. Piazzon, R. Giofrè, P. Colantonio, and F. Giannini, "Investigation of the AM/PM distortion in Doherty power amplifiers," in *Proc. IEEE Topical Conf. Power Amplif. Wireless Radio Appl. (PAWR)*, Jan. 2014, pp. 7–9.

- [8] L. Piazzon *et al.*, "Effect of load modulation on phase distortion in Doherty power amplifiers," *IEEE Microw. Wireless Compon. Lett.*, vol. 24, no. 7, pp. 505–507, Jul. 2014.

- [9] R. Quaglia *et al.*, "Experimental investigation of bias current and load modulation effects in phase distortion of GaN HEMTs," *Electron. Lett.*, vol. 50, no. 10, pp. 773–775, May 2014.

- [10] L. C. Nunes, P. M. Cabral, and J. C. Pedro, "AM/PM distortion in GaN Doherty power amplifiers," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2014, pp. 1–4.

- [11] C. F. Campbell, K. Tran, M.-Y. Kao, and S. Nayak, "A K-band 5W Doherty amplifier MMIC utilizing 0.15 μm GaN on SiC HEMT technology," in *Proc. IEEE Compound Semiconductor Integr. Circuit Symp. (CSICS)*, Oct. 2012, pp. 1–4.

- [12] M. Schetzen, "Nonlinear system modeling based on the Wiener theory," *Proc. IEEE*, vol. 69, no. 12, pp. 1557–1573, Dec. 1981.

- [13] R. Giofrè *et al.*, "A comprehensive comparison between GaN MMIC Doherty and combined class-AB power amplifiers for microwave radio links," *Int. J. Microw. Wireless Technol.*, vol. 8, nos. 4–5, pp. 673–681, Jun. 2016.

- [14] S. Boumaiza and H. Golestaneh, "Joint circuit-level and digital predistortion strategies for enhancing the linearity-efficiency tradeoff of Doherty power amplifiers," in *IEEE MTT-S Int. Microw. Symp. Dig.*, May 2016, pp. 1–3.

- [15] R. S. Pengelly, S. M. Wood, J. W. Milligan, S. T. Sheppard, and W. L. Pribble, "A review of GaN on SiC high electron-mobility power transistors and MMICs," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 6, pp. 1764–1783, Jun. 2012.

- [16] R. Giofrè *et al.*, "GaN-MMIC Doherty power amplifier with integrated reconfigurable input network for microwave backhaul applications," in *IEEE MTT-S Int. Microw. Symp. Dig.*, May 2015, pp. 1–3.

- [17] V. Camarchia, M. Pirola, and R. Quaglia, *Electronics for Microwave Backhaul*. Norwood, MA, USA: Artech House, 2016.

- [18] H. Karkhane, A. Ghorbani, and H. R. A. Davar, "Quantifying and cancellation memory effect in high power amplifier for OFDM systems," *Prog. Electromagn. Res. C*, vol. 3, pp. 183–194, Mar. 2008.

- [19] L. C. Nunes, P. M. Cabral, and J. C. Pedro, "A physical model of power amplifiers AM/AM and AM/PM distortions and their internal relationship," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2013, pp. 1–4.

- [20] L. C. Nunes, P. M. Cabral, and J. C. Pedro, "AM/AM and AM/PM distortion generation mechanisms in Si LDMOS and GaN HEMT based RF power amplifiers," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 4, pp. 799–809, Apr. 2014.

- [21] J. Aikio and T. Rahkonen, "A comprehensive analysis of AM–AM and AM–PM conversion in an LDMOS RF power amplifier," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 2, pp. 262–270, Feb. 2009.

### **IEEE**Access

- [22] T. Rahkonen, S. Hietakangas, and J. Aikio, "AM-PM distortion caused by transistor's signal-dependent input impedance," in *Proc. Eur. Conf. Circuit Theory Design (ECCTD)*, Aug. 2011, pp. 833–836.

- [23] W. Hallberg, M. Özen, D. Gustafsson, K. Buisman, and C. Fager, "A Doherty power amplifier design method for improved efficiency and linearity," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 12, pp. 4491–4504, Dec. 2016.

- [24] A. S. Sedra and K. C. Smith, *Microelectronic Circuits*. London, U.K.: Oxford Univ. Press, 2009.

- [25] P. Colantonio et al., "Improved phase linearity in source field plate AlGaN/GaN HEMTs," in Proc. 9th Eur. Microw. Integr. Circuit Conf. (EuMIC), Oct. 2014, pp. 349–352.

- [26] D. Floriot et al., "GH25–10: New qualified power GaN HEMT process from technology to product overview," in Proc. 9th Eur. Microw. Integr. Circuit Conf. (EuMIC), Oct. 2014, pp. 225–228.

VITTORIO CAMARCHIA (S'01–M'04–SM'14) received the Laurea degree in electronic engineering and the Ph.D. degree in electronic and communications engineering from the Politecnico di Torino, Turin, Italy, in 2000 and 2003, respectively. From 2001 to 2003, he was a Visiting Researcher with the Electrical and Computer Engineering Department, Boston University, Boston, MA, USA. He is currently an Assistant Professor with the Department of Electronics and Telecom-

munications, Politecnico di Torino. His research is focused on RF device modeling, simulation, and characterization, both linear and nonlinear and power amplifier design. He was a recipient of the 2002 Young Graduated Research Fellowship presented by the Gallium Arsenide Application Symposium Association.

**PAOLO COLANTONIO** was born in Roma, Italy, in 1969. He received the Electronic Engineering degree and the Ph.D. degree in microelectronics and telecommunications from the University of Roma Tor Vergata, Italy, in 1994 and 2000, respectively. In 1999, he became a Research Assistant with the University of Roma Tor Vergata, where, since 2002, he has been a Professor of Microwave Electronics. He authored or co-authored over 200 scientific papers. He *Efficiency RE and Microwave Solid State Power*

authored the book *High Efficiency RF and Microwave Solid State Power Amplifiers* (Wiley, 2009). His main research activities are in the field of nonlinear microwave circuit design methodologies, nonlinear analysis techniques, and the modeling of microwave active devices.

**FRANCO GIANNINI** was born in Galatina, Italy, in 1944. He received the Electronics Engineering (*summa cum laude*) degree from the University of Roma La Sapienza Rome, Italy, in 1968, and the Doctor Honoris Causa degree from the Warsaw University of Technology (WUT), Warsaw, Poland, in 2008. Since 1980, he has been a Full Professor of Applied Electronics with the University of Rome Tor Vergata, Rome, Italy. Since 2001, he has been an Honorary Professor

with WUT. He has authored or co-authored over 430 scientific papers. He has been involved with problems concerning modeling, characterization, and the design methodologies of linear and nonlinear active microwave components, circuits, and subsystems, including monolithic microwave integrated circuits. He is a consultant for various national and international industrial and governmental organizations, including the International Telecommunication Union and the European Union. He is a member of the Board of Directors of the Italian Space Agency. He is the President of the GAAS Association. He has also been a member of numerous committees of international scientific conferences.

**ROCCO GIOFRÈ** received the Electronic Engineering (*summa cum laude*) degree (M.S. Eng.) and the Ph.D. degree in space systems and technologies from the University of Roma Tor Vergata, in 2004 and 2009, respectively. He is currently an Assistant Professor with the University of Roma Tor Vergata. He has authored or co-authored over 120 scientific papers. His research interests include RF power amplifier theory, design and test, linearization, and efficiency improving tech-

niques. He was a recipient of the 2005 Young Graduated Research Fellowship presented by the GAAS Association and the Best Paper Award at the Second EuMIC Conference in 2007.

**TAO JIANG** was born in Anhui, China, in 1989. He received the B.S. and M.S. degrees in electronic engineering and the Ph.D. degree from the Politecnico di Torino, Turin, Italy, in 2010, 2012, and 2016, respectively. His current research interests concern the FPGA-based digital pre-distortion of power amplifiers.

**MARCO PIROLA** (M'97) was born in Velezzo Lomellina, Italy, in 1963. He received the Laurea degree in electronic engineering and the Ph.D. degree from the Politecnico di Torino, Italy, in 1987 and 1992, respectively. In 1992 and 1994, he was a Visiting Researcher with the Hewlett Packard Microwave Technology Division, Santa Rosa, CA, USA. Since 1992, he has been with the Electronics Department, Politecnico di Torino, first as a Researcher and, since 2000, as an Asso-

ciate Professor, where his research concerns the simulation, modeling, and measurements of microwave devices and systems.

**ROBERTO QUAGLIA** was born in Casale Monferrato, Italy, in 1984. He received the degree (*cum laude*) in electronic engineering and the Ph.D. degree in electronic devices from the Politecnico di Torino, Turin, Italy, in 2008 and 2012, respectively. He is currently a Lecturer with Cardiff University. His research interests concern the design, modeling, and predistortion of high efficiency MMIC power amplifiers. He was a recipient of the European Union Marie Skłodowska Curie Fellowship

and the 2009 Young Graduated Research Fellowship presented by the GAAS Association.

**CHIARA RAMELLA** was born in Biella, Italy, in 1985. She received the M.S degree in electronic engineering and the Ph.D. degree in electronic devices from the Politecnico di Torino, in 2009 and 2013, respectively. She is currently a Research Assistant with the Politecnico di Torino. Her research activities spread from low-noise analog electronic design to RF/microwave design and measurements.