Received October 10, 2013, accepted November 26, 2013, date of publication December 20, 2013, date of current version January 7, 2014.

Digital Object Identifier 10.1109/ACCESS.2013.2295764

# A Contract-Based Methodology for Aircraft Electric Power System Design

PIERLUIGI NUZZO<sup>1</sup>, HUAN XU<sup>2</sup>, NECMIYE OZAY<sup>3</sup>, JOHN B. FINN<sup>1</sup>, ALBERTO L. SANGIOVANNI-VINCENTELLI<sup>1</sup>, RICHARD M. MURRAY<sup>4</sup>, ALEXANDRE DONZÉ<sup>1</sup>, AND SANJIT A. SESHIA<sup>1</sup>

<sup>1</sup>Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, Berkeley, CA 94720, USA

Corresponding author: P. Nuzzo (nuzzo@eecs.berkeley.edu)

This work was supported in part by IBM and United Technologies Corporation (UTC) via the iCyPhy consortium, and in part by the TerraSwarm Research Center, one of six centers supported by the STARnet phase of the Focus Center Research Program, a Semiconductor Research Corporation Program sponsored by MARCO and DARPA.

**ABSTRACT** In an aircraft electric power system, one or more supervisory control units actuate a set of electromechanical switches to dynamically distribute power from generators to loads, while satisfying safety, reliability, and real-time performance requirements. To reduce expensive redesign steps, this control problem is generally addressed by minor incremental changes on top of consolidated solutions. A more systematic approach is hindered by a lack of rigorous design methodologies that allow estimating the impact of earlier design decisions on the final implementation. To achieve an optimal implementation that satisfies a set of requirements, we propose a platform-based methodology for electric power system design, which enables independent implementation of system topology (i.e., interconnection among elements) and control protocol by using a compositional approach. In our flow, design space exploration is carried out as a sequence of refinement steps from the initial specification toward a final implementation by mapping higher level behavioral and performance models into a set of either existing or virtual library components at the lower level of abstraction. Specifications are first expressed using the formalisms of linear temporal logic, signal temporal logic, and arithmetic constraints on Boolean variables. To reason about different requirements, we use specialized analysis and synthesis frameworks and formulate assume guarantee contracts at the articulation points in the design flow. We show the effectiveness of our approach on a proof-of-concept electric power system design.

**INDEX TERMS** Design methodology, design automation, aircraft, power systems, control system synthesis, contract-based design, platform-based design, cyber-physical systems.

# I. INTRODUCTION

The advent of high capability, reliable power electronics together with powerful embedded processors has enabled an increasing amount of "electrification" of vehicles such as cars and aircraft in recent years [1], [2]. Hydraulic, pneumatic and mechanical systems are being replaced by cyber-electrical components that increase the overall system efficiency [3]. However, the increased use of electrically-powered elements poses significant challenges to the aircraft electric power system in terms of the reliability of electrical power generation and distribution while satisfying safety requirements.

A severe limitation in common design practice is the lack of formalized specifications. System requirements are

predominantly written in text-based languages that are not suitable for mathematical analysis and verification. Assessing system correctness is then left for simulations and prototype tests later in the design process, when modifications are significantly more expensive. Additionally, the inability to rigorously model the interactions among heterogeneous components and between the physical and the cyber sides of the system poses a serious obstacle. Thus, the traditional heuristic design process based on text-based requirement capture and designers' experience leads to implementations that are inefficient and sometimes do not even satisfy the requirements, yielding long re-design cycles, cost overruns and unacceptable delays.

<sup>&</sup>lt;sup>2</sup>Institute for Systems Research and Aerospace Engineering, University of Maryland, College Park, MD 20742, USA

<sup>&</sup>lt;sup>3</sup>Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109, USA

<sup>&</sup>lt;sup>4</sup>Engineering and Applied Science Department, California Institute of Technology, Pasadena, CA 91125, USA

We propose instead to carry out a rigorous design process that includes allocation of the requirements to the components and early validation of design constraints. By following the platform-based design paradigm [4], we proceed by subsequent refinement of design requirements using a library of available components. To perform this task, we define convenient abstractions for system exploration and compositional synthesis of system topology (interconnection among the various components) and control. In particular, we build a rich, multi-view set of component models that can be used by different, domain-specific analysis, synthesis and verification frameworks. We first synthesize an electric power system topology from system requirements formalized as arithmetic constraints on Boolean variables. For the given topology, we translate the requirements into temporal logic formulas, by which we synthesize and verify control protocols. To reason about different requirements in a compositional way, we use the concept of *contracts* [5] that formalize the notion of interfaces between models and tools in the design flow. A few theoretical results (Theorem 3.1, Propositions 6.1 and 6.2) show how contracts can offer a natural framework to reason about distributed control architectures as well as the heterogeneous interface between the controller and its

Our design methodology builds on a number of results that have opened the way for a more structured approach to the design of aircraft electric power systems. The adoption of model-based development and simulation for the analysis of aircraft performance and power optimization has already been advocated in [6], [7]. In the context of the More Open Electrical Technologies (MOET) project [2], a set of model libraries have been developed using the Modelica language [8] to support "more-electric" aircraft simulation, design and validation. Simulation is used for electric power system performance verification (e.g., stability and power quality) at the network level, by leveraging models with different levels of complexity to analyze different system properties, and validated with real equipment measurements. However, design space exploration, optimization and analysis of faulty behaviors in these models can still become computationally unaffordable unless proper levels of abstraction are devised, based on the goals at each design step.

A library-based approach to instantiate, analyze and verify a system design was also adopted in [9], [10], within the META research program, with the aim to compress the product development and deployment timeline of defense systems. A simulation framework based on Modelica was developed to enable exploration of architectural design decisions, while a language based on SysML [11] was proposed to enable semantically robust integration of models, analytical methods and results provided by other domain specific languages and tools [12]. Such integration language incorporates assumeguarantee contracts to formalize system requirements and enable the generation of monitors. In this paper, we further extend the use of assume-guarantee contracts as a design aid in combination with platform-based design to yield system

synthesis and optimization in addition to system simulation and verification.

An optimization-oriented power system design methodology following the platform-based paradigm was proposed in [13] where initial specifications are refined and mapped to the final implementation in four steps. At each step, a binary optimization problem is formulated to derive a class of candidate implementations for the next exploration step. The methodology deals with how to select the power generators and synthesize the electric power system topology. In this paper, we extend the flow in [13] to enable synthesis of electric power system topology and control, subject to heterogeneous sets of system requirements that are not always approximated by binary or mixed integer-linear constraints. To perform automatic synthesis of control protocols, we build on recent works on formal synthesis of aircraft vehicle management systems [14], distributed control synthesis [15], and reactive synthesis for electric power systems [16]. In particular, we express system specifications in linear temporal logic (LTL) [17], [18] and leverage a combination of tools from the computer science and formal methods domains.

The remainder of the paper is organized as follows. After a brief description of a typical electric power system and its design challenges in Section II, we provide some background on contract-based design and control synthesis in Section III. Section IV summarizes our electric power system design methodology while Section V and Section VI provide details on topology and control design. Section VII reports results from the application of our methodology to a prototype electric power system design, and is followed by concluding remarks in Section VIII.

# **II. THE AIRCRAFT ELECTRIC POWER SYSTEM**

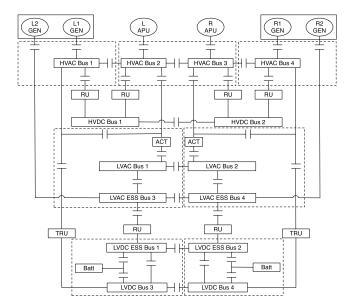

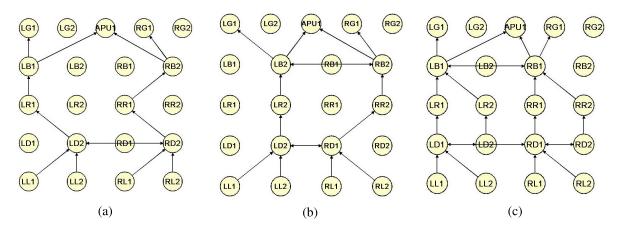

Fig. 1 illustrates a sample architecture for power generation and distribution in a passenger aircraft in the form of a single-line diagram (SLD) [1], a simplified notation for three-phase power systems. Typically, aircraft electric power systems consist of generation, primary distribution and secondary distribution sub-systems. In this paper, we focus on the primary power distribution system, which includes the majority of the supervisory control logic.

# A. COMPONENTS

The main components of an electric power system are generators, contactors, buses, and loads. Primary *generators* are connected to the aircraft engine and can operate at high or low voltages. *Auxiliary generators* are mounted atop an *auxiliary power unit* (APU). The APU is normally used on ground (when no engines are available) to provide hydraulic and electric power, but can also be used in flight when one of the primary generators fails. With a small abuse of notation, we hereafter refer to auxiliary generators themselves as APUs. *Batteries* are primarily used at start-up and in case of emergency. AC and DC *buses* (both high and low-voltage) deliver power to a number of loads. Buses can be essential or non-essential. Essential buses supply loads that should always be

powered, while non-essential ones supply loads that may be shed in the case of a fault or limited power capacity.

Contactors are electromechanical switches that connect components, and therefore determine the power flow from sources to loads. They are configured to be open or closed by one or multiple controllers (not shown in Fig. 1), denoted as *Bus Power Control Units* (BPCU).

FIGURE 1. Single-line diagram of an aircraft electric power system adapted from a Honeywell, Inc. patent [19].

Loads include subsystems such as lighting, heating, avionics and navigation. Bus loads also include power conversion devices: Rectifier units convert AC power to DC power, while AC transformers (ACTs) step down a high-voltage to a lower one, Transformer Rectifier Units (TRUs) both decrease the voltage level and convert it from AC to DC.

#### **B. SYSTEM DESCRIPTION**

The main AC power sources at the top of Fig. 1 include two low-voltage generators, two high-voltage generators, and two APU-mounted auxiliary generators. Each engine connects to a high-voltage AC (HVAC) generator (L1 and R1) and a low-voltage AC (LVAC) generator (L2 and R2). Panels, denoted as dashed square boxes, represent groups of components that are physically separated on the aircraft. The three panels below the generators include the HVAC buses, which can be selectively connected to the HVAC generators, to the auxiliary generators, and to each other via contactors, denoted by double bars.

Four rectifier units are selectively connected to buses as HVAC loads. The two panels below the high-voltage DC (HVDC) buses include the LVAC subsystem. A set of AC transformers (ACTs) convert HVAC power to LVAC power and are connected to four LVAC buses. LVAC ESS Bus 3 and LVAC ESS Bus 4 are essential and are selectively connected to the two low-voltage generators. The LVAC essential buses are also connected to rectifier units, and thus

to low-voltage DC (LVDC) power. The LVDC subsystem also contains two batteries. Power can be selectively routed directly from the HVAC bus to the LVDC buses 3 and 4 using TRUs.

One or more bus power control units use sensors (which are not depicted in Fig. 1) to measure physical quantities, such as voltages and currents, and control the state (open or closed) of the contactors, to dynamically reconfigure the system based on the status and availability of the power sources. For the rest of the paper, we denote this centralized or distributed supervisory control unit as BPCU.

# C. SYSTEM REQUIREMENTS

Given a set of loads, together with their power and reliability requirements, the goal is to determine the system's architecture and control such that the demand of the loads is satisfied for all flight conditions and a set of predetermined faults. To better formalize this design objective, we begin with a qualitative analysis of the main system requirements, by categorizing them in terms of safety and reliability requirements. For each of these categories, we provide a few examples that serve as a reference for the rest of the paper.

Safety specifications constrain the way each bus must be powered to avoid loss of essential features, and the maximum time interval allowed for power shortages. For instance, to avoid generator damage, we proscribe AC sources to be paralleled, i.e. no AC bus can be powered by multiple generators at the same time. Moreover, we refine the definition of essential loads and buses (such as flight-critical actuators) provided above by requiring that they be never unpowered for more than a specified time  $t_{max}$ .

Reliability specifications describe the bounds on the failure probabilities that can be tolerated for different portions of the system. Based on its failure modes, every component is characterized by a failure rate. A failure rate of  $\lambda$  indicates that a failure occurs, on average, every  $1/\lambda$  hours. For a given mission profile, failure rates can be translated into failure probabilities so that system reliability specifications are also expressed in terms of the failure probabilities of the components. Based on the component failure rates, a typical specification would require that the failure probability for an essential load (i.e., the probability of being unpowered for longer than  $t_{max}$ ) be smaller than  $10^{-9}$  per flight hour. The actual probability value depends on the load criticality [1]. In our example, both the electric power system topology and the controller should be designed to accommodate any possible combination of faults potentially causing the failure of an essential component, and having a joint probability larger than  $10^{-9}$  per flight hour.

# III. CONTRACT-BASED DESIGN OF CYBER-PHYSICAL SYSTEMS

Inspired by recent results on assume-guarantee compositional reasoning and interface theories in the context of hybrid systems and software verification, our methodology is based on the use of assume-guarantee contracts for cyber-

physical systems [5]. Informally, contracts mimic the thought process of a designer, who aims at *guaranteeing* certain performance figures for the design under specific *assumptions* on its environment. The essence of contracts is, therefore, a *compositional* approach, where design and verification complexity is reduced by decomposing system-level tasks into more manageable subproblems at the component level, under a set of assumptions. System properties can then be inferred or proved based on component properties. In this respect, contract-based design can be a rigorous and effective paradigm while dealing with the complexity of modern system design, and has been successfully applied to other embedded system domains, such as automotive applications [20] and mixed-signal integrated circuits [21].

#### A. COMPONENTS

We summarize the main concepts behind contract-based design starting with the notion of components. A summary of the notation used in this Section and in the rest of the paper is given in Table 1.

A *component*  $\mathcal{M}$  can be seen as an abstraction, a hierarchical entity representing an element of a design, characterized by the following *component attributes*:

- a set of input *variables*  $U \in \mathcal{U}$ , output variables  $Y \in \mathcal{Y}$ , and internal variables (including state variables)  $X \in \mathcal{X}$ ; a set of configuration *parameters*  $\kappa \in \mathcal{K}$ , and a set of input, output and bidirectional *ports*  $\lambda \in \Lambda$  for connections with other components;

- a set of *behaviors*, which can be implicitly represented by a dynamic *behavioral model*  $\mathcal{F}(U,Y,X,\kappa)=0$ , uniquely determining the value of the output and internal variables given the one of the input variables and configuration parameters. We assume that components can respond to every possible sequence of input variables, i.e., they are receptive to their input variables. Behaviors are generic, and could be continuous functions that result from solving differential equations, or sequences of values or events recognized by an automata model;

- a set of *non-functional models*, i.e. maps that allow computing non-functional properties of a component corresponding to particular valuations of its input variables and configuration parameters. Examples of nonfunctional maps include the *performance model*  $\mathcal{P}$ , computing a set of performance figures by solving the behavioral model, or the *reliability model*  $\mathcal{R}$ , providing the failure probability of a component.

Components can be connected together by sharing certain ports under constraints on the values of certain variables. In what follows, we use *variables* to denote both component variables and ports. Moreover, components can be hierarchically organized to represent a system at different levels of abstraction. Given a set of components at level l, a system can then be composed by *parallel composition* and represented as a new component at level l + 1. At each level of abstraction, components are also capable of exposing multiple, complementary *views*, associated to different concerns (e.g. safety,

TABLE 1. Notation.

|                                                                                    | Platform Components and Contracts         |

|------------------------------------------------------------------------------------|-------------------------------------------|

| Symbol                                                                             | Definition                                |

| $\overline{\mathcal{M}}$                                                           | Generic platform component                |

| U                                                                                  | Input variable set                        |

| $\mathcal{U}$                                                                      | Input variable domain                     |

| Y                                                                                  | Output variable set                       |

| $\mathcal{Y}$                                                                      | Output variable domain                    |

| X                                                                                  | Internal (and state) variable set         |

| $\mathcal{X}$                                                                      | Internal variable domain                  |

| $\mathbb{S} = U \cup Y \cup X$                                                     | Component (system) variable set           |

| $\mathcal{S}, dom(\mathbb{S})$                                                     | Component (system) variable domain        |

| $\kappa$                                                                           | Configuration parameter set               |

| $\mathcal{K}$                                                                      | Configuration parameter domain            |

| $\lambda$                                                                          | Port set                                  |

| $\Lambda$                                                                          | Port domain                               |

| $\mathcal{F}(U,Y,X,\kappa) = 0$                                                    | Behavioral model                          |

| $\mathcal{P}$                                                                      | Performance model (map)                   |

| $\mathcal{R}$                                                                      | Reliability model (map)                   |

| M                                                                                  | Implementation (and set of its behaviors) |

| $\mathcal{C} = (A, G)$                                                             | Contract (assumptions, guarantees)        |

| E                                                                                  | Set of legal environments for $C$         |

|                                                                                    | Discrete Event (LTL) Abstraction          |

| Symbol                                                                             | Definition                                |

| Σ                                                                                  | Generic system (and set of its behaviors) |

| S                                                                                  | System variable set                       |

| S, dom(S)                                                                          | System variable domain                    |

| s                                                                                  | System state                              |

| $\sigma = s_0 s_1 s_2 \dots$                                                       | System behavior                           |

| 3                                                                                  | Environment variable set                  |

| $\mathcal{E}, dom(\mathcal{E})$                                                    | Environment variable domain               |

| e                                                                                  | Environment variable valuation            |

| $\mathfrak D$                                                                      | Controlled variable set                   |

| $\mathcal{D}, dom(\mathcal{D})$                                                    | Controlled variable domain                |

| d                                                                                  | Controlled variable valuation             |

| $C_{LTL} =$                                                                        | LTL contract                              |

| $=(\varphi_e,\varphi_e\to\varphi_s)$                                               |                                           |

|                                                                                    | Hybrid Model (STL) Abstraction            |

| Symbol                                                                             | Definition                                |

| $oldsymbol{u}(t)$                                                                  | Input signal                              |

| $oldsymbol{y}(t)$                                                                  | Output signal                             |

| $oldsymbol{x}(t)$                                                                  | Internal (state) signal                   |

| $oldsymbol{s} = (oldsymbol{u}, oldsymbol{y}, oldsymbol{x})$                        | System trace or behavior                  |

| $\kappa$                                                                           | Configuration parameter vector            |

| $\mathfrak{F}(\boldsymbol{u},\boldsymbol{y},\boldsymbol{x},\boldsymbol{\kappa})=0$ | Behavioral model                          |

| $C_{STL} =$                                                                        | STL contract                              |

| $= (\varphi_e, \varphi_e \to \varphi_s)$                                           |                                           |

| $C'_{LTL} = $                                                                      | LTL contract refined into STL             |

| $=(\varphi_e',\varphi_e'\to\varphi_s')$                                            |                                           |

performance, and reliability), which can be expressed via different formalisms and analyzed by different tools.

A component may be associated to both implementations and contracts. An *implementation* M is an instantiation of a component  $\mathcal{M}$  for a given set of configuration parameters. In what follows, we also denote with M the set of all its behaviors.

# **B. CONTRACTS**

A contract  $\mathcal{C}$  for a component  $\mathcal{M}$  is a pair of assertions (A, G), called the assumptions and the guarantees. An assertion H represents a specific set of behaviors over variables that satisfies H. Therefore, operations on assertions and contracts are set operations. An implementation M satisfies an assertion H whenever M and H are defined over the same set of variables and all the behaviors of M satisfy the assertion, i.e. when

$M \subseteq H$ . The set of all the legal *environments* for  $\mathcal{C}$  collects all implementations E such that  $E \subseteq A$ . An implementation of a component satisfies a contract whenever it satisfies its guarantee, subject to the assumption. Formally,  $M \cap A \subseteq G$ , where M and  $\mathcal{C}$  have the same variables. We denote such a *satisfaction* relation by writing  $M \models \mathcal{C}$ . Similarly, we relate a legal environment E to a contract  $\mathcal{C}$  by the satisfaction relation  $E \models_E \mathcal{C}$ .

Any implementation M of a component such that  $M \subseteq G \cup \neg A$ , where  $\neg A$  is the complement of A, is also an implementation for C. In general,  $M_C = G \cup \neg A$  is the maximal implementation for C. Two contracts C and C' with identical variables, identical assumptions, and such that  $G' \cup \neg A = G \cup \neg A$ , possess identical sets of implementations. Such two contracts are then *equivalent*. Therefore, any contract C = (A, G) is equivalent to a contract in *saturated form* (A, G'), which also satisfies  $G' \supseteq \neg A$ , or, equivalently,  $G' \cup A = True$ , the true assertion. To obtain the saturated form of a contract, it is enough to take  $G' = G \cup \neg A$ .

Contracts associated with different components can be combined according to different rules. Similar to parallel composition of components, *parallel composition* of contracts can be used to construct composite contracts out of simpler ones. Let  $\mathcal{C}_1 = (A_1, G_1)$  and  $\mathcal{C}_2 = (A_2, G_2)$  be contracts in saturated form, then the assumptions and the guarantees of the composite  $\mathcal{C}_1 \otimes \mathcal{C}_2$  can be computed as follows [20]:

$$A = (A_1 \cap A_2) \cup \neg (G_1 \cap G_2), \tag{1}$$

$$G = G_1 \cap G_2. \tag{2}$$

The composite contract must clearly satisfy the guarantees of both. Moreover, since the environment should satisfy all the assumptions, we should expect that the assumptions of each contract would also combine by conjunction. In general, however, part of the assumptions  $A_1$  will be already satisfied by composing  $C_1$  with  $C_2$ , which acts as a partial environment for  $C_1$ . Therefore,  $G_2$  can relax the assumptions  $A_1$ , and viceversa, which motivates equation (1). To use equation (1) and equation (2), the behaviors related to the original contracts need to be extended to a common set of variables. Such an extension, which is also called *alphabet equalization*, can be achieved by an operation of inverse projection [20].

Even if they need to be satisfied simultaneously, multiple views of the same component do not generally compose by parallel composition. Therefore, the *conjunction* ( $\land$ ) of contracts can also be defined so that if  $M \models \mathcal{C}_1 \land \mathcal{C}_2$ , then  $M \models \mathcal{C}_1$  and  $M \models \mathcal{C}_2$ . Contract conjunction can be computed by defining a preorder on contracts, which formalizes a notion of *refinement*. We say that  $\mathcal{C}$  refines  $\mathcal{C}'$ , written  $\mathcal{C} \preceq \mathcal{C}'$  (with  $\mathcal{C}$  and  $\mathcal{C}'$  both in saturated form), if  $A \supseteq A'$  and  $G \subseteq G'$ . Refinement amounts to relaxing assumptions and reinforcing guarantees, therefore strengthening the contract. Clearly, if  $M \models \mathcal{C}$  and  $\mathcal{C} \preceq \mathcal{C}'$ , then  $M \models \mathcal{C}'$ . On the other hand, if  $E \models_E \mathcal{C}'$ , then  $E \models_E \mathcal{C}$ . With the given ordering, we can compute the conjunction of contracts by taking the greatest

lower bound of  $C_1$  and  $C_2$ . For contracts in saturated form, we have

$$C_1 \wedge C_2 = (A_1 \cup A_2, G_1 \cap G_2),$$

(3)

i.e. *conjunction* of contracts amounts to taking the intersection of the guarantees and the union of the assumptions. Conjunction can be used to compute the overall contract for a component starting from the contracts related to multiple views (concerns, requirements) in a design.

In addition to satisfaction and refinement, *consistency* and *compatibility* are also relations involving contracts. Technically, these two notions refer to individual contracts. A contract is *consistent* when the set of implementations satisfying it is not empty, i.e. it is feasible to develop implementations for it. For contracts in saturated form, this amounts to verifying that  $G \neq \emptyset$ . C is *compatible* if there exists a legal environment E for C, i.e. if and only if  $A \neq \emptyset$ . The intent is that a component satisfying contract C can only be used in the context of a compatible environment. In practice, however, violations of consistency and compatibility occur as a result of a parallel composition, so that we can refer to the collection of components forming a composite contract as being consistent or compatible.

# C. PLATFORM-BASED DESIGN AND CONTRACTS

We use contracts in the context of platform-based design [4], a paradigm that allows reasoning about design in a structured way. In platform-based design, design progresses in precisely defined abstraction levels; at each level, functionality (what the system is supposed to do) is strictly separated from architecture (how the functionality can be implemented). Differently than model-based development, platform-based design consists of a *meet-in-the-middle* approach where successive top-down refinements of high-level specifications across design layers are mapped onto bottom-up abstractions and characterizations of potential implementations. Each layer is defined by a design *platform*, which is a *library* (collection) of *components*, models, representing functionality and performance of the components (as detailed in Section III-A), and *composition rules*.

In this context, contracts can play a fundamental role in: (i) determining *valid* compositions so that when the design space is explored, only *legal* (i.e. satisfying the composition rules) compositions that are *compatible* (i.e. satisfying the contracts) are taken into consideration; (ii) guaranteeing that a component at a higher level of *abstraction* is an accurate representation of a lower level component (or aggregation of components); (iii) checking that an architecture platform is indeed a correct *refinement* of a specification platform, and (iv) formalizing top-level system *requirements*.

Since compatibility is assessed among components at the same abstraction layer, the first category of contracts is denoted as *horizontal contracts*. If an environment violates a horizontal contract, it cannot host any of its implementations.

However, checking horizontal contracts is not sufficient, in general, to guarantee correct implementations. When

analyzing the behavior of complex cyber-physical systems, simplified macro-models can be used to capture the relevant behavior of the components at higher levels of abstraction. Therefore, guarantees should also be provided on the accuracy of the macro-models with respect to models at lower levels of abstraction. These guarantees are captured via bottom-up vertical contracts. On the other hand, vertical contracts can also be used to encode top-down requirements that system architects introduce to craft the behavior of a chosen architecture according to the desired functionality. The above set of constraints can be expressed using top-down vertical contracts. They are used to ensure that an implementation is correct, by checking that the architecture platform is a refinement of the specification platform.

To partition system specifications, we identify which entity is responsible for a set of requirements, and which ones are just indirectly affected. By assigning information about requirements to components, we make it explicit what each component guarantees and what it assumes about its environment. Both of these aspects determine the top-down vertical contract for the component. If the assumptions are satisfied, then the component specification can be developed independently of other subsystems. In section IV, we exploit this concept to independently develop the electric power system topology and its control protocol.

To formulate system and component requirements as contracts, we adopt different formalisms based on the computational models used to represent the components and the tools used to analyze and synthesize them. Example of formalisms include automata or temporal logic constructs (e.g. used for safety requirements), probabilistic constraints (e.g. used for reliability requirements), linear arithmetic constraints on Boolean variables (e.g. used for connectivity requirements), integro-differential equations, and linear or nonlinear constraints on real numbers (e.g. used for real-time requirements). In what follows, we review the formalisms adopted in Section VI for the analysis and synthesis of reactive controllers in a contract-based framework.

# D. REQUIREMENT FORMALIZATION

We use two formal specification languages, namely, linear temporal logic (LTL) and signal temporal logic (STL), particularly suitable for capturing system and component requirements and reasoning about the correctness of their behaviors. As such, these languages will be used for defining contracts for control design.

# 1) LINEAR TEMPORAL LOGIC

Temporal logic is a branch of logic that incorporates temporal aspects in order to reason about propositions in time, and was first used as a specification language by Pnueli [22]. In this section, we consider a version of temporal logic called linear temporal logic (LTL), whose formal semantics can be found in [23]. While in contract-based design the component is regarded as the fundamental element of a design, and systems are denoted as interconnections of components, as

we describe the basics of LTL, we prefer to adhere to the classical terminology, which is historically consolidated [23], and define design abstractions in terms of systems.

Definition 1: A system consists of a set S of variables. The domain of S, denoted by dom(S), is the set of valuations of S.

Definition 2: An atomic proposition is a statement on system variables that has a unique truth value (*True* or *False*) for a given value s. Let  $s \in dom(S)$  be a state of the system (i.e., a specific valuation of its variables) and p be an atomic proposition. Then  $s \models p$  if p is *True* at the state s. Otherwise,  $s \not\models p$ .

LTL also includes Boolean connectors such as negation  $(\neg)$ , disjunction  $(\lor)$ , conjunction  $(\land)$ , material implication  $(\rightarrow)$ , and two basic temporal modalities, *next*  $(\bigcirc)$  and *until*  $(\mathcal{U})$ . By combining these operators, it is possible to specify a wide range of requirements. Given a set AP of atomic propositions, LTL formulas are formed according to the following grammar:

$$\varphi := True \mid p \mid \neg \varphi \mid \varphi_1 \wedge \varphi_2 \mid \bigcirc \varphi \mid \varphi_1 \mathcal{U} \varphi_2$$

where  $p \in AP$ . Formulas involving other operators, including *eventually* ( $\Diamond$ ) and *always* ( $\square$ ), can be derived from these basic ones.

LTL formulas over AP are interpreted over infinite sequences of states. In the LTL abstraction, we denote such a sequence as a *behavior* of the system. Let  $\sigma = s_0 s_1 s_2 \dots$  be a behavior and  $\varphi$  be an LTL formula. We say that  $\varphi$  holds at position  $i \geq 0$  of  $\sigma$ , written  $s_i \models \varphi$ , if and only if  $\varphi$  holds for the remainder of the sequence starting at position i. Then, a sequence  $\sigma$  satisfies  $\varphi$ , denoted by  $\sigma \models \varphi$ , if  $s_0 \models \varphi$ . Let  $\Sigma$  be the collection of all sequences  $\sigma$  such that  $\sigma \in \Sigma$ . Then, a system composed of the variables S is said to satisfy  $\varphi$ , written  $\Sigma \models \varphi$ , if all sequences satisfy  $\varphi$ .

# 2) SIGNAL TEMPORAL LOGIC

LTL allows formal reasoning about temporal behaviors of systems with Boolean, discrete-time signals (variables) or sequences of events. To deal with dense-time real signals and hybrid dynamical model that mix the discrete dynamics of the controller with the continuous dynamics of the plant, several logics have been introduced over the years, such as Timed Propositional Temporal Logic [24], and Metric Temporal Logic [25]. Signal Temporal Logic (STL) [26] has been proposed more recently as a specification language for constraints on real-valued signals in the context of analog and mixed-signal circuits. In this paper, we refine LTL system requirements into constraints on physical variables (e.g. voltages and currents) expressed using STL constructs. Then, we monitor and process simulation traces to verify constraint satisfaction, while optimizing a set of design parameters.

For a hybrid dynamical model, we define a *signal* as a function mapping the time domain  $\mathbb{T} = \mathbb{R}_{\geq 0}$  to the reals  $\mathbb{R}$ . A multi-dimensional signal q is then a function from  $\mathbb{T}$  to  $\mathbb{R}^n$  such that  $\forall t \in \mathbb{T}$ ,  $q(t) = (q_1(t), \ldots, q_n(t))$ , where  $q_i(t)$  is the *i*-th component of vector q(t). It is convenient to repre-

sent the behavior of the system's variables over time using multi-dimensional signals. Therefore, we assume that a hybrid system behavioral model  $\mathcal{F}$  (e.g. implemented in a simulator) takes as input a signal u(t) and computes an output signal y(t) and an internal signal x(t) such that  $\mathcal{F}(u(t), y(t), x(t), \kappa) = 0$ , where  $\kappa$  is a given vector of system configuration parameters. A collection of signals resulting from a simulation of the system is a *trace*, which can also be viewed as a multi-dimensional signal. A trace s(t) that includes all the system input, output and internal signals can also denote a system *behavior*.

In STL, constraints on real-valued signals, or *predicates*, can be reduced to the form  $\mu = g(q) \sim \pi$ , where g is a scalar-valued function over the signal  $q, \sim \in \{<, \leq, \geq, >, =, \neq \}$ , and  $\pi$  is a real number. As in LTL, temporal formulas are formed using temporal operators, *always*, *eventually* and *until*. However, each temporal operator is indexed by intervals of the form  $(a, b), (a, b], [a, b), [a, b], (a, \infty)$  or  $[a, \infty)$ , where each of a, b is a non-negative real-valued constant. If I is an interval, then an STL formula is written using the following grammar:

$$\varphi := True \mid \mu \mid \neg \varphi \mid \varphi_1 \wedge \varphi_2 \mid \varphi_1 \mathcal{U}_I \varphi_2$$

The *always* and *eventually* operators are defined as special cases of the *until* operator as follows:  $\Box_I \varphi \triangleq \neg \Diamond_I \neg \varphi$ ,  $\Diamond_I \varphi \triangleq True \mathcal{U}_I \varphi$ . When the interval I is omitted, we use the default interval of  $[0, +\infty)$ .

The semantics of STL formulas are defined informally as follows. The signal q satisfies  $\mu = g(q) < 2$  at time t (where  $t \ge 0$ ), written  $(q, t) \models \mu$ , if g(q(t)) < 2. It satisfies  $\varphi = \Box_{[0,2)}$  (q > -1), written  $(q, t) \models \varphi$ , if for all time  $0 \le t < 2$ , q(t) > -1. The signal  $q_1$  satisfies  $\varphi = \Diamond_{[1,2)}q_1 > 0.4$  iff there exists time t such that  $1 \le t < 2$  and  $q_1(t) > 0.4$ . The two-dimensional signal  $q = (q_1, q_2)$  satisfies the formula  $\varphi = (q_1 > 10) \mathcal{U}_{[2.3,4.5]}$   $(q_2 < 1)$  iff there is some time  $t_0$  where  $2.3 \le t_0 \le 4.5$  and  $q_2(t_0) < 1$ , and for all time t in  $[2.3, t_0)$ ,  $q_1(t)$  is greater than 10. We write  $q \models \varphi$  as a shorthand of  $(q, 0) \models \varphi$ . Formal semantics can be found in [26].

Parametric Signal Temporal Logic (PSTL) is an extension of STL introduced in [27] to define template formulas containing unknown parameters. Syntactically speaking, a PSTL formula is an STL formula where numeric constants, either in the constraints given by the predicates  $\mu$  or in the time intervals of the temporal operators, can be replaced by symbolic parameters. These parameters are divided into two types:

- A *scale* parameter  $\pi$  is a parameter appearing in predicates of the form  $\mu = g(q) \sim \pi$ ,

- A *time* parameter  $\tau$  is a parameter appearing in an interval of a temporal operator.

An STL formula is obtained by pairing a PSTL formula with a valuation function that assigns a value to each symbolic parameter. For example, consider the PSTL formula  $\varphi(\pi, \tau) = \Box_{[0,\tau]} \ q > \pi$ , with symbolic parameters  $\pi$  (scale) and  $\tau$  (time). The STL formula  $\Box_{[0,10]} \ q > 1.2$  is an instance of  $\varphi$  obtained with the valuation  $w = \{\tau \mapsto 10, \ \pi \mapsto 1.2\}$ .

#### E. REACTIVE CONTROL SYNTHESIS

Reactive systems are systems that maintain an ongoing relation with their environment by appropriately reacting to it. The controllers that regulate the behavior of such systems are called reactive controllers.

A *control system* is a composition of a physical plant, including sensors and actuators (e.g., an electric power system topology with fault sensors and contactors), and an embedded controller that runs a control protocol (control logic) to restrict the behaviors of the plant so that all the remaining behaviors satisfy a set of system specifications. System specifications can be expressed as a contract  $\mathcal{C} = (A, G)$ , where, roughly speaking, assumptions A encode the allowable behaviors of the environment the control system operates in, and guarantees G encode the system requirements.

The synthesis of reactive controls can then be interpreted in terms of assume-guarantee contracts. Given the system contract  $\mathcal{C}$ , control synthesis finds a control logic that, when implemented, ensures that the system satisfies  $\mathcal{C}$ ; or declares that no such logic exists. It is possible to extend this idea to distributed control architectures. In distributed synthesis, different control subsystems can be composed if their contracts are compatible. Hence, the goal of distributed synthesis is to simultaneously refine a system contract into compatible horizontal contracts for the components (i.e., subsystems), and to find the control logics that realize those contracts.

# 1) REACTIVE SYNTHESIS FROM LTL SPECIFICATIONS

Let  $\mathcal E$  and  $\mathcal D$  be sets of environment and controlled variables, respectively. Let  $s=(e,d)\in dom(\mathcal E)\times dom(\mathcal D)$  be a state of the system. Consider an LTL specification  $\varphi$  of assumeguarantee form

$$\varphi = (\varphi_e \to \varphi_s), \tag{4}$$

where  $\varphi_e$  characterizes the assumptions on the environment and  $\varphi_s$  characterizes the system requirements. The synthesis problem is concerned with constructing a control protocol (a partial function  $f:(s_0s_1...s_{t-1},e_t)\mapsto d_t$ ) which chooses the move of the controlled variables based on the state sequence so far and the behavior of the environment so that the system satisfies  $\varphi_s$  as long as the environment satisfies  $\varphi_e$ . If such a protocol exists, the specification  $\varphi$  is said to be *realizable*. Reactive synthesis can then be viewed as a two-player game between an environment that attempts to falsify the specification in equation (4) and a controlled plant that tries to satisfy it.

For general LTL, the synthesis problem has a doubly exponential complexity [28]. However, a subset of LTL, namely generalized reactivity (1) (GR(1)), generates problems that can be solved in polynomial time (i.e., polynomial in  $|dom(\mathcal{E}) \times dom(\mathcal{D})|$ , the number of valuations of the variables in  $\mathcal{E}$  and  $\mathcal{D}$ ) [29]. GR(1) specifications restrict  $\varphi_e$  and  $\varphi_s$  to take the following form, for  $\alpha \in \{e, s\}$ ,

$$\varphi_{\alpha} := \varphi_{\text{init}}^{\alpha} \, \wedge \bigwedge_{i \in I_{1}^{\alpha}} \Box \varphi_{1,i}^{\alpha} \wedge \bigwedge_{i \in I_{2}^{\alpha}} \Box \Diamond \varphi_{2,i}^{\alpha},$$

where  $\varphi_{\rm init}^{\alpha}$  is a propositional formula characterizing the initial conditions;  $\varphi_{1,i}^{\alpha}$  are transition relations characterizing safe, allowable moves and propositional formulas characterizing invariants;  $\varphi_{2,i}^{\alpha}$  are propositional formulas characterizing states that should be attained infinitely often;  $I_1^{\alpha}$  and  $I_2^{\alpha}$  are index sets enumerating formulas  $\varphi_{1,i}^{\alpha}$  and  $\varphi_{2,i}^{\alpha}$ , respectively.

Given a GR(1) specification, there are game solvers and digital design synthesis tools that generate a finite-state automaton that represents the control protocol for the system [30], [31].

#### 2) DISTRIBUTED SYNTHESIS

To provide an inherent level of redundancy for system reliability, distributed control architectures are increasingly being adopted in modern aircraft electric power systems, thus motivating the extension of reactive synthesis techniques to the design of distributed controllers. Given a global specification and a system composed of subsystems, distributed synthesis proceeds by first finding local specifications for each subsystem, and then synthesizing local controllers for these subsystems separately. If the local specifications satisfy certain conditions, it can be shown that the local controllers realizing these local specifications can be implemented together and the overall system is guaranteed to satisfy the global specification, as detailed in [15]. We describe below a special case of distributed architecture, i.e. a serial interconnection of controllers, which is used in the design in Section VII-B.2 to synthesize controllers for AC and DC subsystems separately. The following theorem is based on a result that was first reported in [15]. We introduce here a new proof that shows how contracts can offer a rigorous and effective framework to reason about distributed control architectures in a compositional manner.

# Theorem 3.1: Given

- a system characterized by a set S = D ∪ E of variables, where D and E are disjoint sets of controllable and environment variables,

- its two subsystems with variables  $\mathcal{S}_1 = \mathcal{D}_1 \cup \mathcal{E}_1$  and  $\mathcal{S}_2 = \mathcal{D}_2 \cup \mathcal{E}_2$ , where for each  $i \in \{1, 2\}$ ,  $\mathcal{D}_i$  and  $\mathcal{E}_i$  are disjoint sets of controllable and environment variables for the  $i^{th}$  subsystem,  $\mathcal{D}_1$  and  $\mathcal{D}_2$  are disjoint, and  $\mathcal{D} = \mathcal{D}_1 \cup \mathcal{D}_2$ ,

- a set  $\Im$  of pairs of variables representing the interconnection structure, that is, for a serial interconnection,  $\Im = \{(o_1, i_2) | o_1 \in O_1 \subseteq (\mathcal{D}_1 \cup \mathcal{E}_1), i_2 \in I_2 \subseteq \mathcal{E}_2\}$ , where for all  $(o, i) \in \Im$ , o = i,

- a global specification  $\varphi: \varphi_e \to \varphi_s$ , and two local specifications  $\varphi_1: \varphi_{e_1} \to \varphi_{s_1}$  and  $\varphi_2: \varphi_{e_2} \to \varphi_{s_2}$ , where  $\varphi_e, \varphi_{e_1}, \varphi_{e_2}, \varphi_s, \varphi_{s_1}$ , and  $\varphi_{s_2}$  are LTL formulas containing variables only from their respective sets of environment variables  $\mathcal{E}, \mathcal{E}_1, \mathcal{E}_2$  and system variables  $\mathcal{E}, \mathcal{E}_1, \mathcal{E}_2$ ;

if the following conditions hold:

- 1) any behavior that satisfies  $\varphi_e$  also satisfies  $(\varphi_{e_1} \wedge \varphi_{e_2})$ ,

- 2) any behavior that satisfies  $(\varphi_{s_1} \wedge \varphi_{s_2})$  also satisfies  $\varphi_s$ ,

- 3) there exist two controllers that make the local

specifications  $(\varphi_{e_1} \to \varphi_{s_1})$  and  $(\varphi_{e_2} \to \varphi_{s_2})$  true under the interconnection structure  $\mathcal{I}$ ;

then, implementing the two controller together leads to a controller that satisfies the global specification  $\varphi_e \to \varphi_s$ .

*Proof:* The conditions on  $\mathcal{D}$ ,  $\mathcal{D}_1$ ,  $\mathcal{D}_2$  ensure that the two controllers are composable, i.e. they do not try to control the same output (controllable) variables. We first derive contracts from global and local specifications, by defining the following sets of behaviors in terms of assumptions and guarantees:

$$A = \{\sigma : \sigma \models \varphi_e\}; \quad A_i = \{\sigma : \sigma \models \varphi_{e_i}\};$$

$$G = \{\sigma : \sigma \models (\varphi_e \to \varphi_s)\}; \quad G_i = \{\sigma : \sigma \models (\varphi_{e_i} \to \varphi_{s_i})\};$$

$$A' = \{\sigma : \sigma \models (\varphi_{e_1} \land \varphi_{e_2})\};$$

$$G' = \{\sigma : \sigma \models ((\varphi_{e_1} \land \varphi_{e_2}) \to (\varphi_{s_1} \land \varphi_{s_2}))\}.$$

We immediately observe that  $A' = A_1 \cap A_2$  while  $G' \supseteq (G_1 \cap G_2)$ . Now, let  $\mathcal{C} = (A, G)$  be the global contract and  $\mathcal{C}_1 = (A_1, G_1)$ ,  $\mathcal{C}_2 = (A_2, G_2)$  the local contracts, all in saturated form. Clearly, for any implementation  $M_i, M_i \models \mathcal{C}_i$  if and only if its set of behaviors  $\sigma_{M_i} \subseteq G_i$ , i.e.  $\sigma_{M_i} \models \varphi_i$ , after alphabet equalization. Moreover, because any implementations  $M_1$  and  $M_2$  of  $\mathcal{C}_1$  and  $\mathcal{C}_2$  are composable, contract composition using equations (1) and (2) is well defined and the composition  $M_1 \times M_2$  (under the interconnection  $\mathfrak{I}$ ) is an implementation of  $\mathcal{C}_1 \otimes \mathcal{C}_2$  (under the interconnection  $\mathfrak{I}$ ).

We now prove that

$$C_1 \otimes C_2 \leq C$$

,

i.e.,  $C_1 \otimes C_2 = (A_{12}, G_{12})$  refines C. By the definition of refinement, this amounts to showing that  $G_{12} \subseteq G$  and  $A_{12} \supseteq A$ . We obtain

$$G_{12} = (G_1 \cap G_2) \subset G' \subset G \tag{5}$$

by conditions 1 and 2 in the theorem statement, and

$$A_{12} = (A_1 \cap A_2 \cup \neg G_{12}) \supseteq (A_1 \cap A_2) = A' \supseteq A,$$

(6)

by condition 1. Moreover, if  $\mathcal{C}$  is compatible (i.e. A is not empty),  $\mathcal{C}_1 \otimes \mathcal{C}_2$  will also be compatible (i.e.  $A_{12}$  is not empty) by (6). Equations (5) and (6) allow us to conclude that  $\mathcal{C}_1 \otimes \mathcal{C}_2$  is well defined and refines  $\mathcal{C}$ , hence for any implementations  $M_1$  and  $M_2$  of  $\mathcal{C}_1$  and  $\mathcal{C}_2$ ,  $M_1 \times M_2$  satisfies the global specification.

There are two sources of conservatism in distributed synthesis. The first one is due to the fact that local controllers have only local information. Therefore, even if there exists a centralized controller that realizes a global specification, there may not exist local controllers that do so. This is an inherent problem and can only be addressed by modifying the control architecture (e.g., by changing the mapping of controlled variables to controllers, by introducing new sensors, or by modifying the information flow between local controllers). The second source of conservatism is computational. Even when local controllers that realize the global specification exist, it might be difficult to find them (e.g., see [28] for some undecidability results). We note that the conditions provided

**VOLUME 2. 2014**

8

in Theorem 3.1 are only sufficient conditions. The choices of  $\varphi_{e_i}$  and  $\varphi_{s_i}$  for  $j \in \{1, 2\}$  plays a role in the level of conservatism. In principle,  $\varphi_{e_i}$  and  $\varphi_{s_i}$  should be chosen such that A' is as "small" as possible, and G' is as "large" as possible in the sense of set inclusion. Hence, when conditions 1 and 2 are satisfied but condition 3 is not satisfied, one can gradually refine the local specifications. See [15] for further details and an example of such a refinement.

# F. DESIGN SPACE EXPLORATION AND PERFORMANCE **OPTIMIZATION**

Several real-time performance requirements (e.g. timing constraints), mostly relating to the dynamic behaviors of the physical plant and the hardware implementation of the control algorithm, are better assessed on hybrid dynamical models. For this purpose, we refine a subset of LTL requirements into STL constructs on physical (e.g. electrical, mechanical) quantities and leverage off-line or on-line monitoring techniques while optimizing the system.

A Boolean verdict on whether a property is satisfied may not be sufficient for design space exploration and system optimization. In fact, we are also interested in capturing the robustness of satisfaction of a formula  $\varphi$  by a signal q, i.e., the amount of margin by which a property is satisfied. To do so, we refer to the quantitative semantics of STL. The quantitative semantics of STL are defined using a real-valued function  $\rho$  of a trace q, a formula  $\varphi$ , and time t satisfying the following property:

$$\rho(\varphi, \boldsymbol{q}, t) \ge 0 \text{ iff } (\boldsymbol{q}, t) \models \varphi.$$

(7)

The underlying idea is that, whenever the absolute value of  $\rho(\varphi, q, t)$  is large, a change in q is less likely to affect the Boolean satisfaction (or violation) of  $\varphi$  by q, i.e. the margin by which a design satisfies  $\varphi$  is larger.

Without loss of generality, an STL predicate  $\mu$  can be identified to an inequality of the form  $g(\mathbf{q}) > 0$  (the use of strict or non strict inequalities is a matter of choice and other inequalities can be trivially transformed into this form). From this form, a straightforward quantitative semantics for predicate  $\mu$  is defined as

$$\rho(\mu, \mathbf{q}, t) = g(\mathbf{q}(t)). \tag{8}$$

Then  $\rho$  can be inductively defined for every STL formula using the following rules:

$$\rho(\neg \varphi, \mathbf{q}, t) = -\rho(\varphi, \mathbf{q}, t) \tag{9}$$

$$\rho(\varphi_{1} \wedge \varphi_{2}, \boldsymbol{q}, t) = \min(\rho(\varphi_{1}, \boldsymbol{q}, t), \rho(\varphi_{2}, \boldsymbol{q}, t))$$

$$\rho(\varphi_{1} \mathcal{U}_{I} \varphi_{2}, \boldsymbol{q}, t) = \sup_{t' \in t+I} \left[ \min \left( \rho(\varphi_{2}, \boldsymbol{q}, t'), \right) \right]$$

$$\inf_{t'' \in [t, t')} \rho(\varphi_{1}, \boldsymbol{q}, t'')$$

$$(11)$$

$$\inf_{t'' \in [t, t')} \rho(\varphi_1, \boldsymbol{q}, t'') \Big) \bigg]. \tag{11}$$

Additionally, by combining equation (11), and  $\Box_I \varphi \triangleq \neg \Diamond_I \neg \varphi$ , we get

$$\rho(\Box_I \varphi, \boldsymbol{q}, t) = \inf_{t' \in t+I} \rho(\varphi, \boldsymbol{q}, t')$$

(12)

Finally, for  $\Diamond$ , we get a similar expression using sup instead of inf. It can be shown that  $\rho$ , as defined above, satisfies equation (7) and thus defines a quantitative semantics for STL [32].

By leveraging such quantitative semantics, a design space exploration problem on a hybrid system model defined as in Section III-D.2 can be formulated as follows. Let  $C_{STL} =$  $(\varphi_e, \varphi_s)$  be an STL contract encoding a set of system requirements, with  $\varphi_e$  and  $\varphi_s$  PSTL formulas. Let C be an array of costs, and  $\kappa \in \mathcal{K}$  a vector of platform configuration parameters, i.e., a vector of variables in the hybrid system model that are selected as a result of the design process. Our goal is to find a set of parameter vectors  $\kappa^*$  that are Pareto optimal with respect to the objectives in C, while guaranteeing that the system satisfies  $\varphi_s$  for all possible system traces  $s \in \mathcal{S}$  satisfying the environment assumptions  $\varphi_e$ . Examples of design parameters could be the controller clock or a tunable delay in a component.

To formalize the above multi-objective optimization problem, we partition  $\varphi_s$  as

$$\varphi_{s}(\boldsymbol{\tau},\boldsymbol{\pi}) = \varphi_{sc}(\boldsymbol{\tau},\boldsymbol{\pi}) \wedge \bigwedge_{i=1}^{m} \varphi_{sr,i}(\boldsymbol{\tau},\boldsymbol{\pi}), \tag{13}$$

where a set of time parameters  $\tau \in \mathcal{T}$  and scale parameters  $\pi \in \Pi$  can be used to capture degrees of freedom that are available in the system specifications, and whose final value can also be determined as a result of the optimization process. The formula  $\varphi_{sc}$  in (13) encodes the requirements that will be considered as "hard" optimization constraints for Boolean satisfaction, while  $\varphi_{sr,i}$  are formulas that will also be considered for robust satisfaction, i.e., given a system trace s' and a parameter set  $(\tau', \pi')$ , the robust satisfaction  $\rho_i(\varphi_{sr,i}(\tau',\pi'),s',0)$  will also be computed. Similarly, the array of costs C can be partitioned as follows

$$C(\kappa, \tau, \pi) = \left( C_c(\kappa, \tau, \pi), C_i(\rho_i(\varphi_{s,ri}(\tau, \pi), s(\kappa), 0)) \Big|_{1 \le i \le m} \right), (14)$$

where  $C_c(\kappa, \tau, \pi)$  is a vector of costs that depend only on the parameters of the model and the formulas; it can be used to capture, for instance, some performance figures (e.g., bandwidth, energy) as a function of the system design parameters, or the duration of a requirement violation. Each component  $C_i(\rho_i(\varphi_{sr,i}, s, 0))$  in (14) is instead a scalar function of the quantitative satisfaction of each formula  $\varphi_{sr,i}$ ; it can be used to capture and maximize the margin by which  $\varphi_{sr,i}$  is satisfied.

By putting it all together, the design exploration problem can be expressed as a multi-objective robust optimization problem

$$\min_{\kappa \in \mathcal{K}, \tau \in \mathcal{T}, \pi \in \Pi} C(\kappa, \tau, \pi) \tag{15}$$

s.t.

$$\begin{cases}

\mathcal{F}(s, \kappa) = 0 \\

s \models \varphi_s(\tau, \pi) & \forall s \text{ s.t. } s \models \varphi_e

\end{cases}$$

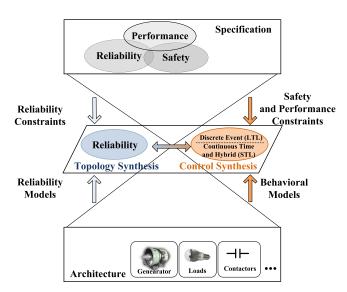

**FIGURE 2.** Pictorial representation of the main steps in the electric power system design flow in Fig. 3.

where we aim to minimize a set of costs over all possible system and formula parameter valuations, for all the system behaviors satisfying the behavioral model and the contract  $C_{STL}$ . For a given parameter valuation  $\kappa'$ , s' = (u', y', x') is the trace of input, output and internal signals that are obtained by simulating  $\mathcal{F}(.)$ . A multi-objective optimization algorithm with simulation in the loop can then be used to find the Pareto optimal solutions  $\kappa^*$ . While this may be expensive in general, it becomes affordable in many practical cases, as will be shown in Section VI and Section VII.

# IV. PLATFORM-BASED FLOW FOR ELECTRIC POWER SYSTEM DESIGN USING CONTRACTS

Our design flow, pictorially represented in Fig. 2, consists of two main steps, namely, topology design and control design. The topology design step instantiates electric power system components and connections among them to generate an optimal topology while guaranteeing the desired reliability level. Given this topology, the BPCU state machine can then be synthesized in the *control design* phase to actuate contactors while guaranteeing that loads are correctly powered. The above two steps are, however, connected. The correctness of the controller needs to be enforced in conjunction with its boundary conditions, i.e., the assumptions on the entities that are not controlled, yet interact with it. An example of such an assumption is the number of paths from generators to a load made available by the electric power system architecture to the controller. Similarly, the reliability of an architecture must be assessed under the assumptions that the controller adequately configures the contactors to leverage the available paths. Therefore, to achieve independent implementation of architecture and controller, we address the synthesis problem in a compositional way, by using contracts to incorporate the information on the environment conditions under which each entity is expected to operate.

Our design process includes a top-down and a bottom-up phase. In the top-down phase, we associate the requirements to the different entities in the system and formulate top-down vertical contracts for them. In the bottom-up phase, we populate the library of architecture components including, for instance, generators, buses, power converters and contactors. Each component is characterized by its attributes, including multiple models or views, such as behavioral or reliability views, and finite state machine or continuous-time models, as detailed in Section III-A. Horizontal contracts specify legal compositions between components. Bottom-up vertical contracts define under which conditions a model is a faithful representation of a physical element in the system. In what follows, we provide details on the electric power system design space exploration.

# A. DESIGN SPACE EXPLORATION

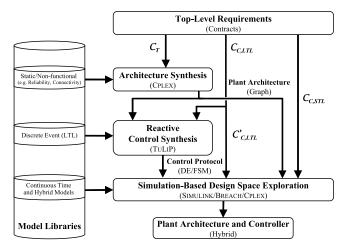

There is currently no automated procedure for optimal synthesis of control protocols simultaneously subject to reliability, safety and real-time performance constraints. Therefore, we reason about these three aspects of the design by using specialized analysis and synthesis frameworks that operate with different formalisms. Contracts specifying the interface between components and views help transfer requirements between different frameworks and verify correctness with respect to the full set of requirements. As also shown in Fig. 3, our design space exploration is organized as follows:

FIGURE 3. Electric power system architecture and control design flow and tool chain.

a) From system requirements, we generate a set of requirements for the electric power system architecture (denoted as a contract  $C_T$  in Fig. 3). Safety, connectivity and power flow requirements are expressed as arithmetic constraints on Boolean variables (mixed integer-linear inequalities); reliability constraints are inequalities on real numbers involving component failure probabilities. The trade-off between redundancy and cost can then be explored and an electric power system topology is synthesized to minimize the total component cost while

- satisfying the constraints above. The synthesized topology serves as a specification (assumption) for the subsequent control design step.

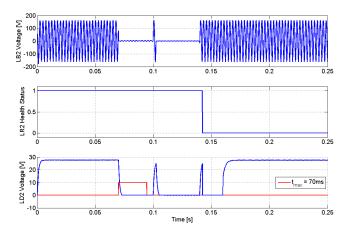

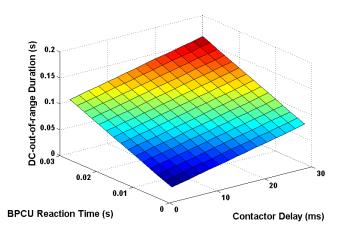

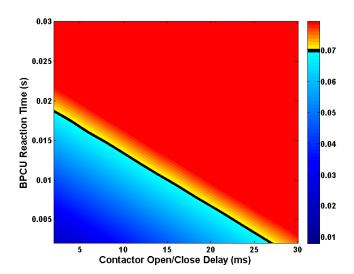

- b) A subset of the original high-level system specifications are translated into LTL formulas for the topology generated in a) (contract  $C_{C,LTL}$  in Fig. 3). Using the results in Section III-E, a reactive control protocol is then synthesized from LTL constructs and made available as one (or more) state machines, satisfying safety and reliability specifications by construction. However, several architectural and real-time constraints (e.g. timing) related to the physical plant and the hardware implementation of the control algorithm are not available at this level of abstraction. Approaches to incorporate timing within reactive control synthesis, by using timed specification languages (e.g., timed computation tree logic) and related synthesis tools (e.g., UPPAAL-Tiga [33]), are currently under investigation. In this work, timing constraints are handled at a lower abstraction level, as detailed below.

- c) The architecture in a) and the controller in b) are executed using continuous-time or hybrid behavioral models to assess satisfaction of (some of) the requirements at a lower abstraction level (contract  $C_{C,STL}$  in Fig. 3). The LTL requirements from b) are also refined into STL formulas (contract  $C'_{C,LTL}$  in Fig. 3). Simulation traces are monitored to verify and optimize the controller using the approach detailed in Section III-F. As an example, an optimal reaction period can be selected in the presence of delays in the switches and under the assumption of a synchronous controller implementation. The resulting architecture and controller pair is then returned as the final design.

We provide details on both topology and control synthesis in Section V and Section VI, including sufficient conditions for their co-design, while guaranteeing that top-level requirements for the controlled system are satisfied.

#### V. ELECTRIC POWER SYSTEM TOPOLOGY DESIGN

We cast the topology design problem as a mixed integer-linear optimization problem. Our goal is to derive an electric power system architecture that satisfies a set of connectivity, power flow and reliability requirements, while minimizing cost and complexity (i.e. number of components) of the overall network.

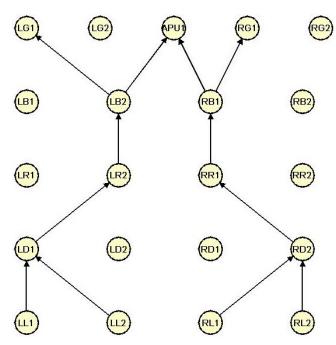

The electric power system architecture is modelled as a directed graph  $\mathcal{G} = (V, E)$ , where each node  $v_i \in V$  represents a component (with the exception of contactors, which are associated with edges) and each edge  $e_{ij} \in E$  represents the interconnection between  $v_i$  and  $v_j$   $(i, j \in \{1, \dots, n\})$ . Therefore, the set of Boolean variables  $\{e_{ij}\}$ , each denoting the presence or absence of an interconnection, are the decision variables for our optimization problem. While connectivity and power flow requirements generate constraints that are linear in the decision variables, or can be straightforwardly linearized, the situation is different for reliability constraints.

# Algorithm 1 Topology Design

**Input**: Topology template  $\mathcal{T}$ , arrays of generator power ratings g, component failure probabilities P and costs w, required reliability  $r^*$ , set of connectivity and power requirements R **Output**: Topology  $\mathcal{G}$

```

while r \ge r^* do \triangleright failure probability [Cost, Cons]=FORMMILP(\mathcal{T}, w, g, R) \mathcal{G}=SOLVE(Cost, Cons) [r, \mathbf{R}_{new}] = RELANALYSIS(\mathcal{G}, P) \mathbf{R} = ADDCONST(\mathbf{R}, \mathbf{R}_{new}) \triangleright add new constraints end while

```

A reliability constraint prescribes that the failure probability of a critical load, i.e. the probability that a load stays unpowered longer than specified because of failures, should be less than a desired threshold. As further discussed in Section V-B, evaluating such a failure probability produces high-order polynomial inequalities in terms of the decision variables. Such constraints would either call for a nonlinear solver or for several symbolic manipulations and linearization techniques, possibly involving large sets of auxiliary variables. Therefore, instead of formulating a single, "flat" optimization problem, we propose an iterative algorithm inspired by the *mixed integer-linear programming modulo theory* approach [34], [35], summarized in Algorithm 1.

The topology design algorithm receives as inputs: (part of) the electric power system platform library  $\mathcal{L}$ , including generator power ratings g, component costs w and failure probabilities P; a topology template  $\mathcal{T}$  with the maximum number of allowed components for each category and their composition rules; the set of requirements, including connectivity constraints, load power and reliability requirements. Reliability requirements are generally specified at critical loads or essential buses; to simplify, in Algorithm 1, we assume that an overall system reliability requirement  $r^*$  is provided, as defined in Section V-B.

A mixed integer-linear program (MILP) generates minimum cost topologies for the given set of connectivity and power flow constraints. The MILP is solved in a loop with a reliability analysis algorithm, which receives as input a candidate topology, evaluates the failure probability of critical loads and implements strategies to improve the reliability, by providing additional constraints for the MILP, until all requirements are satisfied.

The contract for the topology design step can then be expressed as a pair  $\mathcal{C}_T = (A_T, G_T)$ , where  $A_T$  represents the set of topology graphs that conform to the template  $\mathcal{T}$  and are labelled with the generator power ratings  $\mathbf{g}$ , the component costs  $\mathbf{w}$  and failure probabilities  $\mathbf{P}$ .  $G_T$  represents the topology graphs that satisfy the load reliability requirements and power requirements (in nominal conditions). Both  $A_T$  and  $G_T$  can be concretely expressed using mixed integerlinear or nonlinear constraints (originated from probability computations) in the decision variables and the graph model parameters. In what follows, we detail the two key

components of our synthesis flow, namely the MILP formulation function FORMMILP and the reliability analysis function RELANALYSIS.

#### A. MIXED INTEGER-LINEAR PROGRAM FORMULATION

FORMMILP formulates the optimization problem by assuming an initial graph template  $\mathcal{T}$  for the electric power system topology, comprising a maximal number of virtual nodes and edges together with their composition rules. Some nodes and edges are activated during an optimization run to generate a candidate topology. The others remain inactive or can be used in subsequent optimization runs to provide redundant paths, by increasing or reconfiguring the electric power system interconnections until all the reliability requirements are satisfied. The candidate topology resulting from an optimization step is a minimal topology, in which unnecessary nodes and edges are pruned away to minimize the overall network cost, while satisfying a set of connectivity and power flow constraints.

To simplify our notation, we partition the adjacency matrix of  $\mathcal{G}$  into smaller blocks to represent interconnections between subsets of components, as summarized in Table 2. For instance, the interconnections between  $n_{gen}$  generators and  $n_{acb}$  AC buses can be represented by a  $n_{gen} \times n_{acb}$  connectivity sub-matrix denoted as  $\mathbf{M}^{gb}$ . We further assume that any interconnection (edge) between two components is associated to a contactor. Relaxing this assumption entails minor modifications in our formulation to handle contactors as separate nodes in  $\mathcal{G}$ .

**TABLE 2.** Connectivity sub-matrices.

| Variables         | Interconnection       | Dimension                 |

|-------------------|-----------------------|---------------------------|

| $\mathbf{M}^{gb}$ | Generator - AC Buses  | $n_{gen} \times n_{acb}$  |

| $\mathbf{M}^{bb}$ | AC Buses - AC Buses   | $n_{acb} \times n_{acb}$  |

| $\mathbf{M}^{br}$ | AC Buses - Rectifiers | $n_{acb} \times n_{rec}$  |

| $\mathbf{M}^{rd}$ | Rectifiers - DC Buses | $n_{rec} \times n_{dcb}$  |

| $\mathbf{M}^{dd}$ | DC Buses - DC Buses   | $n_{dcb} \times n_{dcb}$  |

| $\mathbf{M}^{dl}$ | DC Buses - Loads      | $n_{dcb} \times n_{load}$ |

The cost function is the sum of the costs of all components (associated with the nodes) and contactors (associated with the edges) used in the electric power system architecture, i.e.

$$\sum_{i=1}^{|V|} \delta_i w_i + \sum_{i=1}^{|V|} \sum_{j=1}^{|V|} e_{ij} \tilde{w}_{ij}$$

(16)

where |V| is the number of nodes,  $w_i$  is the cost of component i,  $\tilde{w}_{ij}$  is the cost of contactor on edge  $e_{ij}$  and  $\delta_i$  is a binary variable equal to one if the component is instantiated in a topology and zero otherwise.

All components and paths in the electric power system need to obey the composition rules in our library. In particular, *connectivity* constraints enforce legal connections among components and are formalized as arithmetic constraints on the Boolean decision variables. As an example, we prescribe that any DC load must be directly connected to only one

DC bus as follows:

$$\sum_{i=1}^{n_{dcb}} M_{i,j}^{dl} = 1 \quad \forall j \in \mathbb{N}, \ j \in [1, n_{load}].$$

Moreover, all DC buses that are connected to the network (e.g. to a load or another DC bus) must be connected to at least one TRU to receive power from an AC bus i.e.  $\forall j \in \mathbb{N}, j \in [1, n_{dch}]$

$$\sum_{i=1}^{n_{rec}} M_{i,j}^{rd} \ge \sum_{i=1}^{n_{load}} M_{j,i}^{dl}, \quad \sum_{i=1}^{n_{rec}} M_{i,j}^{rd} \ge \sum_{i=1}^{n_{dcb}} M_{j,i}^{dd}.$$

All TRUs that are connected to a DC bus must be connected to at least one AC bus, i.e.  $\forall j \in \mathbb{N}, j \in [1, n_{rec}]$

$$\sum_{i=1}^{n_{acb}} M_{i,j}^{br} \ge \sum_{i=1}^{n_{dcb}} M_{j,i}^{rd}.$$

Similarly, all AC buses that are connected to a TRU or another AC bus must be connected to one generator, i.e.  $\forall j \in \mathbb{N}, j \in [1, n_{acb}]$

$$\sum_{i=1}^{n_{gen}} M_{i,j}^{gb} \geq \sum_{i=1}^{n_{rec}} M_{j,i}^{br}, \quad \sum_{i=1}^{n_{gen}} M_{i,j}^{gb} \geq \sum_{i=1}^{n_{acb}} M_{j,i}^{bb},$$

while a rectifier cannot be directly connected to more than one DC bus and to more than one AC bus, i.e.  $\forall j \in \mathbb{N}, j \in [1, n_{rec}]$

$$\sum_{i=1}^{n_{dcb}} M_{j,i}^{rd} \le 1, \quad \sum_{i=1}^{n_{acb}} M_{i,j}^{br} \le 1.$$

Power-flow constraints are used to enforce that the total power provided by the generators in each operating condition is greater than or equal to the total power required by the connected loads. For instance, in normal operating conditions, the power generated on each side should be greater than or equal to the total power required by the loads on that side. On the other hand, when only the APU is active, then it should be capable of powering at least the non-sheddable loads on both sides of the system.

# **B. RELIABILITY ANALYSIS**

As discussed in Section III-A, every library component is characterized by a reliability model estimating the failure probability during its operation. Experimental data on the failure rates of the physical components (e.g. contactors, generators, buses) have been collected over the years and made available in the literature. Failure rates can be related to probabilities as follows. We assume that the time at which a component can fail is a random variable with an exponential distribution, whose parameter  $\lambda$  is the failure rate [36]. Therefore, the probability that a failure is observed in a time interval T can be computed as  $P_{fail} = 1 - e^{-\lambda T}$ . The objective of the reliability analysis function RELANALYSIS is then to compute the probability of composite events of failure in the system, starting from the failure probabilities of its components. We denote as overall system failure F an event in which there is no possibility for any of the available generators to deliver power

to a critical load or an essential bus. Therefore, the overall system failure probability r, also denoted as *reliability level*, is defined as

$$r = \mathbb{P}(F) = \mathbb{P}\left(\bigcup_{k=1}^{m} F_k\right),\tag{17}$$

where  $F_k$  is a failure event at the critical load (or essential bus) j, and m is the total number of critical loads (or essential buses). We assume that when a component fails, it is no longer possible to deliver power from and through that component, i.e. the component becomes an open circuit in the schematic and cannot be recovered. Moreover, failures in different components are considered as independent.

To compute the reliability at a critical load, we adopt an extension of traditional fault tree analysis (FTA) that supports hierarchical composition, similar to the approach in [37]. Besides handling decomposition with respect to the hierarchy of failure influences, our formulation is able to compute failure probabilities directly from the electric power system topology. Our assumption is that the reliability level of an electric power system can be statically determined by its topological structure and the redundancy of the paths used to power a critical load.