Received 27 February 2024, accepted 8 May 2024, date of publication 13 May 2024, date of current version 21 May 2024. Digital Object Identifier 10.1109/ACCESS.2024.3400624

## **SURVEY**

# **Era of Sentinel Tech: Charting Hardware Security** Landscapes Through Post-Silicon Innovation, **Threat Mitigation and Future Trajectories**

## MAMIDIPAKA B. R. SRINIVAS<sup>(D)</sup> AND KONGUVEL ELANGO<sup>(D)</sup>, (Senior Member, IEEE) School of Electronics Engineering, Vellore Institute of Technology (VIT), Vellore, Tamil Nadu 632014, India

Corresponding author: Konguvel Elango (konguvel.e@vit.ac.in)

This work was supported by the Vellore Institute of Technology, Vellore, Tamil Nadu, India.

**ABSTRACT** To meet the demanding requirements of VLSI design, including improved speed, reduced power consumption, and compact architectures, various IP cores from trusted and untrusted platforms are often integrated into a single System-on-Chip (SoC). However, this convergence poses a significant security challenge, as adversaries can exploit it to extract unauthorized information, compromise system performance, and obtain secret keys. Meanwhile, traditional CMOS features have limitations in addressing hardware vulnerabilities and security threats, so promising post-silicon technologies offer potential solutions. Beyond-CMOS technologies offer avenues to fortify hardware security through distinct physical properties and nontraditional computing paradigms. These advancements bolster authentication processes, enhance key generation mechanisms, ensure hardware integrity and fortify resilience against side-channel attacks, hardware Trojans and quantum-resistant cryptography in securing hardware systems. This article provides a detailed review of hardware security, encompassing the identification and mitigation of threats, the implementation of robust countermeasures, the utilization of innovative primitives, countermeasures, various methodologies and distinct features offered by emerging technologies to resist hardware threats. Moreover, strategies to address challenges, explore future directions, and outline plans for achieving further research outcomes have been put forth in this field.

**INDEX TERMS** Dual precharge logic (DPL), fault injection attacks (FIA), hardware wallets (HW), negative capacitance FET (NCFET), measurement-to-disclosure (MTD), spintronics, sense amplifier-based logic (SABL), tamper resistance, temporal majority voting (TMV).

## I. INTRODUCTION

Cyber-attacks have become increasingly sophisticated and persistent, targeting both software and hardware vulnerabilities. The evolving threat landscape in the modern life of digitization necessitates the adoption of hardware security measures. Attackers aim to compromise systems and gain unauthorised access to private information. The threats connected to the major US healthcare data breaches disclosed during the COVID outbreak [1]. This highlights the critical role of hardware security in mitigating such threats. Moreover, the modern design landscape exhibits a growing dependence on various components including,

The associate editor coordinating the review of this manuscript and approving it for publication was Ahmed M. Elmisery<sup>10</sup>.

architectures, intellectual property, and hardware accelerators embedded in SoCs to enhance the performance of the system. This reliance further amplifies the need for robust hardware security measures. With the proliferation of Internet of Things (IoT) devices and interconnected systems, hardware security becomes particularly vital. These devices are extensively deployed in sectors such as critical infrastructure, healthcare, financial transactions and transportation, where the security and integrity of the hardware are of utmost importance. Thus, safeguarding these devices against tampering, unauthorised access, and potential disruptions is crucial, underscoring the necessity of hardware security.

With the rapid proliferation of IoT devices, ensuring security has become imperative. The inherent vulnerabilities in IoT systems necessitate powerful security protocols to protect

© 2024 The Authors. This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 License. For more information, see https://creativecommons.org/licenses/by-nc-nd/4.0/

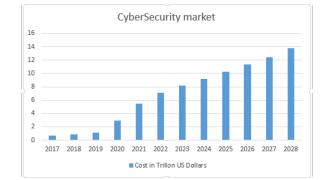

FIGURE 1. Forecast of the cyber security market.

against potential threats and breaches. Therefore, prioritizing ultra-low power consumption and high-speed capabilities, and addressing security concerns has become an essential requirement for IoT devices and systems [2], [3], [4]. In modern times, there has been a significant rise in economic losses resulting from the escalation of cyberspace, hardware assaults and breaches in information and communication systems. The increasing frequency and sophistication of these assaults pose a significant peril to the integrity and security of critical platforms. Consequently, mitigating and preventing cyber and hardware breaches has become a pressing concern for organizations operating in information and communication domains, aiming to safeguard their assets, reputation, and financial stability [5], [6]. Hardware breaches can have significantly more severe consequences compared to cyber security attacks, primarily because software inherently relies presuming that the hardware below isn't compromised. While cyber security attacks can cause disruptions and compromise software systems, hardware breaches have the potential to undermine the foundation on which software operates. This fundamental reliance on uncompromised hardware makes it crucial to prioritize hardware security as any compromise can lead to widespread vulnerabilities throughout the software ecosystem. Therefore, the damaging impact of hardware breaches stems from their ability to undermine the trust and integrity of the underlying hardware, thereby posing significant challenges for ensuring the security and reliability of software systems [7], [8], [9], [10], [11]. As a result, numerous polls have revealed the expense of cyber security as shown in Figure. 1 [12].

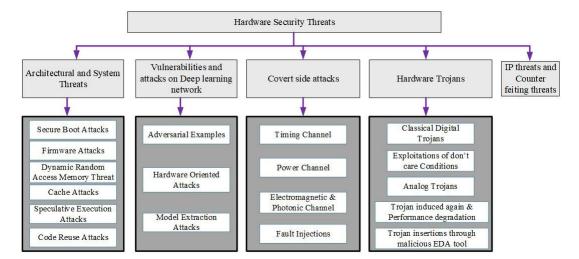

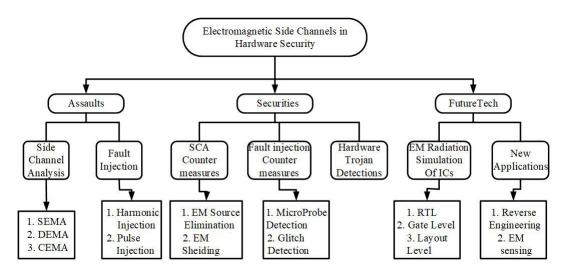

It's important to note that attackers continually evolve their techniques, and new attack vectors may emerge over time and weaken the effective performance and efficiency of hardware systems. The various security attacks impact hardware/software such as Hardware Trojans, supply chain attacks, side-channel attacks, physical tampering, hardware key loggers, electromagnetic and photonic attacks, Direct memory access attacks (DMAA), Hardware Interceptions, Fault injection attacks, malicious firmware, Hardware based crypto-attacks, Bus snooping, counterfeiting of IC, machine learning models are some examples of hardware-related security attacks.

| TABLE 1. List of abbreviations used in this article | TABLE 1. | List of | abbreviations | used | in this | article. |

|-----------------------------------------------------|----------|---------|---------------|------|---------|----------|

|-----------------------------------------------------|----------|---------|---------------|------|---------|----------|

| Abbreviation | Description                                      |

|--------------|--------------------------------------------------|

| CAD          | Computer Aided Design                            |

| CMOS         | Complementary Metal Oxide Semiconductor          |

| SoC          | System on Chip                                   |

| VLSI         | Very Large Scale Integrated Circuits             |

| IP core      | Intellectual property core                       |

| DPL          | Dual Precharge Logic                             |

| FIA          | Fault Injection Attacks                          |

| HW           | Hardware Wallets                                 |

| HSM          | Hardware Secure Models                           |

| ІоТ          | Internet Of Things                               |

| MTD          | Measurement-To-Disclosure                        |

| TMV          | Temporal Majority Voting                         |

| NCFET        | Negative Capacitance Field Effect Transistor     |

| SABL         | Sense Amplifier Based Logic                      |

| DMAA         | Direct Memory Access Attacks                     |

| TRNGs        | True Random Number Generators                    |

| PUFs         | physical Unclonable Functions                    |

| PCM          | Phase Change Memory                              |

| TFET         | Tunnel Field Effect Transistor                   |

| RRAM         | Resistive random-access memory                   |

| CNTFET       | Carbon Nanotube FET                              |

| STT-MJT      | Spin Transfer Torque Magnetic tunnel junction    |

| HyperFET     | Hybrid Phase Transition FET                      |

| FSC-PCs      | Fluorescence Structural Colour Phonotic Crystals |

| TEEs         | Trusted Execution Environments                   |

| SRAM         | Static random-access memory                      |

| NVM          | Non-Volatile Memory                              |

| OS           | Operating System                                 |

| PUF-SSTFs    | PUF-Secure Split Test with functional testing    |

| CSST         | Connecticut Secure Split Test                    |

| STDs         | Spin Torque Diodes                               |

| DPA          | Differential Power Analysis                      |

| SOT          | Spin-Orbit Torque                                |

| SiNW-FET     | Silicon Nanowire-FET                             |

| FPGA         | Field Programmable Gate Array                    |

| PCB          | Printed Circuit Board                            |

| SAR-ADC      | Successive Approximation Register - ADC          |

| CRO-PUF      | Configurable Ring Oscillator PUF                 |

| RACRO-PUF    | Robust Architecture CRO-PUF                      |

In summary, hardware security is essential for protecting data, defending against cyber threats, and ensuring the reliability of systems in real-time applications across industries. It fosters trust, resilience, and compliance with regulations while mitigating risks in the supply chain. By safeguarding against unauthorized access and ensuring regulatory compliance, hardware security enhances the overall security posture of organizations across diverse sectors.

#### **II. LITERATURE REVIEW**

Hardware security plays a pivotal role in real-time contexts by safeguarding sensitive data, thwarting cyber attacks, and bolstering the reliability of systems. It provides resilience against sophisticated threats, ensures compliance with regulations, and mitigates risks in the supply chain. Through features like tamper resistance and secure elements, hardware security maintains data confidentiality, integrity, and availability, bolstering organizational security across various sectors.

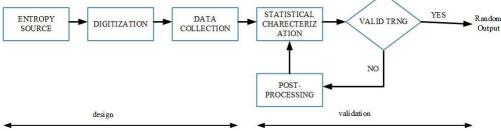

CMOS circuits, designed for stability and consistency, struggle to generate truly random outputs required for True Random Number Generators (TRNGs). While they may exhibit some variability due to environmental noise and process variations, this randomness often falls short of cryptographic standards. Additionally, CMOS circuits are ill-suited for Physical Unclonable Functions (PUFs), as they minimize variations to ensure consistent performance, hindering the diversity needed for effective PUF functionality. Moreover, the sensitive nature of CMOS circuitry and the intricate interplay of electrical signals make them susceptible to side-channel attacks, allowing adversaries to exploit vulnerabilities and extract valuable information.

To overcome these limitations the advantages of post-CMOS technologies in hardware security stem from their ability to address the limitations of traditional CMOS technology while also providing opportunities for the development of more robust, resilient, and future-proof security solutions.

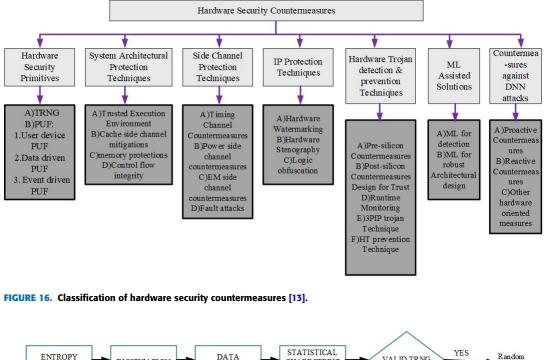

The road map to security devices with the unique features of post-silicon devices has been discussed, along with the most recent design strategies used by designers to address security threats, vulnerabilities, and their solutions [13], [14], [15], [16]. Security experts have been working incredibly hard to create unique hardware security techniques for all various types of above-listed attacks [17], [18], [19], [20], [21], [22].

Addressing the challenges inherent to CMOS technology, only a handful of review papers have explored selective hardware primitives, with little focus on resilience against machine and deep learning models. For the first time, this article delves into recent advancements in device modelling, leveraging improved security features, resistance to emerging threats, and enhanced performance. The overall related works is summarized in Table 2. The aim is to offer state-of-the-art countermeasures for threats against hardware security, paving the way for the development of more robust, resilient, and future-proof security solutions.

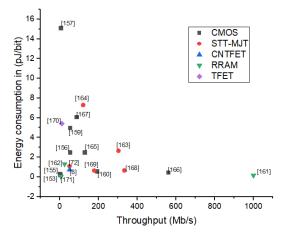

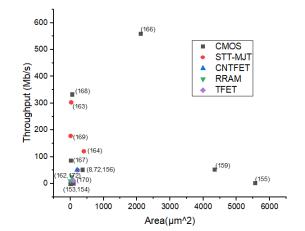

The primary contribution of this paper lies in its exploration of recent advancements in hardware security primitives, particularly focusing on enhanced device characteristics such as RRAM, STT-MJT, NCFET etc. For instance, leveraging RRAM, a TRNG has been engineered to mitigate vulnerabilities to hardware attacks while enhancing throughput and reducing power consumption compared to conventional devices [161] and so forth. Building upon the foundation laid by previous research, the article introduces novel enhancements to security primitives, further fortifying their resilience against machine learning attacks. By shedding light on the symbiotic relationship between hardware security primitives and machine learning attacks, the article contributes to advancing the field's understanding of robust security solutions in the era of evolving cyber threats. Moreover, the article paves the way for the development of more secure and efficient hardware implementations, with implications spanning across various domains, including cybersecurity, IoT and beyond.

The presentation of the article is structured as follows. Firstly, We present a quick explanation of the essential hardware security properties in Section III. Then the distinct qualities and most recent developments in post-silicon technology in section IV. Next describes the hardware security measures that are regularly employed to counter security threats along with current developments to mitigate hardware threats and vulnerabilities with next-generation computing devices which have been listed in Section V. Section VI highlights the recent advancements of machine learning in hardware security. Additionally, some contemporary challenges and prospects in the mentioned areas have been highlighted in Section VII. Section VIII emphasizes an overview and discussion of security modules based on postsilicon devices. Section IX with future research directions. At last, section X ended with the conclusion of this article.

### **III. COMMON HARDWARE SECURITY FEATURES**

For data processing in electronics to be vulnerable to numerous risks and vulnerabilities, it is necessary to have confidentiality, integrity, availability, isolation, reliability, constant time, and quantitative security features in designing Hardware Wallets (HW), and Hardware Secure Models (HSM). Common hardware security properties refer to the key aspects or goals that are typically desired and pursued when designing and implementing secure hardware systems. These properties aim to protect against various threats and vulnerabilities. These security attributes also lay out significant constraints to the verification tools for design. These features aim to help hardware designers and CAD tool developers reduce the time and cost of developing secure products by taking into account the latest advancements in terms of hardware security [13], [23]. Here are some common hardware security properties:

## A. TAMPER RESISTANCE

Tamper resistance is a fundamental hardware security property that aims to avoid unauthorized physical permission to the device and protect it from tampering or reverse engineering. Tamper-resistant hardware employs techniques such as secure enclosures, anti-tamper coatings, sensors, and meshing to detect and respond to tampering attempts, including opening the casing or probing the device. One of the various kinds of security enclosures the forward integrity model is followed by a logging system with tamper-evident, which safeguards the integrity of logging data collected in former times [24]. Attackers may have the ability to alter the historical logging data produced, Yet the tamper-evident system will identify any breach in integrity. Several instances of tamper-evident systems developed with various technologies and applications are discussed [25], [26], [27]. For instance, in anti-tampering coatings, the spray coating technique produced Fluorescence-Structural Colour Photonic Crystals (FSC-PCs) in a limited period by chemically joining fluorescent molecules to colloidal particles, a two-sided security card with different information displayed on each side depending on the amount of light. Data encryption and reading are both possible during the light-switching process,

| year &<br>Ref    | Post-CMOS technologies dis-<br>cussed                                                                                             | Hardware Primitives Discussed                                                                                                                                                                                                                              | Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Research Gap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Future Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2016<br>[337]    | Nano Electro Mechanical Sys-<br>tems (NEMS) and Carbon Nan-<br>otube (CNT)                                                        | Hardware Trojans,Side channel At-<br>tack Analysis,Camouflaging                                                                                                                                                                                            | The methodology addresses IC vulnera-<br>bilities, resilience against hardware Tro-<br>jans, power-based side-channel attacks,<br>and IP reverse-engineering via camouflag-<br>ing on emerging technologies.                                                                                                                                                                                                                                                                                                                                                              | Not Discussed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Future research may validate findings<br>with IC measurements, characterize<br>emerging devices, and develop methods<br>for consistent device traits amid process<br>variations, bolstering resilience against<br>security threats.                                                                                                                                                                                                                                                                                       |

| 2017<br>[338]    | PCM,Graphene,CNTs                                                                                                                 | PUFs,TRNGs,Design for Anti-<br>Tamper, Anti-Counterfiet, Anti-<br>Reverse Engineer                                                                                                                                                                         | The methodology explores features<br>and security applications of emerging<br>nanoscale devices (PCM, graphene,<br>CNTs), addressing challenges,<br>limitations, and providing a roadmap. It<br>also highlights open questions and future<br>research in nanoscale security.                                                                                                                                                                                                                                                                                              | Not Discussed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | paper suggests overcoming manufactur-<br>ing challenges, ensuring security against<br>attacks and data leaks, and promoting<br>multidisciplinary collaboration for in-<br>formed device design.                                                                                                                                                                                                                                                                                                                           |

| 2019<br>[339]    | EmergingFlash,PCM,<br>RRAM,Spintronics                                                                                            | PUFs                                                                                                                                                                                                                                                       | The methodology discusses security ser-<br>vices for connected devices and IoT, con-<br>sidering architectures with mature and<br>emerging technologies. It emphasizes ex-<br>perimental works with a review of security<br>and performance metrics.                                                                                                                                                                                                                                                                                                                      | The paper identifies gaps in resilience<br>to probing attacks, calls for more exper-<br>imental research to address evaluation<br>challenges and model various attacks,<br>and advocates for large-scale NVM-<br>based PUFs fully integrated with CMOS<br>circuits, resistant to noninvasive attacks.                                                                                                                                                                                           | Not Discussed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2021<br>[13]     | <ul> <li>(i) spintronics, (ii) memristors,</li> <li>(iii) CNT (iv) nanowires and (v)</li> <li>3D and 2.5D integration.</li> </ul> | Reverse         Engineer-<br>ing,Tampering,Theft           Hardware Trojans,Physical Attacks,<br>Data Security, PUFs,TRNGs,Logic<br>Locking,Split         Manufacturing,<br>Camouflaging and Root of Trust                                                 | The methodology surveys hardware secu-<br>rity, assesses emerging technologies, ex-<br>plores their role in improving security,<br>highlights challenges, and evaluates their<br>alignment with hardware security needs                                                                                                                                                                                                                                                                                                                                                   | Integrating security early for emerging<br>technologies in CMOS integration pro-<br>motion.Identifying weak links in hybrid<br>security scheme implementations                                                                                                                                                                                                                                                                                                                                  | Not Discussed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2021<br>[14]     | Not Discussed                                                                                                                     | Reverse Engineering, Tampering,<br>Theft of IP, Hardware Trojans,<br>Physical Attacks, Data Security,<br>PUFs, TRNGs, Side Channel At-<br>tacks(Timing, EM, Power, Phonotics),<br>Logic Locking, Split<br>Manufacturing, Camouflaging<br>and Root of Trust | The methodology covers protection<br>techniques, design tools for detecting<br>hardware vulnerabilities, and the<br>importance of understanding hardware<br>security threats. It discusses the need<br>for better design tools, common security<br>properties, hardware attacks, security<br>mechanisms, and secure hardware design<br>tools from academia and industry.                                                                                                                                                                                                  | Security in hardware design needs im-<br>provement, with better tools, standard-<br>ized models, and effective metrics nec-<br>essary. Integrating security alongside<br>traditional parameters presents promis-<br>ing but challenging research directions.                                                                                                                                                                                                                                    | Integrate security into IoT/CPS system-<br>atically, develop tools for balancing se-<br>curity with other parameters, ensure<br>sensor/actuator security, address COTS<br>component security, secure AI/ML tech-<br>niques, and establish accessible security<br>metrics.                                                                                                                                                                                                                                                 |

| 2021<br>[15]     | TFET,PCM.CNTFET,<br>STT_MJT,RRAM, HyperFET                                                                                        | PUFs,TRNGs, Side Channel<br>Analysis(EM,Power,Phonotics),<br>Hardware Obfuscations                                                                                                                                                                         | The methodology discusses nanoelec-<br>tronic device principles, CMOS chal-<br>lenges, emerging nanotechnologies' bene-<br>fits, and analyzes post-CMOS device per-<br>formance in countermeasures.                                                                                                                                                                                                                                                                                                                                                                       | The paper identifies gaps in device mod-<br>els, circuit availability, metrics for secu-<br>rity assessment, engineers' knowledge,<br>and post-CMOS device security study. It<br>also discusses challenges and benefits of<br>post-CMOS devices for hardware secu-<br>rity.                                                                                                                                                                                                                     | The paper recommends researching in-<br>tegrated device architectures to optimize<br>beyond-CMOS device benefits, focus-<br>ing on improving tunneling efficiency in<br>TFETs. It highlights the potential of NC-<br>TFET and PC-TFET for lower energy<br>consumption and steeper subthreshold<br>swing without leakage degradation.                                                                                                                                                                                      |

| 2023<br>[340]    | Not Discussed                                                                                                                     | Power analysis attack on AES de-<br>signs                                                                                                                                                                                                                  | The methodology entails researching<br>countermeasures to mitigate AES<br>vulnerabilities against side-channel<br>attacks, particularly focusing on power<br>analysis in IoT devices. It involves<br>examining security metrics and design<br>overheads of countermeasures employing<br>hiding or masking techniques, with<br>a prerequisite understanding of AES<br>algorithm and Galois field theory. The<br>study is specifically scoped to address<br>power analysis attacks targeting IoT<br>devices secured with AES encryption.                                    | Research Gap not identified                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Future research should prioritize<br>strengthening AES designs against<br>evolving threats such as EM-based<br>attacks, leakage power analysis<br>attacks, and frequency-domain CPA.<br>Additionally, there's a necessity to<br>investigate methods for reducing design<br>overheads without compromising<br>security levels in countermeasure<br>designs.                                                                                                                                                                |

| 2023<br>[341]    | Not Discussed                                                                                                                     | Microarchitectural Side-Channel<br>Threats                                                                                                                                                                                                                 | The article encompass presenting a com-<br>prehensive overview of microarchitecture<br>security research efforts, introducing a<br>classification scheme for recent research,<br>providing extensive coverage of published<br>works from the past five years, and iden-<br>tifying areas of active and less-explored<br>research. Additionally, the paper aids in<br>the security-oriented architectural process<br>by categorizing relevant primary studies<br>into Metrics, Modeling, and Assessment;<br>Design flow and Synthesis; Verification;<br>and Miscellaneous. | The research identified gaps in consol-<br>idating current microarchitecture secu-<br>rity research and in comparing studies<br>due to methodological variations. Ad-<br>ditionally, in highlighted the need for<br>improved security in trusted comput-<br>ing mechanisms like Intel SGX with-<br>out sacrificing performance and empha-<br>sized the ongoing challenge of balancing<br>system performance and security amidst<br>methodological limitations in systematic<br>mapping studies. | Identified gaps include outdated efforts<br>in compiling microarchitecture security<br>research and challenges in comparing<br>works due to diverse methodologies.<br>There's a need for enhanced security<br>in trusted computing mechanisms like<br>Intel SGX with minimal performance<br>impacts. Ongoing research emphasizes<br>the challenge of balancing system per-<br>formance and security. Methodological<br>hurdles in mapping studies underscore<br>the need for improvement in study qual-<br>ity and scope. |

| 2023<br>[342]    | Not Discussed                                                                                                                     | only on Arbiter-PUFs                                                                                                                                                                                                                                       | The methodology includes implementing<br>the fundamental Arbiter PUF design on<br>ZedBoard to assess its performance under<br>various response lengths. Furthermore, it<br>involves scrutinizing the design, compo-<br>nents, attributes, and susceptibilities to<br>machine-learning attacks.                                                                                                                                                                                                                                                                            | The research identified gaps in consol-<br>idating current microarchitecture secu-<br>rity research and in comparing studies<br>due to methodological variations. Ad-<br>ditionally, it highlighted the need for<br>improved security in trusted comput-<br>ing mechanisms like Intel SGX with-<br>out sacrificing performance and empha-<br>sized the ongoing challenge of balancing<br>system performance and security amidst<br>methodological limitations in systematic<br>mapping studies. | Future research directions in PUF tech-<br>nology may involve investigating Com-<br>posite PUFs, combining RO PUFs and<br>APUFs, creating digitized variants of<br>APUFs such as Mem-APUF, and explor-<br>ing composite PUF configurations like<br>LP-PUF.                                                                                                                                                                                                                                                                |

| Proposed<br>Work | TFET,PCM,CNTFET, STT-<br>MJT, Silicon Nanowire,<br>Memristors,NCFET,<br>HyperFET                                                  | TRNGs, PUFs(Ring<br>Oscillator,Arbiter, Strong,Weak,<br>Memory based PUFs),Side<br>Channel Analysis(Power,<br>EM,Timing),Hardware Trojan<br>and IP protection(Hardware Water<br>marking, Logic Obfuscation, Split<br>Manufacturing)                        | The methodology covers nanoelectronic<br>device principles, emerging nanotech-<br>nologies' benefits, recent advancements<br>in device level, and analyzes post-CMOS<br>device performance in countermeasures.<br>It includes protection techniques, high-<br>lights an understanding of hardware secu-<br>rity threats, and discusses common secu-<br>rity properties, attacks, and mechanisms.<br>Additionally, it explores hardware primi-<br>tives resilient to machine and deep learn-<br>ing models in TRNG, PUFs, and side-<br>channel attacks.                    | Discussed in "Challenges and opportu-<br>nities in hardware security using emerg-<br>ing devices" section                                                                                                                                                                                                                                                                                                                                                                                       | Discussed in "Future research direction section" .                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## TABLE 2. Overview of the proposed work with respect to previous works in Beyond-CMOS for hardware security.

which can be used to present completely distinct information. The FSC-PCs, which have a quick and easy construction procedure and special optical characteristics, have enormous potential for data display and anti-counterfeiting [28]. The method makes use of temperature readings for evaluation, where it is desirable to lessen reliance on external measuring apparatus to facilitate the integration of embedded testing and activity monitoring. Over the lifespan of a chip. As a first step toward achieving HT detection through on-chip power monitoring with a focus on temperature-based analysis, a completely differential temperature sensor was introduced in this paper [29]. A temperature sensor designed with full differential configuration that uses chopper stabilized amplification was developed by modifying the input currents in the differential configuration of BJT being utilized as temperature sensors, the suggested two-stage trans-impedance there has been a modification to the amplifier architecture built utilizing a chopping technique to mitigate flicker noise, the signal-to-noise ratio has greatly improved, according to simulation data [30].

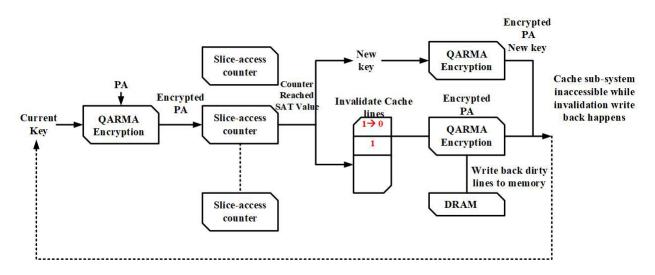

#### **B. SECURE KEY STORAGE**

Secure key storage is critical for cryptographic operations and maintaining the confidentiality and integrity of sensitive data. Hardware security properties often include mechanisms for securely generating, storing and managing cryptographic keys within the hardware device. These mechanisms can involve dedicated secure elements, hardware-based key storage, or Trusted Execution Environments (TEEs) that provide secure isolation for key management. Farha et al. [31] have made experiments and improvements of SRAM-PUF, and the use of PUF to secure Zig Bee devices. The authors have demonstrated the efficacy of SRAM-PUF in safeguarding keying materials of Zig Bee devices, Whether through the generation of secret keys or the secure storage of secret keys in the NVM of the local device, with no requirement for the installation of additional equipment. The proposed HSM in [32] eliminates by storing cryptographic keys and the susceptibility to attacks against these stored keys is eliminated. The HSM generates the cryptographic key from sub-components exhibiting similar to multi-factor authentication, where each factor is an independent authenticator. The proposed scheme improves security by integrating physical security into digital security. In other words, as long as either the crypto provider device stays secure or the human aspect is maintained component stays protected, maintaining the integrity of the system security. The authors in [33] implemented a secure monitor for isolation and capability management, which provides data-flow isolation and controlflow isolation to protect a COLONY's data within the context of memory and CPU and prevent untrusted system software preventing the circumvention or incomplete execution of COLONY's code. The paper also assigns capabilities to each instance of COLONY to access essential system-level semantics, do not protect keys from extraction when the key is at rest and stored in an inactive state. However, the work produced by Han et al. [34] provided uses with multiple security features, such as Intel SGX and HSM commands, to set up a secure channel and restrict to regulating key attributes of keys within an HSM to control key usage. ScaleTrust also applies authenticated encryption to all keys during transmission, which prevents sensitive data leakage and defends against active attacks manipulating data messages. Additionally, Scale Trust guarantees encryption for all keys between the enclave and the HSM, which makes it resistant to eavesdropping.

#### C. SIDE-CHANNEL ATTACK RESISTANCE

Side-channel attacks leverage unintended information leakage during cryptographic operations, such as power consumption, electromagnetic emissions, or timing measurements. Hardware security properties aim to mitigate side-channel attacks by implementing countermeasures such as power analysis resistance, electromagnetic shielding, randomization techniques, and constant-time algorithms to eliminate or minimize the leakage of sensitive information. The proposed technique from the paper [35] uses an on-demand current equalizer modulating the equalization current to obscure information about current leakage of the Advanced Encryption Standards (AES) engine. Additionally, the on-demand current equalizer is proposed to incorporate a randomization operation to further enhance the Power Side Channel Attacks (PSCA) resistance of the cryptographic engine, unlike former works that enable the randomization process in the Integrated Voltage Regulator (IVR). This approach can add additional obfuscation to the current profile of the encryption engine to enhance its PSCA resistance without incurring any performance penalty.

#### D. HARDWARE AUTHENTICATION

Hardware authentication properties focus on verifying the authenticity and integrity of the hardware device itself. These properties often involve hardware-based secure elements or secure boot processes that ensure only trusted and authorized hardware components are used and that the device hasn't been tampered with or modified. The method in the paper [33] involves modifying the boot loader to load a secure monitor instead of a secure OS. The secure monitor initiates the protected environment and loads a secure OS to memory. The secure OS initiates the secure environment and shifts to the normal environment to execute a kernel loader. The kernel loader initiates the loading of a non-secure operating system and executes it. Upon loading each binary image, the loader computes the checksum to ensure the integrity of the image. The booting order remains static, with the secure OS running first to initialize the platform. The three properties that are enforced require that the boot loader is loaded from a tamperresistant ROM, the secure OS is loaded and initialized before the non-secure OS, and every time a loader loads a binary

image, it computes the checksum to verify the integrity of the image.

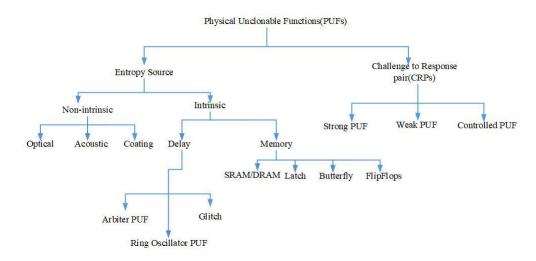

## E. PHYSICAL UNCLONABILITY

Physical Unclonability is a property that leverages unique physical characteristics or manufacturing variations in the hardware to provide device identity and protection against cloning or counterfeiting. As semiconductor industry's globalization has produced a convoluted supply chain comprising numerous contract manufacturers in various nations. Outsourced Semiconductor Assembly and Test (OSAT) facilities are now producing counterfeit semiconductors, overbuilding chips from foundries and other security-related issues. Hardware security properties can include measures such as incorporating PUFs or other hardware-based techniques to ensure each device has a unique identity that cannot be easily replicated. So the PUF-SSTF scheme incorporates PUFs to generate random numbers that are used to scramble the test response and generate functional keys. PUFs are used to generate an enormous number of legitimate functional keys for a millions of IoT nodes, which makes it difficult for attackers to clone or counterfeit the ICs. The PUF-based SSTF scheme is a reliable solution for the identity management of IoT devices post-deployment in the field. The security analysis for PUF-SSTF covers both test response locking and functional keys across recognized benchmark circuits, and the results obtained are comparable with the CSST scheme [36].

## F. SECURE COMMUNICATION INTERFACES

Hardware security properties encompass secure communication interfaces, including encryption, authentication, and secure protocols for data transfer. These properties focus on protecting data integrity and confidentiality during communication between hardware devices or with external systems, in many cores with shared memory, the Gossip-Network on chip (Gossip-NoC), Reinbrecht et al. [37] employ Secure Zones (SZs) as the defence strategy. The traffic monitors added by the authors enable the Gossip-NoC routers to switch from XY to YX when they see unusual activity. Additionally, Grammatakakis et al. [38] secure the system from unwanted access to shared memories by utilizing firewalls inside the Network Interfaces (NIs). Only specific memory locations are permitted access thanks to the firewall configuration. Attack attempts are recorded by the NI and sent to the Security Event Correlation (SEC) agent, a thread on the host CPU. The Network-On-Chip (NoC) and firewall are installed in the programmable logic on a Zed board with an ARM Cortex A9 (host CPU) in use by the authors. The SEC oversees the protective measures [39].

## G. SECURE DEBUGGING AND TESTING

Secure debugging and testing properties involve mechanisms that protect against unauthorized access, tampering, or exploitation during the development, testing, and maintenance phases. Hardware security properties may include secure access control, encrypted debug interfaces, and secure testing processes to prevent unauthorized individuals from accessing sensitive areas of the hardware or injecting malicious code during debugging or testing. The great controllability and observability that the JTAG standard, also known as IEEE 1149.1, offers for ICs makes it useful for debugging and testing. It provides good observability and controllability for users to access the Test Data Registers (TDRs) and Boundary-Scan Cells (BSCs) through the Test Access Port (TAP). As a result, users can test and debug ICs using a variety of techniques, including postsilicon debugging, chip reconfiguration, verification, power management, and clock control [40].

## H. SECURE BOOT AND FIRMWARE INTEGRITY

Secure boot and firmware integrity properties aim to ensure that the device starts up with trusted and unmodified firmware or software. These properties include measures such as secure boot processes, firmware encryption, digital signatures, and secure firmware update mechanisms to protect against unauthorized modifications or the installation of malicious firmware. For embedded devices, firmware encryption can stop the firmware from being read to copy the device into a fake or to steal the creator's intellectual property. Additionally, the integrity is protected to prevent an attacker from maliciously altering the firmware. In [41] illustrates a cryptographic concept for implementing Secure Boot capabilities using the inherent features of a particular hardware device.

In, summary FSC-PCs promise improved tamper resistance, while fully differential temperature sensors show potential for detecting hardware Trojans. ScaleTrust's secure key storage addresses insider threats and scalability, focusing on optimization and advanced encryption. Additionally, lightweight power side-channel attack protection utilizes on-demand current equalizers for enhanced key resistance. Trusted execution environments like COLONY ensure hardware authentication, while integrating PUFs enhances IoT semiconductor security. Future efforts focus on optimization and advanced designs for stronger security and resilience. These are some of the common hardware security properties that help mitigate various threats and vulnerabilities. Implementing these properties contributes to building robust and secure hardware systems that can withstand attacks and protect sensitive data and functionality.

## IV. UNIQUE CHARACTERISTICS AND MOST RECENT ADVANCEMENTS IN POST-SILICON TECHNOLOGY

## A. TUNNEL FIELD EFFECT TRANSISTOR (TFETS)

Everyone is indeed required with low-power application devices and inexpensive transistors are essential for the technological world of today. A 3 nm MOSFET nanoelectronic device has just been created by investigators. Even though MOSFET reduces size and power consumption, there are still

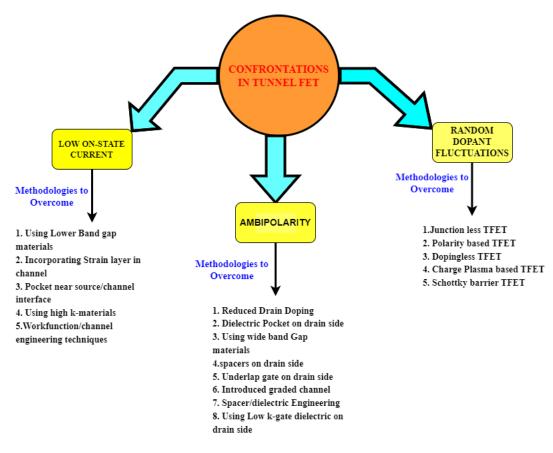

FIGURE 2. Confrontations and possible solutions.

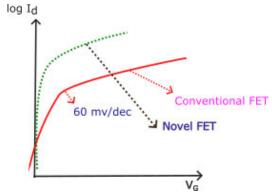

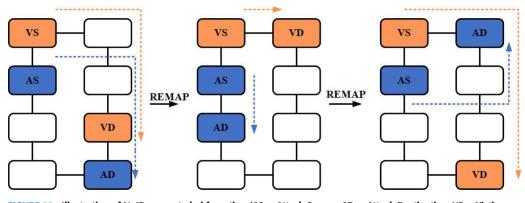

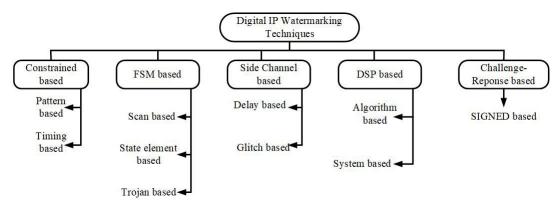

certain problems because of Short Channel Effects (SCEs) like a hot electron, channel length modulation, leakage current, off-state current, threshold voltage roll-off, subthreshold slope is more than 60mv/dec, impact Ionization, Drain Induced Barrier Lowering (DIBL), and some other processes. Energy efficient TFETs are regarded as a promising technology for future generation circuit devices and hardware security applications in contrast to the conventional MOSFET with impeccable characteristics. Having a low sub-threshold swing < 60mv/dec of an established limit, which implies that they can more quickly transition between the current on and off phases, is advantageous for low-power hardware security applications because it permits operation that is both energy-efficient and has a sufficient level of performance. Because the Ion and Ioff currents weren't improved simultaneously, our various classic heterojunction TFETs couldn't fulfil the demands for the better performance of TFETs, but with a Near Broken-Gap Heterojunction (NBGH) at the source/channel interface, a linearly graded channel component and a novel Graded-Channel Heterojunction TFET (GCH-TFET) [42] is presented to aid in the use of IOT applications [43] and still there are many engineering techniques used for various applications in all ways.. Comparing TFETs to traditional CMOS transistors surpasses the restrictions imposed by the CMOS transistor, Because of this reason it has gained interest among researchers. The quantum tunnelling process in the TFETs, namely band-toband tunnelling (BTBT) across the source-channel interface, which decreases the short-channel effects and improves the Subthreshold Slope (SS) lower than 60mv/dec [44], [45]. Inspite of the advantages mentioned above TFET also have drawbacks such as low-on current, ambipolar conduction, and random doping fluctuations. Many researchers have proposed several techniques to overcome these shortcomings in TFETs. The possible challenges and solutions for these particular drawbacks are shown in Figure.2 [46], [56]. The other side of TFET also has some special characteristics that may make them less vulnerable to specific side-channel attacks, in the work demonstrated with the TFET SABL makes it less susceptible to static power side-channel intrusions [47] and it can be used in the neuromorphic computing like Spiking Neural Networks (SNNs) based on TFET neurons are presented for pattern recognition applications, showcasing its great advantage on energy effectiveness [48]. Still, TFET can be explored to the strong hardware secure designs because of its peculiar characteristics like side-channel attacks counter measures [49], hardware primitives like physical unclonable methodologies [50], true random number generators [51], hardware obfuscations [52] and hardware Trojans [53], [54], [55].

Emerging hardware technologies like TFETs and spinbased devices offer improved hardware security over CMOS. TFETs resist side-channel attacks and reduce power consumption, though facing challenges in low ON-state current and complexity. Similarly, TFET-based current mode logic (CML) reduces power consumption and resists attacks like DPA, but encounters fabrication complexity and scalability issues. Spin-based devices provide non-volatile data integrity but are vulnerable to magnetic field manipulation. Future research aims to optimize TFET and spin-based device designs and develop encryption techniques to enhance system security in IoT and other applications.

## **B. HYBRID PHASE TRANSITION FET (HYPERFET)**

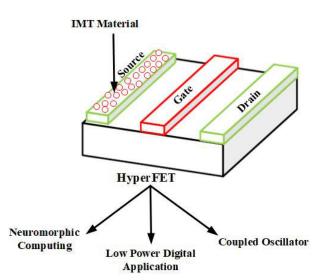

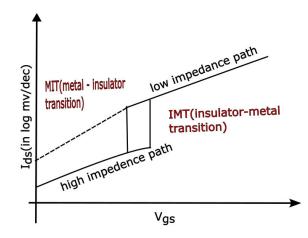

The testability, dependability, and safeguarding of electronic systems are critical challenges for the protection of human life with the rapid growth of advanced computing technologies in all electronic domains. But for the past few decades, power has become a significant barrier for very large integrated circuits. The scaling of CMOS technologies in the past allowed for the payment of functionality increases in chips by lowering the supply voltage and lowering transistor capacitance. This opens it for the researchers to find new paradigms, new physics and new mechanisms to overcome the limitations of conventional CMOS this helps to evolve with a new emerging technology called HyperFET. The working functionality of this device starts with the novel operation i.e. the strong electron-electron interactions present, transition metal oxide materials can exhibit a variety of phases with vastly different electrical, magnetic, structural, and thermal properties. Electronic controls that allow for reversible control of these phase transitions may lead to whole new devices with capabilities beyond those of current semiconductor technology. At approximately  $670^{\circ}$ , a metal-insulator transition (MIT) takes place in the transition metal oxide material  $VO_2$ . By connecting  $VO_2$  to the source of traditional CMOS devices, hyperFET devices have recently been shown. These HyperFET showed a sharp switching slope that was below the ambient temperature Boltzmann switching limit of 60 mV/dec [57], [58], [59]. This new evolution of functionality opens the applications in domains like low-power digital applications [60], [61], [62], neuromorphic computing, coupled oscillators [63], hardware security applications [64] shown in Figure.3.

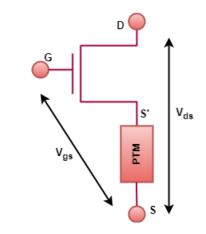

It is observed and demonstrated that CMOS technologies are found to have various disadvantages in terms of power density and energy resources because of technology scaling, given the impossibility of obtaining lower threshold voltages without causing significant leakage currents. So, an alternative emerging device has shown to overcome that limitations of the traditional transistor, called HyperFET. It contains the Phase Transition Material (PTM) connected to the source terminal of FET as shown in Figure. 4. The PTM will result in the sudden high impedance (insulator) - low impedance (metal) transitions to increase the  $I_{on}$  current and to reduce  $I_{off}$

FIGURE 3. Cross-sectional view of HyperFET and its applications.

FIGURE 4. HyperFET [60], [61], [62], [63], [64], [65].

FIGURE 5. General I -V characteristics [60], [61], [62], [63], [64], [65].

current which helps to decrease the SS. In the insulating phase in the absence of electrical stimulation, PTMs often stabilize. The current flowing through the PTM grows linearly as a voltage ( $V_{gs}$ ) is applied, as demonstrated by the I - V curve in Figure. 5.

FIGURE 6. General I -V characteristics [60], [61], [62], [63], [64], [65].

HyperFET circuits reduce power consumption and enhance hardware security, but novel materials and design approaches may introduce vulnerabilities. Challenges persist in balancing performance and security for wearable and IoT applications. PTM modulated HyperFETs offer higher ON current and steep sub-threshold curves, requiring meticulous parameter optimization. Similarly, AlGaN/GaN phaseFETs with ALD VO<sub>2</sub> resistors provide ultralow leakage and steep sub-Boltzmann switching but face fabrication complexity and compatibility issues. Despite potential advantages, emerging devices like HyperFETs encounter limitations in maturity, cost, and compatibility.

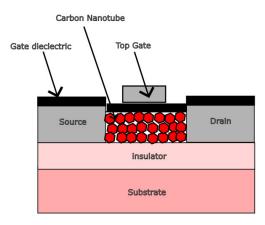

## C. CARBON NANOTUBE FET (CNTFET)

The area and power-delay-product (PDP) for CNTFETs have undergone significant improvements over MOS devices, which renders them enticing to MOS competitors. Carbon atoms compose the internal structure of hollow shapes and cylindrical nanotubes that are referred to as CNTs in a hexagonal lattice configuration. Conceptually, they resemble graphene sheets rolled into tubes, where graphene constitutes a monolayer of carbon atoms organized in a two-dimensional honeycomb pattern. CNTs exhibit varying diameters and lengths and are categorized mainly as Single-Walled Carbon Nanotubes (SWCNTs), featuring a solitary graphene layer, and Multi-Walled Carbon Nanotubes (MWCNTs), which comprise multiple layers of graphene tubes nested akin to Russian nesting dolls. Due to their distinctive structure, CNTs showcase remarkable mechanical, electrical, and thermal attributes, positioning them optimistically across a spectrum of applications encompassing electronics, materials science, and nanotechnology. The cross-sectional view of CNTFETs is shown in Figure. 6. Depending on how the carbon atoms organize themselves, CNTs are likely to be classed into two groups: metallic (m-CNTs) or semiconductor (s-CNTs). The non-zero band gap energy found in s-CNTs can be taken advantage for the production of CNTFETs, which are compatible with adding to silicon MOSFETs fabrication process. The CNT has been grown on a surface and plays out as a channel underneath the control via a gate. Although the CNT region between the source and drain electrodes is fervently doped, the CNT region underneath the gate is undoped. The features of these CNFETs are likely to be the same as CMOS functionality as well as the regular fabrication process. In CNTFET the mobility of charge carriers is the same which helps the voltage transfer characteristics be symmetrical. Apart from that, the diameter of the CNTs can be use for figuring out the threshold voltage of a CNTFET.

$$DCNT = (\frac{\sqrt{3}a_0}{\pi})(\sqrt{n^2 + m^2 + nm})$$

(1)

A CNT's functionality may differentiate between metallic and semiconductors relying on its chirality (n, m). The diameter of CNT can be measured as shown in the above equation (1) where  $a_0$  is the interatomic distance between two carbon atoms. The CNT becomes metallic when n-m = 3K (K  $\epsilon$  Z) and n = m; otherwise, it seems a semiconductor and can be employed as the channel region of a Nanotube-based device [66]. By the variation in operational characteristics between a metallic source/drain and the CNT, multiple kinds of CNTFETs have since been evolved, all showcasing a high  $I_{ON}/I_{OFF}$  ratio [67], [68]. There is no guarantee that perfect alignment of the CNTs during the fabrication process is inevitable. Misaligned CNTs and metallic CNTs provide critical challenges for CNTFET circuits which gives improper functionality to designed circuits. And some other certain inherent variations like CNT-chirality, CNT-diameter, inter-CNT spacing, transistor width, gate pitch, gate-dielectric thickness, gate height, and dopant content [69], [70] These inherent variations in the CNFETs have been taken advantage to the design of hardware security models like TRNGs [72] and PUFs [71]. Since carbon nanotubes possess low off-current tendencies and can serve as the channel connecting both the source and the drain in CNTFETs, they harness less power. Further lessening consumption of power is due to the fact that no current flows across the source back to the drain which employs the design for low-power applications in contrast to the traditional CMOS [73]. This advantage of CNTFET is used in strengthening the side channel attacks [74].

Integrating the Lorenz chaotic system into CNT-PUF designs enhances security against machine learning attacks. However, PUFs based on CNTFETs face challenges such as manufacturing variability and susceptibility to side-channel attacks, requiring robust encryption and key management solutions. Despite offering higher speed and lower power consumption, CNTFET technology presents security risks due to process variations and manufacturing defects, necessitating tailored solutions for enhanced hardware security.

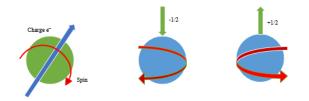

#### **D. SPINTRONICS**

Spintronics, short for "spin transport electronics," revolves around the manipulation of electron spin in electronic devices. It expands on traditional electronics by harnessing both electron charge and spin for various applications.

FIGURE 7. Basic orientation and notation of charge used in spintronics.

In spintronics, electron spin a quantum property analogous to intrinsic angular momentum is pivotal. In numerous manners, spintronics diverges in structure compared to CMOS technology to be put to use in a broad spectrum of applications. Firstly Spintronics utilizes spin-polarized currents where electrons possess preferred spin orientations. The spin orientation and its notation are represented in Figure. 7. This polarization can be controlled using magnetic fields. Secondly, materials with efficient spin transport properties are used, enabling the propagation of spin information over extended distances. Thirdly electron spin is manipulated through mechanisms like magnetic fields or spin-orbit interactions, allowing for control and switching between spin states. Fourthly spin-polarized electrons are injected into materials, with changes in spin orientation detected. This forms the basis of data writing and reading in devices. Finally, in the applications comprising ferromagnetic layers separated by an insulating barrier, MTJs serve as non-volatile memory in applications like MRAM, in the recent advancements in response to the von Neumann bottleneck challenge, an innovative approach has been explored replacing conventional computing architectures incorporating sophisticated sensing circuits and autonomous logic processing units by adopting a write-in-memory logic paradigm using memory cells. Nevertheless, this approach faces the drawback of heightened energy consumption for writing compared to the established reading energy consumption. To address this issue, a solution is proposed an ultra-low-power, highspeed In-Memory Computing (IMC) unit founded on fieldaccelerated spin-orbit torque (SOT) magnetic random access memory (MRAM), leveraging voltage-controlled magnetic anisotropy (VCMA). The study delves into the magnetization dynamics of the device by solving a tailored Landau-Lifshitz-Gilbert equation [83] through a physics-based compact model. This newly suggested MRAM architecture is put to the test for operations pertaining to Boolean logic and a non-volatile full-adder (NVFA), showing its potential to mitigate energy challenges while enabling advanced computing functionalities [75]. Spin FETs blend traditional transistor structures with spin effects, introducing novel logic and memory functions and these generate microwave signals via angular momentum transfer and find use in RF and microwave technologies, the work introduced was a concise electrical model for Spin-Torque Diodes (STDs) utilized as continuous-wave (CW) radio-frequency (RF) detectors. This model integrates the nonlinear resistance of the STD junction by assessing its current-voltage (I-V) behaviour, incorporates the input and output impedance of the STD, and factors in the bandwidth and the impact of spin-torque gain based on RF input power [76]. Leveraging spin for advanced logic gates and qubits, with implications for computing advancements [78]. Spintronics memristors blend the scalability of spin-transfer torque devices with the non-volatile features characteristic of memristors. This combination fulfils the demands of robust data processing that necessitate high-speed, low-power, & scalable quantum computation (QC) [77]. Spintronics offers advantages such as reduced energy consumption, faster data processing, and non-volatile memory. Its transformative potential spans memory devices, processors, sensors, and communication systems, by leveraging electron spin properties for innovation.

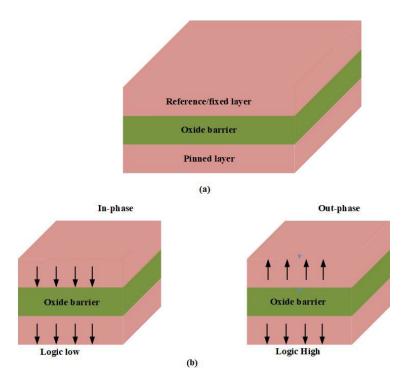

## 1) SPIN TRANSFER TORQUE MAGNETIC TUNNEL JUNCTION (STT-MJT)

STT-MTJ is a specific kind of spintronic technology of that falls under the umbrella of spintronics. It entails employing spin transfer torque for regulating the magnetic moments' orientation upon an MTJ. Two ferromagnetic layers have been separated from one another via an insulating tunnelling wall in an MTJ as shown in Figure.8. The tunnelling current, which is capable of being utilized for interpreting data in binary formats, gets impacted by the relative direction of the magnetic moments within these layers. The magnetic moments can be altered by applying a current with a certain spin polarization, permitting data both to be written and read in memory devices.

STT-MTJ can be understood as a specialized application of spintronics principles, with its primary emphasis on harnessing spin transfer torque to achieve specific functionalities, notably in the domains of memory and storage. Spintronics, however, encompasses a wider spectrum of ideas and mechanisms that go beyond STT-MTJ, encompassing various approaches to spin manipulation, spin-based logic, and more. An STT-MTJ consists of three key components: two magnetic layers divided by a slender insulating layer. These layers are typically made of ferromagnetic materials with distinct magnetic orientations. When an electric current flows through the MTJ structure, it consists of electrons with their individual spins. The spin polarization of these electrons refers to the predominant direction of their spins, either "up" or "down. "The insulating layer between the two magnetic layers is thin enough to allow a phenomenon called "spin-dependent tunnelling" to occur. Electrons with spins aligned parallel to the magnetic layers (e.g., "up" in both layers) have a higher probability of tunnelling through the insulating layer than electrons with anti-parallel spins (e.g., "up" in one layer and "down" in the other). When a current with spin-polarized electrons flows through the MTJ, it applies a torque to the magnetic moments of the two ferromagnetic layers. This torque can cause a change in the relative alignment of their magnetic orientations. The

**FIGURE 8.** STT-MJT a) Device architecture b) Stochastic toggle action.

magnetic layers' relative orientation affects the tunnelling probability of electrons, which, in turn, influences the overall resistance of the MTJ. When the magnetic layers are parallel (low-resistance  $(R_P)$  state), it corresponds to one binary value (e.g., "0"). When they are anti-parallel (high-resistance  $(R_{AP})$  state), it corresponds to the opposite binary value (e.g., "1") as shown in Figure.8. STT-MTJ devices can be used for both reading and writing data. To read data, a small current is passed through the device, and the resulting resistance can be measured to determine the stored binary value. To write data, a larger current is applied to change the magnetic state of the MTJ, effectively switching it between the low-resistance (RP) and high-resistance (RAP) states, representing "0" and "1," respectively [79]. STT-MTJ relies on the controlled manipulation of electron spins and their effect on the magnetic layers' relative alignment to store and retrieve binary information. The difference between the resistances is termed as tunnelling magnetic resistance (TMR) is noted as in equation (2)

$$TMR = \frac{R_{AP} - R_P}{R_P} * 100 \tag{2}$$

The read stability of MJT depends upon the TMR ratio as it's more higher the more stable and accurate in reading from MJT [79], [80]. By the inherent physical properties of Utilizing the spin transfer torque mechanism, the MTJ undergoes state transitions when subjected to a bidirectional current (I) surpassing the critical current level ( $I_{C_0}$ ) [81]

where the critical current is given by equation (3),(4).

$$I_{C_0} = 2\alpha \frac{\gamma e}{\mu_B g} E \tag{3}$$

$$E = \frac{\mu_0 M_s H_k V}{2} \tag{4}$$

where E is the Potential Energy Threshold,  $H_k$  is the Effective Anisotropy Strength,  $\mu_0$  is the Permeability of the Void,  $M_s$  is the Full Magnetization,  $\chi$  is the Relaxation Rate in Magnetism,  $\gamma$  is the Gyromagnetic Momentum, e is the Quantum of Charge,  $\mu_B$  is the Bohr magneton, V is the volume of the void,  $k_B$  is the Bohr magneton, V is the polarization efficiency factor, T is temperature,  $\tau$  is switching duration,  $\tau_0$  is standard time [81].

The probability function of stochastic switching behaviour is represented in terms of current (I), critical current( $I_c$ ),  $\Delta$  is temperature factor and time (T) as equation (5):

$$p(1,t) = 1 - exp(\frac{-t}{\tau_0}exp[-\Delta(1-\frac{I}{I_c})^2])$$

(5)

The time it takes to transition between the two operational modes is expressed as shown below in equation (6):

$$\tau = \tau_0 exp(\frac{E}{K_B T} (1 - \frac{I}{I_{C_0}})) \qquad (I > I_{C_0}) \tag{6}$$

In STT-MTJ devices, it's because of important inherent variations to consider that can be leveraged for security enhancements. These variations can add an extra layer of protection against unauthorized access and tampering like random variability, write and read noise, bit errors, temperature sensitivity, process variability, magnetic field

sensitivity, write, read, retention variability etc can make them more resilient and resistant to a broad spectrum of attacks, including physical tampering, side-channel attacks, and unauthorized access attempts. In the paper a novel neuromorphic spin-based TRNG that relies on the stochastic characteristics exhibited by MTJs operating in the sub-critical current regime. In the proposed design, effectively mitigates the influence of process variations through the incorporation of a neuromorphic architecture and the integration of an embedded XNOR operation. Moreover, the TRNG proposal delivers impressive advantages, including high throughput, reduced energy consumption per random data bit, as well as decreased power dissipation and area overhead when juxtaposed with state-of-the-art spin-based TRNGs, all attributed to its streamlined and efficient structure [72]. 2T/3T MTJs serve as a vital component in logic locking when seamlessly integrated into the circuit. They play a pivotal role in generating a key combination that is indispensable for ensuring the correct operation of the circuit. As discussed in paper [19], logic locking is a strategic method that introduces novel key inputs and logic elements into the circuit, causing it to exhibit erroneous behaviour until the precise key combination is furnished. In the context of MTJ-based logic locking, these MTJ structures are instrumental in constructing this crucial key combination. These structures are meticulously engineered to be sensitive to specific key parameters, necessitating precise parameter configuration to enable the circuit to function correctly. This approach is versatile, finding utility in both combinational and sequential logic-locking scenarios. So this offers enhanced security coverage across a broader range of threats when contrasted with alternative obfuscation techniques like IC camouflaging and split manufacturing. To mitigate the risk of side-channel attacks, the authors in paper [47] suggest the adoption of SABL gates, which have demonstrated superior resistance to Differential Power Analysis (DPA) when compared to traditional CMOS gates. Additionally, the proposed TFET SABL gates further bolster DPA resilience by reducing data dependencies on device power consumption. Furthermore, the authors recommend combining logic encryption/locking with these TFET SABL gates to achieve heightened hardware security with exceptionally low energy consumption. Overall, the TFET SABL gates put forth in this proposal exhibit reduced energy consumption and increased DPA resilience, positioning them as a promising choice for secure and energy-efficient cryptographic systems. Within the domain of SOT-assisted MTJ technology, the MTJ resistance functions as a distinctive identifier. This resistance undergoes variation due to diverse process factors, including oxide layer thickness and TMR ratio, resulting in resistance discrepancies among individual devices. To authenticate a device, a designated challenge is applied, enabling the measurement of MTJ resistance and the derivation of a device-specific response. This distinct response operates as the device's unique signature, meticulously archived as a challenge-response pair within a database for authentication purposes. The response's uniqueness stems from the inherent, unpredictable process variations inherent to device manufacturing, rendering the replication or prediction of this response a challenging endeavour this feature stands as a crucial requirement for PUF's, establishing SOT-assisted MTJ as a strong candidate for PUF implementation [20].

The spin-orbit torque MRAM unit offers security advantages over CMOS but requires further research to address integration challenges and vulnerabilities. Spintronic devices like spin-torque diodes and memristors show promise but need improvements in parameter extraction accuracy and scalability. A compact model of magnetic tunnel junctions aims to enhance reliability and security by addressing fabrication errors and stochastic behaviour. Despite fabrication complexity, spintronic random number generators offer secure solutions with lower power consumption, emphasizing the importance of managing process-induced variations for reliable security features.

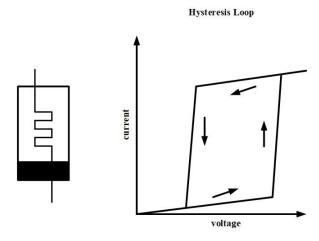

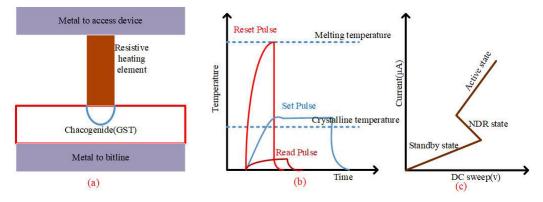

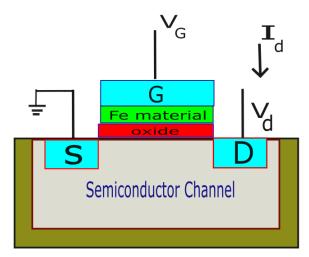

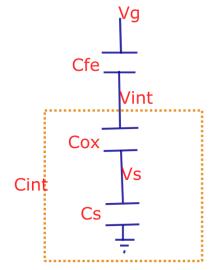

## E. MEMRISTORS