Received 14 March 2024, accepted 12 April 2024, date of publication 23 April 2024, date of current version 31 May 2024.

Digital Object Identifier 10.1109/ACCESS.2024.3392621

# **Spacer Dielectric Analysis of Multi-Channel Nanosheet FET for Nanoscale Applications**

ASISA KUMAR PANIGRAHY<sup>®1</sup>, (Member, IEEE), VEERA VENKATA SAI AMUDALAPALLI<sup>2</sup>, DEPURU SHOBHA RANI<sup>3</sup>, (Member, IEEE), MURALIDHAR NAYAK BHUKYA<sup>®4</sup>, (Member, IEEE), HIMA BINDU VALIVETI<sup>®2</sup>, (Senior Member, IEEE), VAKKALAKULA BHARATH SREENIVASULU<sup>®5</sup>, (Member, IEEE), AND RAGHUNANDAN SWAIN<sup>®6</sup>, (Senior Member, IEEE)

Corresponding author: Asisa Kumar Panigrahy (asisa@ifheindia.org)

The authors want to acknowledge the ICFAI Foundation for Higher Education Hyderabad (IcfaiTech), Hyderabad, India for the financial support and resources needed to conduct the research.

**ABSTRACT** This work investigates the effect of single and dual-k spacer materials consisting of different dielectric constants (k) in optimized nano-channel gate-stack nanosheet (NS-FET) employing hafnium oxide and silicon dioxide as gate insulator to improve its sub-threshold performance. The effect of the external low-k spacer modification in the dual-k spacer has been shown by adjusting the inner high-k spacer. The drain-induced barrier lowering (DIBL) in this modification with dual-k spacer is 14 mV/V, a significant improvement above single spacer NS-FET. The Visual TCAD 3D Cogenda tool is used to examine the performance of the developed NS-FET with air, single, dual-k, and hybrid spacers. The CADENCE platform is used to perform circuit aspects. Additionally, a comparison of the device architecture's performance study with respect to DC characteristics is made. DC parameters of the proposed device are established:  $I_{ON}$  to  $I_{OFF}$  ratio of approximately  $10^5$ , DIBL of approximately  $10^5$ , Dibl. of approximately  $10^5$ , Dibl. of  $10^5$

**INDEX TERMS** CMOS inverter, DIBL, dielectric material, gate-all-round (GAA), power consumption, nanosheet (NS) FET, silicon on insulator (SOI).

### I. INTRODUCTION

According to technical advancements, when an electronic gadget gets smaller, its complexity rises and performance improves. The development of transistors towards nanometer technology has improved its working performance while maintaining the benefit of mobility at smaller dimensions. As per the International Road map for Devices and

The associate editor coordinating the review of this manuscript and approving it for publication was Wen-Sheng Zhao .

Systems (IRDS), devices close to the nanometer range are most appropriate for low-power as well as high frequency applications [1].

The FinFETs have developed vastly during the past decade as transistor size has drastically decreased. Considering their height/width ratio, FinFETs may operate efficiently on nanometer technologies ranging from below 32 nm to 10 nm [2]. FinFET is a multigate device that uses dual or multi-gates wrapped around the channel on a substrate to reduce short-channel effects (SCE) and provide better

Department of ECE, Faculty of Science and Technology (IcfaiTech), The ICFAI Foundation for Higher Education, Hyderabad, Telangana 501203, India

<sup>&</sup>lt;sup>2</sup>Department of ECE, GRIET, Hyderabad, Telangana 500090, India

<sup>&</sup>lt;sup>3</sup>Department of Electrical and Electronics Engineering, Institute of Aeronautical Engineering, Hyderabad, Telangana 500043, India

<sup>&</sup>lt;sup>4</sup>Department of Electrical Engineering, School of Engineering and Technology, Central University of Haryana, Mahendragarh, Haryana 123031, India

<sup>&</sup>lt;sup>5</sup>Department of Electronics and Communication Engineering, Manipal Institute of Technology Bengaluru, Manipal Academy of Higher Education, Manipal, Karnataka 576104, India

<sup>&</sup>lt;sup>6</sup>Department of ETC, Parala Maharaja Engineering College, Brahmapur, Odisha 761003, India

control on an electrostatic channel. FinFETs are particularly suitable for low-power integrated circuits. Furthermore, FinFETs demonstrate a notable proficiency in promoting vertical tunneling instead of corner tunneling. This achievement is attributed to integrating a vertical-tunnel FET designed with negative capacitance. Because of its creative design, the transistor switch operates more efficiently since it creates a powerful vertical electric field [3].

Tri-gate construction is used to enclose all the three sides of the channel. The FinFETs still have a variety of design, device performance, structural, and cost-effectiveness issues that hinder further scaling down despite this advancement [4]. Fin architectures must be able to maintain optimal performance even when device dimensions are reduced. Furthermore, SCEs can be restricted by having a robust channel control structure regulating the channel from all directions, which is essential for technology nodes smaller than 10 nm.

The potential of gate-all-around (GAA) NS-FET is greater when compared to current FinFET technology due to better gate controllability [5]. While scaling is continuous, the channel from all sides encloses the gate. The most suitable alternatives to update FinFET in the sub-10-nm zone are GAA devices like nanowires and nano-sheets. SOI technology involves an insulator substrate like SiO<sub>2</sub>(silicon dioxide) being coated by a thin layer of active region [6]. FDSOI technology is best used in enhanced versions of next-generation wireless applications operating at high frequency and low power [7]. Junctionless transistors (JLTs) can be designed with nano-sheet devices in mind by guaranteeing consistent doping in the channel material, which prevents the formation of junctions between the drain/source and channel [8]. Yu et al. highlighted that adopting inverted-T Bulk FinFET technology has various benefits, including lower wafer costs, reduced occurrence of defects, and ineffective change in thermal energy [9]. However, there may be an issue with the substrate leaking hindrance. By combining two gate insulators above an un-doped substrate, gate-stack technology may significantly reduce leakage. Chiang inferred that the investigations on JLT technology can boost the ON current  $(I_{ON})$  as it has a larger channel volume, broader width of the Fin, and low thickness [10].

The single, dual, or GAA FET, lightly doped drain (LDD) implantation, designed gate, or bulk FET are employed in the existing literature. Every method that has been developed has improved switching times between devices or SS. The authors of this work tackled the difficulties by designing a Junction-less NS gate-stack SOI FinFET and evaluating its performance on spacer regions using a variety of dielectric materials, highlighting the shortcomings of current technologies in terms of practicality and dependability.

The proposed device structure, physical model description, simulation result calibration, and possible fabrication steps to realize the device are explained in section II. The DC analysis results are demonstrated and the physics behind it are discussed in section III. The power analysis and circuit performance are presented in section IV and section V respectively.

Finally, concluding remarks on the manuscript are given in Section VI.

# **II. DEVICE STRUCTURES AND SIMULATION METHOD**

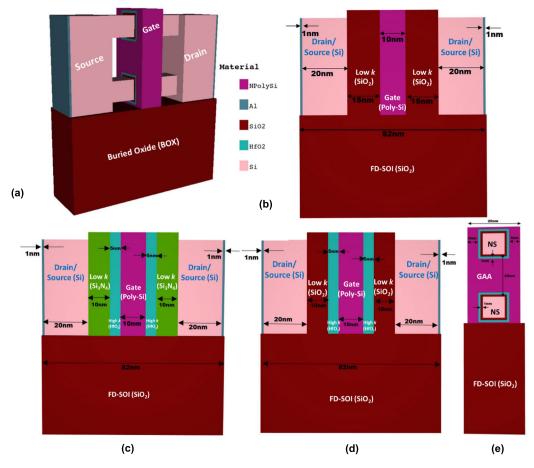

The three-dimensional (3D) device structure of the NS-FET is based on 10 nm technology node [11], [12], [13], [14]. Fig. 1 depicts the front and side view of the device wherein the NS-FET is designed with gate length, fin width, and channel height of 10 nm each. NS-FET is designed to have two channels with 15 nm channel spacing on both sides. The device parameters are presented in Table 1.

The FinFET is implemented with two evenly doped channels with donor doping concentrations of 10<sup>18</sup> cm<sup>-3</sup>. Both Source and Drain have a consistent donor doping level of  $10^{20}$  cm<sup>-3</sup>. The Gate contact is made of polysilicon with a work function of 4.5 eV. HfO2 and SiO2 are used to make the FinFET gate oxide [6], [15]. As the dimensions of transistors shrink, the gate oxide thickness also needs to decrease to maintain proper control over the channel. The trend of reducing the gate oxide thickness in traditional SiO<sub>2</sub>-based devices increases gate leakage and power consumption. High-k dielectric material is used for this purpose along with SiO2. The channel is insulated using low- and high-kmaterials with a total thickness of 2 nm. This inhibits the gate current from evading into the channel and ensures insulator sealing. The device functions more efficiently when a dielectric material is placed between the channel's source and drain [11].

The source and drain are directly connected to the gate to create an NS-FET, as shown in Fig. 1. Insulators are used in the spacing area to reduce parasitic capacitance, increasing resistance. To achieve this, single and dual dielectric spacer materials fill the region between the gate and source/drain [16], [17], [18]. These regions contribute to reducing SCE and improving device performance. The spacing area can be deposited with a low k dielectric material like air and SiO<sub>2</sub>, as shown in Fig. 1(a) and 1(b). The dual-spacer arrangement of high and low dielectric materials in the spacer region can be observed in Fig. 1(c) and 1(d). The length and width of each side are 15 nm and 20 nm, respectively, in a single spacer arrangement. In the dual spacer case, a high-k, and low-k insulator combination of length 5 nm adjacent to the gate and 10 nm adjacent to the source/drain region are considered respectively with a width of 20 nm [19]. The Cogenda Visual TCAD device simulator was used to simulate these devices [20]. The Lombardi mobility model, Shockley-Read-Hall (SRH), and Auger recombination models are all used in the simulation to represent minority carrier recombination. Additionally, the simulation uses the QDDM model from Visual TCAD, which will consider the quantum effects at lower nodes.

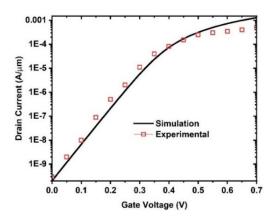

The physical models are determined upon calibration of simulation results obtained from transfer characteristics with experimental results [14]. The calibrated transfer characteristics obtained by normalizing  $I_{\rm DS}$  with  $W_{\rm fin}$  are demonstrated in Fig. 2, demonstrating an excellent match and justifies the

FIGURE 1. Front view of 10 nm NS-FET structure with (a) air (b) SiO<sub>2</sub> (c) Nitride+HfO <sub>2</sub> (d) HfO<sub>2</sub> +SiO<sub>2</sub> spacer material (e) Side view of proposed NS-FET structure.

consideration of appropriate physical models during TCAD simulation.

# **III. RESULTS AND DISCUSSION**

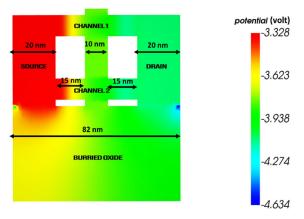

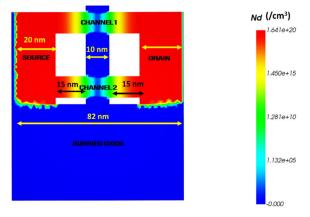

The global temperature of operation of NS-FET is set at 300K. Fig. 4 shows the distribution of surface potential of the devised NS-FET at  $V_{GS}=0.7V,\,V_{DS}=0.75V,\,$  and doping of  $10^{18}\,$  cm $^{-3}$ . The application of  $V_{DS}$  left little potential in the channel and source regions while producing a highly concentrated potential on the drain side. The source and drain areas of the NS-FET donor distributions are heavily doped. The channel region is also doped with donor dopant, as shown in Fig. 4.

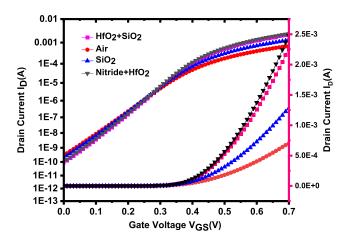

The drain current is considered in Fig. 5 to illustrate the transfer characteristics in linear and logarithmic scales. For estimating the device's performance, the calculation of variables such as  $V_{\rm th}$ ,  $I_{\rm ON}/I_{\rm OFF}$  ratio, SS, and DIBL are crucial. For air, SiO<sub>2</sub>, HfO<sub>2</sub>+SiO<sub>2</sub>, and HfO<sub>2</sub>+nitride, the transfer characteristics are demonstrated. A crucial metric for evaluating the electrical performance of FET devices is the ratio of  $I_{\rm ON}$  to  $I_{\rm OFF}$ . The  $I_{\rm ON}$  stands for the ON-state current and measures the device's ability to handle power when the FET is turned on. The  $I_{\rm OFF}$ , on the other hand, depicts off-state

**TABLE 1.** 10 NM technology: NS-FET and FINFET dimensions.

| Region                   | Dimension                        |                                        |  |

|--------------------------|----------------------------------|----------------------------------------|--|

|                          | NS-FET designed in this work     | Fin FET considered for comparison [11] |  |

| Gate length              | 10 nm                            | 10 nm                                  |  |

| Gate Oxide thickness     | 1 nm                             | 3 nm                                   |  |

| (High-k)                 |                                  |                                        |  |

| Gate Oxide thickness     | 1 nm                             | 0.5 nm                                 |  |

| (Low-k)                  |                                  |                                        |  |

| Spacing Oxide (Low-k)    | 10 nm                            | 7 nm                                   |  |

| Spacing Oxide (High-k)   | 5 nm                             | 2 nm                                   |  |

| EOT                      | 0.75 nm                          | 0.75 nm                                |  |

| S/D doping concentration | $1 \times 10^{20} / \text{cm}^3$ | $1x10^{19}/cm^3$                       |  |

| Fin Pitch                | 20 nm                            | -                                      |  |

| Channel height           | 10 nm                            | 30 nm                                  |  |

| Channel width            | 30 nm                            | 10 nm                                  |  |

| Work function            | 4.5eV                            | 4.8eV                                  |  |

| BOX                      | 45 nm                            | 50 nm                                  |  |

current and shows how well FETs work to block current while it is in OFF condition. The on current, off current, and their ratio can be used to determine the switching characteristics and power efficiency of the device [3]. The ON and OFF

**FIGURE 2.** Calibration of simulated transfer characteristics with Experimental results [14].

FIGURE 3. Potential distribution/ Potential difference of NS-FET at  $V_{GS} = 0.7V$ ,  $V_{DS} = 0.75V$ .

FIGURE 4. Doping Concentration (N<sub>d</sub>) of Two-channel NS-FET.

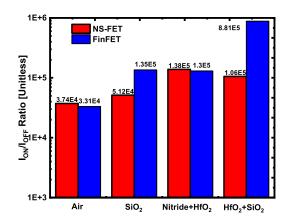

currents and their ratio for the 10 nm NS-FET and FinFET technologies are shown and compared in Tables 2 and 3, respectively. The values listed here represent different dielectric materials utilized to fill the voids.

All the NS-FETs with different spacers have  $I_{ON}$  and  $I_{OFF}$  currents in the range of  $10^{-7}$  and  $10^{-12}$ , respectively. FinFETs with different spacers have  $I_{ON}$  and  $I_{OFF}$  currents

FIGURE 5. Transfer characteristics of the proposed NS-FET with single-k and dual-k spaces in linear and logarithmic scale.

**FIGURE 6.** The Comparison of  $I_{ON}/I_{OFF}$  ratio for the NS-FET and FinFET with single-k and dual-k spacers.

**TABLE 2.** ON and OFF current analysis for varying spacer Materials: NS-FET technology.

|   | Spacer                             | NS-FET                                  | NS-FET I <sub>ON</sub> | NS-FET I <sub>OFF</sub> |

|---|------------------------------------|-----------------------------------------|------------------------|-------------------------|

|   | Material                           | I <sub>ON</sub> /I <sub>OFF</sub> Ratio | current (A)            | current (A)             |

| Ī | Air                                | 3.74E+04                                | 1.11E-07               | 2.97E-12                |

| Ī | SiO <sub>2</sub>                   | 5.12E+04                                | 1.04E-07               | 2.03E-12                |

| Ī | Nitride+HfO <sub>2</sub>           | 1.38E+05                                | 1.27E-07               | 0.919E-12               |

| Γ | HfO <sub>2</sub> +SiO <sub>2</sub> | 1.06E+05                                | 1.15E-07               | 1.09E-12                |

**TABLE 3.** ON And OFF current analysis for varying spacer materials: FINFET technology [11].

| Spacer                             | FinFET                                  | FinFET I <sub>ON</sub> | FinFET I <sub>OFF</sub> |

|------------------------------------|-----------------------------------------|------------------------|-------------------------|

| Material                           | I <sub>ON</sub> /I <sub>OFF</sub> Ratio | current (A)            | current (A)             |

| Air                                | 3.31E+04                                | 8.08E-5                | 2.44E-9                 |

| $SiO_2$                            | 1.35E+05                                | 8.10E-5                | 5.98E-10                |

| Nitride+HfO <sub>2</sub>           | 1.30E+04                                | 8.13E-5                | 6.24E-10                |

| HfO <sub>2</sub> +SiO <sub>2</sub> | 8.81E+05                                | 8.14E-5                | 9.24E-11                |

ranging from  $10^{-5}$  to  $10^{-11}$ . In contrast, NS-FET for single-k spacer outperforms FinFET regarding  $I_{ON}/I_{OFF}$  ratio calculation, improving by 10.55% for air and 73.5% for SiO<sub>2</sub>. Fig. 6 compares  $I_{ON}/I_{OFF}$  ratio for the NS-FET and FinFET with single-k and dual-k spacers.

FIGURE 7. The threshold voltage of 10 nm node NS-FET and FinFET with different spacers.

TABLE 4. Threshold voltage for NS-FET and FINFET for varying spacer materials.

| Spaces Material                    | NS-FET (V <sub>th</sub> ) in volts | FinFET (V <sub>th</sub> ) in volts |

|------------------------------------|------------------------------------|------------------------------------|

| Air                                | 0.35                               | 0.145                              |

| $SiO_2$                            | 0.36                               | 0.175                              |

| Nitride+HfO <sub>2</sub>           | 0.38                               | 0.235                              |

| HfO <sub>2</sub> +SiO <sub>2</sub> | 0.37                               | 0.225                              |

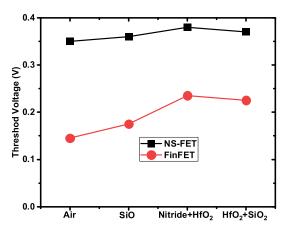

It is necessary to decrease the V<sub>th</sub> of NS devices to maintain satisfactory performance. It has been demonstrated that the NS-FET device can operate at a lower gate voltage by lowering V<sub>th</sub>. As a result, the gate oxide layer experiences less electrical stress. This not only leads to lower power consumption but also improves the switching speed of the device [21]. Fig. 7, along with Table 4, demonstrates the threshold voltage for NS-FET and FinFET devices using single and dual-k dielectric materials.

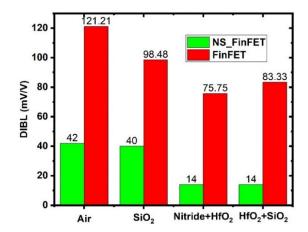

The DIBL and SS are crucial short-channel parameters that determine the performance of devices. In these devices, drain potential has a significant influence on the energy band diagram in the channel region [18]. The drain bias unintentionally lowers the barrier between the source and drain, resulting in a subthreshold current, and the effect is commonly referred to as DIBL. DIBL and SS can be expressed through (1) and (2) respectively [2]. Table 5 depicts the DIBL values of NS-FET and FinFET for various spacer materials.

$$DIBL(mV/V) = \left| \frac{V_{th1} - V_{th2}}{V_{DS1} - V_{DS2}} \right|$$

(1)

$$SS(mV/dec) = \left[ \frac{\partial log_{10}(I_{DS})}{\partial V_{gs}} \right]^{-1}$$

(2)

$$SS(mV/dec) = \left[\frac{\partial log_{10}(I_{DS})}{\partial V_{gs}}\right]^{-1}$$

(2)

$V_{th1}$  at  $V_{DS1} = 0.75V$  (high drain voltage) and  $V_{th2}$ at  $V_{DS2} = 0.04V$  (low drain voltage) are vital parameters required while calculating the DIBL as indicated in (1). DIBL in case of FinFET with Air spacer (single-k) is measured to be 121.21 mV/V, and this value decreased by 65.34% to 42 mV/V in the case of NS-FET. Similarly, the DIBL value for FinFET with SiO<sub>2</sub> spacer (single-k) is 98.48 mV/V, decreasing by 59.37% to 40 mV/ V with NS-FET. For

**TABLE 5.** DIBL for NS-FET and FINFET with varying spacer materials.

| Spaces Material                    | NS-FET DIBL<br>(mV/V) | FinFET DIBL<br>(mV/V) [11] |

|------------------------------------|-----------------------|----------------------------|

| Air                                | 42                    | 121.1                      |

| $SiO_2$                            | 40                    | 98.48                      |

| Nitride+HfO <sub>2</sub>           | 14                    | 75.75                      |

| HfO <sub>2</sub> +SiO <sub>2</sub> | 14                    | 83.33                      |

FIGURE 8. DIBL of NS-FET and FinFET for 10 nm technology node.

TABLE 6. SS for NS-FET and FINFET with varying spacer materials.

| Spaces Material                    | SS in NS-FET (mV/dec) | SS in FinFET (mV/dec) |

|------------------------------------|-----------------------|-----------------------|

| Air                                | 67                    | 70.63                 |

| $SiO_2$                            | 65                    | 65.6                  |

| Nitride+HfO <sub>2</sub>           | 62                    | 62.01                 |

| HfO <sub>2</sub> +SiO <sub>2</sub> | 61.2                  | 62.86                 |

FinFET with Nitride+HfO<sub>2</sub> spacer layers (dual-k), the DIBL value is 75.75 mV/V, and it is decreased by 81.43% to 14 mV/V with NS-FET. Lastly, the DIBL value for FinFET with HfO<sub>2</sub>+SiO<sub>2</sub> spacers (dual-k) is 83.33 mV/V, and it is decreased by 83.19% to 14 mV/V with NS-FET, as shown in Table 5 and Fig. 8.

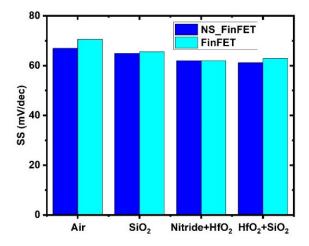

The subthreshold swing is a parameter claiming to improve when the short channel effects in the device are low [2]. The SS value obtained in NS-FET is 67 mV/ec witnessing an improvement of 5.28% compared to the single-k (air) FinFET. Compared to NS-FET, the SS has improved by 0.92% for the spacer material SiO<sub>2</sub>. Likewise, as mentioned in Table 6 and illustrated in Fig. 9, the SS for dual-k(Nitride+HfO<sub>2</sub>) for either of the devices remained unaltered but displayed an improvement in SS compared to the former materials. Similar improvement can be seen in dual-k (HfO<sub>2</sub>+SiO<sub>2</sub>), where the SS almost meets its ideal value of 60mV/Dec [3]. The dielectric fringing fields reduce leakages as spacer materials change from air to low-k to high-k. This lowers the SCEs and thus enhances the device's SS and DIBL characteristics. NS-FET, built with the concept of multiple channels, gathers an advantage when compared to FinFET in improving the SS and DIBL.

FIGURE 9. SS of NS-FET and FinFET for 10 nm technology.

**TABLE 7.** Performance comparison.

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$  |                          |          |                  |          |        |

|---------------------------------------------------------|--------------------------|----------|------------------|----------|--------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$   | Devices                  | $V_{th}$ | $I_{ON}/I_{OFF}$ | SS in    | DIBL   |

| HfO <sub>2</sub> +SiO <sub>2</sub>                      |                          | (V)      | Ratio            | (mV/dec) | (mV/V) |

| Nitride+HfO <sub>2</sub>                                |                          | 0.37     | 1.2E5            | 61.2     | 14     |

| 51.55   INV NS-FET [23]   0.38   5.03E7   61.48   34.29 |                          | 0.38     | 1.1E6            | 62       | 14     |

| 34.29                                                   | JL NS-FET [22]           | 0.38     | 3.54E7           | 63.7     | 51.55  |

| Gate-Based Junction-less   22                           | INV NS-FET [23]          | 0.38     | 5.03E7           | 61.48    | 34.29  |

|                                                         | Gate-Based Junction-less | 0.86     | 9.6E12           | 61.51    | 22     |

|                                                         |                          | 0.86     | 4.5E12           | 58.67    | 52.37  |

Additionally, Table 7 contrasts the DC characteristics of the proposed NS FETs with those of the Junction-less NSFET, the Heterojunction Si<sub>1-x</sub>Ge<sub>x</sub> FinFET, and the Multi-Channel-Multi-Gate-Based Junction-less Field Effect Transistor that have been reported in the literature [22], [23], [24], [25]. As Table 7 makes abundantly evident, NS-FETs with different space charge region materials have comparable [22], [23], or much lower threshold voltages [24], [25], as well as reasonable SS and DIBL, all of which greatly reduce SCE and make them perfect for low power applications.

### IV. POWER ANALYSIS

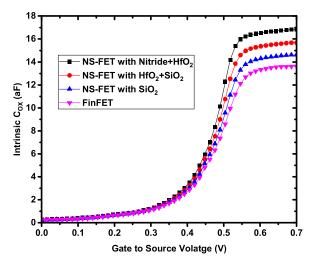

When determining if low power consumption will be attained, a device's power consumption measurement is essential. Thus, assuming  $V_{\rm dd} = 0.7V$  and gate work function of 4.8 eV the following formula is used to compute the dynamic and average power [9], [26], [28]. The  $C_{\rm OX}$  represents the equivalent oxide capacitance obtained by the series combination of capacitance due to spacer oxide layers [27]. The variation of capacitances with varying gate voltage is presented in Fig. 10.

FIGURE 10.  $C_{OX} \sim V_{GS}$  Characteristics for FinFET vs NS-FET structures.

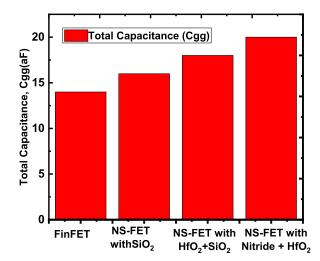

FIGURE 11. Total Capacitance, Cgg (aF) of various FETs.

Upon multiplication of maximum  $C_{OX}$  with  $V_{dd}^2$  and  $0.5V_{dd}^2$ , dynamic and average power are obtained as per (3) and (4), respectively.

$$Dynamicpower = C_{ox}.V_{dd}^2$$

(3)

$$AveragePower = \frac{1}{2}C_{ox}.V_{dd}^2 \tag{4}$$

Figure 11 depicts the total capacitance (Cgg=Cgs+Cgd) of various FETs. The rise in Cgs and Cgd results in rise in the total capacitance with increase in dielectric permittivity. Thus, Cgg is low for FinFET combination followed by SiO<sub>2</sub> and HfO<sub>2</sub>+SiO<sub>2</sub> and Nitride+HfO<sub>2</sub>.

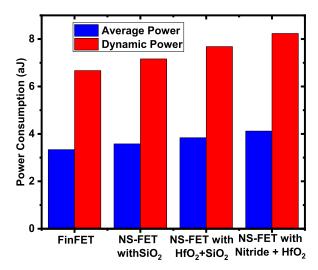

The variation of dynamic and average power of FinFET, proposed NS-FET with single dielectric SiO<sub>2</sub> and with diverse space charge regions including HfO<sub>2</sub>+SiO<sub>2</sub>, and Nitride+HfO<sub>2</sub>, are shown in Fig. 12. Compared to a traditional FinFET, the NS-FET with Nitride+HfO<sub>2</sub> as the space charge region consumes a relatively little amount of average and dynamic power.

FIGURE 12. Power consumption in attoJoule (aJ) for NS-FET.

FIGURE 13. (a) Transfer characteristics for PMOS and NMOS inverters and (b) CMOS inverters.

# **V. CIRCUIT PERFORMANCE**

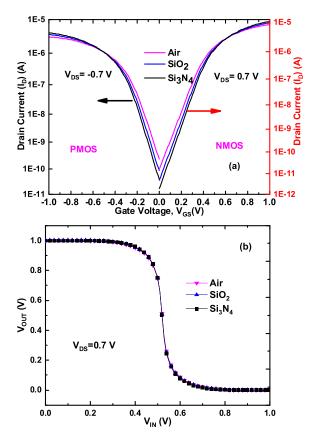

The CADENCE tool examines the device's efficiency towards the circuit for different spacer materials. The performance of the CMOS inverter is shown in Fig. 13. Fig. 13(a) displays the PMOS and NMOS transfer characteristics of the NS-FET at  $V_{DS}=0.7V$ . The  $Si_3N_4$ 's strong fringing fields cause lower  $I_{OFF}$  and greater  $I_{ON}$ . The  $V_{OUT}$  with  $V_{IN}$  fluctuation is shown in Fig. 13(b). There are slight differences

in the transfer characteristics between  $SiO_2$ , Air, and  $Si_3N_4$  dielectrics.

# VI. CONCLUSION

The developed 10 nm technology FINFET and NS-FET has two channels with uniform NS-FET doping concentrations for a variety of spacer region materials with single-k (Air and SiO<sub>2</sub>), dual-k (HfO<sub>2</sub>+SiO<sub>2</sub> and Nitride+HfO<sub>2</sub>) spacers. The device is designed with GAA and FDSOI technology. The 3D devices are thoroughly investigated for factors such as transfer characteristics, threshold voltage, ION to IOFF ratio, DIBL, and SS. In comparison to FinFET, the DIBL of the NS-FET's changing dielectric spacer materials like Air, SiO<sub>2</sub>, HfO<sub>2</sub>+SiO<sub>2</sub>, and Nitride+HfO<sub>2</sub> is improved by 65.34%, 59.37%, 81.43%, and 83.19%, respectively, while the SS is decreased by 5.28%, 0.92%, 0.02%, and 2.68%. The  $I_{ON}/I_{OFF}$  ratio for a single-k spacer is better. From this result, it can be concluded that subthreshold leakage is decreasing for NS-FET compared to FinFET by changing the spacer materials. Furthermore, the power consumption is comparably small for NS-FET with diverse space charge regions. The leakage current reduction implies and assures improved device performance for low-power nanoscale applications.

# **ACKNOWLEDGMENT**

The authors acknowledge the SPDC Laboratory, GRIET, Hyderabad, for providing the access to Cogenda Visual TCAD tool facility.

### **REFERENCES**

- [1] W. M. Arden, "The international technology roadmap for semiconductors—Perspectives and challenges for the next 15 years," *Current Opinion Solid State Mater. Sci.*, vol. 6, no. 5, pp. 371–377, Oct. 2002.

- [2] J.-S. Yoon, J. Jeong, S. Lee, and R.-H. Baek, "Multi-V<sub>th</sub> strategies of 7-nm node nanosheet FETs with limited nanosheet spacing," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 861–865, 2018.

- [3] R. Yuvaraj, A. Karuppannan, A. K. Panigrahy, and R. Swain, "Design and analysis of gate stack silicon-on-insulator nanosheet FET for low power applications," *Silicon*, vol. 15, no. 4, pp. 1739–1746, Sep. 2022.

- [4] N. A. Kumari, V. B. Sreenivasulu, and P. Prithvi, "Impact of scaling on nanosheet FET and CMOS circuit applications," ECS J. Solid State Sci. Technol., vol. 12, no. 3, Mar. 2023, Art. no. 033001, doi: 10.1149/2162-8777/acbcf2.

- [5] P. H. Vardhan, S. Ganguly, and U. Ganguly, "Threshold voltage variability in nanosheet GAA transistors," *IEEE Trans. Electron Devices*, vol. 66, no. 10, pp. 4433–4438, Oct. 2019.

- [6] V. B. Sreenivasulu, N. A. Kumari, V. Lokesh, S. K. Vishvakarma, and V. Narendar, "Common source amplifier and ring oscillator circuit performance optimization using multi-bridge channel FETs," ECS J. Solid State Sci. Technol., vol. 12, no. 2, Feb. 2023, Art. no. 023013.

- [7] J.-P. Raskin, "Fully depleted SOI technology for millimeter-wave integrated circuits," *IEEE J. Electron Devices Soc.*, vol. 10, pp. 424–434, 2022.

- [8] V. B. Sreenivasulu, N. A. Kumari, V. Lokesh, J. Ajayan, M. Uma, and V. Vijayvargiya, "Design of resistive load inverter and common source amplifier circuits using symmetric and asymmetric nanowire FETs," *J. Electron. Mater.*, vol. 52, no. 11, pp. 7268–7279, Nov. 2023.

- [9] E. Yu, K. Heo, and S. Cho, "Characterization and optimization of inverted-T FinFET under nanoscale dimensions," *IEEE Trans. Electron Devices*, vol. 65, no. 8, pp. 3521–3527, Aug. 2018, doi: 10.1109/TED.2018.2846478.

- [10] T.-K. Chiang, "A new threshold voltage model for short-channel junctionless inverted T-shaped gate FETs (JLITFET)," *IEEE Trans. Nanotechnol.*, vol. 15, no. 3, pp. 442–447, May 2016.

- [11] N. Vadthiya, "Design and deep insights into sub-10 nm spacer engineered junctionless FinFET for nanoscale applications," ECS J. Solid State Sci. Technol., vol. 10, no. 1, Jan. 2021, Art. no. 013008.

- [12] M. G. Bardon, P. Schuddinck, P. Raghavan, D. Jang, D. Yakimets, A. Mercha, D. Verkest, and A. Thean, "Dimensioning for power and performance under 10 nm: The limits of FinFETs scaling," in *Proc. Int. Conf. IC Design Technol. (ICICDT)*, Jun. 2015, pp. 1–4.

- [13] V. V. Sai Amudalapalli, H. Bindu Valiveti, and A. K. Panigrahy, "Design and comparative analysis of 10 nm and 16 nm multichannel nanosheet FinFET with varying doping concentrations," in *Proc. 8th Int. Conf. Commun. Electron. Syst. (ICCES)*, Jun. 2023, pp. 198–203.

- [14] C. Auth et al., "A 10 nm high-performance and low-power CMOS technology featuring 3<sup>rd</sup> generation FinFET transistors, self-aligned quad patterning, contact over the active gate and cobalt local interconnects," in *Proc. IEDM*, Jun. 2017, pp. 29.1.1–29.1.4.

- [15] C. J. Gonta, "Atomic layer of deposition of ferroelectric HfO<sub>2</sub>," J. Microelectron. Eng. Conf., vol. 23, no. 1, p. 12, 2017.

- [16] V. B. Sreenivasulu and V. Narendar, "Design and temperature assessment of junctionless nanosheet FET for nanoscale applications," *Silicon*, vol. 14, no. 8, pp. 3823–3834, Jun. 2022.

- [17] D. Jang, D. Yakimets, G. Eneman, P. Schuddinck, M. G. Bardon, P. Raghavan, A. Spessot, D. Verkest, and A. Mocuta, "Device exploration of NanoSheet transistors for sub-7-nm technology node," *IEEE Trans. Electron Devices*, vol. 64, no. 6, pp. 2707–2713, Jun. 2017.

- [18] V. B. Sreenivasulu, A. K. Neelam, S. R. Kola, J. Singh, and Y. Li, "Exploring the performance of 3-D nanosheet FET in inversion and junctionless modes: Device and circuit-level analysis and comparison," *IEEE Access*, vol. 11, pp. 90421–90429, 2023, doi: 10.1109/ACCESS.2023. 3306050.

- [19] A. Samal, K. P. Pradhan, and S. K. Mohapatra, "Improvising the switching ratio through low-k/high-k spacer and dielectric gate stack in 3D FinFET—A simulation perspective," *Silicon*, vol. 13, no. 8, pp. 2655–2660, Aug. 2021.

- [20] Genius, 3-D Device Simulator, Version 1.9.3, Reference Manual, Cogenda Pvt. Ltd., Singapore, 2008.

- [21] M.-H. Chiang, C.-N. Lin, and G.-S. Lin, "Threshold voltage sensitivity to doping density in extremely scaled MOSFETs," *Semicond. Sci. Technol.*, vol. 21, no. 2, pp. 190–193, Feb. 2006.

- [22] V. B. Sreenivasulu and V. Narendar, "Design insights of nanosheet FET and CMOS circuit applications at 5-nm technology node," *IEEE Trans. Electron Devices*, vol. 69, no. 8, pp. 4115–4122, Aug. 2022, doi: 10.1109/TED.2022.3181575.

- [23] A. S. Kumar, V. B. Sreenivasulu, S. R. Chavva, S. Bhandari, N. A. Kumari, A. Pothabolu, M. Deekshana, and R. P. Somineni, "Nanosheet field effect transistor device and circuit aspects for future technology nodes," ECS J. Solid State Sci. Technol., vol. 12, no. 8, Aug. 2023, Art. no. 083009.

- [24] S. Verma, V. Narula, and S. L. Tripathi, "Performance analysis of multichannel-multi-gate-based junctionless field effect transistor," *IETE J. Res.*, vol. 2023, pp. 1–11, Jun. 2023.

- [25] S. Verma and S. L. Tripathi, "Effect of mole fraction and fin material on performance parameter of 14 nm heterojunction  $\mathrm{Si}_{1-x}\mathrm{Gex}$  FinFET and application as an inverter," *Silicon*, vol. 14, no. 14, pp. 8793–8804, Sep. 2022.

- [26] V. B. Sreenivasulu and V. Narendar, "A comprehensive analysis of junctionless tri-gate (TG) FinFET towards low-power and high-frequency applications at 5-nm gate length," *Silicon*, vol. 14, no. 5, pp. 2009–2021, Apr. 2022.

- [27] N. A. Kumari, V. B. Sreenivasulu, J. Ajayan, T. J. Reddy, and P. Prithvi, "Spacer engineering on nanosheet FETs towards device and circuit perspective," ECS J. Solid State Sci. Technol., vol. 12, no. 5, May 2023, Art. no. 053009.

- [28] V. B. Sreenivasulu, A. K. Neelam, A. K. Panigrahy, L. Vakkalakula, J. Singh, and S. G. Singh, "Benchmarking of multi-bridge-channel FETs toward analog and mixed-mode circuit applications," *IEEE Access*, vol. 12, pp. 7531–7539, 2024, doi: 10.1109/ACCESS.2024. 3350779.

ASISA KUMAR PANIGRAHY (Member, IEEE) received the Ph.D. degree from the Electrical Engineering Department, Indian Institute of Technology Hyderabad, in 2017, with a specialization in microelectronics and VLSI. Currently, he is an Associate Professor and the Head of the Department of Electronics and Communication Engineering, The ICFAI Foundation for Higher Education, Hyderabad, India. He has authored 25 peer-reviewed and SCI-indexed articles in pres-

tigious publications, including IEEE, Elsevier, and Springer. His areas of research interests include vertical IC (3D IC) integration, semiconductor device simulations and modeling, and sensors based on micro-nanomaterials. He is an Academic Editorial Board Member of Journal of Nanomaterials (Hindawi). He received the Excellence in Research Award from the Director of the Indian Institute of Technology Hyderabad, during the Foundation Day of the Institute, in 2015 and 2016. He received the DST Young Scientist Award from the Department of Science and Technology, Government of India, in 2016. He received the CSIR Young Scientist Award from CSIR, Government of India, in 2016. He received the Distinguished Japanese Society for the Promotion of Science (JSPS) Award from The University of Tokyo, Japan, as an Invited Speaker, in 2017. He received the Gandhian Young Technological Innovation Award for the research work "A Low-Cost Disposable Microfluidic Biochip for Malaria Diagnosis" from the Honorable President of India Shri Ram Nath Kovind Ji at Rashtrapati Bhavan, in March 2018

**VEERA VENKATA SAI AMUDALAPALLI** is currently pursuing the M.Tech. degree with the Electronics and Communication Engineering Department, GRIET, Hyderabad, Telangana, India. His current research interests include nanoelectronics, semiconductor device modeling, and simulation.

**DEPURU SHOBHA RANI** (Member, IEEE) received the B.E. degree in electrical and electronics engineering from Jawaharlal Nehru Technological University, Hyderabad, India, and the M.Tech. degree in power systems and the Ph.D. degree from Sri Venkateswara University, Tirupati, India. Currently, she is a Professor with the Department of Electrical and Electronics Engineering, Institute of Aeronautical Engineering, Hyderabad. Her areas of research interests include control systems and

the application of power systems and power electronics.

MURALIDHAR NAYAK BHUKYA (Member, IEEE) was born in Andhra Pradesh, India, in 1987. He received the B.Tech. degree in electrical and electronics engineering and the M.Tech. degree in power electronics from Jawaharlal Nehru Technological University, Hyderabad, India, in 2008 and 2013, respectively, and the Ph.D. degree in electrical and electronics engineering from JNT University, Kakinada. He is currently an Assistant Professor with the Department of Electrical Engi-

neering, School of Engineering and Technology, Central University of Haryana, India. His areas of research interests include control systems, special machines, and the application of power electronics in renewable energy systems.

HIMA BINDU VALIVETI (Senior Member, IEEE) received the master's degree in telecommunication engineering from the Royal Melbourne Institute of Technology (RMIT), Australia, and the Ph.D. degree from GITAM Deemed to be University. She is currently a Professor and the Head of the Department of Electronics and Communication Engineering, Gokaraju Rangaraju Institute of Engineering and Technology. She has more than eighteen years of industry, academic, and research

experience put together. She published more than 35 research papers in peer-reviewed journals and international conferences. She has research and consultancy funding of 15 lakhs in the area of the IoT and machine learning for vehicle suspension systems technology. Her research interests include software-defined networking, computer networks, wireless communications, nano-electronics, the IoT and embedded systems, probability and stochastic processes, signal processing, and artificial intelligence/machine learning (AI/ML). She is a Senior Member of the IETE student bodies and an Advisor of IEEE CAS. She is the Organizing Chair of the AICTE-funded conference and the Short Term Training Program. She is an active speaker of various conferences, FDPs, workshops, and training programs, and a reviewer of numerous SCI and Scopus journals. She has organized various workshops and value-added courses for undergraduate students of all disciplines.

RAGHUNANDAN SWAIN (Senior Member, IEEE) received the Ph.D. degree in compound semiconductor-based electronic devices from the National Institute of Technology, Silchar, in 2016. He then joined as an Assistant Professor and working to date with the Parala Maharaja Engineering College, Constituent College of Government of Odisha affiliated with Biju Patnaik University of Technology. Currently, he is guiding four students towards their Ph.D. As a Principal Investigator on

one funding research project and a Co-Principal Investigator on another, he carried them out. He has published 20 international journal articles in reputed journals, such as IEEE, Elsevier, and Springer. He has presented his work at 12 international conferences in the area of semiconductor devices inside India and abroad. His research interests include GaN-based heterostructure devices, nano-channel FinFETs, and power electronic applications. He is a Regular Reviewer of indexed journals of IEEE, Elsevier, and Taylor and Francis.

. . .

### VAKKALAKULA BHARATH SREENIVASULU

(Member, IEEE) received the B.Tech. degree in electronics and communication engineering and the M.Tech. degree in VLSI and embedded systems from Jawaharlal Nehru Technological University, Anantapur, Andhra Pradesh, India, in 2013 and 2016, respectively, and the Ph.D. degree from the National Institute of Technology (NIT) Warangal, Warangal, India, in 2022. He was a Postdoctoral Research Associate with Indian Insti-

tute of Technology (IIT) Patna, Patna, India, in 2023. He has published several peer-reviewed articles on topics, such as Tri-Gate FET, FinFET, multi-fin FET, nanowire, nanosheet, and novel structures for CMOS circuit applications. Some of his works are recognized as the most popular and top-cited list of articles in IEEE Transactions on Electron Devices, Microelectronics Journal, and International Journal of RF and Microwave Computer-Aided Engineering. His current research interests include the design of novel device architectures and circuits for sub-5-nm technology regimes, compact modeling, artificial neural networks, and neuromorphic computing approaches for semiconductor devices.