Received 13 March 2024, accepted 7 April 2024, date of publication 10 April 2024, date of current version 22 April 2024. Digital Object Identifier 10.1109/ACCESS.2024.3387094

# **FETs for Analog Neural MACs**

RINKU RANI DAS<sup>®</sup>, T. R. RAJALEKSHMI<sup>®</sup>, SRUTHI PALLATHUVALAPPIL<sup>®</sup>, (Graduate Student Member, IEEE), AND ALEX JAMES<sup>®</sup>, (Senior Member, IEEE)

School of Electronic Systems and Automation, Digital University Kerala, Thiruvananthapuram 695317, India

Corresponding author: Alex James (apj@ieee.org)

This work was supported by the Ministry of Electronics and IT, Government of India.

**ABSTRACT** This study provides a comprehensive view on neural network systems with implemented with crossbar circuits, and device-level understanding of modern FET technologies in neuromorphic computing. This work categorizes and analyzes various transistor types, including ion-gate, ferroelectric, and floating-gate transistors, shedding light on their unique advantages and applications in neuromorphic computing. In this overview, we explore the fundamental principles, recent advancements, and significant trends in transistor-based neuromorphic devices, providing valuable insights into this innovative field. This work also examines resistive memories and 2D materials, that could revolutionize transistor fabrication for neuromorphic devices. Further, various research challenges, limitations, and potential research directions are discussed.

**INDEX TERMS** Field effect transistor (FET), CMOS, memristors, multiply and accumulate (MAC), 2D materials, FeFET, IGT.

## I. INTRODUCTION

The wide range of hardware implementations in the analog, digital or mixed signal domains of bio-inspired computing systems contributes to the era of neuromorphic computing. Neuromorphic computing closely resides in analog computing hardware similar to the human brain. The expected functionalities and how closely they mimic the human brain are the most important factors in neuromorphic computing hardware. It attempts to integrate various biological characteristics of the human brain such as synapses, synaptic weight, synaptic transmission, spike-time encoding, different types of plasticity, parallel processing of accumulated information and higher cognitive functions. The extremely low power consumption, fast processing of information and high density of the human brain are the leading factors on which the evolving neural network implementations in the digital, analog and mixed-signal domains are the focus. Extreme energy efficiency is accounted for in advanced spiking neural networks. The analogies between biological neural networks and hardware systems can implement using transistors by making them operate in a region that follows the dynamics of neurons and synaptic dynamics. The amount of data being generated, processed and stored is increasing, and the higher energy consumption required for the same is due to the data traffic between memory and processing, which is separated in the Von-Neumann architecture. This causes huge energy wastage and reduces computational speed. The possibility of integrating memory and processing units taking inspiration from the human brain via neuromorphic chips addresses the bottleneck for data transmission, which helps to acquire energy consumption and computational speed similar to that of the dynamics of the human brain. One key challenge for neuromorphic computing hardware implementation is the different non-idealities and variabilities of memory devices along with transistor technology. To accelerate more than conventional digital circuits, the complexity of building neuromorphic chips that require analog behavior of memory devices and transistors needs to be addressed further. The lack of hierarchical boundaries, which von-Neumann allows for development, is lacking in the case of neuromorphic computing and needs to be addressed to accelerate its evolution [1]. While building neuromorphic chips, many neurons and synapses must be modelled to make them computationally powerful and to imitate brain functions such as non-linearity, spiking behavior, plasticity and long-term

The associate editor coordinating the review of this manuscript and approving it for publication was Chaitanya U. Kshirsagar.

memory. Millions of biological interconnections, such as that of the human brain, need to be replicated in neuromorphic chips to mimic high degrees of interconnection.

Analog computing, in-memory computing, spike coding, task-specific connectivity, and parallel processing are the key tricks employed by the human brain that can be transferred to neuromorphic computing hardware. Currently, it is difficult to mimic all the features of the human brain, but it can be made comparable by starting from conventional technologies and then exploring new dimensions. Neuromorphic computing is progressing to cover the information storage and processing principles of the human brain. For example, the scientific community has already performed sound, image and video processing for recognition, which is mostly at the theoretical and algorithmic levels using computers based on the Von-Neumann architecture. Currently, researchers are putting great effort into implementing the functions using novel architectures in a manner where the human nervous system performs storage and computations that range from single-memory devices to in-memory computing architectures. To build efficient neural computing architectures that perform beyond Von-Neumann's computing architecture, scientists must bridge the gap between today's electronic chips and human intelligence. The characteristics of the human brain, such as storing information in the analog domain and plastic rather than having limited reconfigurability, million synapses and neurons, and multiple dynamics rather than having a single clock, are to name a few, taking into account the evolving neuromorphic computing hardware design [2]. The architectural and computational principles of the human brain, with an energy consumption of approximately 20 Watts, need to be replicated in neural chips, which is a crucial challenge to address. Different features of the human brain still cannot be understood like laminar architecture, diversity (for example, various types of distinguishable neuron cells exist, but most deep neural networks use identical neurons), a high degree of organization (specific areas for specific tasks, which are usually not considered in neural networks) and synapses that have complicated biochemical processes encoded as a single weight value in neural networks. Bridging these gaps opens the possibility of well-established neuromorphic computing architectures that have the potential to store and compute similar to the human brain. Neuromorphic hardware is biologically inspired by computational aspects of the human brain. Mapping between biological and artificial computations requires a set of in-memory computing circuitries [3]. Neural networks can be implemented using transistor-based resistive memory circuits. The Weighted summation operations, succeeding activation functions, and remaining intermediate operations can be implemented using specific circuits such as one-transistor-one-memristor-based crossbars, opamp-based analog-to-digital converters, sample and hold circuits, purely transistor-based control switches, activation functions and transmission gates. The memristors are artificial synapses. Voltage pulses are applied to change

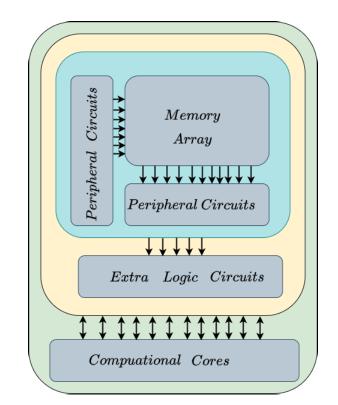

FIGURE 1. The system-level architecture blocks of in-memory computing.

the conductance states of the memristor to which the input weights of the neural networks are mapped, which is analogous with the application of neural spikes are to change the synaptic weights [4], [5], [6]. The memristive device and selector transistors are arranged in rows and columns to implement weighted summation operations [7]. Other transistor technology-based circuits are used for further computations to implement neural networks.

The most significant functional units of neural systems are the neurons and synapses [8]. Scientists and engineers can create artificial systems, by understanding and replicating the behavior of these components. Next-generation neuromorphic computing that mimics the human brain, using advanced techniques to boost computational power and pattern recognition, is receiving significant attention [9]. Neurons receive information from sensory organs or other neurons. It then generates an electrical signal after a certain threshold point called the action potential. Finally, the electrical signal is transmitted over long distances within the nervous system. Synapses transmit signals from one neuron to another. Neurons receive signals from thousands of neurons via synapses. Synapses act as neural bridges where information is stored and processed through dynamic adjustments in their connection strengths, enabling the brain to learn and form memories [10]. This neural system can integrate seamlessly with a parallel in-memory computing architecture, offering low power consumption and enabling more precise information processing [11]. Traditional digital computing is performed using CMOS technology to simulate

biological synapses and neurons [12]. However, digital computing using conventional CMOS technology has various unwanted issues [13]. It is very difficult to handle the information between physically separated computing and memory units. Conventional computing consumes more power, speed, and work overheads. To overcome these limitations various types of modified transistors has been proposed and studied. Electrolyte-gated transistors (EGTs), ferroelectric-gate field effect transistor (FET) (FeFETs), and floating Gate (FG) FET have been recognized as highly promising neuromorphic devices for emulating both neurons and synapses [14]. Their unique characteristics help to mimic the behaviour of synapses and neurons more closely than traditional digital computation units based on complementary metal oxide semiconductor (CMOS) technology. By examining the interplay between neural network architectures and transistor-based devices, this comprehensive review focuses on the pivotal role of transistors in realizing neuromorphic computing.

This study encompasses a wide spectrum of technical details, spanning from modular and three-dimensional crossbar arrays to circuit-level implementations and transistor technologies. It focuses on covering the core concepts of neuromorphic computing and examining its fundamental principles alongside neural network architectures, three-dimensional crossbar arrays, and circuit-level implementations. We provide concise progress in transistor technology over time and explore the latest advancements in transistor-based neuromorphic devices. We discuss the working mechanism of transistors, followed by their integration in neuromorphic computing. Additionally, we conducted an in-depth analysis of the materials crucial to these transistors, emphasizing their significance in advancing the field. The focus is on materials such as silicon, ferroelectric materials, and 2D materials, which have the potential to revolutionize the fabrication of transistors for neuromorphic devices. As neuromorphic computing continues to grow, it is crucial to understand how transistors and neural networks work together to improve cognitive computing. The review concludes by addressing the challenges faced in this field and discussing future perspectives.

#### **II. NEUROMORPHIC COMPUTING**

Fig. 1 shows Computation-In-Memory(CIM), in which computation occurs in the memory core. The system-level architecture integrates processing within memory. The architecture mainly consists of non-volatile memory devices that enable storage and computation. The memory core comprises a memory array and a peripheral circuit. The computational results are produced within the array or in the periphery. Based on where the computational results are formed, the CIM architecture can be classified into CIM-Array and CIM-Periphery. The computational results are produced and stored in the form of resistance states within the memory array in the case of CIM-Array. Because computation and storage occur within the same memory array, the maximum

bandwidth can be acquired for transferring data between the computation and memory. High parallelism can be achieved because the computations are performed independently of sense amplifiers. Endurance and energy issues occur because of the frequent write operations. In complex functionalities, there is a chance of performance overhead owing to device programming and cascading. The CIM-Array requires significant design efforts.

In CIM-Periphery, computational results are produced within the periphery circuitry. Memory periphery circuits are mostly based on CMOS technology; the output is voltage. Because the memory states do not change during computation or post-computation, this type of architecture will not affect the endurance of the memory array. During computations, the sense amplifiers and analog-to-digital converters are shared, which causes performance degradation.

The Von-Neumann architecture faces various challenges while scaling down existing technology without compromising efficient computation. The complexity and large volume requirement for realizing neural network algorithms to hardware demands the characteristics of scalability, non-volatility, high density for integration, and low area and power consumption. The evolving resistive memory devices and memristors integrated with transistor technology are good candidates for mimicking synapses in hardware neural network implementations. Memristive devices mimic synapses in the human brain. Hence, memristors mimic synapses in neural network hardware implementations. The characteristics of memory resistors such as scalability, nonvolatility, transistor compatibility, high density for integration, and low power and area consumption, make them suitable for neural network implementations. They are also flexible for acting as multi-level cell memory, Scaling by three-dimensional stacking, and multilayer cells, which gives a higher level of scalability. Neural network weights are mapped to the conductance values of the memristor, which helps to emulate the weighted summation operation in neural network implementation.

The emerging Neuromorphic computing [15] technology brings high-performance computations in analog, digital and mixed-signal domains that are brain-inspired [16]. Neuromorphic computers draw inspiration from the structure and functions of neurons and synapses found in the human brain. Processing and storage functionalities highly resemble human intelligence. Neuromorphic computers use programming algorithms based on different neural networks. It differs from Von-Neumann computers. The processing and storing are performed by the CPU and memory units separately in the case of Von-Neumann. Hence, neuromorphic computing simplifies computations through parallel processing and storage without requiring separate locations.

The computations performed in neuromorphic computing architectures are parallel and comparatively simple compared to the Von-Neumann architecture [17]. The collocation of memory and processing helps reduce the throughput and power requirements required for data transfer. The flexibility

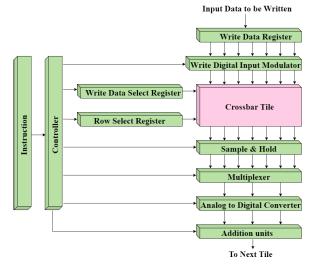

**FIGURE 2.** Functional blocks of neuromorphic computing hardware architecture.

to scale helps build larger networks based on different applications in artificial intelligence, machine learning, etc.

The Spiking Neural Network (SNN) is inspired by biological neural systems and performs computations in which neurons and synapses include notions of time. SNN algorithms comprise neurons and synapses associated with time delay for neuromorphic computing, which is significantly different from other neural networks [18]. Different neuron models are there like Integrate-and-Fire, Hodgkin-Huxley neuron model, etc. Spikes fire when the charge is integrated over time and meets the threshold in the case of Integrate-and-Fire. The neurons will have a rest time after firing, which is called the refractory period. In SNN, both neurons and synapses include time components based on which functionalities vary. Based on the network activity, the synapse's weight value changes. In a neuromorphic architecture, one can program neuron thresholds, delay values, and synaptic weights. In realizing SNN on neuromorphic hardware, information asynchronously propagates throughout the network, which can be treated as event-driven and fits well with temporal dynamics.

For Spiking Neural Networks, TENNLab has different architectures. Two of these are WHETSTONE, NIDA, MrDANNA and DANNA2. The DANNA2 is a twodimensional architecture. Properties such as synaptic weight and neuron threshold are represented by integers. In NIDA, the length of the synapses determines synaptic delays in the three-dimensional architecture. In MrDANNA, the architecture was implemented using memristors. The three-dimensional spiking architecture WHETSTONE stores elements at a floating point. TENNLab implemented a two-dimensional spiking architecture with FPGA, software and Very Large Scale Integration implementations [19].

The modulation of synaptic strength is contingent on the activity of connected neurons, a characteristic that can be theorized as a learning mechanism. Spike-timing-dependent

54022

plasticity (STDP) is the prevalent synaptic plasticity mechanism employed in neuromorphic computing. It involves adjusting weights based on the relative spike timings between pre and post-synaptic neurons. Recurrent Neural Networks with synaptic plasticity and delays are a broader class of SNN used for modelling. An example of such a class of networks is polychronization networks, which are implemented for spatio-temporal classifications.

#### A. NEUROMORPHIC COMPUTING: ARCHITECTURES

AI systems consistently outperform computation and storage. The in-memory computing approach which closely resides in the human brain is inspired by the learning, processing, and storing capabilities of the human brain with extremely low power, latency, and highly dense architecture. Memristive devices that offer highly dense memories can potentially emulate the human brain. They are analog programmable devices that can be programmed to desired conductance states, and they retain their latest attained resistance value. It acts as a non-volatile memory. Because computations are naturally analog, analog memristive computing is widely accepted and considers memory and the connection of memories as a type of intelligence. The possibility of lower signal attenuation issues, reduced parasitic impact, computation process before noise build-up, performance of Multiply and Accumulate (MAC)operation, reduction in the number of computational blocks, and dense architecture with reduced power, area, and latency enhances the demand for memristive computing in neuromorphic applications [20], [21], [22], [23].

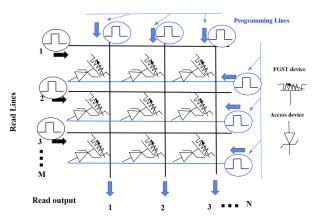

In the crossbar arrangement, memristors and transistors are arranged in a matrix form. Transistors are selector devices. Each memory cell consists of a memristor and transistor [24]. There are multiple inputs and outputs. The Input voltages are fed through the rows and the output currents are read from the columns. The current read equals the result of the multiplication and accumulation operation carried out between the input voltages and the equivalent conductance of the memristor and transistor. The Multiplication and accumulation operations in a memristive crossbar emulate the weighted summation operation in neural network [25], [26]. In neural network implementations, the weights are mapped to the conductance values of the memristor. Some of the application areas of crossbars are neural networks (Artificial Neural Networks, Convolutional Neural Networks, Deep Neural Networks, Spiking Neural Networks, Cellular Neural Networks), Analog/Digital Memory (associative, long-term memory, Multi-level memory, NAND.etc), and Solvers (Linear Equations, Partial Differential Equations, Markov Chains, etc), analog/digital logic gates (threshold logic, bio-inspired,.etc), cryptography (PUF), image processing (Cellular Neural Networks, object detection, edge detection, face detection, etc.).

Fig. 2 shows a detailed neuromorphic architecture block diagram having the major components along with the

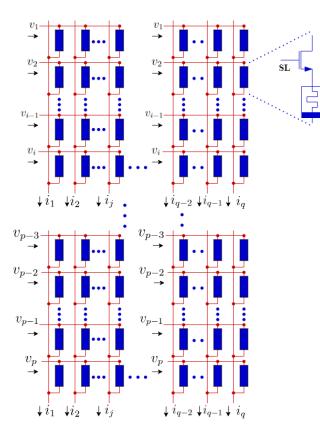

**FIGURE 3.** The tiled architecture of a memristive crossbar with  $p \times q$  cells implemented using multiple sub crossbars each of size  $i \times j$ . The number of sub-crossbars for rows and columns is c and d where  $p = c \times i$  and  $q = d \times j$ .

crossbar array. The write, read, and computation operations are executed using a crossbar. Computational operations include logical, addition, and multiplication operations.

# 1) WRITE OPERATION

To which row and column of the crossbar the data need to be fed should be specified. Three registers are assigned to perfom the task. The Write Data register (WD register) is used to feed the data, that be written to the crossbar. The length of the WD register depends on the width of the crossbar and the number of conductance levels that the memristors can program. To address the issues of endurance and power consumption, it is not necessary to select all elements in the array for writing data. A Write Data Select register (WDS register) is used to select the columns to be activated (Particularly for write-verify operation). A Row Select register (RS register) is used to select the desired row to which the data must be written. Depending on the crossbar technology, the voltage required to be applied to the crossbar varies. Digital-to-Analog Converter (DAC) converts data from digital to analog. Different voltage levels must be applied to the gate and source of the target row.

## 2) READ AND COMPUTATIONAL OPERATIONS

In architecture, the output generated by different operations must be read by the peripheral circuit. This can be a direct memory read or the result of computational operations. After matrix multiplication, the generated analog result needs to be captured by a sample and hold circuit. This sample and hold circuit helps to separate the execution in an array and the operations in read-out circuitry. This helps to pipeline the system. The results, in analog form, are given to the Analog-to- Digital Converter/ Sense Amplifiers (ADC/SA) for conversion to the digital domain. To avoid issues of high area and power consumption, the ADCs are not allocated to each column. Multiplexers are used to share several columns with an ADC. Additional computational operations were performed using the addition unit.

# III. MODULAR AND THREE-DIMENSIONAL CROSSBAR ARRAY ARCHITECTURES

The neural network implementation of a memristive crossbar array uses two architectures, two-dimensional and threedimensional. The two-dimensional tiled architecture of a memristive crossbar array is more widely used than the threedimensional architecture, which is still evolving.

#### A. MODULAR ARCHITECTURE

To achieve highly complex neural applications, a large memristive crossbar array must be created. Large memristive crossbar arrays are limited by the sneak current issue, which causes read-out current errors, a lack of accuracy, and power loss. The influence of the sneak path issues is addressed by dividing the larger crossbar array into smaller ones as shown in Fig. 3. This modular memristive crossbar array approach helps reduce the IR drop (Intermediate Resistance Drop) and sneak current issues to an extent, especially when it needs to be scaled. Each layer of the memristive crossbar array consists of memristors and selector devices arranged in matrix form. Each node can be accessed using its corresponding rows and columns. These resistive memory devices, along with selector devices, are responsible for emulating the synapses in neural networks. By adjusting the different parameters of these memristive devices through amplitude and frequency adjustment of the applied voltage, with the help of selector devices, different conductance states are attained. A modular crossbar array is designed by breaking a large memristive crossbar array into smaller modules by dividing them into rows from several small modules of equal size. The number of rows in each module equals the total number of rows in the larger array divided by the total number of modules. For each module, the number of columns is the same for each module. The total output current from the column of the larger array is equal to the summation of the currents from the corresponding columns of each module. The Other columns operate simultaneously in the same routing mechanism. This approach provides an appropriate restriction on the path of the leakage current. In the Modular Memristive Crossbar Array approach, the path of the leakage current is restricted by dividing a larger crossbar array into several modules. Owing to the reduced sneak path current, the read-out current error is also reduced.

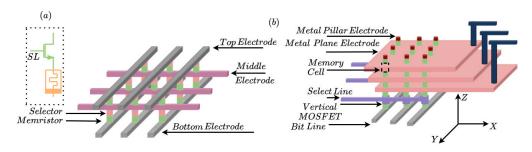

**FIGURE 4.** Three-dimensional architecture of memristor crossbar array in which each node contains the memory device and transistor (a) Horizontally stacked crossbar array (b) Vertical crossbar array.

Further Processing

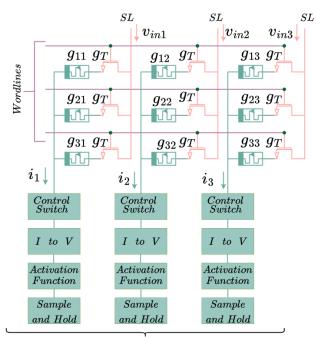

**FIGURE 5.** Memristor-crossbar architecture with inputs  $v_1$ ,  $v_2$ ,  $v_3$  and output currents  $i_1$ ,  $i_2$ ,  $i_3$ . The conductance of memristors is denoted as  $g_{mn}$  and that of transistors is denoted by  $g_T$ . The intermediate circuitry consists of a control switch, a current-to-voltage converter, a sample and hold circuit, and circuitry corresponding to the activation function.

A more accurate implementation of neural networks can be achieved because of the reduced relative current error.

#### **B. THREE-DIMENSIONAL ARCHITECTURE**

The two-dimensional tiled architecture of a memristive crossbar array restricts the possibility of implementing a neural network with several layers above a specific limit. To address this limitation, the three-dimensional arrangement of crossbar arrays provides a highly dense arrangement of devices. A neural network with many layers does not contribute significantly to the chip area when using a threedimensional architecture. Reduced latency for operation also helps reduce power. A more advanced scheduling mechanism for writing, reading, and computation operations

54024

in a three-dimensional architecture further helps reduce energy consumption.

When hardware neuromorphic computing requires wider and deeper neural networks to implement complex functionalities, the three-dimensional integration of memristive crossbar arrays will be more efficient and effective, as shown in Fig. 4. Hardware implementation of a neuromorphic chip for high-density applications, memristors can be scaled with three-dimensional integration to function as multilayered neural networks with minimum area requirement. Threedimensional integration can be performed in two ways. Vertically stacked three-dimensional crossbar arrays [27].

In the three-dimensional horizontally stacked crossbar arrays shown in Fig. 4(a), a higher density can be attained by, vertically stacking two-dimensional crossbar arrays. Owing to the flexibility to scale laterally, peripheral circuits can be placed under crossbar arrays to obtain a more compact design, and a separate selector or transistor can be accompanied by a resistive memory. Hence, the selector and transistor can be individually optimized. The number of interconnections can be reduced to simplify the fabrication process using a shared middle electrode. This shared middle electrode can be either a bit line or word line. If bit lines are shared, the number of peripheral circuits can be reduced because the connected read-out circuits, including sense amplifiers and current-to-voltage converters, can be reduced. Hence, it is preferable to obtain higher power and area efficiency. In this type of three-dimensional integration, a minimum of three major lithography and etching steps are required for fabrication. The challenge in the three-dimensional integration is increasing the number of stacking layers, and the number of interconnects also increases accordingly and demands more lithographic and etching processes. Staircasing the interconnects to both the bit lines and word lines will be another challenge, because different lengths of the interconnections cause different voltage drops among different layers.

By fabricating vertical crossbar arrays, as shown in Fig. 4(b), the challenges encountered with horizontal crossbar arrays can be addressed. This can be treated as a word-plane-type crossbar array. Here the plane electrode serves

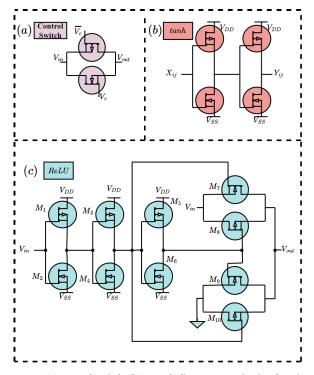

**FIGURE 6.** (a) Control Switch, (b) Hyperbolic tangent activation function (c) ReLU activation function.

as the wordline. Memristors that can be treated as vertical memory elements are formed at the crosspoints of each pillar electrode and plane electrode. To select the bitline, a vertical mosfet is used in which the gate is controlled by the selected line. In this type of three-dimensional arrangement, only one critical photolithography is needed, and hence the fabrication cost is reduced. In this case, there are also challenges such as etching deep holes.

# IV. THE CIRCUIT-LEVEL IMPLEMENTATION OF NEUROMORPHIC COMPUTING ARCHITECTURES

Complex neural networks are integrated with edge devices using CMOS-Memristive neuromorphic circuits because they are programmable, non-volatile devices capable of in-memory computing [28]. This helps to avoid sending large amounts of data collected by edge devices to the processing unit and memory and provides limited area and power consumption. As mentioned in the previous sections, crossbar array nodes consisting of transistor-memristor pairs are used to accelerate multiplication and accumulation operations for neural networks in hardware implementations. Different neural networks such as Artificial Neural Networks, and Long Short-Term Memory networks, are implemented in hardware using one transistor-one memristor crossbars.

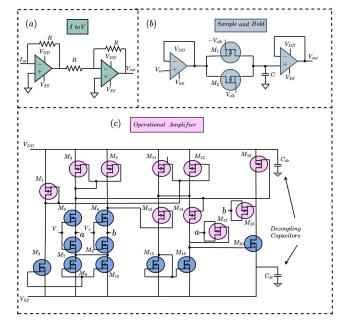

Fig. 5, 6, and 7 refer to the circuits involved in the neuromorphic hardware implementations. The crossbar circuits, activation functions, control switches, sample and hold, and current-to-voltage converters are based on CMOS circuits. The convolution and deconvolution operations required for

neural networks are realized using memristive crossbars and, their sizes depends on the input image. Memristors are programmed to the desired conductance states with the help of transistor selectors based on the mapping of weights; accordingly, a weighted summation is performed. In neural network implementation using a memristive crossbar architecture, control switches control the sequential processing of the rows and columns of the crossbar. The control switches assist in facilitating the sequential processing of the crossbar columns. The switching transistors, accompanied by resistive memory devices, are connected to the control voltage at the drain rather than at the source to improve the linearity of the switch. It also helps reduce the leakage current when the control switch is off. A simple control switch is shown in Fig. 6(a). When the voltage at  $V_c$  is elevated, the input to the NMOS is in a high state, while the input to the PMOS is in a low state. Hence, the NMOS and PMOS are turned on. It acts as a common resistance path; in other words, it acts as a short circuit. Input  $v_{in}$  is passed to the output. When Vc is low, the input to the NMOS is low, and the PMOS is high. Hence NMOS and PMOS are turned off. It will act as a high resistance path, or in other words, as an open circuit. The input  $v_{in}$  will not be passed to the output, and the realization of some activation functions using transistor technology is illustrated in Fig. 6(b) and (c). Fig. 6(b) shows the Hyperbolic tangent (tanh) activation function. The two cascaded inverters and biasing voltages  $V_{DD}$  and  $V_{SS}$  realize the tanh activation function. Fig. 6(c) shows the activation function ReLU (Rectified Linear Unit). Two transmission gates exist in a ReLU circuit.  $M_1, M_2, M_7$  and  $M_8$  are supplied with input voltage. The threshold voltages of the inverters are 0. When the input signal is positive, M7 and M8 are on, which can be treated as under the condition of the transmission gate, and the input is passed to the output. When the input signal is negative, M9 and M10 are on, which can be treated as the on condition of the second transmission gate, and the input is passed to the output(which is grounded).

The circuit diagram of the opamp and the circuits designed using the opamp are shown in Fig. 7. A circuit diagram of the opamp is shown in Fig. 7(c). It consists of two differential stages and a common gain stage. The output current read from the columns was converted into voltage using opamp-based current-to-voltage converters. As shown in the circuit diagram in Fig. 7(a), the I- to-V converter gives an inverted output after the first stage, which is equal to the product of the input voltage and feedback resistance. The second stage gives a non-inverted output, which also equals the product of the input (output of the first stage) and the feedback resistance. During the sequential processing of crossbar columns, an analog Sample and Hold circuit are used to retain the voltage signal as shown in Fig. 7(b). It comprises two voltage buffers to mitigate the impact of signals from other circuit components on the sampled signal, along with a single sample and hold component. The input is sampled when  $V_{clk}$  is high. The output from the activation functions can be read  $V_{clk}$  will be high until the last column is read.

FIGURE 7. (a) Current-to-voltage converter, (b) Sample and hold circuit, (c) Opamp circuit with two differential stages and one gain stage.

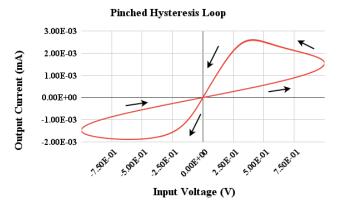

**FIGURE 8.** Pinched Hysteresis of a memristor in which the output current lags behind the input voltage.

#### **V. MEMRISTIVE DEVICES**

Memristors, operating as two-terminal devices, display resistance that is affected by factors such as the magnitude, applied voltage, and polarity. Even in the absence of an applied voltage, the resistance remains, resulting in non-linear and memory characteristics. Several types of memristors exist, each with unique characteristics and materials. Several emerging memristors, including resistive random access memory (ReRAM), Phase Change Memory (PCM), and Spin-Torque Transfer RAM (STT-RAM), operate based on resistive switching in memristor materials. Nevertheless, the specific mechanism of resistive switching varies among memristors.

The characteristics of a memristor showing the variation in the output current with respect to the input voltage is shown in Fig. 8. The output current lags behind the input voltage, resulting in a pinched hysteresis loop that passes through the origin. Each slope refers to a conductance state that can be programmed. When the frequency increased, the area of the pinched hysteresis loop decreased. At a higher frequency, it appears as a straight line.

#### A. RESISTIVE RANDOM ACCESS MEMORY (RERAM)

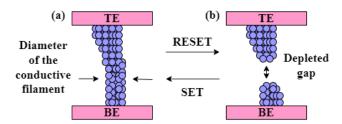

ReRAM, which is an emerging resistive memory, has low writing energy and high density. ReRAM is also suitable for building low-latency memories. It also provides a high endurance (10<sup>10</sup>) also. Technologies that use variations in resistance to store information are called resistive memory. ReRAM especially points to metal-oxide Resistive Random Access Memory because metal oxide is used as the storage medium. ReRAM consists of two electrodes (top and bottom electrodes) and a metal-oxide layer sandwiched between them, as shown in Fig. 9. To switch the resistive state of a ReRAM cell, an external voltage of a particular polarity, duration, and magnitude is applied. SET (switching from high resistance state to low resistance state) and RESET (switching from low resistance state to high resistance state) are controlled by the external voltage. The switching process of the ReRAM is based on the formation and rupture of the conductive filament between the electrodes. The SET process involves the regeneration of conductive filament by drifting oxide ions to the anode (positive electrode) and leaving oxide vacancies in the metal oxide layer. In the RESET process, oxide ions are returned to the oxide layer by the force of an electric field, followed by recombination with oxide vacancies. As a result, the conductive filament is cut off, and the ReRAM is transferred to a high resistance state. The resistance of a memristor can be programmed to vary values between these two high resistance state and low resistance state, by applying voltage pulses and changing their amplitude and frequency. The larger the size of the conductive filament, the smaller the resistance. Multiple states are achieved by changing the strength of the conductive filament, which depends on the applied voltage. In digital memristive devices, the initial formation process of the conductive filament is termed electroforming. After the electroforming process, the filamentary switching model functions. The voltage required for electroforming is higher than that required for switching. Analog memristive devices are free of electroforming. The Characteristics of ReRAM vary with the materials. ReRAM has the advantages of high endurance  $(10^{10})$ , scalability, and switching speed with relatively less energy consumption and latency.

## B. PHASE CHANGE MEMORY (PCM)

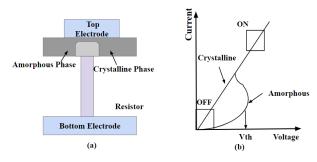

Phase Change Memory (PCM), also known as Perfect RAM (PRAM), PCRAM, and Chalcogenide RAM (CRAM), belongs to the category of emerging non-volatile memories that rely on the principles of chalcogenide glass, and possess two distinct phase states [29]. PCM's switching operation of

**FIGURE 9.** ReRAM device: Set (Transition from High Resistance State to Low Resistance State) and Reset (Low Resistance State to High Resistance State) operations. (a) The top Electrode and Bottom Electrode are connected by a Conductive Filament in Low Resistance State. (b) In High resistance, this Conductive Filament disconnects.

PCMs relies on the phase change of the material, transitioning from an amorphous state to a crystalline state. This process involves two distinct resistance levels: low and high. The PCM technology stores information through the transition from a low-resistance crystalline state to a high-resistance amorphous state. Shifting from the amorphous phase to the crystalline phase is considered the SET process whereas the reverse method from the crystalline phase to the amorphous phase is considered RESET switching. The PCM cell architecture is presented in Fig.10 (a). PCM cells exhibit a low resistance state (LRS) at high temperatures. Applying an external power supply and current allows PCM cells to rapidly RESET to a high-resistance state (HRS) in a short time-period. This RESET process involves a transition from a crystalline state to amorphous phase state. Achieving a return to a crystalline state involves the SET process, which requires an external current pulse at the melting temperature. However, the crystallization process requires a longer duration. The I-V characteristics of the PCM cells are presented in Fig. 10 (b) [30].

**FIGURE 10.** PCM: (a) Crystalline state vs amorphous state. (b) I-V characteristics of PCM cells.

The SET and RESET processes are responsible for toggling the device between ON and OFF states. During the transition between ON and OFF states, a brief gap exists in the OFF region owing to the phase-switching process. PCM technology exhibits faster operation, lower power consumption, lower supply voltage, and superior endurance compared to flash memory technology.

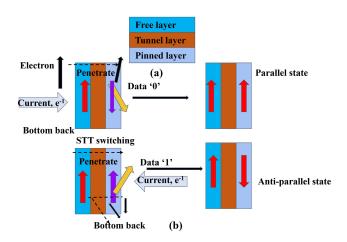

## C. SPIN-TRANSFER TORQUE MAGNETIC RANDOM-ACCESS MEMORY

Magnetic Tunnel Junction Spin-Transfer Torque (MTJ STT) technology is an important mechanism in Magnetic Random-Access Memory (MRAM), that employs a magnetic tunnel junction that comprising layers of ferromagnetic material separated by an insulating tunnel barrier. In STT MRAM, a magnetic tunnel junction (MTJ) consists of three layers: two ferromagnetic (FM) layers separated by a thin insulating tunneling barrier. Within the MTJ, the fixed layer is magnetically linked with an antiferromagnet (AFM), which requires stable magnetization while undergoing voltage changes. The resistance within the MTJ varies between low when the magnetizations of the FM layers are parallel and high when they are anti-parallel. This variation can be quantified using the tunneling magnetoresistance (TMR) ratio [31].

FIGURE 11. Figure caption illustrating the MTJ structure and the process of spin transfer torque-induced magnetization switching: transitioning from an anti-parallel to parallel orientation (top) and from parallel to anti-parallel (bottom).

The spin-transfer torque (STT) influences the magnetization of the MTJ's free layer when an unpolarized electric current becomes spin-polarized upon passing through the fixed layer [32]. Fig. 11 depicts the cell structure of the MTJ STT switching mechanism, transitioning from an anti-parallel orientation to a parallel orientation. During this process, electrons move from the pinned layer to the free layer, where magnetization is easily rotatable. As electrons rotate the magnetization, they align in the same spin direction, generating a spin-polarized current upon traversing the pinned layer. This spin-polarized current then affects the free layer, subjecting it to torque based on spin angular momentum. The magnetic state of the free layer changed when the torque exceed a specific threshold value.

For a transition from a parallel to an anti-parallel orientation (illustrated in Fig. 11(b)), electron flow needs to occur from the free layer to the pinned layer. Electrons that maintain the same spin direction after passing through the free layer and reaching the pinned layer facilitate this

FIGURE 12. Schematic of the point contact transistor.

transition. Conversely, electrons with different spin directions are reflected at the insulator-pinned layer boundary and bounce back to the free layer. This reflection induces a spin transfer torque on the free layer, ultimately switching its magnetization when the torque exceeds the threshold value.

# VI. TRANSISTOR TECHNOLOGY IN NEUROMORPHIC DEVICES

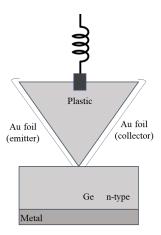

## A. EVOLUTION OF TRANSISTOR TECHNOLOGY

The first seed of the electronics industry called the 'vacuum tube' was invented in 1904 [33], as a device designed to regulate electron flow within a vacuum. However, during World War II, the demand for vacuum tubes surged, revealing their limitations. These tubes are plagued by increasing complexity, cost, and power consumption which degrade their reliability. As the 1940s drew to a close, the electronic industry discovered two semiconductor devices: the point-contact germanium transistor and the bipolar junction transistor (BJT) [34] as shown in Fig. 12.

In a landmark achievement in 1947, a team comprising William Shockley, John Bardeen, and Walter Brattain introduced the point-contact transistor [35]. A year later, in 1948, William Shockley pioneered BJT. This three-terminal device plays a crucial role in our everyday existence as amplifiers and switch, impacting our lives in numerous subtle yet significant ways. BJTs typically consume more power and have lower switching speeds which makes them less efficient in applications where power efficiency is critical. The transistor's trans-formative legacy extends to the evolution of field effect transistors (FETs). FETs are voltage-controlled devices, that provide a high level of performance in terms of power efficiency and reliability. The FET uses an electric field to control the current flow making it a voltage device instead of a current device.

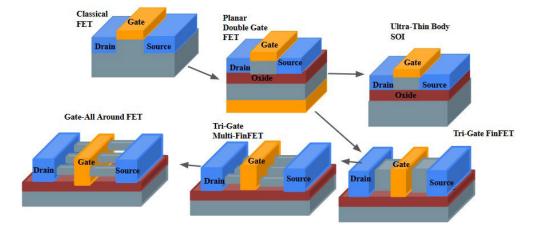

The very first FET device called the Junction Field Effect Transistor (JFET) patented by Heinrich Welker in 1945, is often used in low to medium-frequency amplification and switching circuits [36]. Despite the invention of the junction field effect transistor, the journey was far from over, as its performance fell short of expectations, leaving room for exploration and improvement in other forms of the device. The JFET device has introduced more gate leakage current owing to high drain voltage which degrades the device's performance. In 1959, Mohamed Atalla and Dawon Kahng [37] discovered the metal-oxide-semiconductor field effect transistor (MOSFET) [38] considered the driving engine of the semiconductor industry. MOSFETs are incredibly versatile 20th-century inventions, which have become iconic for their role in making tiny chips, MOSFETs are used in almost all electronic devices, from amplifiers and voltage regulators to microprocessors and memory cells. They are also essential in power management circuits and switching applications. It packed more into less space, remained affordable, and ran faster. For over 40 years, MOSFETs have dominated the semiconductor industry. Scaling is an important approach, for increasing the packing density of the chip. Scaling enhances the device's speed functionality with a minimum fabrication cost. However, MOSFET faces various unwanted problems owing to reducing the device dimensions. The overscaling of device dimensions in MOSFET introduces a non-ideal effect called short channel effects (SCEs) [39]. These SCEs affect the device's efficiency. In 1997, Dr. Chenming Hu invented a fin-shaped field effect transistor (FinFET) [40]. FinFET is a triple gate device, that has better electrostatic gate control capability over the channel which reduces the leakage current. Intel was the first company to adopt FinFET technology over CMOS technology in 2012. FinFET technology [40] has been used in the semiconductor industry for more than one decade.

FETs are a broad category of transistors that are used in various applications from sensors to memories [41]. The Metal-Semiconductor Field-Effect Transistor (MESFET) [42] is a type of field-effect transistor (FET) commonly used in high-frequency and high-speed applications, particularly in Radio Frequency (RF) and microwave circuits, including satellite communication, radar systems, and wireless communication. MESFETs are typically fabricated using compound semiconductor materials such as gallium arsenide (GaAs) or indium phosphide (InP). These materials offer a high electron mobility, which is advantageous for high-frequency applications.

Graphene FETs (GFETs) [43] offer unparalleled potential as electronic devices in the semiconductor industry, particularly for high-frequency and high-speed applications. Departing from the conventional FET design, GFETs utilize graphene as the channel material instead of silicon, capitalizing on graphene's superior mobility, enhanced thermal conductivity, and lower parasitic capacitance. These unique properties empower the seamless design of cutting-edge RF electronic circuits, making GFETs a promising choice for the future of semiconductor technology. The various FET configurations are presented in Fig. 13.

Transistor technology has undergone a remarkable evolution since the birth of the transistor, propelling the world into

FIGURE 13. Schematic structure of various FETs.

FIGURE 14. IGTs structure.

the digital age. It has come a long way since its inception, transforming the world of electronics and paving the way for countless technological advancements. This demonstrates a remarkable tale of miniaturization, efficiency, and exponential growth. The evolution of transistor technology has revolutionized the computing, communication, and countless industries, leaving an indelible mark in the modern world. Over the decades, transistors have shrunk in size, expanded in functionality, and become an integral part of our daily lives. The evolution of transistor technology from vacuum tubes to silicon transistors and beyond has been a defining factor in the electronics industry. The relentless pursuit of smaller, faster, and more efficient transistors has driven the evolution of technology. Transistors are used in many electronic devices, from tiny parts to big computers. Without them, many of our gadgets would not have worked. In the next section, we provide a detailed overview of the emerging memory devices for a better understanding.

# VII. TYPES OF TRANSISTORS USED IN NEUROMORPHIC DEVICES

## A. ION-GATE NEUROMORPHIC TRANSISTORS

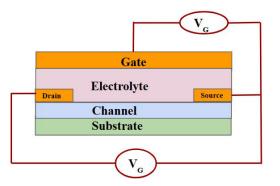

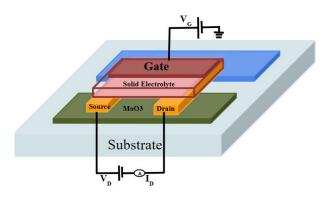

Ion-gate transistors (IGTs) share a similar structural and voltage bias configuration with MOSFETs as shown in Fig. 14. However, a crucial divergence arises from the choice

**FIGURE 15.** (a) Electrostatic doping mechanism with an impermeable channel (b) Electrochemical doping mechanism with a permeable channel.

of the gate dielectric materials. While MOSFETs rely on insulating gate dielectrics, IGTs opt for electrolytes, which serve dual purposes as electron insulators and ion conductors within the gate dielectric. These differences in the gate dielectrics lead to distinct working mechanisms for the two devices. MOSFETs fundamentally control the current flow when a supply voltage is applied to the gate and the gate to the drain terminal. The applied gate voltage determines the extent of control over the channel, allowing MOSFETs to act as crucial switches or amplifiers in electronic circuits [44]. This process exclusively involves electron

**FIGURE 16.** Transconductance ( $G_m = dI_D/dV_{GS}$ ) performance of IGTs Structure.

movement and is essentially a capacitive charging mechanism. On the other hand, IGTs follow the same roots as MOSFETs. In IGTs, the gate terminal bias governs the control of the current. However, in IGTs, the movement of ions within the electrolyte of IGTs, come into play at specific gate voltage levels. This ion movement is a critical factor in the distinctive working mechanism of IGTs within the electrolyte, which occurs at specific gate voltage levels. This ion movement is a key factor in the unique working mechanism of IGTs [45].

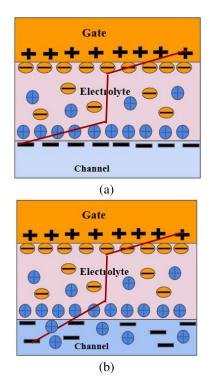

In IGTs structures, there are two distinct working mechanisms electrostatic and electrochemical carrier doping mechanisms, where impermeable and permeable channel materials can be considered [46]. Fig. 15(a) represents the schematic diagram of the IGTs where an impermeable channel is used. Applying a positive bias to the gate terminal in the presence of an electrolyte results in the attraction of cations to the negatively charged gate, while anions are repelled. While the channel remains impermeable, positive ions from the electrolyte gather near the interface between the electrolyte and the channel. This accumulation of oppositely charged ions creates an electric double layer (EDL), essentially forming a parallel plate capacitor structure, where one plate is formed by the accumulated positive ions and the other plate is the channel surface with induced negative ions. The formation of EDL is a fundamental concept in electrochemistry is widely utilized in various applications, including capacitors, supercapacitors, and electrochemical sensors, in which the charge separation at the interface plays a crucial role.

Fig. 15(b) the working function of the IGT is depicted, taking into account the permeable channel. Upon applying a positive voltage to the gate terminal, electrolyte ions start migrating toward the channel, facilitated by the channel's ability to permit ion passage through the interface. The electrolyte ions are injected more towards the channel owing to the high supply voltages. An opposite type of charge carrier was injected into the channel region to compensate for the injected electrolytic ions. The electrochemical

doping mechanism involves the injection of electrolytic ions whereas opposite ions move towards the gate. IGTbased electrochemical doping is also called electrochemical transistor (ECT). IGTs have polarized and nonpolarized gates, where the nonpolarized gate configuration boasts a higher capacitance value that enhances gate controllability compared to a polarized gate setup [47], [48]. The polarized gate can increase the gate controllability of the channel by enlarging the area of the gate-electrolyte interface.

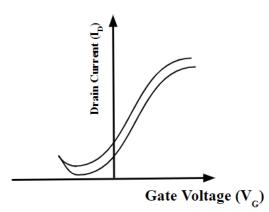

Fig.16 shows the transconductance performance of the IGT transistor, which IGT possesses a significant capacitance value, thereby enhancing the transconductance value in comparison to traditional transistors. This characteristic is advantageous for small signal amplification.

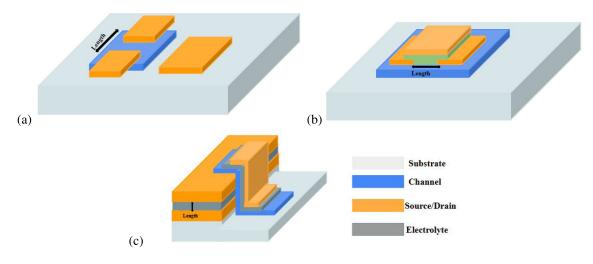

Different types of IGT structures exist in practical applications. They can be categorized into two primary groups: planar and vertical. Planar structures, in turn, can be further classified into co-planar and lateral thin-film transistor (TFT) structures. In the co-plane structure, the source, drain, and gate electrodes are placed in the same plane, as shown in Fig. 17(a). Within co-planar structures, the source, drain, and gate electrodes are commonly deposited simultaneously onto the substrate through methods like spin coating. These IGTs are ideal for sensors because of their simple design, easy fabrication, and the fact that they don't require device miniaturization

Another planar IGT structure lateral thin-film transistor is shown in Fig. 17(b). Lateral TFT-based IGTs have four specific configurations based on the locations of the source, drain, and gate electrodes: top-gate top contact, top-gate bottom contact, bottom-gate top contact, and bottom-gate bottom contact. Unlike co-plane architecture, lateral TFT designs are more mature in their processing and offer integration possibilities into arrays. However, the energy efficiency and processing speed of planar IGT structures need to be improved. To address these issues of planar IGT, a vertical field effect transistor (vFET) [49] has been demonstrated to improve the saturation current and switching frequency, as shown in Fig. 17(c). The vFET structure offers a higher saturation current with minimum operating voltage which reduces the total power consumption of the device [50]. A comparative analysis between the IGT and alternative devices for implementing neuromorphic computing is presented in Table 1.

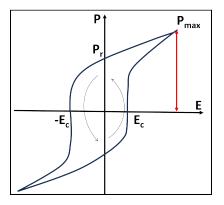

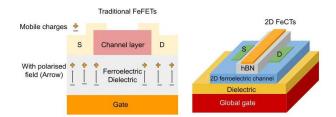

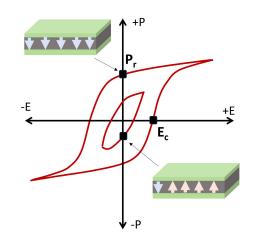

**B.** FERROELECTRIC-GATE NEUROMORPHIC TRANSISTORS Since the discovery of ferroelectricity in BaTiO<sub>3</sub>, ferroelectric materials, have attracted considerable attention [51]. Ferroelectric field effect transistors (FeFETs) use ferroelectric materials as gate dielectrics. FeFETs typically use the same designs as their conventional counterparts, but instead of relying on an external electric field, they control the conductance of the channel by polarization [52]. The loop in Fig. 18 shows a characteristic hysteresis loop that displays the relationship between the induced polarization and the applied electric field. The hysteresis loop shape

FIGURE 17. The basic structures of various IGTs. (a) Co-plane structure (b) Lateral TFT structure (c) Vertical structure.

signifies the inherent ferroelectric properties of the material including its coercive field ( $E_c$ ), remnant polarization ( $P_r$ ), and polarization saturation  $(P_{max})$ . The transistor provides features such as a high operating speed and multi-domain switching possibility and hence, is suitable for the application of neural computing. FeFETs can possess two architectures. The Metal-Ferroelectric-Insulator-Semiconductor (MFIS) or Metal-Ferroelectric-Metal-Insulator-Semiconductor(MFMIS). Lue et. al. provided detailed information on the simulation and modelling of these two types of transistors [53]. It discusses the behavior of the drain current, channel potential, surface band bending, and space charge density as functions of the drain voltage. This study uses a wide range of materials and geometric parameters to gain insight into the operation of FeFETs. It also describes the calculation algorithm used and states that the results are independent of the equivalent oxide thickness (EOT) of the insulator. The study mentioned that the hysteresis loop of the ferroelectric layer traces a clockwise direction for a p-type substrate and a counterclockwise direction for an n-type substrate.

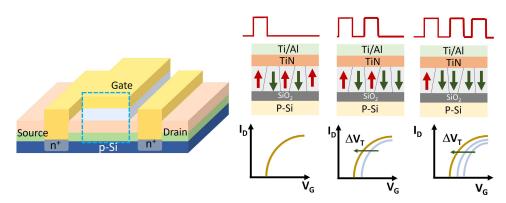

The diagram (Fig. 19) illustrates the conventional structure of a FeFET, the gate voltage pulses applied to it, the resulting multi-level polarization states, and the corresponding transfer curves [54]. By applying short voltage pulses to the gate, the threshold voltage of the underlying MOSFET channel can be gradually tuned, thereby adjusting the drain-to-source conductance. This feature allows the implementation of weight updates in FeFET synapses, enabling the storage and manipulation of analog synaptic weights in neural computing systems. The carrier concentration in the channel can be precisely and gradually adjusted by manipulating the polarization state of the ferroelectric dielectric using gate voltage pulses. This ability allows FeMFETs to distinguish various logic states, making them capable of serving as both memory and logic devices with non-volatile characteristics. In the context of neuromorphic transistors, the utilization of

**FIGURE 18.** Hysteresis loop illustrating the polarization-electric field (P-E) behavior of a ferroelectric material under varying electric fields. The hysteresis loop's shape signifies the material's inherent ferroelectric properties, including its coercive field ( $E_c$ ), remnant polarization ( $P_r$ ), and polarization saturation ( $P_{max}$ ).

multi-domain polarization switching enables multiple levels of channel conductance to be achieved. This capability is valuable for recording the synaptic weights in neuromorphic circuits.

The analog conductance modulation behavior in ferroelectric thin-film transistors (FeTFTs), comprising nanoscale ferroelectric materials and oxide semiconductors, was demonstrated by Lee et al. [55]. Precise control of the polarization changes within the nanoscale ferroelectric layer induces conductance modulation and depression characteristics in FeTFTs. These devices exhibit potentiation and depression properties characterized by high linearity, multiple states, and minimal cycle-to-cycle/device-to-device variations. Through simulations employing measured properties, a recognition accuracy of 91.1 % for handwritten digits was achieved by a neuromorphic system featuring FeTFTs as synaptic devices. This study presents a potential avenue for realizing neuromorphic hardware systems employing FeTFTs as synaptic devices. Takagi et. al. observed that, in the

**FIGURE 19.** The configuration of a FeFET, the applied gate voltage pulses, the numerous switching states of multi-domain partial polarisation, and the associated transfer curves are shown in an illustration [54].

FIGURE 20. Schematic of the structure of FG transistor.

case of small polarization regimes, a linear proportionality exists between the memory window (MW) and ferroelectric polarization [56]. The relationship between the MW of ferroelectric field-effect transistors (FeFETs) and the P-E hysteresis loop of a ferroelectric gate insulator was investigated theoretically in this study. Furthermore, it is determined that when the remanent polarization significantly exceeds the product of the permittivity and coercive field, the MW approaches a limiting value equivalent to 2 times the coercive field multiplied by the thickness of the ferroelectric material. Tunneling factors that may influence MW in practical FeFET devices are discussed, including the presence of interlayers, interface charges, and minor-loop operation.

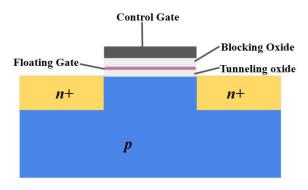

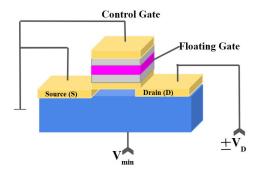

#### C. FLOATING GATE (FG) NEUROMORPHIC TRANSISTORS

A floating gate transistor is a type of transistor that uses a non-volatile memory device such as flash memory. The first metallic floating gate in a MOSFET was discovered by Kahng and Sze in 1967 [57].

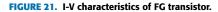

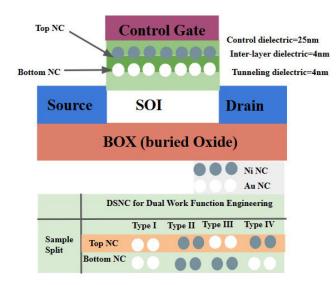

The structure of the FG transistor differs from that of a conventional MOSFET, as shown in Fig.20. A metallic floating gate was placed between two different dielectric layers with two different oxide thicknesses. The thick upper dielectric layer serves as an effective barrier, preventing the flow of charge carriers from the floating gate to the control gate during both programming and erasing processes. On the other hand, a lower thinner dielectric layer can block charge carriers from shifting from the semiconductor layer in the absence of a power supply. Therefore, charge carriers can be stored in the floating gate layer even after a power supply outage [58]. There are many ways in which the charge can shift to or from the floating gate of the transistor such as hot electron injection, Fowler-Nordheim (F-N) tunneling, and direct tunneling.

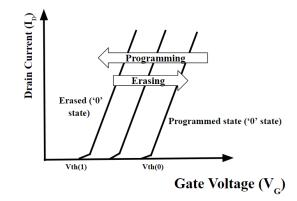

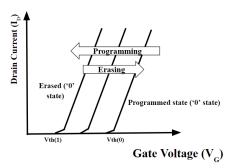

Fig.21 shows the I-V characteristics of the FG transistor. In an ideal MOSFET, the threshold voltage remains constant at a fixed drain voltage. However, for Floating Gate (FG) transistor devices, the threshold voltage changes because of the trapping of charge carriers in the floating gate. This phenomenon affects the conductivity during programming and erasing operations. When the threshold voltage value is designated as'0' or  $V_{Th}(0)$ , the Floating Gate (FG) is recognized as the 'programmed state' resulting from the injection of a negative charge. On the other hand, 'erased state' can be called when threshold voltage returns to  $V_{Th}(1)$  due to the supply of negative voltage at the gate electrode. In the erased state, no charges were trapped in the floating gate, signifying the 'OFF' or '0' state, while the programmed state is referred to as '1' or 'ON' state.

During hot electron injection programming, vertical and lateral electric fields must be applied. The lateral electric

FIGURE 22. Schematic structure of hot electron injection, Fowler-Nordheim tunneling, direct tunneling.

field provides sufficient energy to surpass the energy barrier separating the floating and semiconductor layers. The vertical electric field is generated by the gate voltage, which helps the charge carriers to be trapped in the floating gate layer. This process enables exceptionally rapid write speeds, typically within the microsecond range for a single data bit. Additionally, it enables write operations with significantly lower control gate voltages, making the memory efficient and responsive [59]. The Fowler-Nordheim (F-N) tunneling mechanism occurs because of the presence of a higher electric field, and charge carriers pass through the thin barrier. The thin barrier allows charge carriers to tunnel through it [60]. The F-N tunneling mechanism requires minimum energy for the process of 'program' and 'erase' operation and offers good efficiency compared to other injection methods. However, this process has some disadvantages owing to the high electric field and long access time. The direct tunneling (DT) mechanism occurs because of a higher electric field and extremely thin layers. Owing to the ultra-thin nature of the oxide layer in the DT process, the charge carriers can easily move. The direct tunneling method provides a faster programming speed with less power consumption. However, it reduces the data retention capabilities. To enhance charge retention, increasing the barrier height can be beneficial, which in turn reduces tunneling probabilities. In the DT mechanism, the tunnel oxide layer is generally constrained to around 6 nm. However, because of trap-assisted electron tunneling induced by oxide aging, a more realistic thickness may need to be increased to approximately 7-8 nm [61]. The schematic structure of the hot electron injection, Fowler-Nordheim tunneling, and direct tunneling mechanism ha shown in Fig.22. Conventional FG transistor faces several challenges owing to the over-scaling of the device dimensions. One main problem is the decreasing distance between cells, leading to cell-to-cell interference and parasitic capacitance. The reduction in oxide thickness enhances the tunneling issue which increases the leakage current, making it difficult to manage charge retention. Additionally, a smaller floating gate carries a small number of free electrons which degrades the performance of the device. Scientists have created several enhanced iterations of FG transistors aimed at improving their efficiency. Examples include silicon-oxidenitride-oxide-silicon (SONOS) [62], and nano-floating-gate (NFG) memory devices, which incorporate metal nanoparticles (NPs) and utilize organic/inorganic nano-materials in their dielectric layers [63]. All the modified structures of the FG transistor offer better durability, and less power consumption with a smaller chip size than conventional FG transistor. Modified structures can store multiple levels of data which attract the semiconductor memory industry. Liu et al. [64] constructed an organic FET (OFET) memory incorporating self-assembled gold nanoparticles (NPs) into the gate dielectric. Constructed on a silicon (Si) substrate to control the gate electrodes, the device utilized a 100 nm thick silicon oxide (SiO<sub>2</sub>) layer as the charge-blocking dielectric. Poly(3-hexylthiophene) (P3HT) serves as a semiconductor channel layer, with additional polyelectrolytes separating it and a poly(4-vinylphenol) (PVP) tunneling layer covering the gold nanoparticles (NPs). Despite exhibiting an impressive switching ratio of 1500, the device exhibits a relatively short retention time of 200 s. Ryu et al. [65] approached a non-volatile transistor memory in which a double-stacked layer of metal NPs was used, as shown in Fig.23. They formed various types of charge-tapping layers by depositing different sequences of gold (Au) and nickel (Ni) such as Ni/Ni, Au/Au, Ni/Au, and Au/Ni to observe the memory device performance. The utilization of both top and bottom charge-trapping layers (Au/Ni) has been observed to improve program/erase speeds significantly and notably extend data retention times. Chang et al. [66] demonstrated an FG memory device incorporating high-k oxide dielectrics, such as HfLaO, HfON, and HfO as the blocking, charge trapping, and tunneling dielectric layers, respectively. Memory devices provide a low program/erase voltage of 12 V and also contribute a programming speed of 1/100 ms.

Loai et al. introduced an energy-efficient memristive device-based FG FET device [38]. Operating in a subthreshold memristive mode, this distinctive device is referred to as the Y-flash [8], [34] and is engineered to be linearized for small change in signals. By incorporating recent advancements in memristive techniques utilized in small-scale selector-free dense integrated Artificial Neural Networks (ANNs) for spike-timing-dependent plasticity (STDP), Vector-Matrix Multiplication (VMM), associative memory, and classification training, we developed a practical and high-performance memristive device.

**FIGURE 23.** Schematic diagram of double-stacked metal nanocrystals (NC).

Through both theoretical analysis and experimental validation, our research demonstrated the viability of this memristive device for applications in high-performance neuromorphic computing. This innovative approach not only paves the way for energy-efficient computing but also opens up new possibilities for advanced neural network applications, making it a promising technology for the future of artificial intelligence and cognitive computing.

# D. PERSPECTIVE ON TRANSISTORS IN COMPUTING

Integrating various types of transistors into neuromorphic computing systems offers a holistic approach to emulate the complexity of the human brain. By combining their unique characteristics such as ion-based modulation, non-volatility, and analog behavior—neuromorphic systems can achieve energy-efficient, adaptive, and self-learning capabilities. These advancements have brought us closer to realizing artificial intelligence models that can learn, adapt, and process information in ways that resemble human cognition.

# VIII. INTEGRATION OF TRANSISTORS IN NEUROMORPHIC SYSTEMS

IGTs have evolved from traditional MOSFET, that were initially designed as switches for both analog and digital circuits. However, IGT can be used for sensor and neuromorphic computing. IGTs have a large channel capacitance which enhances the transconductance value, and can be applied for small signals.

IGT-based electrostatic and electrochemical doping mechanisms can make neural networks to study synapses in the brain. Lenz et al. [85] demonstrated a vertical structure IGT. Initially, they designed an Au/Ti/SiO<sub>2</sub>/Ti/Au stack with a cross structure and created empty spaces perpendicular to the stacking orientation with Ti and SiO<sub>2</sub> materials. The height of these voids corresponds to the length of the channel and

#### TABLE 1. Comparative analysis between IGT and alternative devices for implementing neuromorphic computing.

| Device | Maxi-  | Maxi-         | Maximum   | Non-      | Maxi-             | Maxi-  |  |

|--------|--------|---------------|-----------|-----------|-------------------|--------|--|

| name   | mum    | mum           | oper-     | linearity | mum               | mum    |  |

|        | no of  | oper-         | ating     |           | en-               | reten- |  |

|        | states | ation         | energy    |           | durance           | tion   |  |

|        |        | speed         |           |           |                   |        |  |

| IGT    | 10000  | 5ns           | 1.23fJ    | Low       | $10^{9}$          | >25 h  |  |

|        | [67]   | [68]          | [69]      |           | [70]              | [71]   |  |

| PCM    | 26     | 700ps         | 1 pJ [74] | High      | 10 <sup>11</sup>  | >1000  |  |

|        | [72]   | [73]          | -         | -         | [75]              | years  |  |

|        |        |               |           |           |                   | @ RT   |  |

|        |        |               |           |           |                   | [76]   |  |

| MOSFET | 2 [3]  | $< 10^{1}$ ns | 1–10 fJ   | High      | >10 <sup>16</sup> | 1-10   |  |

|        |        | DRAM          | [3]       |           | [3]               | ns [3] |  |

|        |        | [3]           |           |           |                   |        |  |

| RRAM   | 64     | 85ps          | 115 fJ    | High      | $10^{12}$         | >1000  |  |

|        | [77]   | [78]          | [79]      |           | [80]              | years  |  |

|        |        |               |           |           |                   | @ RT   |  |

|        |        |               |           |           |                   | [81]   |  |

| FTJ    | 10     | 10ns          | 100 fJ    | High      | 4x10 <sup>6</sup> | 3 days |  |

| /FeFET | [82]   | [82]          | [82]      |           | [83]              | [84]   |  |

FIGURE 24. Schematic of the structure of IGT based on MoO<sub>3</sub> material.

their depths, determined by SiO<sub>2</sub> thickness and etching time, respectively, were precisely controlled. The proposed device uses a spin coating technique to fill the constructed voids. It is observed that the proposed vertical IGT improvised the high on-state current densities and switching ratio by <3mA cm<sup>-2</sup> and 10<sup>8</sup>, respectively. The power consumption has been optimized by 100 fJ per event which is good compared to other similar types of devices.

Shang et al. [86] designed an IGT based on layered transition metal oxide -phase molybdenum oxide ( $\alpha$ -MoO<sub>3</sub>) as shown in Fig. 24. The higher band-gap characteristics of  $\alpha$ -MoO<sub>3</sub> make it an insulator. They considered Li<sup>+</sup> electrolyte solid material instead of a liquid material. When a supply voltage was applied to the gate terminal, tiny particles called Li<sup>+</sup> to move in and out of the  $\alpha$ -MoO<sub>3</sub> material. The proposed transistor with Li<sup>+</sup> as the dopants offers a channel conductance switching value of  $< 10^{-5}$  Torr. These specialized devices are highly energy-efficient and can be employed to construct large-scale computer systems by densely packing them together.

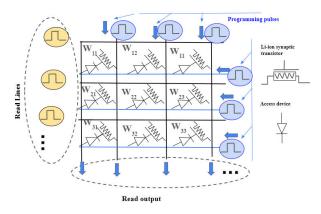

Fig. 25 schematically illustrates a crossbar array comprising a synaptic-weight layer. The weighted summation of the neural network is emulated in the arrangement by calculating vector-matrix multiplication. The switching of

FIGURE 25. Diagram of the synaptic weight layer comprising an IGT crossbar array.

the devices can be performed by programming by applying suitable voltage pulses along the horizontal and vertical lines. Synaptic transistors, based on  $\alpha$ -MoO<sub>3</sub>, serve as memory elements within the crossbar array [46]. By applying a gate voltage, the interaction of lithium ions with the layered  $\alpha$ -MoO<sub>3</sub> channel results in analog switching of the  $\alpha$ -MoO<sub>3</sub> layer. The ionic liquid was subsequently substituted with a solid-state Li<sup>+</sup> electrolyte. Li<sup>+</sup> electrolytes are considered dopants that enhance the switching of the channel conductance under vacuum conditions. Additionally, the  $\alpha$ -MoO<sub>3</sub>-based synaptic transistors demonstrate exceptionally low conductance (<75 nS), making them highly advantageous for energy efficiency and the manufacture of extensive crossbar arrays.

Zhu et al. [87] proposed a latterly coupled IGT featuring a co-planar architecture that operates on an electrostatic doping mechanism. This structure changes the electrical properties to mimic how synapses in the brain work for short-term memory. The planar structure of an IGT can be built with multiple gates and channels. Recently, researchers have been paying considerable attention to the electrochemical doping mechanism of IGT owing to its non-volatile characteristics. This method does not forget information when the power is turned off, which makes it useful for mimicking the long-term memory of the synapses in the brain. Burgt et al. [88] demonstrated a neuromorphic organic transistor based on an electrostatic doping mechanism with affordable plastic materials that act like an artificial synapse [89]. The proposed transistor provides non-volatile and reproducible states (more than 500) at a very low operating voltage, as noted in [90]. However, the devices exhibited a higher channel conductance value ranging from 500 to - 2000  $\mu$ S.

More electrical power was required to carry the current capacity when the array dimensions were increased. Nevertheless, by combining a conductive polymer with an insulator, the device consumes less electricity. This mixing composition offers a lower synaptic weight readout (< 10 nA) [91].

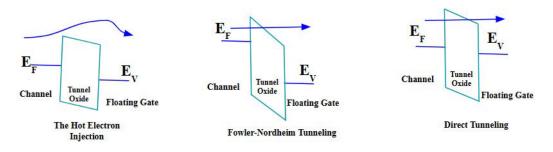

Wang et al. proposed a ferroelectric material-based transistor for applications in neural computing [92]. The device

**IEEE**Access

FIGURE 26. Schematic diagram representing the Ferroelectric field effect transistor structure [92].

FIGURE 27. Implementation of analog vector-matrix multiplication and row-wise parallel weight updates via a Ferroelectric Field-Effect Transistor (FeFET) pseudo-crossbar array. Incorporating access transistors alongside FeFET storage devices in synaptic weight cells to minimize disturbance effects [54].

structure of ferroelectric channel transistors (FeCTs) is shown in Fig. 26. In the device fabrication process, the bottom dielectric layer, aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) is deposited onto the substrate using atomic layer deposition (ALD). Mechanical exfoliation was used to create a 2D - In<sub>2</sub>Se<sub>3</sub> channel layer and bottom hexagonal boron nitride (h-BN). The elimination of the PVA sacrificial layer employed wet methods, while the design of the electrode was accomplished through the utilization of electron beam lithography. Al<sub>2</sub>O<sub>3</sub> layers, produced by ALD, dopes the In<sub>2</sub>Se<sub>3</sub> channel. Therefore, the bottom h-BN layer's existence is essential for optimizing the interface. In addition, the h-BN layer serves as a passivation layer for the In<sub>2</sub>Se<sub>3</sub> channel in addition to being a dielectric, thereby isolating it from the ambient environment. When a voltage is applied to the gate electrode, the polarization of the ferroelectric material changes, resulting in a change in the threshold voltage of the device. This change in threshold voltage allows for the storage and retrieval of information in FeFETs. The ferroelectric material acts as a non-volatile memory element, enabling the FeFET to retain its state even when power is removed. The device's impressive performance includes a 40 nanosecond write speed, increased endurance made possible by the internal electric field, low energy consumption at 234/40 femto-joules per event for excitation/inhibition, and a high-precision simulation with an accuracy rate of 94.74%.

FIGURE 28. Schematic diagram of FG transistor as two terminal devices.

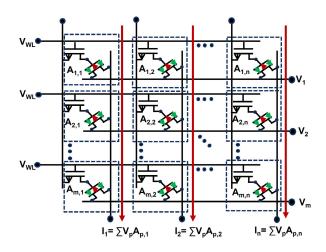

The FeFET synapse can be incorporated within pseudocrossbar arrays, enabling simultaneous row-based adjustments of the weight and column-based computation of the combined FeFET conductances. Fig 27 shows the crossbar array for the ferroelectric material-based transistors. Using high-speed weight update pulses, which are mapped to the conductance states that vary between dynamic changes, The FeFET synapse combines the ability to modulate the ferroelectric polarization with the help of metal oxide semiconductor field effect transistors. The crossbar arrangement of the FeFET synapses allows the weighted summation of individual FeFET conductance values. The conductance states were programmed, and the results from the columns were read using programming voltage pulses and the application of read voltages.