IEEEAccess Multidisciplinary : Rapid Review : Open Access Journal

Received 18 February 2024, accepted 22 March 2024, date of publication 28 March 2024, date of current version 3 April 2024.

Digital Object Identifier 10.1109/ACCESS.2024.3382932

# Vertical Surrounding Gate Transistor for High Density and Low Voltage Operation in DRAM

### WENQI WANG<sup>(D)</sup>, SANG DON YI<sup>1</sup>, FU LI<sup>1</sup>, QINGCHEN CAO<sup>1</sup>, JIANGLIU SHI<sup>1</sup>, BOK-MOON KANG<sup>1</sup>, MEICHEN JIN<sup>1</sup>, CHANG LIU<sup>1</sup>, ZHENHUA WU<sup>(D)</sup>, GUILEI WANG<sup>1</sup>, AND CHAO ZHAO<sup>(D)</sup>

<sup>1</sup>Beijing Superstring Academy of Memory Technology, Beijing 100176, China

<sup>2</sup>Key Laboratory of Microelectronics Devices and Integrated Technology, Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China Corresponding author: Wenqi Wang (wenqi.wang@bjsamt.org.cn)

This work was supported by the National Key Research and Development Program of China under Grant 2022YFB3606900.

**ABSTRACT** In this article, a honeycomb vertical surrounding gate access transistor array scheme is proposed to further decrease the DRAM cell area with aggressively shrink bit line (BL) pitch and word line (WL) pitch adopting the ZigZag BL and WL air gap. To verify the process feasibility, process flow emulation is optimized by virtual fabrication with SEMulator3D<sup>®</sup>. Moreover, the ZigZag BL feasibility in lithography process is evaluated by optical proximity correction (OPC) simulation. In addition, the parasitic capacitance of BL and WL decrease 22.8% and 76.8%, respectively, as compared to reference paper. And the electrical properties of the proposed device are simulated by three-dimensional technology computer aided design (3D TCAD). The GIDL effect is prohibited through prolonging the drain extension and reducing its doping concentration. Finally, the surrounding gate transistor can achieve high on-state current (>30  $\mu$ A) at V<sub>g</sub> = 1.5 V and off-state current below 0.1 fA at V<sub>d</sub> = -0.2 V. These results are beneficial for the direction of pathfinding for increasing the density and decreasing the energy consumption of DRAM.

**INDEX TERMS** Vertical surrounding gate transistor (VSGT), dynamic random-access memory (DRAM), parasitic capacitance, optical proximity correction (OPC), area scaling, power saving.

#### I. INTRODUCTION

The access transistor in dynamic random-access memory (DRAM) cell is the switch between bit-line data path and the capacitor [1]. The basic electrical requirement of the access transistor is high  $I_{on}/I_{off}$  ratio, which lead to long retention time and high write speed [2]. As the cell area shrinks from  $8F^2$  to  $4F^2$ , the access transistor structure of 1T1C DRAM need to overcome short channel effect during the technology scaling down progress. Thus, the access transistor structure and saddle-fin structure to vertical channel structure [2], [3]. The vertical channel transistor (VCT) can release the channel length in the vertical direction [4], which become the most suitable candidate for  $4F^2$  architecture [5].

The associate editor coordinating the review of this manuscript and approving it for publication was Gustavo Callico<sup>10</sup>.

Several researchers have been studied the VCT for DRAM access transistor, among them the vertical surrounding gate transistor offers better gate control, lower current leakage and immunity for Row Hammer effect [6], [7]. The existing VCT array scheme adopt the non-closely aligned square arrangement [8]. This arrangement will face huge challenge in process and device performance when the word-line (WL) pitch and BL pitch keep decreasing. Meanwhile, it is also difficult for orthogonal VCTs to form storage node pads for connecting honeycomb capacitors. Therefore, other access transistor arrangement is desirable for close-packed array. Besides, the power consumption of DRAM is a key point in modern computer system. Reducing the supply voltage become the main solution. For access transistor, the low operating voltage is desirable [9]. To decrease the operation voltage, decreasing the BL contact resistance is essential. However, the buried BL with low contact resistance is

### **IEEE**Access

(b)

difficult to form through implanting and etching process. For non-vertical surrounding gate transistor, researcher optimized the epitaxial source/drain growth process to reduce the contact resistance [10], [11]. Nevertheless, epitaxial BL has higher resistance than metal BL. Innovative method to form low resistance BL is necessary for low operation voltage of DRAM.

Herein, a novel vertical surrounding gate transistor arranged in honeycomb array for further scaling down  $4F^2$ DRAM architecture is proposed. First, the integration process is explored and the process scheme is optimized, including the ZigZag BL and WL air gap. Among them, the horizontal and vertical pitch of ZigZag BL are investigated by optical proximity correction (OPC). Afterwards, the capacitance of WL and BL are extracted. Then the device optimization and simulation are conducted, which indicate the novel vertical surrounding gate transistor can operate at low voltage.

#### **II. PROCESS INTEGRATION**

To further reduce the cell area, a novel vertical surrounding gate array transistor process integration scheme was proposed. The process flow emulation was built by SEMulator3D<sup>(R)</sup> virtual fabrication platform.

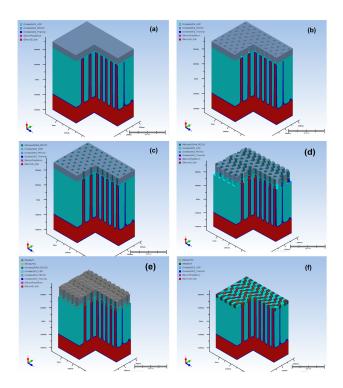

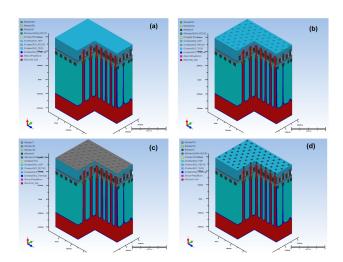

As shown in Figure 1, the honeycombs Si drain pillar were recess etched by 300 nm to corelate the isolation process in core and peripheral regions. The oblique and orthogonal self-aligned double patterning (SADP) was used to generate patterns of the polysilicon. Then using polysilicon as hard mask to etch SiO<sub>2</sub>. Afterwards, SiO<sub>2</sub> acted as a shelter from Si multi-etch. Removing the SiO<sub>2</sub> and depositing the polysilicon before thermal oxidation to cure the etch damage.

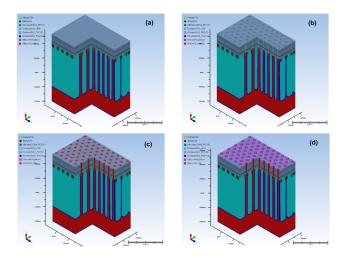

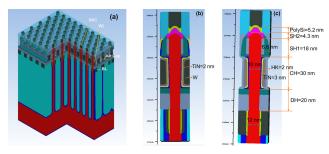

Figure 2 shows the scheme of BL formation process. The high dose arsenic was implanted to Si pillar for ohmic contact. Then depositing oxide and etching hole to fill  $Si_3N_4$  as the hard mask. Following which, the SAQP process was adopted to form ZigZag trench. Finally,  $TiSi_x$  salicidation and W CMP process were carried out.

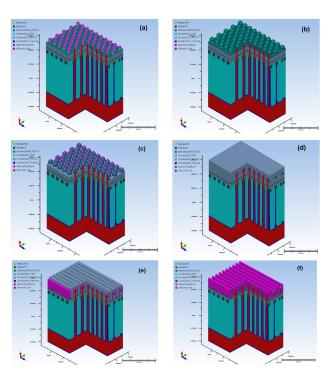

To control the gate length precisely, the gate length was defined using oxide deposition thickness, instead of the lithography or etch [12]. The detailed flow was depicted in Figure 3, where sandwich structure (oxide/ nitride/ oxide/ nitride/ oxide) with aligned etched holes provides the low-temperature epitaxy location. The selective epitaxial growth should be proceeded under 600°C to protect BL salicidation [13]. Next, in-situ doping is performed while growing the polysilicon at temperature below 450°C. At such low temperature, the arsenic doping concentration could reach  $1 \times 10^{21}$  cm<sup>-3</sup>.

Using polysilicon as hard mask of oxide, the upper oxide layer was etched back. Then,  $Si_3N_4$  was deposited on the pillar. Afterwards,  $Si_3N_4$  was etched back straightly to expose the middle oxide layer. Deposit oxide and CMP to acquire smooth surface. Define the WL gap by lithography and etch. Following that, the polysilicon was deposited as sacrifice layer. And the oxide was removed by wet etch. All the above process are shown in Figure 4. Then, the high-k metal gate

(a)

**FIGURE 1.** The drain pillar formation process scheme. (a) The 1st SADP process. (b) The 2st SADP process. (c) The horizontal polysilicon hard mask patten. (d) The polysilicon pillar hard mask patten. (e) Si pillar after multi-etch. (f) Oxidation and isolation.

layers were deposited by ALD. Fill in the W and etch back to form the WL. Deposit the oxide and expose the silicon surface. After removing the polysilicon and exposed high-k material, fill in the  $Si_3N_4$  and etch back. Finally deposit the oxide and remove  $Si_3N_4$  by wet etch. The air-gap WL was formed as Figure 5 depicts.

As Figure 6 shown, the oxide and high-k material were etched back to expose the highly-doped polysilicon layer, and then oxide was deposited and SNC contact holes were generalized. Eventually,  $TiSi_x$  silicide and W contact were formed. Figure 7(a) shows the final SGT array structure. Figure 7(b) (c) display the cross-sections of the device.

The BL capacitance (CAP) is an important factor for the sensing margin of BL sense amplifier (SA). And the WL capacitance is related to the access transistor loading. The air gap was adopted to reduce WL coupling issue and alleviate the signal delay. And the firstly formed BL and finally formed Si transistor will decrease BL2SUB CAP. The BL and WL CAP were extracted and listed in TABLE 1.

#### **III. ZigZag BL OPC EVALUATION**

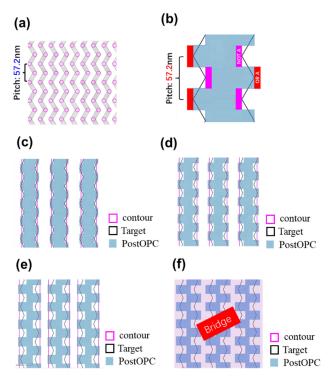

The ZigZag BL can be fabricated by SAQP process [15]. The width and pitch of BL mandrel are preset at 65 nm and 132 nm, respectively. The vertical pitch of BL mandrel is predetermined as 57.2 nm, as Figure 8 shows. Using the Inverse Lithography Technology (ILT), no matter how the mask shape changes in horizontal post OPC, the contour is straight. It is speculated that the pitch between the two

**FIGURE 2.** The ZigZag BL formation process scheme. (a) Implantation and oxide deposition. (b) Hole open align to the Si pillar. (c) SiN<sub>x</sub> filling as hard mask. (d) ZigZag trench formation by SAQP. (e) TiSi<sub>x</sub> salidation. (f) Ti removal and CMP to expose the Si surface.

FIGURE 3. The channel formation process scheme. (a) The oxide/nitride/oxide/nitride/oxide structure deposition. (b) The aligned hole open. (c) Low temperature selective Si epitaxial growth. (d) Highly doped polysilicon epitaxial growth.

inflection points (57.2 nm) is too small and exceeded the resolution limit.

To achieve the ZigZag BL, the BL vertical pitch is doubled. The virtual lithography simulation scene is set as immersion scanner. The light source wavelength is 193 nm, and the numerical aperture (NA) is 1.35. Figure 9 (b) is the optimized light source. We simulated the BL mandrel width at 45 nm and 65 nm, the results are shown in Figure 9 (c) and (d), respectively. When the exposure latitude (EL) set at 5% and

**FIGURE 4.** The WL formation process scheme. (a) Straight etch the oxide layer. (b) SiN<sub>x</sub> deposition. (c) Anisotropic etching the SiN<sub>x</sub>. (d) Depositing the oxide and CMP. (e) WL definition. (f) oxide removal.

**FIGURE 5.** The WL air gap formation process scheme. (a) High k metal gate formation. (b) Filling oxide and CMP to expose polysilicon. (c) Polysilicon removal. (d) SiN<sub>x</sub> deposition and etch back. (e) Oxide deposition and CMP. (f) SiN<sub>x</sub> removal.

the critical dimension at +/-5%, the depth of focus (DOF) of Figure 9 (c) and (d) are 80 nm and 196 nm, respectively.

**FIGURE 6.** The storge node contact formation. (a) Oxide deposition and CMP. (b) Contact hole open. (c)  $TiSi_x$  salidation. (d) W deposition.

**FIGURE 7.** (a) The final SGT array structure. (b) The cross-section view along the WL. (c) The cross-section views perpendicular the WL.

| Design<br>Items | Units   | SGT<br>[This paper]  | VCT<br>[14] |

|-----------------|---------|----------------------|-------------|

| CBL2Sub         | aF/cell | 0.4                  | 1.5         |

| CBL2BL          | aF/cell | 7.53                 | 8.8         |

| CBL2WL          | aF/cell | 1.95                 | 2.5         |

| CBL2SN          | aF/cell | $1.5 \times 10^{-6}$ | NA          |

| CWL2WL          | aF/cell | 2.20                 | 20.3        |

| CWL2BL          | aF/cell | 1.95                 | 3.6         |

| CWL2SN          | aF/cell | 1.84                 | 1.9         |

| RBL             | Ω/cell  | 8.6                  | NA          |

| RWL             | Ω/cell  | 47                   | NA          |

TABLE 1. The extracted WL and BL capacitance.

The process window OPC is accessible in lithography process [16].

As descripted in Figure 2(d), the Zigzag pattern could be realized by SAQP process. The first mandrel width is defined

FIGURE 8. The wave distance split in horizontal. (a) the original ZigZag BL scheme. (b) The OPC cell patten (c) The additional horizontal protrusion (A) assumed 0 nm. (d) The A assumed 5 nm. (e) The A assumed 10 nm. (f) The A assumed 15 nm.

FIGURE 9. (a) The optimized ZigZag BL with double vertical pitch. (b) The source illuminator profile (TE mode). (c) The mandrel width is 45 nm. (d) The mandrel width is 65 nm.

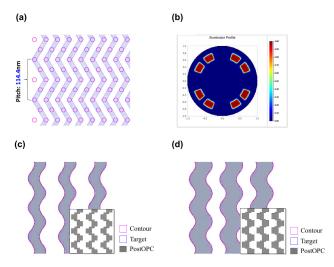

as 45 nm, and its vertical pitch is defined as 114.4 nm. The first mandrel was generated by etch process, and then mandrel 2 was deposited on the surface of mandrel 1. The straight etch was implemented on the mandrel 2, which generate the first sidewalls. The mandrel 1 was removed and the lateral mandrel 2 pitch was reduced by half. The second sidewalls were created by deposition and etching. Then the second sidewall act as hard mask and the Si pillar side region were exposed to generate BL contact.

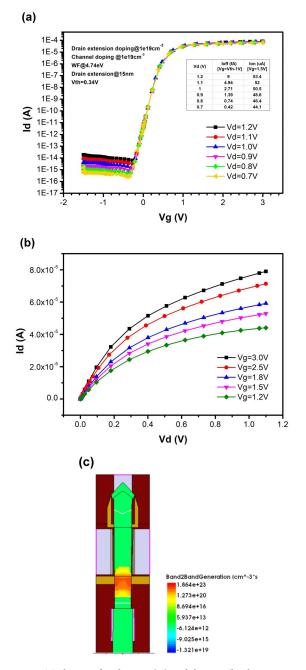

FIGURE 10. (a) The transfer characteristics of the SGT. (b) The output characteristics of the SGT. (c) Band2band generation rate of the SGT.

#### **IV. DEVICE EVALUATION AND OPTIMIZATION**

Since the formation scheme of SGT transistor enables higher doping concentration implantation in BL and feasible in process, this would drop the BL resistance dramatically, leading the low voltage with appropriate operation current. And then, the transistor can operate at low voltage with appropriate operation current. The junctionless SGT transistor gained constant doping at  $1 \times 10^{19}$  cm<sup>-3</sup> by in-situ doping during epitaxy process and the gate metal WF at 4.74 eV. The bandgap narrowing and Fermi-Dirac model are activated for heavy doped regions in TCAD simulation. And the Philips Unified

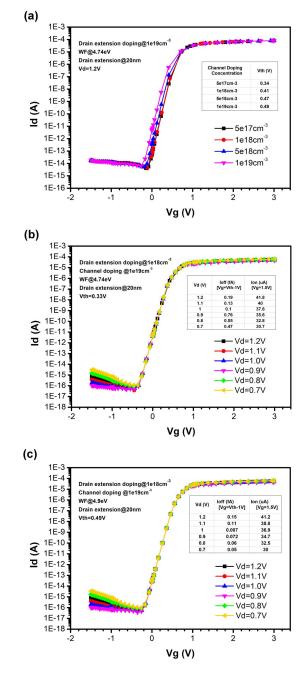

FIGURE 11. (a) The transfer characteristic with different channel doping. (b) The transfer characteristic with WF at 4.74eV. (c) The transfer characteristic with WF at 4.9 eV.

and Lombardi are also included in the mobility model. The Auger, Shockley-Read-Hall and nonlocal band-to-band tunneling are invoked in recombination model.

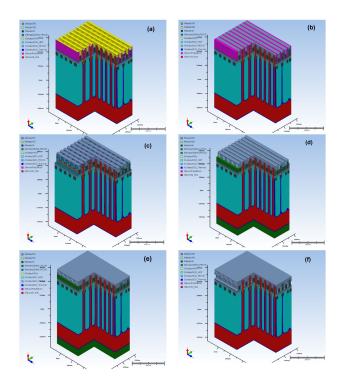

The SGT's transfer characteristic and output characteristic are shown in Figure 10. The  $I_{on}$  at 1.5 V in gate voltage is 10 times larger than other researcher's simulation value [14]. Nevertheless, the off-state current is 27 times larger than that. For the junctionless transistor, the gate induced drain leakage (GIDL) is the main reason for high off-state current, especially the lateral band-to-band tunneling [17], [18], [19].

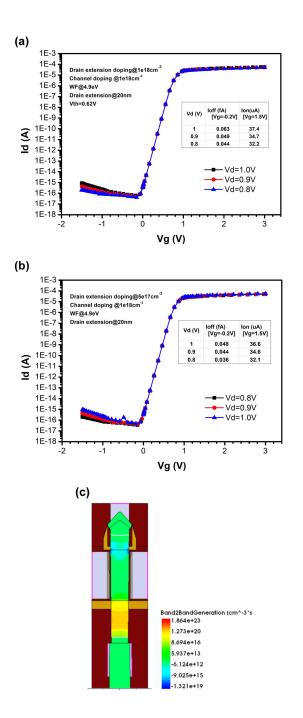

**FIGURE 12.** (a) The transfer characteristic with drain extension doping at  $1 \times 10^{18}$  cm<sup>-3</sup>. (b) The transfer characteristic with drain extension doping at  $5 \times 10^{17}$  cm<sup>-3</sup>. (c) Band2band generation rate of the SGT of (b).

In Figure 10 (a), the BTBT-induced parasitic BJT is trigged in junctionless transistor, which make the off-state current less dependent on the gate voltage [20]. Figure10 (c) shows the band-to-band generation rate is very high in the junction between channel and drain. The narrow depletion region may cause such GIDL effect. Thus, decreasing the doping concentration and prolonging the length of drain extension region will prohibit the band-to-band tunneling. Figure 11 demonstrates the GIDL effect was alleviated and  $I_{off}$  was reduced to below 0.1 fA with relatively high  $I_{on}$ .

The threshold voltage (V<sub>th</sub>) of access transistor in DRAM should be larger than logic devices for lower off-state current. In junctionless transistors, decreasing the channel doping concentration and increasing the gate metal work function (WF) are benefit for channel volume depletion, which lead to the increase in  $V_{th}$  [21]. Figure 11(a) shows the  $V_{th}$  increased from 0.34 V to 0.49 V as the channel doping decreased to  $5 \times 10^{17}$  cm<sup>-3</sup>. Figure 11(b) show the higher WF will increase the  $V_{th}$  from 0.33 V to 0.49 V. Since the  $V_{th}$  is as low as 0.4 V, the gate bias condition of the access transistor is defined as -0.2 V to increase noise immunity. After device optimization, the SGT achieved higher  $I_{on}$  (32.1  $\mu$ A) at 1.5 V gated bias, and lower  $I_{off}$  (0.036 fA) at -0.2 V gate bias, as Figure 12 shows. In practice, the off-state current can be tested by array to avoid the limitations of electrical test equipment. After device tunning, the GIDL effect is alleviated, depicted in Figure 12 (c).

#### **V. CONCLUSION**

A novel SGT array transistor was proposed in honeycomb arrangement, with the benchmark against the  $1\alpha$  DRAM technology node. The process flow emulation shows it can overcome the pitch scaling limits and offer low voltage operation performance at  $4F^2$  cell area. the BL formation and the followed transistor fabrication decrease the BL contact resistance greatly. The electrical results of SGT transistor show excellent SS (73 mV/dec), on-state current (32.1  $\mu$ A), and off-state current (0.036 fA). The ZigZag BL can reduce the cell area without increasing the BL capacitance. Compared with the square arrangement [8], the honeycomb SGT array density has doubled. The WL air gap decrease the WL2WL coupling. The results of this simulation are input into a silicon evaluation to determine the feasibility of developing low-temperature epitaxial equipment and process. All these above merits make such SGT potential for scaling-up and low power consumption.

#### ACKNOWLEDGMENT

The authors thank Yongchun Lu for paper check.

#### REFERENCES

- A. S. Sankpal and D. J. Pete, "Study and analysis of leakage current and leakage power in 1T1C DRAM at nano scale technology," in *Proc. 4th Int. Conf. Electron., Commun. Aerosp. Technol. (ICECA)*, Coimbatore, India, Nov. 2020, pp. 99–104, doi: 10.1109/ICECA49313.2020.92 97568.

- [2] A. Spessot and H. Oh, "1T-1C dynamic random access memory status, challenges, and prospects," *IEEE Trans. Electron Devices*, vol. 67, no. 4, pp. 1382–1393, Apr. 2020, doi: 10.1109/TED.2020.2 963911.

- [3] W.-Q. Wang, "TCAD simulation performance of VGAA for 4F2 high density DRAM cell," in *Proc. IEEE 16th Int. Conf. Solid-State Integr. Circuit Technol. (ICSICT)*, Oct. 2022, pp. 1–3, doi: 10.1109/ICSICT55466.2022.9963197.

- [4] H. Jagannathan, "Vertical-transport nanosheet technology for CMOS scaling beyond lateral-transport devices," in *IEDM Tech. Dig.*, Dec. 2021, pp. 26.1.1–26.1.4, doi: 10.1109/IEDM19574.2021.9720561.

- [5] H. Chung, H. Kim, H. Kim, K. Kim, S. Kim, K.-W. Song, J. Kim, Y. C. Oh, Y. Hwang, H. Hong, G.-Y. Jin, and C. Chung, "Novel 4F2 DRAM cell with vertical pillar transistor(VPT)," in *Proc. Eur. Solid-State Device Res. Conf. (ESSDERC)*, Helsinki, Finland, Sep. 2011, pp. 211–214, doi: 10.1109/ESSDERC.2011.6044197.

- [6] Y. Guerfi and G. Larrieu, "Vertical silicon nanowire field effect transistors with nanoscale gate-all-around," *Nanosc. Res. Lett.*, vol. 11, no. 1, Apr. 2016, Art. no. 210, doi: 10.1186/s11671-016-1396-7.

- [7] J. -W. Han, "Surround gate transistor with epitaxially grown si pillar and simulation study on soft error and row hammer tolerance for DRAM," *IEEE Trans. Electron Devices*, vol. 68, no. 2, pp. 529–534, Feb. 2021, doi: 10.1109/TED.2020.3045966.

- [8] X. Su, Y. Qiu, M. Yu, G. Shao, H. Sun, W. Bai, D. Xiao, K. Cao, and T. Park, "High density V-GAA transistor structure array based on self-aligned double patterning," in *Proc. Int. Workshop Adv. Patterning Solutions (IWAPS)*, Foshan, China, Dec. 2021, pp. 1–3, doi: 10.1109/IWAPS54037.2021.9671059.

- [9] K. K. Chang, A. G. Yağlikçl, S. Ghose, A. Agrawal, N. Chatterjee, A. Kashyap, D. Lee, M. O'Connor, H. Hassan, and O. Mutlu, "Understanding reduced-voltage operation in modern DRAM devices: Experimental characterization, analysis, and mechanisms," *Proc. ACM Meas. Anal. Comput. Syst.*, vol. 1, no. 1, pp. 1–42, Jun. 2017, doi: 10.1145/3084447.

- [10] L. Wu, "The next generation of gate-all-around transistors," *Nature Electron.*, vol. 6, no. 7, p. 469, Jul. 2023, doi: 10.1038/s41928-023-01006-x.

- [11] J. Jeong, S. H. Lee, S.-A. Masuoka, S. Min, S. Lee, S. Kim, T. Myung, B. Choi, C.-W. Sohn, S. W. Kim, J. Choi, J. Park, H. Lee, T. Kim, S. Kim, Y. Yasuda-Masuoka, J.-H. Ku, and G. Jeong, "World's first GAA 3nm foundry platform technology (SF3) with novel multi-bridgechannel-FET (MBCFET) process," in *Proc. IEEE Symp. VLSI Technol. Circuits (VLSI Technol. Circuits)*, Kyoto, Japan, Jun. 2023, pp. 1–2, doi: 10.23919/vlsitechnologyandcir57934.2023.10185353.

- [12] S.-H. Oh, J. M. Hergenrother, D. Monroe, T. Nigam, F. P. Klemens, A. Kornblit, W. M. Mansfield, F. H. Baumann, H. J. Gossmann, C. A. King, R. N. Kleiman, H.-H. Vuong, G. R. Weber, and C. S. Rafferty, "The application of solid source diffusion in the vertical replacement-gate (VRG) MOSFET," *MRS Proc.*, vol. 610, p. B3, Jan. 2000, doi: 10.1557/proc-610b3.2.

- [13] A. Vandooren, "First demonstration of 3D stacked finfets at a 45nm fin pitch and 110nm gate pitch technology on 300 mm wafers," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2018, pp. 7.1.1–7.1.4, doi: 10.1109/IEDM.2018.8614654.

- [14] D. Feng, "Vertical channel transistor (VCT) as access transistor for future 4F2 DRAM architecture," in *Proc. IEEE Int. Memory Workshop (IMW)*, May 2023, pp. 1–4, doi: 10.1109/IMW56887.2023.10145977.

- [15] C. Auth, "A 10nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2017, p. 29, doi: 10.1109/IEDM.2017.8268472.

- [16] J. Mailfert, J. Van de Kerkhove, P. De Bisschop, and K. De Meyer, "Metal1 patterning study for random-logic applications with 193i, using calibrated OPC for litho and etch," *Proc. SPIE*, vol. 9052, Mar. 2014, Art. no. 90520Q, doi: 10.1117/12.2046782.

- [17] S. Sahay and M. J. Kumar, "Insight into lateral band-to-band-tunneling in nanowire junctionless FETs," *IEEE Trans. Electron Devices*, vol. 63, no. 10, pp. 4138–4142, Oct. 2016, doi: 10.1109/TED.2016.2601239.

- [18] J. Hur, B.-H. Lee, M.-H. Kang, D.-C. Ahn, T. Bang, S.-B. Jeon, and Y.-K. Choi, "Comprehensive analysis of gate-induced drain leakage in vertically stacked nanowire FETs: Inversion-mode versus junctionless mode," *IEEE Electron Device Lett.*, vol. 37, no. 5, pp. 541–544, May 2016, doi: 10.1109/LED.2016.2540645.

- [19] J. Fan, M. Li, X. Xu, Y. Yang, H. Xuan, and R. Huang, "Insight into gate-induced drain leakage in silicon nanowire transistors," *IEEE Trans. Electron Devices*, vol. 62, no. 1, pp. 213–219, Jan. 2015, doi: 10.1109/TED.2014.2371916.

- [20] S. Gundapaneni, M. Bajaj, R. K. Pandey, K. V. R. M. Murali, S. Ganguly, and A. Kottantharayil, "Effect of band-to-band tunneling on junctionless transistors," *IEEE Trans. Electron Devices*, vol. 59, no. 4, pp. 1023–1029, Apr. 2012, doi: 10.1109/TED.2012.2185800.

- [21] A. Nowbahari, A. Roy, and L. Marchetti, "Junctionless transistors: State-of-the-art," *Electronics*, vol. 9, no. 7, p. 1174, Jul. 2020, doi: 10.3390/electronics9071174.

**WENQI WANG** received the master's degree from Harbin Institute of Technology and the Ph.D. degree from the Institute of Physics, Chinese Academy of Sciences. She has been working in the field of devices in the semiconductor industry for about six years. She is currently a Senior Engineer with Beijing Superstring Academy of Memory Technology.

**SANG DON YI** received the B.E. and M.E. degrees in electronic material engineering from KwangWoon University, Seoul, South Korea, in 1993 and 1995, respectively. From 1995 to 2015, he was working on Technology Development at SAMSUNG Electronics, South Korea. From 2015 to 2018, he was working on Design Process Integration Analysis for yield enhancement at GlobalFoundries, Singapore. From 2018 to 2022, he was working on 20nm DRAM Technology

Development and Technology Enablement at Jin Semiconductor, China. He is currently an Expert with the Beijing Superstring Academy of Memory Technology. His research interests include novel devices for DRAM and implementation methodology of DRAM design.

**FU LI** received the master's degree from Fuzhou University. He currently holds the position of a Senior Engineer with Beijing Superstring Academy of Memory Technology. He has accumulated six years of experience in lithography.

**QINGCHEN CAO** received the master's degree from Shanghai Institute of Applied Physics, Chinese Academy of Sciences, and the Ph.D. degree in microelectronics from Chinese Academy of Sciences. He has been working in the field of computational lithography in the semiconductor industry for about 15 years. He is currently the Senior Manager of Beijing Superstring Academy of Memory Technology.

**JIANGLIU SHI** is with the Beijing Superstring of Memory Technology, responsible for advanced lithography technology research and development. She has more than 20 years of international experience in semiconductor equipment, process development, and management, with a special focus on photolithography and related technologies.

## IEEE Access

**BOK-MOON KANG** was with Samsung and Hynix. He is currently the Vice President of strategy of Beijing Superstring Academy of Memory Technology. He has 30 years of DRAM design experience. At present, his main research interests include DRAM chip design and ferroelectric memory.

**ZHENHUA WU** received the Ph.D. degree in condensed matter physics from the Institute of Semiconductors, Chinese Academy of Sciences, Beijing, China, in 2011. He joined the Semiconductor Research and Development Center, Samsung Electronics, Suwon-si, South Korea, in 2011. In 2016, he became a Full Professor with Chinese Academy of Sciences. His current research interests include device physics and simulation of nanoscale transistors.

**MEICHEN JIN** received the master's degree in photonics from Ghent University, Ghent, Belgium, in 2016. She was with the Institute of Microelectronics, Chinese Academy of Sciences, Beijing, China, from 2020 to 2022. She has been with Beijing Superstring Academy of Memory Technology, Beijing, since 2022. Her current research interests include novel DRAM, 3D DRAM, and amorphous oxide semiconductors.

**GUILEI WANG** received the Bachelor's and Ph.D. degrees from the University of Chinese Academy of Sciences in 2005 and 2016, respectively. He has been worked as a Professor at the Integrated Circuit Advanced Process Center, Chinese Academy of Sciences until 2021. In October 2021, he joined the Beijing Superstring Academy of Memory Technology as a Full Professor. His research interests are focused on new materials, devices, and process integration for the IC industry.

**CHANG LIU** received the master's degree in electronics and communication engineering from Beijing University of Posts and Telecommunications, Beijing, China, in 2022. Her main research interests include semiconductor devices and reliability testing.

**CHAO ZHAO** received the B.S. degree in physics form Nanjing University in 1982, the M.S. degree in semiconductor from Harbin Industrial University in 1988, and the Ph.D. from the Katholieke Universiteit Leuven of Belgium in 1999. From 2000 to 2010, he was working in IMEC as a Senior Scientist. From 2010 to 2021, he was working as a Full Professor at the University of CAS and IME-CAS. Since 2021, he has been working with the Beijing Superstring Academy of Memory Tech-

nology as the Senior VP. He has authored and coauthored more than 374 scientific papers, two books and four book chapters. His research fields are CMOS and memory processing technology.

...