Received 11 March 2024, accepted 20 March 2024, date of publication 25 March 2024, date of current version 29 March 2024. Digital Object Identifier 10.1109/ACCESS.2024.3381493

## **SURVEY**

# Modern Trends in Improving the Technical Characteristics of Devices and Systems for Digital Image Processing

# NIKOLAY N. NAGORNOV<sup>®1</sup>, PAVEL A. LYAKHOV<sup>®1,2</sup>, MAXIM V. BERGERMAN<sup>2</sup>, AND DIANA I. KALITA<sup>1</sup>

<sup>1</sup>Department of Mathematical Modeling, North-Caucasus Federal University, 355017 Stavropol, Russia

<sup>2</sup>North-Caucasus Center for Mathematical Research, North-Caucasus Federal University, 355017 Stavropol, Russia

Corresponding author: Nikolay N. Nagornov (nnagornov@ncfu.ru)

This work was supported in part by Russian Science Foundation under Project 22-71-00009 (section III and section IV) and Project 23-71-10013 (section V and section VI), and in part by the North-Caucasus Center for Mathematical Research under Agreement with the Ministry of Science and Higher Education of the Russian Federation under Agreement 075-02-2023-938 (section VII).

**ABSTRACT** The technology development greatly increases the amount of digital visual information. Existing devices cannot efficiently process such huge amounts of data. The technical characteristics of digital image processing (DIP) devices and systems are being actively improved to resolve this contradiction in science and technology. The state-of-the-art methodology includes a huge number of very diverse approaches at the mathematical, software, and hardware implementation levels. We have analyzed all modern trends to improve the technical characteristics of DIP devices and systems. The main distinguishing feature of this review is that we are not limited to considering various aspects of neural network image processing, to which the vast majority of both review and research papers on the designated topic are devoted. Review papers on the subject under consideration are analyzed. Various mathematical and arithmetic-logical methods for improving the characteristics of image processing devices are described in detail. Original and significant architectural and structural solutions are analyzed. Promising neural network models of visual data processing are characterized. Hardware platforms for the design and operation of DIP systems that are efficient in terms of resource costs are considered. The most significant improvements achieved through the hardware implementation of models and methods on field-programmable gate arrays and application-specific integrated circuits are noted.

**INDEX TERMS** High-performance computing, low-area design, low-power device, energy-efficient architecture, neural network, hardware accelerator, FPGA, ASIC.

#### I. INTRODUCTION

The technology development is accompanied by a huge increase in the amount of digital visual information [1], [2]. Nowadays, almost every modern member of society has a smartphone from an early age, on which he quickly learns and gets used to taking photos and videos. Many have one or more desktop or laptop computers and other digital devices with even more tools for creating and distributing visual content. In addition to everyday life, digital imaging and image

The associate editor coordinating the review of this manuscript and approving it for publication was Vitor Monteiro<sup>10</sup>.

processing devices have been introduced into various industries, medical diagnostics, satellite systems, are actively used by law enforcement agencies, and so on [3], [4]. The characteristics of digital images are constantly improving including spatial resolution and color depth. Their number is increasing at the same time. This significantly increases the amount of visual information that needs to be registered, processed, stored, and transmitted [2], [5]. But existing and developed devices cannot efficiently process such huge amounts of data, since the rate of their characteristics improvement is inferior to the rate of increasing the amount of information [1], [6]. The technical characteristics of digital image processing (DIP) devices and systems are being actively improved to resolve this contradiction in science and technology [6], [7].

Scientists and engineers around the world develop and implement various mathematical models, computational methods, algorithms, and programs, design experimental architectures and microelectronic devices to improve the DIP system characteristics [8], [9]. Modern methodology includes a huge number of very diverse approaches at the mathematical, software, and hardware implementation levels. Many ideas such as parallel computing have become so widespread that they have been a generally accepted tool used "by default". However, not all approaches are so successful and developed. The main motivation of this review is to cover the variety of approaches to improving the technical characteristics of DIP devices and systems and analyze the most successful or promising of them.

The main purpose of this review is to draw the attention of specialists in the field under consideration to the most modern and widely used approaches with significant undiscovered or unrealized potential which can further improve the technical characteristics of DIP devices and systems. Relevant and significant scientific review and research papers were analyzed. We have identified the most promising mathematical approaches and concepts, architectural and structural solutions, as well as their hardware simulations and implementations. These solutions are systematized and classified. Their common features are highlighted. We draw conclusions about the current state of the ideas development presented and give appropriate recommendations. A separate section is devoted to the analysis of related review papers.

The main distinguishing feature of this review is that we are not limited to considering various aspects of neural network image processing, to which the vast majority of both review and research papers on the designated topic are devoted. This review is structured according to the papers content. The order of materials presentation is defined and presented in the next section.

#### **II. REVIEW METHODOLOGY**

Scientific materials are collected and analyzed in three main stages. Firstly, a search was made for journal research and review papers. A database with significant scientific sources has been compiled. Secondly, a selection of works was carried out. Insignificant works were weeded out. Thirdly, the approaches classification according to the collected research data is carried out.

#### A. SEARCH STRATEGY

The collection of relevant review sources with significant scientific results was the search purpose. We searched for papers published from 2018 to early 2023 in the journals of leading scientific publishers on the research topic. Publishers data and links to them are presented in Table 1. The arXiv database was not considered as a source of significant scientific information since the works published in it are not peer-reviewed. Research topics acted as the main

search guide. We were interested in various DIP problems that require huge computing resources for their solution, as well as a variety of mathematical and technical methods and tools that are actively used to reduce resource costs and improve the technical characteristics of image processing devices and systems. We focused on the image processing itself and not on the processes of their registration, coding, encryption, and transmission over communication channels. Also, this review does not cover the physical principles and technologies underlying the construction of integrated circuit chips such as complementary metal-oxide-semiconductor transistors and their analogues. Various subtleties of the image processing methods implementation, such as the efficiency of computation routing in modern microelectronic devices, are not considered. We did not pay attention to problems with low computational complexity.

#### TABLE 1. Scientific publishers used to collect research and review papers.

| Publisher | URL                                         |

|-----------|---------------------------------------------|

| IEEE      | https://ieeexplore.ieee.org/Xplore/home.jsp |

| Elsevier  | https://www.sciencedirect.com/              |

| Springer  | https://link.springer.com/                  |

| MDPI      | https://www.mdpi.com/search                 |

| ACM       | https://dl.acm.org/                         |

| Wiley     | https://onlinelibrary.wiley.com/            |

Many different keywords are used to search for papers. All possible combinations of two groups of words and phrases have been compiled. The first group includes ways to improve various technical characteristics of image processing devices: "fast"; "speed"; "high-speed"; "highperformance"; "low latency"; "real-time"; "accelerator"; "low-cost"; "efficient"; "area-efficient"; "low-power"; "power-efficient"; "energy-efficient"; "low-complexity"; "FPGA"; "multiply-accumulate". The second group includes the names of tasks or tools most often used to solve them: "image processing"; "image filter"; "image neural network"; "image CNN". Many other words and phrases are also used. However, the search for them did not yield meaningful results. The works found by the given keywords were sorted by relevance in each information resource from Table 1. The titles of the first hundred papers were analyzed. Works whose titles corresponded to the research topic were selected for further analysis.

Most of the papers were low-grade works without significant scientific results. The analysis and primary paper selection according to their abstracts was carried out already at the search stage in order to collect high-quality sources with reliable information. Works focusing on software implementation of the proposed solutions were screened out, as well as work with image processing on central processing unit (CPU), graphics processing unit (GPU), and random access memory (RAM). The significance of all state-of-the-art solutions is only proven by hardware implementation or simulation on specialized platforms such as field-programmable gate arrays (FPGAs) and application-specific integrated circuits (ASICs). Mathematical papers without original and significant solutions and methods were sifted out. Works containing modifications of known approaches for solving problems with low computational complexity, such as pattern recognition using only simple databases (MNIST, Fashion-MNIST, SVHN) and binary image processing, were also ignored. An exception in this case are papers devoted to promising neural network models such as spiking neural network (SNN).

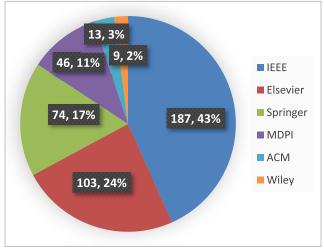

The compiled database of found sources includes 432 research and review papers with significant scientific results on the review subject. The distribution of these works by publishers is shown in Fig. 1.

**FIGURE 1.** Distribution of collected papers by publishers (number of papers; share of the total sources number, %).

#### B. QUALITY ASSESSMENT

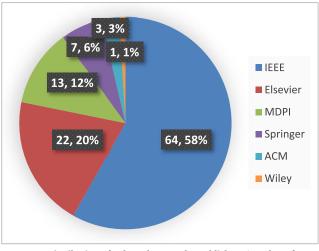

The selection of research papers was carried out according to the criteria from previous subsection. However, this time they were applied to the papers themselves and not just their titles and abstracts. The selection of review papers at this stage was carried out only in accordance with the topic under consideration without regard to the work quality. In general, most of the sources were excluded due to low scientific significance. More than 95% of the selected papers were published in journals from Q1 and Q2 according to JCR 2021 or SJR 2021. Other research and review papers did not contain original and significant solutions the loss of which would affect the methodology breadth under consideration. Thus, they were excluded from our database. A total of 94 papers remained after selection. However, additional sources were found in the analysis of selected works. Those that met all the search criteria were also added to database. Final database consists of the most significant sources and includes 110 papers: 81 research and 29 review. Their distribution by publishers is shown in Fig. 2. We can conclude that IEEE is the leading publisher on the subject under consideration and has published more than half of the found and selected papers. IEEE and Elsevier

**FIGURE 2.** Distribution of selected papers by publishers (number of papers; share of the total sources number, %).

TABLE 2. Journals with the largest number of relevant and significant papers on the topic under consideration.

| Journal                                                                          | Publisher | Number<br>of Papers |

|----------------------------------------------------------------------------------|-----------|---------------------|

| IEEE Access                                                                      | IEEE      | 16                  |

| IEEE Transactions on Circuits and<br>Systems I: Regular Papers                   | IEEE      | 9                   |

| IEEE Transactions on Circuits and<br>Systems II: Express Briefs                  | IEEE      | 9                   |

| IEEE Transactions on Very Large Scale<br>Integration (VLSI) Systems              | IEEE      | 8                   |

| IEEE Transactions on Computer-Aided<br>Design of Integrated Circuits and Systems | IEEE      | 6                   |

| IEEE Transactions on Neural Networks<br>and Learning Systems                     | IEEE      | 6                   |

| Journal of Systems Architecture                                                  | Elsevier  | 6                   |

| Microprocessors and Microsystems                                                 | Elsevier  | 5                   |

contain a total of more than 75%. We also identified the most promising journals with a high concentration of high-quality works (Table 2) containing 5 or more selected sources. We recommend papers from the presented journals, first of all, when collecting sources and analyzing current methods to teams whose research topics are closely related to this review.

The following conclusions are made based on the analysis results with all the papers found and can be used as criteria for work quality assessing when selecting sources for scientific research.

1. Most researchers are guided by the results obtained in the software implementation of their developments. They use Matlab instead of modern specialized computer-aided design systems. This fact frankly testifies to the low level of their scientific competence, the low quality of results obtained verification, and the low significance of the proposed solutions. Works with the software implementation results are published mainly in Q3 and Q4 journals of international scientometric databases. Xilinx, Altera, Synopsys, Cadence, as well as open source software tools such as Yosys are strongly recommended as platforms for such research teams to implement their methods and solutions. 2. A huge number of works contain a comparison of the proposed solutions on FPGA with the implementation results on CPU and GPU while declaring an improvement in device characteristics by tens and hundreds of times. This comparison is absolutely incorrect since FPGA implements the DIP methods and algorithms much more efficiently than CPU and GPU. The presence of such a comparison also indicates the material low quality. Unfortunately, even journals with a high impact factor often contain works with such a comparison.

3. Many researchers compare their developments on FPGAs with approaches implemented on other board families and generations. Often using different conditions and implementation or simulation parameters. Such comparisons are not correct to the proper extent and have low significance. All of the above largely affects the results interpretation and distorts the real significance and scientific value of the proposed solutions.

4. Very often, researchers choose simple image databases such as MNIST, Fashion-MNIST, SVHN as a target source of initial data for the development and implementation of neural network approaches, as well as experimental comparison with state-of-the-art methods. Sometimes binary images are also considered as input data. These problems have low computational complexity and are not a significant test of the proposed solutions. You should not pay attention to works without the results of image processing from other image databases.

5. A significant number of papers on intelligent image processing methods are the same type of work with minimal differences and offer nothing original. Someone uses well-known developments to solve a highly specialized problem that does not require a significant change in approach. Someone focuses on some minor subtleties of the hardware implementation on FPGA. One way or another, a significant number of works parasitize on known methods without offering anything new and significant.

6. Many papers including those from journals with a high impact factor contain: systematic violation of the paper structure and the information presentation logic; insufficiently complete description of the simulation conditions which does not allow the experiments to be reproduced by outside research teams; focusing on the results obtained which testify in favor of the proposed solutions, in conjunction with partial or complete disregard for "uncomfortable" results that can negatively affect the assessment of the developments described. The authors do not always consistently and clearly explain and substantiate in the annotation and introduction: the problem relevance; the proposed approaches and solutions essence; the developed methods purpose; reason of device characteristics improving. For example, it is quite difficult to understand the researchers' ideas by the paper title "FPGA implementation of hybrid recursive reversable box filter-based fast adaptive bilateral filter for image denoising," in which one of the many adjectives also contains a spelling error (correctly "reversible"). The abstract does not clarify the situation much, while this paper was published in the journal from Q2 according to JCR 2021 and SJR 2021. Often, the authors write in the abstract that they achieve an improvement in various indicators but do not indicate how and due to what. Thus, the ideas underlying the developed approaches and the scientific contribution remain unclear. Authors often describe specific numerical results obtained or experimental conditions in introduction instead of a brief summary of the proposed solutions, the ideas underlying them, and distinctive features. Some authors pass off the proposed approach implementation as the scientific contribution, while it is nothing more than a tool for testing the adequacy and significance of this approach. Known methods and original scientific materials are not always clearly separated and do not allow to evaluate the authors contribution. An incredible variety of such errors exists which indicates the low qualification and competence of many actively published scientific research teams.

#### C. SYNTHESIS OF CONSIDERED APPROACHES

The most common and significant approaches to improving the technical characteristics of DIP devices are structured based on the analysis results of selected papers. All solutions are conditionally separated into: mathematical and arithmetic-logical; architectural-structural; perspective; hardware. All found review papers on a given topic in the amount of 29 sources are considered before analyzing the selected approaches. Fig. 3 shows the further presentation order of the review materials. Section III analyzes related review papers. Section IV contains popular mathematical ideas and particular approaches based on them. Section V consists of the original architectural and structural solutions description. Section VI describes the neural network models that are being actively developed, which can become a powerful tool for solving various DIP problems. Section VII provides information on the improvements of image processing devices for all significant FPGA and ASIC hardware implementations made in the analyzed research papers. The main conclusions are formulated in section VIII. Review summary is presented in section IX.

| III. Overview of Review Papers                        |

|-------------------------------------------------------|

| IV. Mathematical and Arithmetic-Logical Methods       |

| A. Approximate Computing                              |

| B. Processing Elements Modification                   |

| C. Convolution Optimization Using the Winograd Method |

| D. Computations in the Residue Number System          |

| V. Various Architectural and Structural Solutions     |

| VI. Promising Neural Network Models                   |

| A. Spiking Neural Network                             |

| B. Binary Neural Network                              |

| VII. Hardware Implementation on FPGA and ASIC         |

| VIII. Discussion                                      |

| IX. Summary                                           |

FIGURE 3. The further presentation order of the review materials.

#### **III. OVERVIEW OF REVIEW PAPERS**

Many review papers in addition to research papers were found. This section analyzes reviews on the designated scientific problem. The materials are structured as follows: a

|              | State-of-the-Art Approaches to Improving the Technical Characteristics of Image Processing Systems |                                     |                                                          |                                                 |                                                      |                           |                          |                                       |                                       |       |

|--------------|----------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------|-------------------------------------------------|------------------------------------------------------|---------------------------|--------------------------|---------------------------------------|---------------------------------------|-------|

| Review Paper | Approximate<br>Computing                                                                           | Processing Elements<br>Modification | Convolution<br>Optimization Using<br>the Winograd Method | Computations in the<br>Residue Number<br>System | Various Architectural<br>and Structural<br>Solutions | Spiking Neural<br>Network | Binary Neural<br>Network | Hardware<br>Implementation on<br>FPGA | Hardware<br>Implementation on<br>ASIC | Other |

| [1]<br>[2]   |                                                                                                    | ×                                   |                                                          | ×                                               | ×                                                    |                           |                          | ×                                     |                                       |       |

| [3]          |                                                                                                    | ×                                   |                                                          |                                                 | ×                                                    |                           |                          |                                       |                                       |       |

| [4]          |                                                                                                    |                                     |                                                          |                                                 |                                                      |                           |                          | ×                                     |                                       |       |

| [5]<br>[6]   |                                                                                                    |                                     | ×                                                        |                                                 |                                                      |                           |                          |                                       | ×                                     |       |

| [7]          |                                                                                                    |                                     |                                                          |                                                 |                                                      |                           |                          |                                       |                                       | ×     |

| [8]<br>[9]   | ×                                                                                                  |                                     |                                                          |                                                 | ×                                                    |                           |                          |                                       |                                       |       |

| [9]<br>[10]  | ×                                                                                                  |                                     | ×                                                        |                                                 | ×                                                    |                           | ×                        | ×                                     |                                       | ×     |

| [10]         |                                                                                                    |                                     |                                                          |                                                 |                                                      |                           |                          |                                       |                                       | ×     |

| [12]         |                                                                                                    |                                     |                                                          |                                                 |                                                      |                           |                          | ×                                     |                                       |       |

| [13]         | ×                                                                                                  | ×                                   |                                                          |                                                 |                                                      |                           |                          |                                       |                                       |       |

| [14]<br>[15] |                                                                                                    |                                     |                                                          |                                                 |                                                      |                           |                          | ×                                     |                                       | ×     |

| [15]         |                                                                                                    | ×                                   |                                                          |                                                 |                                                      |                           |                          |                                       |                                       | ~     |

| [17]         |                                                                                                    |                                     | ×                                                        |                                                 | ×                                                    |                           |                          | ×                                     | ×                                     |       |

| [18]         |                                                                                                    |                                     |                                                          |                                                 |                                                      | ×                         |                          |                                       |                                       |       |

| [19]         | ×                                                                                                  |                                     |                                                          |                                                 | ×                                                    |                           | ×                        | ×<br>×                                | ×                                     |       |

| [20]<br>[21] |                                                                                                    |                                     |                                                          |                                                 |                                                      |                           | ×                        | ~                                     | ~                                     |       |

| [21]         |                                                                                                    |                                     |                                                          |                                                 |                                                      |                           |                          |                                       |                                       | ×     |

| [23]         |                                                                                                    |                                     |                                                          |                                                 |                                                      |                           |                          |                                       |                                       | ×     |

| [24]         |                                                                                                    |                                     |                                                          |                                                 |                                                      |                           |                          |                                       |                                       | ×     |

| [25]<br>[26] | ×                                                                                                  |                                     | ×                                                        |                                                 | ×                                                    |                           |                          | ×<br>×                                |                                       |       |

| [26]         | ×                                                                                                  |                                     | ×                                                        |                                                 | ×                                                    |                           |                          | ×                                     | ×                                     |       |

| [28]         |                                                                                                    |                                     |                                                          |                                                 |                                                      |                           |                          |                                       |                                       | ×     |

| [29]         |                                                                                                    |                                     |                                                          |                                                 |                                                      |                           |                          |                                       |                                       | ×     |

#### TABLE 3. Intersections of significant scientific materials in the found review papers with this review subject.

table with all found review papers; a brief description of each work; conclusions based on the analysis results. The characterization of review materials is subjective and does not claim to be the ultimate truth.

Table 3 is presented below and contains review papers found and highlighted approaches to improve the technical characteristics of DIP devices and systems. If the work contains significant materials on any of the selected approaches, then the cell at their intersection is marked with the sign " $\times$ ". If any review paper does not contain significant materials relevant to our review subject, then the mark is located in the last column.

Paper [1] considers further ways of methodology development for digital devices computations organization based on non-traditional mathematical paradigms: logarithmic number system; residue number system (RNS); stochastic computations; hyperdimensional arithmetic. This review also contains a description of developing technologies to create a material and technical base that can serve as the basis for new generations of digital devices. Work [2] contains a comprehensive analysis of hardware accelerators for the implementation of image processing and computer vision algorithms. A thorough comparison of digital signal processing units (DSP units), GPU, and FPGA was carried out. Numerous features of various architectures and device families from various manufacturers, advantages and disadvantages of various platforms are described in detail.

Paper [3] is devoted to ASIC accelerators for deep neural network (DNN). Multiplier-accumulator (MAC unit) implementation and neural network sparsity are considered in detail. However, the ASIC-based implementation features of neural network computations are described superficially.

Work [4] is devoted to hardware accelerators for real-time face recognition. A lot of algorithms and their implementations based on CPU, GPU, and FPGA are analyzed to solve problems from the area under consideration. The work has a narrow specialization. However, the authors compare various DIP systems in sufficient detail and focus on the high device performance among other things. Paper [5] is devoted to the analysis of methods for speeding up computations in convolutional neural network (CNN). The review has a strange structure and contains many minor errors and typos. Methods for organizing parallel computations and convolution are considered in detail. The issue of implementing convolution through matrix multiplication is widely covered. Various subsampling techniques and activation functions are described. Attention is also drawn to optimization methods for CNN training.

Work [6] is devoted to the analysis of CNN implementations on ASIC. Comparison of neural network architectures on GPU, FPGA, and ASIC is carried out. Many methods for optimizing computations are considered. Various aspects and features of ASIC, as well as specialized techniques for increasing the efficiency of neural network data processing methods, are analyzed. A detailed discussion of the problems is presented and the most promising ways to solve them are outlined.

Paper [7] is a comprehensive analysis of hardware accelerators with a clear structure. This review does not pay much attention to improving the device technical characteristics, but analyzes in detail all sorts of modern platforms aspects and the computations implementation nuances. A huge amount of work is being considered. Their clear classification according to various features is given. A large-scale comparison of methods for accelerators implementation is carried out. All existing problems, their current solutions and challenges are described in an orderly and detailed.

Work [8] is devoted to the analysis of energy-efficient architectures for DNN implementation on edge and mobile devices. Various approaches to optimization of neural network computations on ASIC including those based on network sparsity and approximate computing are considered.

Paper [9] analyzes many aspects of the FPGA accelerators implementation in order to optimize computations in various CNN components. This review is well structured and covers a large number of state-of-the-art approaches. The paper materials are presented clearly. However, not all the ideas described have been analyzed in depth. The narrow coverage of the considered sources is noticeable in places.

Work [10] is a good tutorial with a detailed and visual presentation of all the basics and functioning principles of CNN components. Various aspects of neural network image processing are considered. State-of-the-art CNN architectures are analyzed. This review also has an extensive list of sources for further knowledge deepening.

Paper [11] is a brief and superficial review of DNN optimization methods for efficient hardware implementation on FPGA. This work has a low presentation quality and does not cover all the main implementation aspects of neural network computing. Conference and arXiv papers make up the majority of sources used. These arguments greatly reduce the review significance.

Work [12] reviews FPGA-based deep learning accelerators. Many aspects of the neural network methods implementation for image processing are analyzed. A comparison of various research developments is carried out. The considered works are classified according to various features.

Paper [13] contains a detailed analysis of MAC unit implementation with controlled computation accuracy for neural network devices. Many architectures have been considered. An extensive comparative modeling and comparison of the obtained results was carried out. This review is well structured and has a high presentation quality.

Work [14] is devoted to the analysis of machine vision systems based on FPGA accelerators for unmanned vehicles. Various aspects of autonomous driving and existing FPGA-based solutions for the efficient implementation of neural network computing are considered and discussed. This review focuses on various problems of modern hardware solutions and contains an extended discussion.

Paper [15] reviews the methods of hardware accelerators design for DNN and contains the superficial analysis results of digital device design techniques.

Work [16] considers stochastic computing as a tool for machine learning applications. The architectures of neurons, adders, and multipliers are presented, as well as the analysis results of their effectiveness.

Paper [17] is a review of hardware accelerator architectures for efficient implementation of 3D convolution in CNN. Consideration of 3D convolution instead of a traditional 2D convolution using 3D filter masks is a distinguishing feature of the work. This review is an updated and more compact version of the previous review due to the chosen specialization with all its inherent advantages and disadvantages.

Work [18] is devoted to the analysis of algorithms and hardware implementations of SNN. It mainly discusses the ideas underlying these networks and describes the spike-based computation principles. However, actual hardware solutions are analyzed superficially. This review can serve as a good starting point for researchers interested in mastering this toolkit and wishing to reveal the SNN potential.

Paper [19] is a review of methods for algorithmic and hardware optimization of neural network computations on FPGA devices. Versatile but poorly structured work with a detailed but superficial analysis of approaches based on the analysis of sources with predominantly low scientific significance (30 arXiv papers, 54 conference papers). These shortcomings reduce the review significance.

Work [20] is devoted to the analysis and comparison of existing FPGA-based DNN accelerators. This review is poorly structured but analyzes many papers. Tables with a detailed comparison of various FPGA implementations and a comprehensive description of their characteristics are of particular interest.

Paper [21] is devoted to a detailed analysis of binary neural networks (BNN). The calculations organizing principles using binary weights and activation functions are analyzed. BNN hardware implementation methods based on FPGA and ASIC are described. Various techniques are presented to improve the accuracy of BNN data processing. This review is of interest to researchers who want to deepen their knowledge of the BNN functioning principles.

Work [22] is a low-quality and superficial review of hardware implementation approaches for artificial intelligence algorithms with poor structure and a predominant number of conference papers as sources. This review contains many errors and inaccuracies. The identified shortcomings greatly reduce the review significance.

Paper [23] is a low-quality and superficial review of approaches to the hardware implementation of neural network architectures. This paper contains 150 sources including 55 arXiv papers and 65 conference papers. These facts greatly reduce the review significance.

Work [24] is a low-quality and superficial review of CNN. This review is based on the analysis results of low-grade scientific sources and has a poor structure. The identified shortcomings greatly reduce the review significance.

Paper [25] is devoted to a review of methods for neural networks designing and optimizing based on FPGA devices. The materials are well structured. Various neural network models are considered. Many aspects and features of the neural networks hardware implementation on FPGA are discussed. The main approaches to optimization of computations are classified and described, including the computational accuracy reduction and the convolution implementation in the matrix form. Various architectural solutions are considered and compared.

Work [26] is a brief and superficial review of FPGA-based DNN acceleration methods in the context of cloud computing. Approaches to improve the device performance are described briefly. The identified shortcomings greatly reduce the review significance.

Paper [27] is a review of acceleration methods for neural network computations on FPGA devices. The methodology under consideration is broad in scope. However, approaches are often not analyzed deeply enough and are described briefly, only in general terms revealing the underlying idea. The authors do not describe many works at all, citing only the characteristics of the developed devices.

Work [28] is a low-quality and superficial review of CNN architectures and their FPGA-based implementations. Many methods are described in general terms in a few sentences. arXiv papers make up over a quarter of the sources. Conference papers more than half. These facts greatly reduce the review significance.

Paper [29] is a review of FPGA accelerators for object detection. A superficial analysis and comparison of various platforms and methods for hardware architectures optimizing is carried out. The paper materials are presented at a low scientific level. Nearly half of the sources are arXiv or conference papers. These shortcomings greatly reduce the review significance.

The following conclusions are drawn from the analysis of these review papers.

1. Most of the works are devoted to the methodology development for intelligent processing of digital images based on deep learning and various neural network models. Almost all developments that are not directly related to neural network computing can also improve the technical characteristics of devices and systems for intelligent data processing.

2. The most widely discussed and frequently used approaches are: approximate computing; convolution implementation in the matrix form by the Winograd method (WM); various architectural solutions mostly based on neural network sparsity and pruning; development of specialized hardware accelerators based on FPGA and ASIC.

3. Scientific teams pay a lot of attention to low-grade sources of scientific information when conducting research and writing review papers: non peer-reviewed papers from arXiv; conference papers without a proper description of the methods and conditions for their implementation; journal articles with low scientometric indicators. This fact calls into question the comparison correctness of various research methods and their implementation results, as well as the conclusions drawn significance. The high concentration of such sources clearly indicates the low-quality work. In addition, a significant number of sources are more than 10 years old by the time the corresponding review was published and obviously are not relevant enough for their analysis.

Most of the reviews focused on one or more aspects of DIP. Our review contains the analysis results of all modern tools that are widely used to improve the technical characteristics of DIP devices and systems. The following section introduces the most current and significant mathematical and arithmetic-logical methods of DIP.

### IV. MATHEMATICAL AND ARITHMETIC-LOGICAL METHODS

Modern images are stored primarily in digital form and have limited accuracy. The higher the image accuracy, the more information we have about it. This refers to the image dimension, resolution, the number and depth of color channels. The more information, the more resources are required to process it. Reducing the data representation accuracy in the device memory, namely, approximate computing (subsection IV-A) is the simplest idea to save resources from this point of view.

An image is processed by performing various operations on its pixels or voxels in the case of 3D image. The arithmetic operations of addition, subtraction, multiplication, and division are the basic and most commonly used in image processing. Scaling, comparison, sign detection, exponentiation, square root, and many other are also widely used. Some of them are performed through others depending on the level of implementation (mathematical, software, hardware) and the features of the tools used. Operations have different computational complexity and require different amounts of resources for their implementation. For example, fixed-point multiplication has higher computational complexity than fixed-point addition because it is implemented by multiple additions. The floating point format reverses the computational complexity of these operations. The fixed-point format is more common as it is focused on high-speed computing. The floating point

required image quality as a result of image processing in

format is mainly used in applications with high requirements for computational accuracy. Many approaches have now been developed to further increase the efficiency of performing various fixed-point operations such as addition and multiplication (subsection IV-B). Many of them use approximate computing similar to the methods in subsection IV-A, but implement them by making significant changes to the processing element (PE) structure.

The sharing and reuse of addition and multiplication is at the digital filtering basis which is the most commonly used computational tool for image processing. Filtering is most often implemented as a convolution of an image fragment with a filter of the appropriate size. It is convolution that underlies modern neural network technologies to which the vast majority of works in this research area are devoted. CNN have this name for a reason. Neural network convolution extracts features but also has a large impact on the computational complexity of image processing. Most of the resource costs for the neural network implementation are required precisely for convolution. DNNs with a large number of convolutional layers deserve special attention in this regard. Work is actively underway to modify existing and develop new methods and principles for the convolutional computations implementation in connection with this. The so-called WM (subsection IV-C) is one of the most significant approaches and has repeatedly demonstrated significant success in this direction. This method is based on matrix calculations. Traditional convolution calculates a single value. For example, the brightness of one pixel. WM calculates multiple values in one iteration.

While some researchers are developing various modifications to improve the certain operations efficiency, others are actively working on computing paradigms. RNS (subsection IV-D) is one of the most successful. This tool parallelizes calculations at the arithmetic-logical level and significantly reduces the resource costs of the numerous convolution in particular and the implementation of various image processing methods in general.

All the papers described in section IV are based on one of four basic ideas according to which they are distributed in the corresponding subsections. Therefore, each of subsections IV-A-IV-D first describes the idea itself which underlies the various approaches to its implementation. The following is a brief works description that somehow develop this idea. A conclusion is made based on the papers analysis results after that. Subsections IV-C and IV-D sources rely on a specific method and concept, respectively. Therefore, a brief historical background is made for them.

#### A. APPROXIMATE COMPUTING

Approximate computing is not only the simplest tool for reducing computational complexity but also the most problematic in the context of reducing accuracy. Reducing the amount of information about the image greatly affects the calculation error and the processing quality. This approach is associated with many limitations aimed at achieving the practice. Requirements for the processing quality are imposed on each DIP system developed to solve any particular problem. The most significant calculation error occurs with inputs data size changing. Thus, the original image is usually not cropped and all information about it is used. However, there are works that consider the image bit-depth reduction and analyze the loss of quality caused. The authors of [30] use images with low image bit-depth to increase frame rate and reduce device power consumption while maintaining the necessary accuracy of neural network classification. The input 8-bit image bit-depth is reduced to 3 bits and leads to a moderate calculation error when solving a relatively simple problem. But such a technique imposes many restrictions on reducing the accuracy of intermediate calculations which significantly limits the possibilities of its targeted application. In addition, reducing the input image bit-depth is used in practice only in intelligent data processing which does not require a visual quality assessment by a person and is aimed at reducing the amount of processed data by highlighting main information in the image. In general, approximate computing is implemented mainly in three ways when solving various DIP problems: the designs modifying of adders and multipliers; reducing the bit-width of weight coefficients and activation functions in neural networks; reducing the coefficients bit-width of digital filters used. The first method is discussed in subsection IV-B since it is based on structural changes in PEs and not on a simple discarding of the least significant bits. Approximate computing is a consequence of such changes in this case but not the root cause in contrast to the second and third ways examples of which are presented below.

Weight coefficients and activation functions. The authors of [30] reduce the bit-width of weight coefficients and activation functions in addition to the initial data size to reduce the computational complexity of neural network calculations. Weights are quantized with 4 bits and the activation functions with 6 bits. In [31] only binary weights are used at all, but unlike BNN from 3 to 6 bits are allocated for activation functions, which significantly improves performance and the energy efficiency of convolution. In contrast to this work, the authors of [32] reduce the hardware and time requirements for the implementation of neural network calculations by approximating the hyperbolic tangent function used as an activation function. In paper [33] the quantized weight coefficients have a reduced bit-width to minimize resource costs for the calculations implementation. High accuracy of pattern recognition in images is maintained.

Digital filter coefficients. Paper [34] is devoted to the design of approximate bilateral filters for image denoising. The authors proposed a new approach to digital filtering with reduced computational complexity by approximating the spatial domain coefficients and the intensity range to unsigned integers. A significant improvement in throughput and hardware costs reduction is achieved, at the expense of an acceptable loss in image processing quality. Work [35]

analyzes the influence of the wavelet coefficients accuracy of on the image processing quality at the direct and inverse discrete wavelet transforms. Formulas are derived for calculating the coefficients bit-width that improve the devices characteristics and a high-quality processing is achieved. Paper [36] generalizes the previous study results to the cases of 3D image processing with different color channels bitdepths. The cases of 8-, 12-, and 16-bit images are considered. In [37], a scaling parameter for filter coefficients is introduced and a scheme for digital wavelet filtering of images with reduced computational complexity is proposed.

A variety of digital filtering implementations can be traced in the considered works. However, all of them are based on a single idea of a significant improvement in the device characteristics due to an acceptable deterioration in its qualitative characteristics. The different accuracy influence of digital information representation in intermediate calculations on the image processing result is analyzed for the most part. Comprehensive resource reduction is a strong feature of this approach. Usually, developments reduce one type of resource costs by increasing another. Since the advantage does not come from nowhere. For example, various methods are often proposed to increase device performance with increasing energy consumption. Approximate computing both increases the calculation speed and reduces hardware and energy costs. But the processing quality deterioration entails significant restrictions on this idea usage in various DIP applications that do not accept the loss of even a small part of visual information. For example, medical image processing is very sensitive to information loss, as evidenced by the DICOM standard most commonly used for storing and transmitting diagnostic imaging data. This standard uses increased bit-depth to store images and does not accept lossy compression. However, even loss-of-information applications require a balance between a decrease in computational complexity and an associated increase in calculation error for an acceptable image processing quality in accordance with all the specific limitations of the scientific-technical problem.

#### **B. PROCESSING ELEMENTS MODIFICATION**

Adders and multipliers are the main PEs used in digital image processing devices. PEs multiple use largely determines the hardware, energy, and time resource costs. Various auxiliary tools are also involved on FPGA such as DSP units. Therefore, active work is underway to improve the PEs efficiency. All significant approaches involve structural changes. These ideas are developed in two main directions. The first direction is mentioned in subsection IV-*A* and represents the PE simplification and minimization of basic logical operations. The resulting calculation errors are corrected by some additional tools that do not require significant computational costs. The second direction takes into account implicit information redundancy, various types of connections between PEs, as well as their number, and other possibilities for computations optimizing that do not lead to additional calculation errors. Consider the both directions implementation in more detail.

Approximate adders and multipliers. In [38], an energyefficient approximate adder is proposed. His structure is based on the division of calculations into several parallel blocks. This design shortens the critical path and reduces energy consumption. The resulting errors are detected and corrected by the built-in mechanism. The structure can be adapted both for carry propagation adders and parallelprefix adders. The authors of [39] proposed three schematic models of approximate adders with a modified structure. The developments implementation has reduced power and time costs with a moderate number of computational errors. The paper [40] describes methods for hybrid approximate adders designing based on scale-add operations to reduce energy consumption. Work [41] presents low-power and error-resistant adders and multipliers based on approximation moduli. The authors of [42] propose two designs of a low-power approximate multiplier with a reduced critical path and correction of emerging computational errors. Paper [43] is devoted to the design of approximate Booth multipliers with reduced computational complexity due to some accuracy loss. Three multiplier models are proposed based on various methods for approximating partial product calculations. Work [44] presents a low-power implementation of an approximate MAC unit by replacing multiplication with scaling. Paper [45] discusses the approximate calculations in multipliers focused on energy-efficient digital filtering in convolutional layers of neural networks. Computational error estimation is carried out on the error variance basis, not the average absolute or relative error.

Accurate adders and multipliers. Paper [46] presents a low-power multiplier design based on a Wallace tree using a 7:3 counter and multi-bit addition. The authors of [47] proposed the design technique of modified hybrid full adder and high-performance multiplier. Work [48] describes a high-speed hierarchical MAC unit architecture with a reduced critical path based on a modified Booth encoder and a Wallace tree. Paper [49] presents MAC units with reduced computational complexity based on parallel accumulation technique for CNN. The authors change the traditional operations order. Firstly, they perform the accumulation, then the joint post-pass multiplication. This approach reduces the area and power consumption of the used PEs. The authors of [50] proposed a hardware-efficient implementation of MAC unit based on the Booth multiplier with dual-mode truncation error compensation for convolutional neural networks. Work [51] presents a low-power MAC unit with integration of additions into the partial products reduction. Addition and accumulation of high order bits are not performed until the partial product reduction for the next multiplication in the proposed architecture. The authors of [52] presented a new approach for designing low-power heterogeneous MAC units with a short critical path for voltage scaling resilience and their implementation in DNN. Paper [53] proposes a truncated MAC unit design for digital filtering. This unit does not contain a final adder and has two output values, which significantly reduces the intermediate calculations delay.

The considered works are based on the general idea of computations implementation using PEs built on the basic logical operations "and", "or", and "not". All computing paradigms are built precisely on combinations of these operations. Adders and multipliers are only an intermediate link. All the approaches considered in this subsection are based on increasing the computations efficiency when moving from the logical operations level to the PEs level. Researchers are continuously working to improve the principles of this transition. A wide variety of approaches and their implementations on modern microelectronic devices is observed as a result.

## C. CONVOLUTION OPTIMIZATION USING THE WINOGRAD METHOD

Redundant computations accounting in multiple convolution is the main difference between WM and traditional convolution. The redundancy is present in an implicit form and is effectively eliminated only when organizing computations with several output values in one iteration. Andrei Toom first discovered and described this pattern in his work "The Complexity of a Scheme of Functional Elements Realizing the Multiplication of Integers" in 1963. Stephen Cook developed these ideas and presented them more clearly in his Ph.D. thesis "On the Minimum Computation Time for Multiplication" in 1966. The Toom-Cook algorithm came about as a result. Shmuel Winograd generalized this algorithm and published it in his book "Arithmetic Complexity of Computation" in 1980. All these developments were purely theoretical and did not arouse noticeable interest initially. However, WM was repeatedly modified and adapted to various platforms. The most significant implementation of WM was presented in the form of a report on the topic "Fast Algorithms for Convolutional Neural Networks" at a scientific conference in 2016. Andrew Lavin and Scott Gray clearly demonstrated the WM advantage over traditional convolution when implementing neural network computations on GPU. This work aroused great interest and led to the further WM implementation into various DIP systems. A significant part of computations is performed a priori in the modern form of WM. Most multiplications are replaced by additions with scaling. The computational complexity of digital filtering is greatly reduced as a result. The requirements for the technical characteristics of DIP devices that actively use the convolution operation are reduced using WM. Therefore, WM is actively used in modern DIP devices and systems. Mostly in various CNN and DNN models. A detailed description of the WM principles is presented in the previously mentioned work by Andrew Lavin and Scott Gray. We focus on modern WM implementations.

Paper [54] is devoted to the points choice for the Lagrange polynomial and transformation matrices. This approach minimizes the resource costs for the WM calculations in

DNN with 1D and 2D convolutions. The authors of [55] develop these ideas by proposing an approach to point selection to reduce hardware costs for the implementation of neural network image processing methods. Paper [56] presents a WM-based hardware accelerator with reduced power consumption and hardware costs for object detection using YOLO networks. Work [57] proposed a heterogeneous system for hardware acceleration of neural networks for text recognition. WM improves device performance. The authors of [58] presented a hardware CNN accelerator based on the unified architecture with WM-based element-wise matrix multiplication. Paper [59] describes a high-performance architecture for neural network data processing using WM-based 2D and 3D convolutions. Work [60] presents a 2D digital filtering architecture based on WM to speed up calculations. The authors of [61] optimized the hardware implementation of convolutional computations in neural networks using WM modification and taking into account the network sparsity. This approach significantly reduced the computational latency, device power, and used DSP units. Paper [62] presents an energy-efficient and highthroughput sparse CNN accelerator based on WM matrix multiplication for large convolution kernels. Work [63] proposed a low-power CNN accelerator based on the developed Winograd minimum filtering algorithm. Paper [64] presents high-performance methods for 1D, 2D, and 3D WM-based digital filtering with a convolution step of 2.

Many of the works described contain mostly simple implementations of WM particular cases with strictly defined sets of points and transformation matrices compiled on their basis. The WM digital filtering methodology is developing very slowly unlike all other approaches presented in this review. Most research teams have mastered this technique only superficially without really delving into the mathematical subtleties. This approach significantly hinders the WM development. We hope that WM will become a generally accepted and standard approach to organizing convolutional computing in the future. Then the researchers will study this tool more thoroughly and improve the WM efficiency. This will be a more significant contribution to the science development than simply replacing the traditional convolution with a WM special case in any neural network model.

#### D. COMPUTATIONS IN THE RESIDUE NUMBER SYSTEM

RNS is a non-positional number system in which a number is represented as a group of remainders when divided by a set of RNS moduli. RNS computations are implemented by performing operations on these remainders. RNS is based on modular arithmetic and relies on the Chinese Remainder Theorem first formulated by Sun Tzu in the treatise "Sunzi Suanjing" presumably between the 3rd and 5th centuries AD. Antonin Svoboda and Miro Walach developed the concept of RNS computations and first presented it to the scientific community in 1955. Harvey Louis Garner developed their ideas and presented an extended description of RNS in his Ph.D. thesis "Error Checking and the Structure of Binary Addition" in 1958 and a summary of the basic computational principles in paper "The Residue Number System" in 1959. The concept of RNS computations was proposed as an alternative to traditional positional number systems and gradually developed over time attracting many researchers with its fault tolerance and high potential for parallel computing. RNS found its way into various digital data processing applications at a certain stage in microelectronics development. In particular, in digital signal processing which is described in detail in the work "Residue Number Systems: A New Paradigm to Datapath Optimization for Low-Power and High-Performance Digital Signal Processing Applications." RNS is also considered as a full-fledged replacement for traditional computer arithmetic systems on promising microelectronic architectures of future generations [1]. However, RNS has many disadvantages. Low efficiency in the non-modulo operations implementation such as scaling, division, root extraction, sign determination, and number comparison. High overhead for transferring from RNS to positional number system. Impossibility of numbers visual comparison. No visible signs of overflow. These disadvantages limit the wide practical application of RNS. However, many DIP methods are based on the repeated use the modulo operations of addition and multiplication which realizes the RNS potential. Thus, the computations efficiency is significantly increased which is confirmed by the scientific research results presented below.

The authors of [65] presented a modular adder design with delayed carry-through to improve the various technical characteristics of digital filtering devices. Paper [66] uses RNS to improve the digital filtering speed. Work [67] is devoted to the choice of RNS moduli set for efficient hardware implementation of computations. The proposed set weakens the requirements for energy consumption and device area, but increase PEs delay. Paper [68] presents two modular adders with reduced latency, allocated area, and low energy consumption based on internal calculations without transfers. The authors of [69] proposed a computational approach based on RNS with reduced hardware costs by increasing the energy consumption. Work [37] presents RNS-based method for wavelet processing of 3D medical images. RNS increased the computation speed by increasing the hardware costs. Paper [70] proposes a method for energy-efficient neural network image processing based on RNS. The authors of [33] described an area-efficient hardware implementation of CNN based on RNS computations. Paper [60] presents a high-throughput digital image processing filter architecture based on RNS computations.

The RNS paradigm is actively developing in many directions including both the modular computing methodology on modern platforms and the expansion of its use in DIP applications. Nevertheless, the niche use of RNS computations remains due to its inherent disadvantages. Mathematical tools actively improve the technical characteristics of DIP devices and systems. It relies heavily on the four identified pillars but is by no means limited to them. Attention in this review is paid only to the most significant representatives of this ideas. Many PEs beyond adders and multipliers are also being actively improved. WM is far from the only approach to convolution optimization. Likewise, RNS is just one of many alternative computing paradigms. However, they are among the most common mathematical solutions and are actively used by various research teams around the world. Architectural and structural solutions in contrast do not have a clear hierarchy. Such approaches classification is a very difficult task. But the most common features can be identified. These results are presented in the next section.

## V. VARIOUS ARCHITECTURAL AND STRUCTURAL SOLUTIONS

Scientific teams offer many approaches to improve the technical characteristics of DIP devices based on various architectural and structural solutions. Including hybrid and multimodal neural networks, as well as neural networks ensembles. Such solutions are being actively developed mainly for intelligent data processing systems and represent a large number of versatile ideas and their implementations. The works presented in this section are very original and difficult to classify. They are versatile and replete with great variety and a high concentration of significant solutions. Therefore, they are characterized in more detail than the works from section IV. In addition, some common features and directions for the development of ideas in these works have been identified. Table 4 contains all the similarities found in the considered aspects context of the computational methods implementation, optimization of the processes under consideration, and increasing the efficiency of various tools and structures. The first column contains all works from this section. Correspondence of works to the selected aspects is marked with a " $\times$ " in other columns.

The authors of [57] proposed a heterogeneous neural network acceleration system for text detection in images. The approach is based on the scheme of partitioning into subgraphs and WM, as well as their implementation on CPU-FPGA. This system uses fixed-point quantized weights and piecewise linear approximation of activation functions in neural network to achieve a high degree of parallel computing and reduce resource costs. The experimental results showed a significant increase in device performance.

Work [62] proposes a high-speed hardware CNN accelerator based on sparse matrix multiplication using WM. The dynamic scheduling scheme and the balanced sparse string compression format improve the computational load balance and increase the PEs efficiency. The proposed solutions take into account the sparseness of both the weight coefficients and the CNN activation functions. WM organizes calculations not only in convolutional layers but also in fully connected ones. The proposed ideas combination

| Paper                                                        | Dataflow | Memory | Throughput and<br>Performance | Power and Energy | Parallel computing | Computation<br>Reduction | Processing Element<br>Efficiency | Convolution | Graph | Framework and<br>Design Pattern | Flexibility and<br>Reprogramming | Other                 |

|--------------------------------------------------------------|----------|--------|-------------------------------|------------------|--------------------|--------------------------|----------------------------------|-------------|-------|---------------------------------|----------------------------------|-----------------------|

| [57]                                                         |          |        | ×                             |                  |                    |                          |                                  | ×           | ×     |                                 |                                  |                       |

| [62]                                                         |          |        |                               | ×                |                    | ×                        | ×                                | ×           |       |                                 |                                  |                       |

| [57]<br>[62]<br>[71]<br>[72]<br>[73]<br>[74]<br>[75]<br>[76] |          |        |                               | ×                |                    | ×                        |                                  |             |       |                                 |                                  |                       |

| [72]                                                         |          |        |                               |                  |                    |                          |                                  |             |       | ×                               |                                  |                       |

| [73]                                                         | ×        |        | ×                             |                  | ×                  |                          | ×                                |             |       |                                 | ×                                |                       |

| [74]                                                         |          |        | ×                             | ×                |                    |                          |                                  | ×           |       |                                 |                                  |                       |

| [75]                                                         |          |        |                               |                  |                    |                          |                                  |             |       |                                 |                                  | ×a                    |

| [76]                                                         |          |        |                               | ×                |                    |                          |                                  |             |       |                                 |                                  | $\times^{\mathrm{b}}$ |

| [77]<br>[78]<br>[79]<br>[80]                                 | ×        | ×      |                               | ×                |                    |                          |                                  | ×           |       |                                 |                                  |                       |

| [78]                                                         |          | ×      |                               |                  |                    |                          |                                  |             |       |                                 |                                  |                       |

| [79]                                                         |          |        |                               |                  |                    |                          |                                  |             | ×     | ×                               |                                  |                       |

| [80]                                                         | ×        |        |                               |                  | ×                  |                          | ×                                |             |       | ×                               |                                  |                       |

| [81]                                                         |          | ×      | ×                             | ×                | ×                  |                          | ×                                | ×           |       |                                 |                                  |                       |

| [82]                                                         | ×        |        | ×                             | ×                |                    |                          |                                  | ×           |       |                                 |                                  |                       |

| [83]                                                         | ×        |        | ×                             |                  |                    |                          |                                  |             |       |                                 | ×                                |                       |

| [83]<br>[84]<br>[85]<br>[86]                                 | ×        | ×      | ×                             |                  | ×                  |                          |                                  |             |       |                                 |                                  |                       |