Received 29 January 2024, accepted 10 February 2024, date of publication 19 February 2024, date of current version 29 February 2024. *Digital Object Identifier* 10.1109/ACCESS.2024.3367598

# APPLIED RESEARCH

# A Graph Attention Network Based System for Robust Analog Circuits' Structure Recognition Involving a Novel Data Augmentation Technique

# ALI DEEB<sup>®</sup><sup>1</sup>, MOHAMED SALEM<sup>®</sup><sup>2</sup>, ABDALRAHMAN IBRAHIM<sup>®</sup><sup>3</sup>, JOACHIM PICHLER<sup>2</sup>, SERGII TKACHOV<sup>2</sup>, KARAJ ANJEZA<sup>2</sup>, FADI AL MACHOT<sup>®</sup><sup>4</sup>, (Member, IEEE), AND KYANDOGHERE KYAMAKYA<sup>®</sup><sup>1</sup>

<sup>1</sup>Institute of Smart Systems Technologies, University of Klagenfurt, 9020 Klagenfurt, Austria

<sup>2</sup>Infineon Technologies Austria, 9500 Villach, Austria

<sup>3</sup>AGILOX Services GmbH, 4671 Neukirchen bei Lambach, Austria

<sup>4</sup>Faculty of Science and Technology, Norwegian University of Life Sciences (NMBU), 1430 Ås, Norway

Corresponding author: Ali Deeb (Ali.Deeb@aau.at)

This paper is funded by Infineon Technologies Austria.

**ABSTRACT** This paper addresses the issue of reliable and automated analog circuit's structure recognition (ACSR). First, it presents a comprehensive critical review of the related state-of-the-art. Then, essentially, this study proposes and validates a novel approach for realizing a dependable structure recognition system for analog circuits through a comprehensive ontology definition, some transformation tools, scene modeling through graph models, and then, by involving a graph attention neural network (GAT) model. Knowingly, identifying sub-circuits requires, in the brute-force mode, extensive screening of the numerous alternative substructures that can be constructed from the basic elements (i.e. the transistors) in presence, especially w.r.t. the actual connectivity topology amongst them; this is evidently a very complex and challenging endeavor. The relevant state-of-the-art has involved mostly unsupervised learning approaches to tackle this analog circuit's structure recognition-related challenging task, whereby they have reached a clear limitation of not (or only very hardly) reaching beyond 90% to 93% accuracy/precision. But in this work, we develop, for the first time, a comprehensive supervised-learning approach that demonstrates its clear superiority by enabling the reaching of a recognition accuracy or precision that is reliably in the range beyond 99% (or even 100%) for each subblock of the analog circuit. The supervised clustering approach developed and validated in this study consists of a comprehensive modeling and conceptual pipeline that is implemented around and through a Graph Attention Neural Network model, which ensures a reliable recognition of sub-blocks of analog circuits and their related internal adjacency connectivity topology. Besides the modeling pipeline, this study also develops a set of tools for mapping an analog circuit's schematics into a graph model. To overcome the limited and unbalanced samples for training the graph neural model, this study proposes a special novel augmentation strategy based on a graph sub-cropping technique. This augmentation technique is embedded in a smart stepwise augmentation protocol that leads at the end, through iterative additional dedicated training steps to a significant progressive increase of the recognition accuracy by the graph neural model until reaching more than 99%, better 100%, for each of the subblocks of the analog circuits as demonstrated in the demonstration case-study presented. Indeed, this paper's quintessence represents a significant breakthrough in view of the clear outperforming of the currently relevant related state-of-the-art.

**INDEX TERMS** Analog circuit's structure recognition, graph clustering, deep learning, graph attention neural networks, robust data augmentation.

The associate editor coordinating the review of this manuscript and

approving it for publication was Artur Antonyan

© 2024 The Authors. This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 License. For more information, see https://creativecommons.org/licenses/by-nc-nd/4.0/

#### I. INTRODUCTION

Analog and mixed-signal circuits form the foundation of many electronic devices in use today. As demand for smaller and faster devices grows, the need for higher-speed and lower-power consumption has become increasingly urgent. This has led to the use of more complex and powerful analog/mixed-signal (AMS) systems. However, as these systems become more complex, the design and verification tasks become more challenging and time-consuming. One of the main difficulties in working with analog and mixed-signal circuits is their complexity, which can make it challenging to understand the overall structure of the circuit and how it works [1]. In order to automate the design and verification of AMS circuits, it is essential to recognize the circuit structures used in AMS design. Machine learning has become an active research area in recognizing circuit structures in analog and mixed-signal circuits [1], [2]. Several approaches have been proposed and studied. Some common approaches include using a supervised learning algorithm to learn a set of features from a labeled dataset of circuits and then using those features to recognize circuits in new circuit's data [1]. Other approaches include unsupervised learning algorithms, which learn features from unlabeled data, and through transfer learning, which uses features learned from one dataset to recognize structures in a new dataset [3].

Identifying structures in a hierarchical schematic represents one of the most challenging and time-consuming tasks during the development of an analog-mixed-signal integrated circuit (AMS-IC). Manual structure identification requires a significant amount of domain-specific knowledge [3]. Currently, no commercially available technology can automatically detect structures at the schematic level. The goal of the research reported in this paper is to automatically perform structure recognition in analog circuits while ensuring an accuracy close to or higher than 99%. Therefore, we have used graph neural network approaches to solve the challenging issue of automated subblock detection within a given analog circuit, even across hierarchical borders without making any assumptions about the job beforehand. The experiments conducted in this paper provide results that confirm that the proposed approach, based on Graph Attention Networks, is very promising. Indeed, this work does automatically categorize the functional labels of the identified subblocks. These categories include, for the demonstration use-case, just to name a few, current mirror, differential pair, cascode current mirror, and other analog building blocks of the same level.

The notable contributions of this paper can be summarized around satisfactorily reaching the following core objectives:

- Determining and discussing how important analog circuit's structure (i.e. subblock) recognition is in various important application domains within the AMS circuits engineering processes.

- 2) A comprehensive critical review of the related state-of-the-art.

- 3) A comprehensive ontology in the frame of the converting process of any analog circuit into a graph model, this coupled with a comprehensive modeling workflow that involves machine learning methods, in this case, graph neural networks, to reliably resolve the analog circuit's structure recognition problem or its equivalent task in the graph domain, that is the so-called "graph clustering" problem.

- 4) Suggest a comprehensive protocol for analog circuit structure (sub-blocks) recognition using Graph Attention Network (GAT). In the frame of a comprehensive holistic modeling protocol/methodology, we build and optimize a Graph model that represents the AMS circuit at hand.

- 5) Create and validate a novel dataset augmentation strategy that does enhance progressively the GAT-based graph clustering model's performance, this in consideration of practical real-world scenarios where initial real/native training datasets may be or are rather mostly very limited in size and unbalanced w.r.t. the possible subblock labels.

- 6) Suggest a comprehensive protocol/methodology to ensure a detection accuracy of 100% (or very close to 100%) for all subblocks of a given analog circuit's family (i.e. for a known list of possible subblocks).

- Demonstrate through a conceptual and qualitative comparison with findings from related works the novelty and evident superiority of the overall concept developed in this paper.

Our overall modeling pipeline assumes that the analog circuit to be clustered will be available as a SPICE circuit netlist generated using Cadence Virtuoso, which is the tool used in analog circuits engineering processes. Cadence Virtuoso can produce a description of the circuit entity (the schematics in Cadence Virtuoso) in a text form called "netlist". Thus, a parser is needed to interpret the netlist and build out of it a "graph model" describing the circuit entity. This graph model, the output of the parser, is the one to be processed by a graph attention node classifier model.

In circuits design, a netlist is a description of the connectivity of an electronic circuit. A netlist contains amongst other things a list of the electronic components contained and a list of the nets connecting these components. A net is a collection of two or more interconnected components. A supervised learning-based analog substructure recognition concept has been designed and is comprehensively explained in this work. More than 99% clustering accuracy has been achieved, as validated by the extensive experiments conducted and reported in this paper. This clearly and significantly outperforms competing unsupervised learning approaches from related works. For example, just for illustration, a K-Means followed by (coupled to) a graph neural network (GCN) model was used in an unsupervised learning approach, see Ref [4], to perform structure recognition and find the subcircuits in an analog circuit. However, this last-named concept requires the (guessed

or known) number of subcircuits as input to K-Means to achieve high accuracy, which is a drawback for automation.

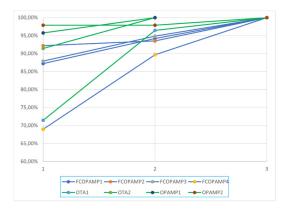

In the core case study discussed in the paper, the initial dataset (processed and built using Cadence Virtuoso) was used for the first comprehensive initial training of the graph attention neural network (GAT) model of our novel concept. However the initial results, which were in the level of those of most related works, needed to be still significantly improved. Hence, a novel and smart augmentation technique has been developed for that purpose, this is based on what we call the "subgraph cropping method" (explained later in this paper), and the subsequent accuracy was effectively stepwise, progressively, and significantly improved. Essentially, as will be closely explained later below, the progressive novel dataset augmentation process is guided by a progressive label-aware dedicated step-wise dataset balancing strategy. The process is successful as it leads to achieving more than 99% accuracy (i.e. 100%) for the structure (i.e. subblocks) recognition endeavor.

This paper's remaining sections are structured as follows; The importance and related a requirements engineering for a comprehensive analog circuits' structure recognition are covered in Section II. A comprehensive critical review of the related state-of-the-art is provided in Section III. In Section IV, we comprehensively describe our novel method for subblock recognition and it is handled through its equivalent problem of "graph clustering", whereby a comprehensive ontology is developed for a comprehensive mapping of an analog circuit into an equivalent graph model. Thereby, a general methodology for building a "graph clustering" pipeline is introduced.

In the following section, Section V, the dataset collection, its transformation, and its general preprocessing are discussed. Section VI presents the concept of a Graph Attention neural network model (the so-called GAT) that we suggest for structure recognition, its design, and its validation. Now, addressing the challenge related to size limited and unbalanced datasets is addressed through one novel innovative data augmentation strategy that is coupled to the GAT model; this is explained in section VII. Further, the experiments' anatomy for the suggested pipeline is presented in section IX. Section X presents and discusses a global qualitative performance evaluation of the suggested GAT-based model when compared to the most relevant recent related works. Finally, Section XI contains comprehensive concluding remarks describing the quintessence of the research reported in this paper.

### II. IMPORTANCE AND REQUIREMENTS OVERVIEW OF AN ANALOG CIRCUITS STRUCTURE RECOGNITION

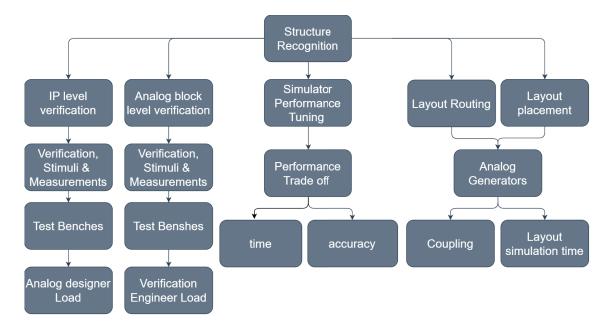

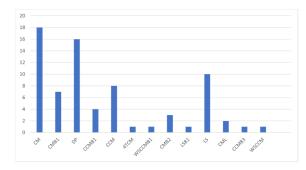

Analog circuits can be viewed as hierarchical structures having different levels. At each level of the hierarchy, one has different building blocks or entities that carry specific names depending on their respective pattern. Thus, every building block of a particular level is made up of lower-level building blocks. And this repeats so all the way down up to the very lowest-level consisting of transistors and other primitives (e.g.: nets, passive elements, diodes, etc.) [2], [4], and [5]. Therefore, analog circuits structure recognition enables a greater understanding of the properties and requirements of a given complex circuit (viewed from various level-related perspectives). Indeed, being able to classify analog circuits and, more specifically, recognize their internal structure without human supervision/intervention does accelerate several processes in the semiconductor industry. For example, a layout engineer could benefit from the structure recognition for layout routing of the subcircuits without inspecting the design in simulation. These work elements help reduce development time. Another practical use is to detect subblocks within a given analog circuit for symmetry detection and component placement in layouts [2]. In general, an efficient structure recognition of analog circuits and of the related topology does significantly impact a lot of semiconductor applications. Figure 1 presents a representative list of the many use-cases (within the circuits engineering business) for which analog subblocks recognition is very needed and is of precious value in the context of analog/mixed signals circuits' engineering.

An analog circuits designer needs knowledge about the subblocks' identities to appropriately translate the design into a layout via layout placement and routing. Therefore, knowing the names of the subblocks and, therefore, their functions will greatly speed up layout simulation and coupling in automated analog circuit generators. Also, in other contexts, to get precise results for analog circuit design, one needs to solve differential equations through simulators. However, doing so either requires a lot of computing time or relies on already pre-solved differential equations, which reduces the accuracy margin. For maintaining a high level of accuracy, analog circuit structure recognition may assist the simulator in finding a better selection of the differential equations that have already been solved and thus support maintaining a high level of accuracy. This is done in much less time than it would take to obtain a precise solution. Analog circuit structure recognition further helps in the so-called "analog block-level identification," which is helpful for block-level verification and thereby lessens the workload of the verification engineer. Analog circuit designers may also gain from understanding the subblocks of the circuit or schematic by selecting the proper test bench to produce stimuli, carry out verification, and carry out additional measurements. Guaranteeing the circuit's functionality at the IP level lowers the amount of work the designer needs.

The importance of structure recognition being so far clear, let us formulate now a minimum requirements engineering dossier (i.e. specification book) for a robust structure recognition model for analog circuits. A genuinely robust analog circuit structure recognition system must meet the following 10 requirements (RQs):

1) REQ-1 (Accuracy Baseline – WITHOUT POST-PROCESSING): The core model (essentially neural model) should guarantee a structure recognition

**FIGURE 1.** Flow diagram of structure recognition importance.

accuracy of at least 97%, with a target to reach an optimal 100% accuracy for all subblocks, including challenging cases such as those outlined in REQ-8. The methodology to ensure reaching the target performance through the core model must be explicitly presented.

- 2) REQ-2 (Topology Variability Robustness): The model should maintain a high recognition robustness across various circuit topologies, encompassing differences in component values, placements, and wiring configurations. Specific common topologies the model should recognize must be identified.

- 3) REQ-3 (Transistor Type Variability Robustness and MULTI-NODES TRANSISTOR REPRESENTA-TION): The model ensure high robustness when faced with circuits that utilize different or mixed transistor types (e.g., bipolar, NMOS, and PMOS) within the same subblock. Future-oriented transistor types should also be taken into consideration. Hereby, it is important to check with how many nodes a transistor is represented. Essentially each transistor shall be represented by multiple nodes in the equivalent graph model. This has also an impact on the vertical scalability described in REQ-5. All models representing a transistor with only one node will surely be limited w.r.t. REQ-5.

- 4) REQ-4 (Dataset Resilience): The model and subsequent additional concepts should be designed to handle dataset challenges like limited size and "subblock labels"-related imbalance. For example, it should integrate some advanced augmentation techniques to mitigate these challenges.

- 5) REQ-5 (Hierarchical Scalability): The model must be applicable across multiple levels of analog circuits, from the simplest to the most complex.

VOLUME 12, 2024

It should adeptly handle multi-level hierarchical circuits where sub-blocks might have intricate internal sub-circuits. (Eventually, a proof of concept must validate performance on at least the four initial levels).

- 6) REQ-6 (Standardized Representation of entities of any level): Advocate for compatibility with a standardized representation of circuits, or ensure the model is adaptable to widely accepted methods. Special focus should be on the representation of transistors and high-level subblocks, addressing issues like the number of nodes required for representation. The issue is that entities of all levels must be capable of being represented with multiple nodes.

- 7) REQ-7 (Size Scalability): The model should be versatile enough to analyze circuits of varied sizes, from those with a handful of components to those with thousands. The model shall be capable of handling varying input-graph sizes.

- 8) REQ-8 (Similar Topology Handling): The model should be capable at recognizing and distinguishing between multiple subcircuits with that have the same label (i.e. similar topologies) within a given circuit, thus avoiding errors like incorrect clustering or merging of distinct sub-circuits.

- 9) REQ-9 (Adaptive Training): The model must support progressive "smart/context-aware" supervised learning, allowing performance improvements over time as more data or feedback is available. This is coupled to an adaptive/smart/ context-aware dataset augmentation.

- REQ-10 (Model Extendibility a.k.a. "HORIZON-TAL SCALABILITY"): Ensure the model can be progressively trained to incorporate new subblock labels or patterns. This includes adding new layers, nodes, or patterns, as well as the potential to forget;

or deprioritize obsolete patterns. We call this "HOR-IZONTAL SCALABILITY". But the introduction of a new sub-block requires the adaptive training mentioned in REQ-9. Thus, a model that does not fulfill REQ-9 cannot satisfy REQ-10 either.

11) REQ-11 (Operational Environment Compatibility): The model should be compatible with prevalent EDA (electronic design automation) tools and platforms and be efficient enough for real-time or near-real-time operation during circuit design processes. This requirement is for me of low priority. This requirement becomes only relevant if the model has proven to satisfy first all 10 previous requirements. The model development in the "RESEARCH" phase tries to satisfy all 10 requirements first. If this succeeds, then for the "ENGINEER-ING" phase, for the application in specific industrial processes later on, this requirement (REQ-11) becomes then relevant.

Ensuring a detection high accuracy (i.e., higher than 97%) for an automated analog circuit structure recognition is not trivial. According to the related works, it is an extremely difficult task to reliably tackle [3], [6]. Still, it is an industrial requirement in view, amongst others, of the various use-cases (see Figure 1) needing this functionality. But in this work, it is crucial to put on the table a comprehensive methodol-ogy/protocol that shows and validates that a 100% detection accuracy can be reached for all subblocks of the analog circuit even for the case described in REQ-8 above.

# III. COMPREHENSIVE CRITICAL REVIEW OF THE RELATED STATE-OF-THE-ART

Knowingly, the analog design and verification processes are time-consuming and require tremendous effort and high human experience (e.g., running test simulations, using behavior models for block functionality checks, and setting proper model test benches) [7]. These two last-named processes need specific design knowledge to ease the identification of structures, sub-structures, and related features. Most of this knowledge production is done manually by virtue of experienced analog design engineers [4], [8], [9]. Because of these needed experiences, several research efforts have started focusing on the automation structure and/or substructure recognition/identification by using different procedures.

In this section, we review related work in AMS schematic structure recognition, focusing on the strengths and weaknesses of existing approaches. Several approaches have been proposed to address the challenge of recognizing the complex structure of analog-mixed-signal (AMS) circuits. These approaches include several methods, which we will discuss as follows:

#### A. TEMPLATE-BASED METHODS

The success of Template-based methods [5], [10], or Librarybased methods, depends on including all possible designs in one library, or in other words, building a comprehensive library of structures. In this case, structure recognition means searching for the exact structure in this library. when it is found, then the procedure is successful. However, any slight change in the design of the circuit structure, which is a common thing and sometimes necessary, leads to a recognition failure. therefore, this method is not robust since the matching with the library elements is strict, and there is no sense of measuring the accuracy of this method for new test samples.

#### **B. SEARCH-ORIENTED BASED METHODS**

The works presented in [11] and [12], have introduced search-oriented algorithms for sub-circuits recognition by involving subgraph isomorphism [11] and pattern matching, [12]. These methods were efficient in subcircuit recognition but are very time-consuming, especially for large circuits, as they use trial and error techniques. The circuits mentioned in these papers were clustered correctly, but no accuracy was stated for a test dataset, and clustering time was the evaluation metric for these methods.

#### C. GRAPH-BASED METHODS METHODS

Reference [13] proposed a circuit graph coding to discover and verify subcircuits. This coding identifies each subcircuit by generating a unique code for each one of the subcircuits. This unique code depends on the fact that each transistor has specific features and is connected to different nodes. the drawback of this approach is that the circuit partitioning is done before the recognition. Hence, the postprocessing is a must to ensure high accuracy. Although the approach was applied on large circuits, which include up to 15000 transistors, no accuracy was mentioned for a test dataset.

In [14], the so-called "bipartite graph labeling" algorithm for the subcircuit recognition was suggested and combined with the "probabilistic match assignment algorithm", [15], [16], for recognizing sub-circuits. In essence, a probabilistic method has also been integrated with a nonlinear function that calculates a structure matrix for matching between devices and nets in different levels (e.g., circuits and subcircuits). However, the structure recognition accuracy varies from 76% to 100%, depending on the test schematic.

The primary concept technique, developed in [15], involves creating match matrices, which define how the subcircuit and circuit nets and devices correspond to one another, respectively. During the optimization phase, the matrix elements are calculated by a productive bipartite graph labeling algorithm and the GA matching method. Besides in [16], an approach to recognize graphs based on optimization for the structure recognition problem. The error propagation and soft (delayed) decision-making concepts from pattern recognition theory are combined with the self-annealing optimization strategy in this approach. In both references, runtime was the evaluation metric.

The probabilistic match assignment method was faster than search-based approaches, but it struggled to keep up with the requirements of CAD software containing a template library of a large number of large circuits, which necessitates more user/tuning effort to reduce the computation cost of the probabilistic match assignment method [17]. In order to overcome the high computation complexity struggle, [18] used a nonlinear graph optimization strategy of second-order terms instead of first-order linear optimization techniques of references [15] and [16].

#### D. UNSUPERVISED LEARNING-BASED METHODS

The topological (structural) properties of analog circuits can now be automatically identified and extracted thanks to a revolutionary technique presented in [19]. The study offers unsupervised feature extraction algorithms. The following key issues are addressed by the method: hierarchical structures, repeated structures, and overlapping amongst building blocks. Thereby 34 modern analog circuits were the subject of experiments that examine feature extraction. The accuracy and efficiency of operations like circuit synthesis, scaling, and design knowledge description depends on the ability to find structural features. Nevertheless no concrete accuracy was provided for a test dataset.

Using GCN proprieties the studies in [20] play a key role in circuit elements classification which, in turn, sums up these elements to make higher-level known building blocks (e.g., current mirror, differential pair) to be used in various circuitry applications. Also, [21] presents a structure recognition algorithm that is "library-free" to extract the basic blocks of any circuit relying on some rules given to the algorithm.

In [22], a system that bridges schematic and layout creation is presented. It achieves this by identifying key subcircuit structures using Graphical Convolutional Neural Networks (GCNNs) and an unsupervised graph clustering approach.. To our knowledge, this framework fully automates clustering. It achieves over 90% accuracy in under 1 second across six analog circuits of varying size and complexity. The maximum accuracy, which varies from 91.3% to 100%, was the only accuracy provided. Meanwhile, [3] proposed a "K-Means + GCN"-based recognition framework for circuit recognition. The experimental findings demonstrate the potential of the suggested approach based on the K-Means and GCNs algorithm.

#### E. SUPERVISED LEARNING-BASED METHODS

Reference [23] uses a convolutional neural network (CNN) for the identification and recognition of building blocks seeking circuit layout automation without considering human inputs or experience. The accuracy reached was  $97.2\% \pm 1.4\%$ . Similar to [24], a Graph Convolutional Network (GCN) based technique is used for structure identification using a transistor-level netlist of the circuit. A unique strategy is presented in [24], for clustering analog circuits utilizing library-based primitive matching and GCN-based machine learning. The GCN-based technique can handle diverse subblock design topologies, as shown on two hand-

crafted circuits. The technology is scalable and successfully clusters circuits into subblocks and creates circuit hierarchy trees. The accuracy of clustering varies from 79.8% to 98.2% depending on the circuit type. However, postprocessing was performed to increase the accuracy to 100% for all test cases. Postprocessing was used to avoid overfitting and to help the GCN model with the limited dataset. Two classes of heuristics were used in the final stage after the GCN. The first class uses a graph-based heuristics in which nodes that belong to the same channel-connected component (CCC), a group of transistors connected at the sources and drains, are assigned to a subblock. We then identify all primitives within a CCC using graph-based approaches to extract primitives within a subblock. All primitives in a CCC that are integral parts of a subblock (e.g., a differential pair in an OTA) are added to the hierarchy tree at the same level. An independent primitive, which can be considered an independent entity (e.g., an input buffer for an oscillator, as occurs in our phased array example), is separated and listed as an independent primitive in the hierarchy tree. The second class refers to circuit-specific knowledge and is based on information about the connections to the input/output ports.

Table 1 shows an overview of the most relevant related works with respect to an assessment of how far they do satisfy or not the eleven hard requirements formulated and outlined in section II (see Requirements Engineering dossier consisting of 11 Requirements)

Table 1's main message is fundamentally and factually a form of "gap analysis" for all works that performed structure recognition regardless of the method. It is true that none of the relevant works entirely meet the specified requirements dossier. However, and this is the main goal, the novel concept developed and validated in this paper is expected to fulfill all of the defined requirements. This will highlight its innovative nature in comparison to the most current and relevant stateof-the-art.

Reference [3] mentions an accuracy of over 95%, but it doesn't reach the 97% baseline. Hence, REQ-1 was not fulfilled. Regarding REQ-2, the paper does discuss the use of different schematics. The used model can recognize different circuit topologies and adapt to different configurations. The paper explicitly states that MOSFETs were considered, without mention of other transistor types like bipolar, NMOS, or PMOS. Therefore, REQ-3 was not met. Regarding REQ-4, there is no clear mention of the model handling dataset challenges. This paper fulfills REQ-5 since the used scheme appears to handle hierarchical schematics. Regarding REQ-6, it is unclear if the model supports a standardized representation of circuits. The paper doesn't explicitly mention varied sizes of circuits, and the model is GCN-based. Hence, REQ- 7 was not met. While the methodology identifies structures, it is unclear if it can distinguish between similar topologies within a given circuit. Therefore, REQ-8 was not fulfilled. Regarding REQ-9: the paper doesn't specify progressive supervised learning based on a step-wise augmentation technique, and the introduction

TABLE 1. An overview of the most relevant related works w.r.t. an assessment of how far they do satisfy the five requirements formulated and outlined in section II (see Requirements Engineering dossier.

|                       | DEO 1 | DEO A | DEO 2 | DEC 1 | DEO 5    |               | DEO 7         | DEO 0 | DEO 0 | DEO 10        | DEO 11        |

|-----------------------|-------|-------|-------|-------|----------|---------------|---------------|-------|-------|---------------|---------------|

|                       | REQ-1 |       | ~     | REQ-4 | <u> </u> | <u> </u>      | REQ-7         | · ·   | REQ-9 | REQ-10        | REQ-11        |

| Rituj et al. [3]      | Yes   | Yes   | No    | No    | Yes      | No            | No            | No    | No    | No            | Yes, possibly |

| Meissner et al. [10]  | No    | Yes   | No    | No    | No       | No            | No            | Yes   | No    | No            | No            |

| Massier et al. [5]    | No    | No    | Yes   | No    | Yes      | No            | Yes           | Yes   | No    | No            | Yes, possibly |

| Ohlrich et al. [11]   | No    | Yes   | Yes   | No    | No       | No            | Yes           | Yes   | No    | Yes           | Yes, possibly |

| Pelz et al. [12]      | No    | Yes   | yes   | No    | Yes      | No            | No            | Yes   | No    | Yes, possibly | Yes, possibly |

| Huang et al. [13]     | No    | Yes   | Yes   | No    | No       | Yes           | Yes           | Yes   | No    | No            | Yes, possibly |

| Rubanov et al. [14]   | Yes   | No    | No    | No    | No       | No            | Yes           | Yes   | No    | No            | Yes, possibly |

| Rubanov et al. [15]   | Yes   | Yes   | No    | No    | Yes      | No            | Yes           | Yes   | No    | No            | Yes           |

| Rubanov et al. [16]   | Yes   | Yes   | No    | No    | Yes      | No            | Yes           | Yes   | No    | No            | Yes, possibly |

| Conn et al. [17]      | No    | Yes   | No    | No    | No       | No            | Yes           | Yes   | No    | No            | No            |

| Rubanov et al. [18]   | Yes   | Yes   | No    | No    | No       | No            | Yes           | Yes   | No    | No            | Yes           |

| Li et al. [19]        | Yes   | Yes   | No    | No    | Yes      | No            | No            | Yes   | No    | No            | No            |

| Neuner et al. [21]    | Yes   | No    | No    | No    | No       | No            | Yes           | Yes   | No    | No            | No            |

| Settaluri et al. [22] | No    | Yes   | No    | No    | Yes      | No            | No            | Yes   | No    | No            | No            |

| Liou et al. [23]      | Yes   | Yes   | Yes   | No    | No       | Yes, possibly | Yes, possibly | No    | No    | No            | Yes           |

| Kunal et al. [24]     | No    | Yes   | No    | No    | No       | No            | No            | No    | No    | No            | No            |

REQ-1: Accuracy Baseline

REQ-2: Topology Variability Robustness

REQ-3:Transistor Type Variability Robustness

REQ-4: Dataset Resilience

REQ-5: Hierarchical Scalability

REQ-6: Standardized Representation REQ-7: Size Scalability

REQ-8: Similar Topology Handling

REO-9: Adaptive Training

REQ-10: Model Extendibility

REQ-11: Operational Environment Compatibility

of a new subblock requires the adaptive training mentioned in REQ-9. Thus, a model that does not fulfill REQ-9 cannot satisfy REQ-10. Regarding REQ-11, the compatibility with prevalent EDA tools or platforms is not mentioned nor discussed.

By applying the same judgment on all other related references that performed analog circuits' structure recognition, Table 1 has been filled, and the justifications of each of the answers posted in Appendix C.

# IV. GENERAL METHODOLOGY FOR REALISING OUR STRUCTURE RECOGNITION PIPELINE

In this paper, we develop and validate a robust novel neural ML model to solve the analog circuits' structure recognition problem. Our overall pipeline assumes that the analog circuit to be clustered will be available as a SPICE netlist, as Cadence Virtuoso is the tool used in analog circuits engineering processes. Cadence Virtuoso can produce a description of the circuit entity (the schematics in Cadence Virtuoso) in a text form called "netlist". Thus, a parser is needed to interpret the netlist and build out of it a "graph model" describing the circuit's entities and how they are interconnected. This graph model, the output of the parser, is the one to be processed by a graph attention neural network based node classifier model.

The parser, in its essential role of processing the netlist and generating a graph model, is fundamentally reliant on a comprehensive ontology. This ontology encompasses various aspects, including how to appropriately represent each component of the analog circuit within the graph model. Moreover, the challenge extends beyond determining the representation of individual electronic elements (e.g., 3-pin transistors, 5-pin transistors, diodes, passives like resistors, capacitors, inductors, etc., as well as nets) within the circuit, and encompasses defining how to articulate the distinctive characteristics associated with each of these elements.

The comprehensive ontology is the foundation of the pipeline. Table 2 shows the most common primitives that can be found in a schematic. Nevertheless, passive elements are not considered for the proof of concept of this paper and can be considered in a later generalized approach. In this paper we chose to use solely transistors and represent each of them with several nodes: Transistor NMOS-1 ((3ports, 3 nodes)), Transistor PMOS-1 ((3ports, 3 nodes)), Bipolar Transistor ((3ports, 3 nodes)), and Nets (1 node) for our proof of concept case-study in this paper.

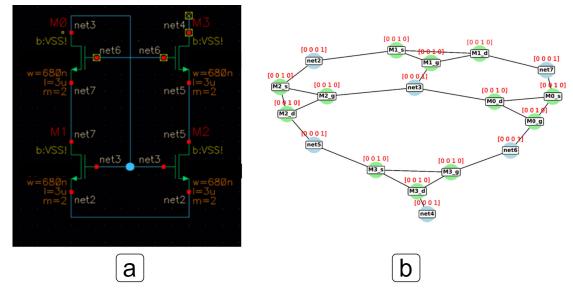

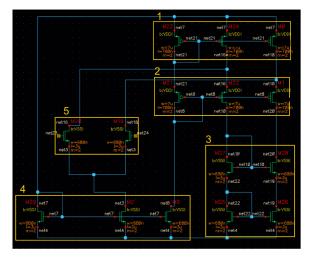

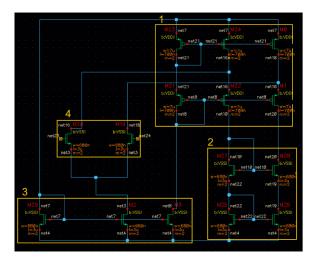

Figure 2.a displays a schematic illustrating a Level L2 circuit constructed using the Cadence Virtuoso design tool. In Figure 2.b, you can observe an equivalent graph, where each transistor is denoted by three nodes, while each net is symbolized by a single node. For instance, the transistor M0 is indicated by nodes M0s, M0g, and M0d, and it is linked to net7, net6, and net3, respectively.

In circuit design and modeling, a netlist is a description of the structure and connectivity within an electronic circuit. Indeed, a netlist is a list of all the components and inter-connections in an electronic circuit which define the electrical connectivity and relationships between components. The netlist includes information about components such as transistors and diodes, as well as passive elements like resistors, capacitors, and inductors, including their electrical characteristics and connections to other compo-

FIGURE 2. a. A schematic representing one illustrative L2 circuit (i.e. an analog circuit of level 2) and exported from the Cadence Design tool as a netlist b, the equivalent graph where each one of the transistors is represented by three nodes, and each net is represented by one node.

| Primitive name                | Number of representing graph nodes |

|-------------------------------|------------------------------------|

| Transistor NMOS-1 ((3ports))  | 3                                  |

| Transistor NMOS-2 ((5ports))  | 5                                  |

| Transistor PMOS-1 ((3ports))  | 3                                  |

| Transistor PMOS-2 ((5ports))  | 5                                  |

| Bipolar Transistor ((3ports)) | 3                                  |

| Diode                         | 2                                  |

| Resistor                      | 2                                  |

| Inductor                      | 2                                  |

| Capacitor                     | 2                                  |

| Voltage Source                | 2                                  |

| Current Source                | 2                                  |

| Nets                          | 1                                  |

TABLE 2. Primitives which can be found in schematics and the number of needed nodes to represent them in the graph domain.

nents. In an analog circuit netlist, passive elements like resistors, capacitors, and inductors are represented by their electrical properties and connections. The netlist includes information about the value and type of each passive element, such as the resistance value of a resistor, the capacitance value of a capacitor, or the inductance value of an inductor. The netlist also specifies the connections between each passive element and other components in the circuit.

Similarly, transistors are represented by their electrical properties and the connections between their three (or more) terminals. The netlist may specify the type of transistor, such as NPN or PNP or NMOS/PMOS, and provide information about the transistor's electrical characteristics such as the maximum current rating and the voltage gain. The netlist also defines the connections between the transistor and other components in the circuit.

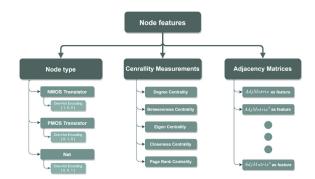

Figure 4 shows all the tested features (i.e. features finally selected to be useful after extensive tests) in order to represent the nodes in the best way possible. However, the one-hot

| TABLE 3.   | Four unique types of elements are considered for this |

|------------|-------------------------------------------------------|

| clustering | problem.                                              |

| Node Type   | Feature Vector |

|-------------|----------------|

| BIPOLAR     | [1000]         |

| NMOS [CMOS] | [0 1 0 0 ]     |

| PMOS [CMOS] | [0 0 1 0 ]     |

| N-Net       | [0 0 0 1 ]     |

FIGURE 3. The tested node features of the equivalent graph are one-hot encoding, the centrality features, and the adjacency matrices features.

encoding features were sufficient to reach the needed high accuracy.

For this problem, we consider four unique types of elements, and we chose one-hot-encoding to represent them as shown in Table 3. These encodings are used to constuct the feature matrix as each one of them is the feature vector for the node it represents.

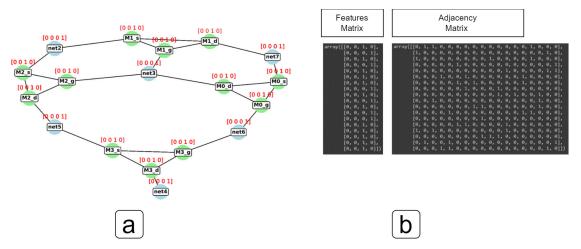

Figure 3.a is the schematic's equivalent graph (of the circuit displayed in Figure 2.a) and it is represented in Figure 3.b by its related adjacency matrix and features matrix. The chosen features (at the end, found to be the best and sufficient),

besides the adjacency matrix, are the one-hot encoding for both transistors and nets (see Fig.3).

The structure recognition concept suggested in this paper is centered around a comprehensive ontology, machine learning techniques, and a spatial graph neural network processor. Figure 5 describes the overall system pipeline architecture suggested in this work. Here, the input analog circuit's schematic is first exported as a netlist in Cadence virtuoso. Then, a parser that we have developed, integrating the knowledge provided by the comprehensive ontology described above, converts the netlist file into a graph model comprising an adjacency matrix and a feature matrix.

Furthermore, the graph model is used as an INPUT of a graph attention neural model GAT model, which shall cluster (after training) the analog circuit sample (represented by the corresponding input graph model) into the building subblocks contained that corresponding analog circuit.

A GAT neural model is indeed an excellent choice compared to other types of graph neural networks and various other machine learning tools. A Graph Attention Network (GAT) is a specific type of graph neural network that effectively models the structure and relationships between components in a circuit. GATs can learn to focus on different components and connections in a circuit, capturing complex dependencies and interactions among them. GATs are particularly well-suited for recognizing the structural patterns in analog circuits, as they can handle variable-size inputs and capture the hierarchical structure of circuits. For example, a GAT can learn to attend to individual components and their connections, and then aggregate this information to make higher-level decisions about the circuit's overall structure. Compared to other types of graph neural networks, such as graph convolutional networks (GCNs), GATs have several advantages for the task of analog circuit structure recognition. First, GATs can handle variable-sized graphs, while GCNs require fixed-size inputs. This is important because the size of an analog circuit can vary greatly depending on its complexity, and GCNs would require padding or truncating the inputs to a fixed size. Second, GATs can capture long-range dependencies in a circuit more effectively than GCNs.

This is because GATs use attention mechanisms that allow the network to learn to attend to different components and connections in the circuit, regardless of their distance from each other. In contrast, GCNs typically only capture information from a node's immediate neighbors. In a previous work [25], we did use GCN for solving a circuit classification problem and could see and feel this limitation of GCNs.

In summary, a graph attention network is a good choice to solve the structure recognition problem of analog circuits because it can handle variable-sized inputs, capture long-range dependencies, and is robust to noise and variability in the circuit components. These advantages make GATs a powerful tool for solving this challenging problem.

#### A. PROOF OF CONCEPT SCENARIO

This work addresses a structure (subblock) recognition problem for analog circuits. Contrary to some most prominent related work which involved some unsupervised learning components, in this work our approach to solve this problem based fully on supervised learning. This our approach is centered around a graph attention network GAT. This requires, amongst others, an appropriately labeled dataset for proper training. The dataset used in the proof of concept is comprehensively explained in Section V.

In view of the very comprehensive Specification Book presented (see requirements engineering: RQ-1, up to RQ-11) in Section II above, the best model to tackle the challenging endeavor addressed in this paper should fulfill satisfactorily the formulated 11 requirements. In the following, we briefly explain, from a philosophical and conceptual perspective, why and how far our concept developed/suggested in this paper will/does fulfill almost all of the 11 tough requirements of the specification book; this underscore how far it does significantly enrich the related state-of-the-art:

- Consider REQUIREMENT-1 A comprehensive protocol showing how an accuracy of 100% can be reached for all known subblocks within analog circuit, eventually progressively: this paper shows and demonstrate that our concept does fully satisfy this requirement as shown in section VIII.

- 2) Consider REQUIREMENT-2 A high robustness w.r.t. topology/architecture variations within circuits/subblocks having the same label: this paper clearly demonstrates, through the proof of concept study, that this requirement is fully satisfied as shown in section VIII.

- Consider REQUIREMENT-3 A high robustness to variations involving different transistor types: this paper clearly demonstrates, through the proof of concept study, that this requirement is fully satisfied. See section IV-C1.

- 4) Consider REQUIREMENT-4 A high robustness to most pervasive real-world imperfections of the training datasets, namely w.r.t. limited dataset size, and strong dataset unbalance: this paper clearly demonstrates, through the proof of concept study, that this requirement is fully satisfied. See Section VII.

- 5) Consider REQUIREMENTS-5 Applicability of the concept (structure recognition model) of this paper to all levels (from the lowest to the highest ones) of analog circuits IPs (intellectual property): this paper has a dedicated sub-section that explains thoroughly, at a conceptual level, how the ontology and the comprehensive protocol of this paper can be applied, after respective simple adaptations, to all layers of an industrial IP stack of analog circuits (i.e. mixed signal circuits). We have called this requirement "vertical scaling". For a multi-level analog circuit (e.g.., a circuits covering the levels 1, 2, 3, and 4, a straightforward procedure is to organize the clustering of subblocks structures

# IEEE Access

FIGURE 4. The schematic equivalent graph is represented by the adjacency matrix and the features matrix. The chosen feature are the one hot encoding for the used transistors and nets.

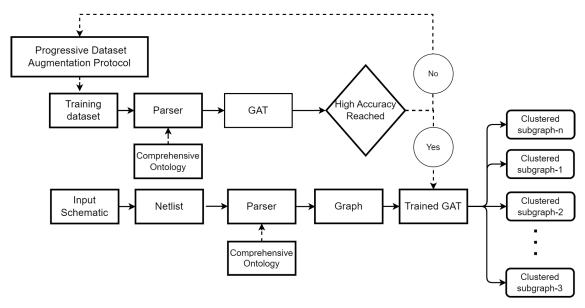

FIGURE 5. Overall system pipeline of the developed Analog Circuit clustering GAT-based system: The progressive dataset augmentation protocol is applied to the training dataset, which is transformed into the graph domain using a parser that considers a comprehensive ontology until high accuracy is reached after performing the needed iterations. When the GCN model is trained, each test schematic is fed to the final pipeline as follows; An input schematic is exported as a netlist by cadence Virtuoso and then converted to a graph model through a parser we have developed. Then, the equivalent graph model is fed into the trained GAT to be clustered into subgraphs. Each one of these subgraphs represents an analog subblock.

in steps, level-to-level, from the lowest to the highest level. This lastly described procedure may be justified by the fact that the analog circuit's schematics is generally (if not always) provided in form of a level-0 circuit. Another possible/alternative procedure is to identify at once the hierarchical structure, covering all four of the analog circuit. The concept presented in this paper, as it is centered around a GAT model, can also be adapted (w.r.t. to both ontology and protocol) and accommodated to implement this named alternative procedure for detecting the hierarchical structure. A justification for this capability is the fact that GATs are particularly suited for the structure recognition problem of analog circuits as they can knowingly handle variable-size inputs and can capture the hierarchical structure of analog circuits.

6) Consider REQUIREMENT-6 - A comprehensive representation, i.e. comprehensive ontology, for all basic electronic components and all subblocks at all levels of the analog circuits' hierarchy where the transistor in all subblocks of higher levels must be represented by three nodes. As already indicated in the comments above on REQ-5, this requirement is fully satisfied in the work presented in this paper.

- 7) Consider REQUIREMENT-7 A scalability of the model w.r.t. the size of the input analog circuit to be analyzed. As already indicated in one of the comments above, the GAT model, which is central piece of our model and concept, can knowingly handle variable-size inputs. This is an important capability of high practical relevance. Thus, the concept suggested in this paper does fully satisfy this requirement.

- 8) Consider REQUIREMENT-8 Capability to perform well, even when there are multiple sub-circuits with similar topologies in the input circuit. This is a very tough requirement that most related works fail to solve. But the case study presented in this paper, proofconcept, shows experimentally that our concept and the model therein does fully solve this requirement too.

- 9) Consider REQUIREMENT-9 Capability for the model to be progressively (extended/tuned) trained to improve performance through a supervised learning process: this paper has a dedicated subsection where the innovative protocol/methodology is comprehensively presented, which solves this concern with full satisfaction, as also demonstrated by the different relative performance results. Thus, this requirement is also fully solved in this paper.

- 10) Consider REQUIREMENT-10 Capability for the model to be progressively (extended/tuned) trained to integrate new (previously not considered in the previous/current GAT model training) subblock (s) through a supervised learning process: in this paper, a dedicated sub-section, where a comprehensive conceptual protocol is presented to solve this issue. We have called this requirement "horizontal scaling". Thus this requirement is also fully solved in this paper. See Subsection VII-D.

- 11) Consider REQUIREMENT-10 (Operational Environment Compatibility): our model is compatible with prevalent EDA (electronic design automation) tools and platforms. It is efficient enough for real-time or near-real-time operations during circuit design processes.

B. HIERARCHICAL STRUCTURES AND LEVELS DEFINITION

In Analog/Mixed-Signal (AMS) design, abstraction is the process of hiding the details of a design at one level of representation in order to simplify the description of the design at a higher level to enable the designer to access the functionality of the design more than the details of the implementation. There are three levels of abstraction in AMS design: circuit level, behavior level, and system level. As the lowest level of abstraction, circuit-level abstraction is concerned with the physical implementation of the concept. The designer focuses on the individual components and their interconnections at this level. As the lowest level of abstraction is concerned with the physical implementation of the concept. Behavior-level abstraction is the next level of abstraction and is concerned with the behavior of the

design. The emphasis is on the input- output behavior of the design rather than on the individual components. The highest degree of abstraction, system-level abstraction focuses on the overall behavior of the system. At this stage, the designer concentrates on the system as a whole instead of on its constituent parts. The focus is on system-level behavior rather than implementation particulars [26]. This work focuses on the circuit level, which has several entities inside. Every circuit can contain a hierarchy which helps in understanding the model.

Analog circuits are often designed with hierarchical structures in order to improve performance and/or reduce/handle complexity. In a hierarchical structure, a circuit is divided into smaller subcircuits, each of which performs a specific function. The subcircuits are then interconnected to form the overall circuit. The hierarchical structure of an analog circuit is a top-down approach, where the circuit is divided into smaller and more manageable blocks. This approach is often used in the design of integrated circuits (ICs). In this approach, the overall circuit is first divided into major blocks, and each block is further divided into smaller subblocks. This approach allows the designer to focus on each block separately and then integrate them together. This results in a more efficient design process and a higher-quality circuit [27]. The most common type of hierarchical structure is the two-level hierarchy. In this structure, the overall circuit is divided into two major blocks: the upper level and the lower level. The upper level contains the more complex blocks, while the lower level contains the simpler blocks.

Another type of hierarchical structure is the three-level hierarchy. In this structure, the overall circuit is divided into three major blocks: the upper hierarchy level, the middle hierarchy level, and the lower hierarchy level. The upper level contains the more complex blocks, while the middle level contains the less complex blocks. The lower level contains the simplest blocks. The fourth type of hierarchical structure is the multi-level hierarchy. In this structure, the overall circuit is divided into two major layers/levels: the upper level/layer and the lower level/layer. The upper level contains the more complex blocks, while the lower level contains the simpler blocks. Another type of hierarchical structure is the threelevel hierarchy. In this structure, the overall circuit is divided into three major blocks: the upper hierarchy level, the middle hierarchy level, and the lower hierarchy level. The upper level contains the more complex blocks, while the middle level contains the less complex blocks. The lower level contains the simplest blocks. The fourth type of hierarchical structure is the multi-level hierarchy. In this structure, the overall circuit is divided into multiple levels, each containing a different level of complexity.

Using a hierarchical structure in analog circuits has numerous advantages. First, it can improve the performance of the circuit by allowing each subcircuit to be optimized for its specific function. Second, it can raise the circuit's complexity without increasing the circuit's number of components or its size. Lastly, it might make testing and debugging the circuit

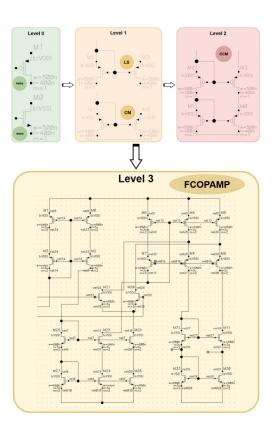

**FIGURE 6.** Example for the three levels of the hierarchy of analog/mix signal circuits IPs.

easier. There are some trade-offs to using a hierarchical structure in analog circuits. First, it can make the circuit more difficult to design and understand. Second, it can increase the cost of the circuit due to the need for more components and/or higher-quality components. Finally, it can make the circuit more sensitive to environmental changes (such as temperature or humidity). Despite the trade-offs, hierarchical structures are often used in analog circuits because the benefits can outweigh the costs.

In this work on analog circuit structure recognition, it was a must to define the levels of the schematics in order to cluster from it the subblocks of the lower level correctly. As mentioned, every block in analog design could be a building block of another more significant building block (of a higher level), which may be confusing for an AI based recognition model.

In this paper, as shown in Figure 6, The very lowest level basic building blocks of the analog circuit are transistors, which could be (PMOS, NMOS, or Bipolar), and all passives are neglected for this proof of concept stage. Every number of transistors, according to how they are interconnected, can form some groups of specific block(s). Those blocks are unique from the interconnections between the transistors inside the block. For example, as shown in Figure 6, transistors M0 and M1 are forming the current mirror (CM). Transistors M2 and M3 form another block, the level shifter (LS). In addition, other blocks may be formed out of two transistors, such as differential pair (DP), voltage

reference (VR), current mirror load (CML), and flip-flop (FF). Those blocks contain some transistors as a lowest-level building blocks; we consider them as level 1 and the transistors level as level 0. The same idea related to the relation from level 0 to level 1 applies to level 1 to level 2. We can see that level 1 blocks can build higher levels of blocks too. For example, CM and LS form the cascode current mirror (CCM), and VR and CML form the 4-transistor current mirror (4TCM). Typically, other level 2 blocks can be formed, such as the Wilson current mirror (WCM), the improved Wilson current mirror (IWCM), and the wide swing cascode current mirror (WSCCM). After level 2 blocks are defined, combinations of the level 2 blocks can construct level 3 blocks, such as the folded cascode operational amplifier (FCOPAMP), the operational amplifier (OPAMP), the transconductance amplifier (OTA), and the Buffer amplifier (BAMP). The AMS circuits could contain many levels until they reach the IP level. Every block of level i - 1 is (may be) a building block of a level-*i* block. Figure 6 provides an example of different levels and how every level builds up to a higher level. Level 0 shows two types of transistors (PMOS and NMOS) as the building blocks of the very lowest level of all the schematics. When we combine two (or more) transistors, we can have different types of level 1 blocks, for example, LS and CM. The LS and CM could be combined and increase the level to a higher level. The combination of LS and CM results in having the CCM. CCM is one block of many that combine schematics of level 3 and higher schematics. In this work we are using and considering different blocks from different levels to be clustered. We call level 1 and level 2 sub-schematics and level 3 as the level main schematic.

#### C. PREPROCESSING: THE PARSER

In this subsection, we answer a very important question of how to project a given circuit from schematic space to graph space. A parser was developed with the main task of providing a proper numerical representation (ontology) of a graph out of a given netlist representing the schematics.

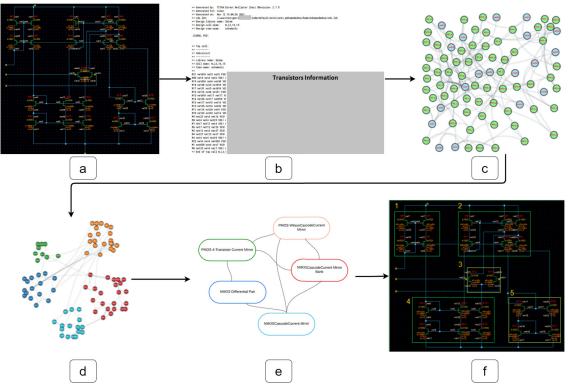

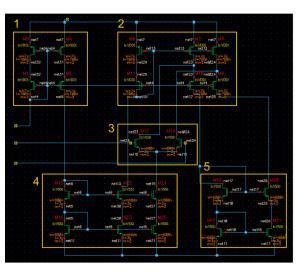

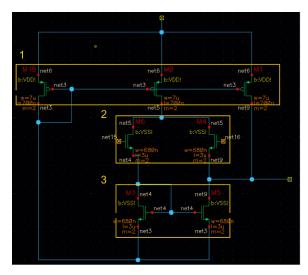

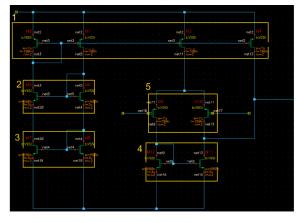

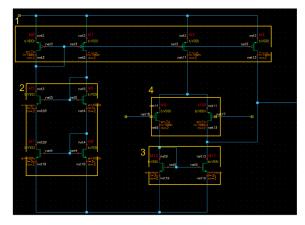

As shown in Figure 7.a, the input is a schematic representing the L2 circuit as exported from the Cadence Design tool as a netlist (See Figure 7.b), then the tool Net2Graph IV-C1 exports an undirected graph (See Figure 7.c) represented mathematically by both an Adjacency Matrix and a Feature matrix. Both matrices form the input of the graph attention network (GAT), the GAT model is comprehensively described in section VI, and the output is a clustered graph as shown in Figure 7.d and 7.e. This result can be visualized in the schematics domain as shown in Figure 7.f.

The parser reads and identifies the electronic elements and the so-called "nets" from the Netlist and generates a graph model with nodes and edges based on the connection provided by the Netlist. This yields an equivalent graph model that adequately describes the original circuit. The equivalent graph is represented by the graph's adjacency matrix and

FIGURE 7. a. the input is schematic representing the L2 circuit and exported from the Cadence Design tool as a netlist b, then the tool Net2Graph exports an undirected graph c represented mathematically as Adjacency and Feature matrices. Both matrices are the input of the graph attention network GAT, and the output is clustered graph as shown in figure d and e. This result can be visualized in the schematics domain as shown in f.

features matrix. A sequence/series of properties of each of graph nodes is described in an appropriate coding in the feature matrix. The feature matrix, for example, specifies whether a node is a net or an electronic element or a part of an electronic element (Since transistors are represented by 3 nodes in this work). The precise type of electronic element is also coded. The GNN (specifically GAT) model is fed by the two matrices: the adjacency matrix and the feature matrix.

#### 1) NET2GRAPH

As described in IV-B, we define three levels for graphs in this work. "Basic building blocks" are represented in level-1 graphs, "functional building blocks" are represented in level-2 graphs, and "modules" are represented in level-3 graphs. The parser Net2Graph was developed to recognize level 1 within a level 2 schematics and to scale it to higher levels. The parser also considers a "label file" depending on the requirements of the experiments. For each netlist and label, the parsed output consists of the following elements:

- Adjacency matrix A: describes the connectivity of the graph nodes.

- Feature matrix X: contains the node features of the graph.

- Labels *L*: vectors of labels: each node has a label that identifies the class of subblocks that it belongs to.

• Graph object *G*: a networkX Python object that contains all the information (graph related information, connectivity information) from the netlist.

The algorithm used to convert the netlist to graphs is described in Appendix A

#### V. DATASET COLLECTION, TRANSFORMATION, AND PREPROCESSING

To train the GAT model to be used for structure recognition we need an appropriate dataset.

#### A. DATASET COLLECTION

Designs for analog/mixed signals originated from a vast body of knowledge that expands daily. Schematics for this proof of concept work were collected from the relevant literature in the field. These schematics cover a variety of levels, each with its unique functionality and distinct architectural approaches to the same functionality. The dataset was collected in PMOS, NMOS, and BIPOLAR transistors, the three most common types. The collection of datasets is carried out in a very structured manner by using a container file, which is used to store the gathered schematics, and by categorizing these schematics according to the different levels and types of transistors.

The dataset uses the ID labeling strategy to organize the data more logically. The ID of every sample shows the information needed to be known about the samples collected.

The form of labeling is **[Transistor type, Schematic level, Schematic type No., Schematic of the same type No., Schematic name, subschematic name]**. For example, **[N, L1, 1, 1, FCOPAMP1, CCM]**. The ID labeling strategy allowed all users involved in the project implementation to explore the collected data. In addition, the strategy of ID labeling is helpful in the statistics of the data, as well as for the completeness, diversity, and comprehension of the data. In addition, the first step toward understanding the common structures of analog schematics and defining the levels of those structures to have powerful AI/ML model models trained on these data.

#### B. DATASET TRANSFORMATION AND ANNOTATION

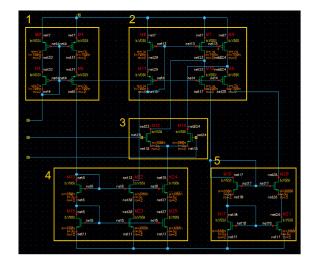

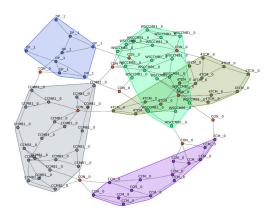

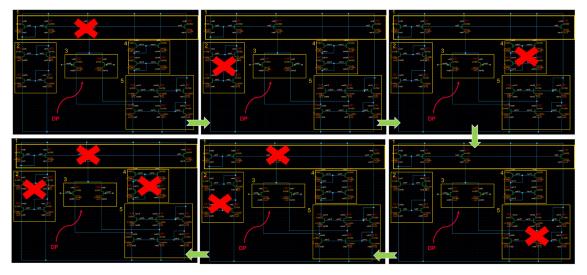

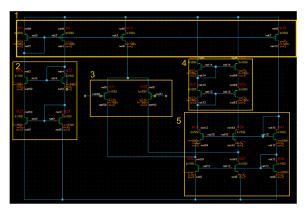

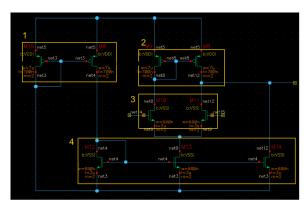

The collected data provide valuable insights into the design of analog/mixed signals. The next step was implementing these collected schematics on the standard design software Cadence Virtuoso. Since the collected data are many and in different levels, types, and transistor technologies, only 8 level-3 schematics, listed in Table 4, have been chosen to perform structure recognition (in the proof of concept prototype). Those 8 Samples are in level 3, with ten different level 2 subschematics inside. The eight samples are real-world circuits that are commonly used in analog design. In addition, eight samples are in NMOS and PMOS transistor types, which helps with the diversity of data. ID labeling was a valuable technique in dataset drawing as it improved the implementation organization and the naming system. Cadence Virtuoso software is a circuits CAD software with various entities, allowing you to use different technologies in the software libraries. The software is so user-friendly as it enables connecting the (transistors) used together by a connection line called (net). The naming of transistors and nets is done automatically and in an organized way. After sorting and defining the schematics level, all eight schematics with their subschematics were implemented in Cadence with a specific transistor industrial library. Analog/mixed signals schematics contain subschematics of common structures with different functionalities, different transistor numbers, and connections between transistors and every group of transistors sets up a structure. With a slight change in the connection between transistors, it can set up another structure/subschematic. For dataset understanding and analysis, all common subschematics are annotated using yellow boxes around the groups of transistors and nets as shown in Figure 8. Every box is numbered and described according to the type of schematics. The annotation is done for the eight chosen schematics. This annotation has the advantage of giving a better visualization of the structures and is a good step toward labeling the dataset components.

Figure 8 demonstrates an example of FCOPAMP1 annotation of subschematics and how it may be used within the context of the main schematic. The annotation was purposefully abstract so that readers would have a better understanding of analog structures and improved statistical capabilities. **TABLE 4.** schematics list: The schematics which will be the input for asnalog circuit structure recognition to find their subschematics in an automatic way.

| Schematic name                           | Subschematics number |

|------------------------------------------|----------------------|

| Folded Cascode Operational Amplifier 1   | 5                    |

| Folded Cascode Operational Amplifier 2   | 5                    |

| Folded Cascode Operational Amplifier 3   | 5                    |

| Folded Cascode Operational Amplifier 4   | 4                    |

| Operational Transconductance Amplifier 1 | 3                    |

| Operational Transconductance Amplifier 2 | 4                    |

| Operational Amplifier 1                  | 5                    |

| Operational Amplifier 2                  | 4                    |

FIGURE 8. Folded Cascode Operational Amplifier Annotation: the nodes and the connecting nets in this analog circuit are gathered into on of the following groups: 1. 4-Transistor Current Mirror, 2. Wilson Cascode Current Mirror Bank 1, 3. Differential Pair, 4. Cascode Current Mirror Bank 1, and 5. Cascode Current Mirror.

In addition to this, the annotation highlights the area on the targeted structures that will be clustered afterwards.

#### C. DATASET LABELING

Data labeling is an essential part of the data preparation phase for machine learning, especially supervised learning. To establish a learning foundation for further data processing, supervised learning uses data that is labeled to establish a correspondence between the input and output forms [28]. Machine learning (ML) and deep learning (DL) require rich data to learn reliably. Information for their training techniques must be labeled to organize data and identify trends. Accurate algorithms require informative, selective, and individual feature labels [29].

The implemented dataset consists of transistors and nets, and the application of supervised learning requires labeling for each component we have. Manual labeling has been tried, but faces serious challenges such as labeling errors and time consumption, as well as lack of improvement, scaling limitations, and low support for generalization.

Given all the challenges mentioned earlier, a novel **Automatic Labeling** (AL) algorithm was implemented and improved. The primary concept of Automatic Labeling (AL) is to iterate at the netlist level to map the transistor names

and net names. These names are grouped and show the group number of their structure/sub-schematics and the class names of every component in a .label file. Since the netlists of the main schematics and sub-schematics are in one container file, a generic Python algorithm maps the transistor instances from the subschematics and groups them according to the file naming, which provides the group number and class name. Subschematics were cut from the main schematic, so net names changed when generating a new netlist for new schematics. Both transistor and net instances were hard to map from the main schematics. A new methodology was developed to solve this problem. It allows us to simultaneously operate on main and subschematics files and provides a robust and efficient labeling system for analog/mixed Signals schematics. Automatic Labeling only accepts main and subschematic netlists with the same naming protocol. The Python code works on every netlist, and the first step is to match the technology, as every transistor is different. After matching, the parser splits netlist lines. All transistors in a sub-schematics netlist are grouped and saved in a dictionary with the group number and the class name. For the net name change challenge, grouped transistors are mapped in the main schematics to get the connections for each transistor and add them to the group. The final step is to generate a .label file with all transistors, three nodes (drain, gate, and source), nets, and connections with class names and group number.

# D. DATASET AUTOMATIC LABELING USE CASES AND IMPROVEMENTS

Automatic Labeling (AL) is a valuable step for automating analog-circuits-related applications of AI. AL enables us to label main schematics and sub-schematics in two seconds instead of one hour without needing to read the schematics. AL is used through the project flow in different applications, and since it is "automated," it was not a trivial task to adapt it for different cases. For instance, when we want to detect a specific sub-schematics within a schematics or what we call "one vs. all" structure recognition, the group numbers in the labels were not used. Instead, every sub-schematics was activated once, and all other sub-schematics were deactivated. For each activation iteration, the model's target block was the activated block. In other words, the targeted block was activated or deactivated using "1" or "0" to provide the model with further information about the sub-schematic within the main schematic that was targeted. The flexibility of the automatic labeling did not stop here; it also improved and became able to remove the labels of the targeted sub-schematics once the model detects it and start iterating on the other sub-schematics doing the same procedure again and having the new schematics activating other targeted sub-schematics. Last but not least, AL was adaptable to target one class within all the schematics and activate it in the improved version of "one vs. all." For example, during one of the initial tuning steps, a differential pair (DP) was selected to be clustered among all sub-schematics and to achieve this, AL has been configured to activate only the selected sub-schematics.

Automatic labeling is thus a precious building brick for all automation processes in the area of analog/mixed signals design and verification automation. In addition, automatic labeling for the dataset has allowed us to go further in the project, specifically for designing and realizing a novel automatic dataset augmentation method.

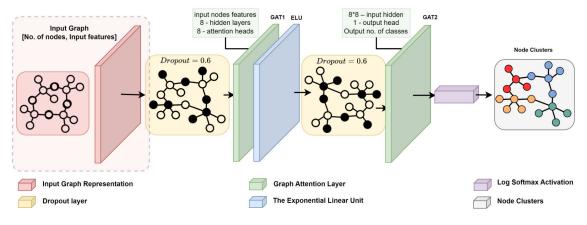

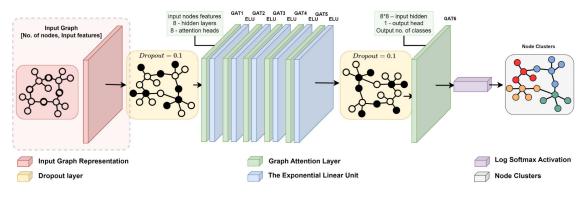

# VI. A ROBUST GAT BASED MODEL FOR STRUCTURE RECOGNITION: DESIGN AND VALIDATION

### A. INTRODUCTION AND BACKGROUND

A novel neural network architecture called GAT (Graph Attention Network) uses masked self-attention layers to overcome the drawbacks of previous GNN approaches based on graph convolution or its approximations. It works with graph-structured inputs. The model allows (implicitly) specifying different weights for different nodes in a neighborhood without requiring any expensive matrix operation (such as an inversion) or knowing the graph structure in advance by stacking layers where nodes can attend to the features of their neighborhood. In this way, GAT simultaneously overcomes many of the main problems of so-called spectral-based neural graph networks [30] and makes the model easily adaptable to inductive and transductive applications.

GATs were first proposed in the paper "Graph Attention Networks" by *Veličković et al.* [31]. In a GAT, each node in the graph is assigned a "hidden state" vector. The hidden state vectors are then used to compute attention weights, which are used to determine how much each node should be "attentioned" to by the network. The hidden state vectors and attention weights are then used to compute a final node representation, which can be used for various downstream tasks such as classification or link prediction. GATs are similar to other neural networks, such as convolutional neural networks (CNNs) and recurrent neural networks (RNNs). However, GATs are explicitly designed for graph data. This makes them more efficient and effective at learning from and making predictions on graph data.

GATs are built on the idea of self-attention, which was introduced by [32]. The Transformer paper showed that self-attention is an effective way to learn representations of data. GATs use self-attention to learn representations of graph data. A self-attention layer of a neural network selectively processes data, focusing on what's important while ignoring the rest. Self-attention is well-suited for learning from graph data because graphs are often highly structured and have many relationships between the data points.

GATs are composed of two layers: an attention layer and a feed-forward layer. The attention layer is where the self-attention mechanism is applied. The attention layer consists of a series of attention heads. Each attention head attends to a different part of the graph. The output of the attention layer is fed into the feed-forward layer. The feed-forward layer is a standard neural network layer that transforms the input data into a new representation. The output of the feed-forward layer is the final representation learned by the GAT. GATs can be trained using standard neural network techniques, such as backpropagation. GATs have been shown to outperform traditional graph neural network architectures on a variety of tasks, such as node classification [33] and link prediction [34], [35]. Additionally, GATs are computationally efficient, making them well-suited for large-scale graph data.

Graph Attention Networks (GATs) [31], and Graph Convolution Networks (GCNs) [20] are both types of neural networks that can be used for learning on graph-structured data. However, there are several critical differences between GATs and GCNs [36], [37]. GATs are designed to operate on a self-attention mechanism, whereby each node attends to all other nodes in the graph to compute its representation. This contrasts with GCNs, which use a neighborhood aggregation scheme where each node only attends to a limited number of neighbors. Another key difference is that GATs use multi-head attention to allow for different node representations to be learned in parallel. GCNs typically use a single attention head. Moreover, GATs are typically trained using a masked self-attention objective, which encourages the model to focus on local structure. GCNs are typically trained using a node classification objective, which can encourage the model to learn global structure. Finally, GATs can be applied to graphs with arbitrary node connectivity, while GCNs require the graph to be locally connected.

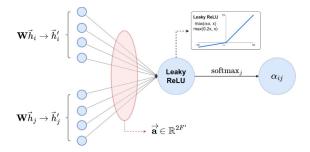

Instead, self-attention is used over the node characteristics and let the attention scores  $\alpha_{ij}$  be implicitly specified. This decision was not made arbitrarily, as the Transformer design has already proven self-attention to be sufficient for state-ofthe-art outcomes in machine translation [32].

#### **B. MATHEMATICAL MODEL**