Received 8 December 2023, accepted 14 January 2024, date of publication 6 February 2024, date of current version 6 March 2024. Digital Object Identifier 10.1109/ACCESS.2024.3362910

# **RESEARCH ARTICLE**

# An Active Track and Hold Circuit With Linearity Enhancement Technique and Its Analysis Using Volterra Series

JUNYOUNG JANG<sup>(1),2</sup>, GEUNHAENG LEE<sup>(1)3</sup>, AND TAE WOOK KIM<sup>(1)</sup>, (Senior Member, IEEE) School of Electrical and Electronic Engineering, Yonsei University, Seoul 03722, South Korea

<sup>1</sup>School of Electrical and Electronic Engineering, Yonsei University, Seoul 03722, South Korea

<sup>2</sup>System LSI Business, Samsung Electronics, Hwaseong 18448, Republic of Korea

<sup>3</sup>Department of Electronic Engineering, Andong National University, Andong 36729, Republic of Korea

Corresponding author: Tae Wook Kim (taewook.kim@yonsei.ac.kr)

This work was supported by the Institute of Information and Communications Technology Planning and Evaluation (IITP) Grant funded by the Korean Government (MSIT) under Grant 2017-0-00418.

**ABSTRACT** This paper presents a comprehensive analysis of active track and hold (T/H) circuits that utilize switched source followers and time-divided post-distortion cancellation. In the track phase, the circuit acts as an active buffer and transfers an input signal, including track-mode distortion caused by the buffer's nonlinear transconductance. In the hold phase, the transferred signal is held but hold-mode distortion is added, including hold-mode feed-through and hold pedestal error, causing deterioration of the circuit's linearity. The time-divided post-distortion cancellation technique improves the circuit's linearity by cancelling the track-mode distortion with the hold-mode distortion. Volterra series analysis offers a comprehensive understanding of the operation. 17 sample chips were measured to verify stable cancellation operation. It shows a mean SFDR value of 77.1 dB and a standard deviation of 1.8 dB with 9mW power consumption.

**INDEX TERMS** CMOS, track and hold, RF sampling, source follower, Volterra analysis, distortion cancellation.

#### I. INTRODUCTION

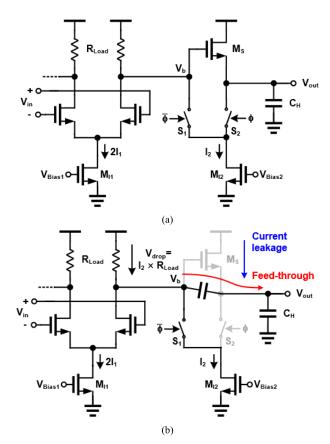

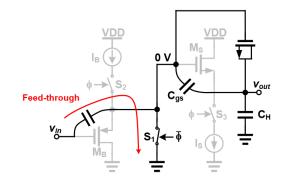

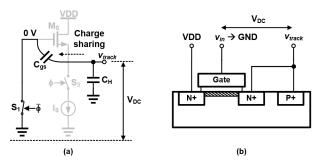

Interest in high-speed time interleaved (TI) ADCs has risen as they have the potential to reduce the complexity, power consumption, and cost of the traditional receiver due to its wide band characteristic [1], [2], [3], [4], [5], [6], [7], [8], [9], [10]. Similarly, the use of front-end track and hold (T/H) circuits to drive TI ADC has gained attention [5], [6], [7], [8], [9], [10], [11], [12], [13]. With the rise in ADC speed and performance, demanding performance requirements are placed on T/H circuits [14], [15], resulting in various efforts to enhance their performance [6], [7], [8], [9], [10], [11], [16], [17], [18], [19], [20]. An active T/H circuit has benefits on speed, but it requires a design consideration for linearity issue [11], [21], [22]. As the active T/H circuit, studies on switched-buffer T/H circuits using an InP/SiGe HBT bipolar or CMOS process to perform charge-domain sampling exist [11], [21], [22], [23], [24], [25], [26], [27]. One of the popular T/H circuits is composed of a common-source amplifier as a pre-amplifier, a switched source follower (SF) as a buffer and a hold capacitor  $(C_H)$  shown in Fig. 1 (a). It performs charge-domain sampling, which offers improved speed [11], [21]. However, it has a drawback for the linearity. During the track phase, the switched SF transfers a signal to the hold capacitor as an SF. The output contains distortion from the nonlinear transconductance of the SF, which is called track-mode distortion. After entering the hold phase, the SF maintains the hold voltage at  $v_{out}$  by decreasing the voltage at the gate node (V<sub>b</sub>) as much as  $I_2 \times R_{load}$  and turning off the M<sub>S</sub>. This is achieved by switching the current path with the switch  $(S_1)$ , as shown in Fig. 1 (b). In the hold mode, hold-mode distortion occurs due to the track-to-hold transition and other hold-mode errors. To overcome the problem of hold-mode distortion, previous studies have been conducted on the linearization of switched-buffer or Switched SF T/H circuits. One technique is the cross-coupled capacitor approach to address the

The associate editor coordinating the review of this manuscript and approving it for publication was Chaitanya U. Kshirsagar.

**FIGURE 1.** (a) Diagram for the conventional active T/H circuit using switched SF and (b) its hold-mode diagram.

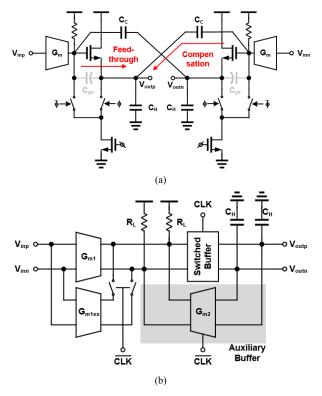

feed-through problem. This aims to reduce clock leakage to the hold capacitor [11], [26], [28]. Fig. 2 (a) shows an example circuit for this technique. Dummy capacitors  $(C_C)$ are used to compensate the feed-through from the gate-source capacitor  $(C_{gs})$  through a cross-coupled connection. Another technique is the mode-switching architecture. To avoid reliance on the matching of capacitors, mode-switching architectures have been proposed [28], [29]. Fig. 2 (b) shows the circuit diagram of this architecture. It uses an additional transconductance stage (G<sub>m1ex</sub>) connected to the load resistors (RL) during the hold phase. During this phase, the Gm1ex stage produces an opposing phase signal, canceling and reducing the signal transferred by the G<sub>m1</sub> stage. As a result, the transconductance stage operates in common mode and reduces the feed-through problem, but a matching issue still exists between G<sub>m1ex</sub> and G<sub>m1</sub>.

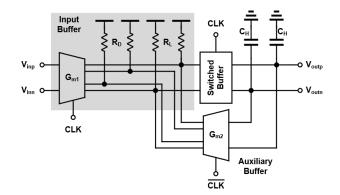

To reduce dependence on matching, the double-switching architecture was proposed based on the mode-switching architecture [18]. Fig. 3 shows the diagram of this architecture. It involves switching the buffer connection by directing the output between the actual load  $R_L$  and the dummy load  $R_D$  using switches. Since it does not require cancellation with an opposing signal, the  $G_{m1ex}$  stage is not necessary in this structure.

The time-divided post-distortion cancellation (TDPD) was proposed which can enhance the linearity of a switched

**FIGURE 2.** Schematic diagrams of the T/H circuit with the (a) cross-coupled capacitor technique [9], [24], [25] and (b) mode-switching architecture [25], [26].

FIGURE 3. Schematic diagram of the T/H circuit with double-switching architecture [18].

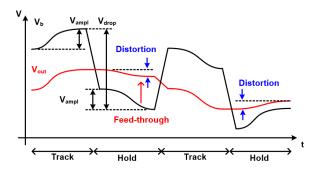

source follower T/H circuit [19]. The TDPD technique enhance linearity by canceling the track mode nonlinearity with the hold mode nonlinearity. The TDPD circuit acts as an active buffer and transfers an input signal, including track-mode distortion caused by the buffer's nonlinear transconductance in the track phase. In the hold phase, the transferred signal is held but hold-mode distortion is added, including hold-mode feed-through and hold pedestal error which deteriorate linearity in a conventional switched source follower T/H circuit. The TDPD improves linearity by cancelling the track-mode distortion from transconductance with the hold-mode distortion from the hold pedestal error while minimizing the hold-mode feedthrough.

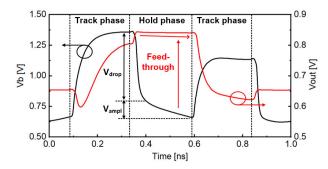

FIGURE 4. Timing diagram for V<sub>b</sub> and v<sub>out</sub> node of Fig. 1.

FIGURE 5. Simulation result for the hold-mode feed-through.

This paper aims to provide a comprehensive explanation of the TDPD T/H circuit with a mathematical analysis using Volterra series starting from the understanding of the track and hold mode behaviors of the switched source follower T/H circuit. Measurement results from multiple sample chips are provided to verify stable cancellation operation of the TDPD.

The remainder of this paper is organized as follows. Section II. discusses the behaviors and distortion of the switched source follower T/H circuit. Section III discusses the design of the TDPD T/H circuit. In Section IV, Volterra series analysis is performed for the equations for both the track-mode and hold-mode distortions. Further, the role of an additional MOS capacitor in the distortion cancellation is described. Section V presents the measurement results. Finally, Section VI presents the conclusions.

# **II. DISTORTION OF SWITCHED SOURCE FOLLOWER**

# A. HOLD-MODE DISTORTION (1): FEED-THROUGH

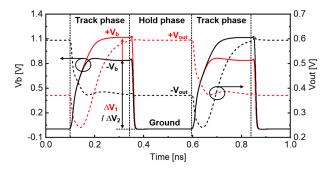

Hold-mode distortions were identified as a cause of poor linearity performance in the switched SF shown in Fig. 1. The first source of hold-mode distortion is hold-mode feedthrough. As shown in Fig. 4, it occurs due to changes in the input signal during the hold phase and becomes more pronounced as the signal frequency approaches the Nyquist rate. During the hold phase, a signal swing is induced at the V<sub>b</sub> node and approaches the peak amplitude (V<sub>ampl</sub>). Subsequently, the signal is transferred to the C<sub>H</sub> through the gate-source capacitance (C<sub>gs</sub>) of the M<sub>S</sub>. This results in the creation of a distortion that depends on the frequency and magnitude of the input signal. Fig. 5 illustrates the simulation

**FIGURE 6.** Timing diagram of differential  $V_b$  node (a) for transitioning to  $V_{CM}$  and (b) for decreasing as much as  $V_{drop}$ .

FIGURE 7. Simulation result for the hold pedestal error.

results of the V<sub>b</sub> and  $v_{out}$  nodes. When the input signal is close to the Nyquist rate during the hold phase, it alters the V<sub>b</sub> node, causing distortions in the  $v_{out}$  node. Studies have been conducted to address this hold-mode distortion problem, but they have drawbacks such as increased power consumption, complicated design, or limitations in performance due to matching properties [11], [21], [22], [26], [28], and [29]. Moreover, if the magnitude of V<sub>drop</sub> is insufficient to turn off M<sub>S</sub> completely, current leakage occurs in addition to feed-through, leading to further distortion. Therefore, a high voltage drop (V<sub>drop</sub>), which is the product of Is and R, is necessary to ensure complete turn-off of the M<sub>S</sub>, but this leads to high current consumption.

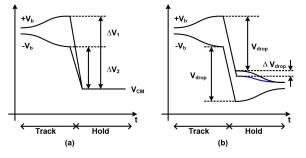

**B.** HOLD-MODE DISTORTION (2): HOLD PEDESTAL ERROR The next distortion is the hold pedestal error, which is caused by the voltage drop that occurs at the track-to-hold transition [20], [22].  $+V_b$  and  $-V_b$  in Fig. 6 indicate the differential signal at the  $V_b$  node in Fig. 1 (a). As shown in Fig. 6 (a), when the voltages of the two nodes decrease to the specific voltage ( $V_{CM}$ ) to turn off the SF, there are different voltage drops,  $\Delta V_1$  and  $\Delta V_2$ , depending on the input signal. These voltage drops affect the differential output differently through the parasitic capacitance between the  $V_b$  and  $v_{out}$  nodes. Previous studies have tried to make a constant voltage drop ( $V_{drop}$ ) independent of the input signal, as shown in Fig. 6 (b), utilizing the pre-amplifier's load resistor and current source. However, there are still the differences in  $V_{drop}$  ( $\Delta V_{drop}$ ) and the pedestal error due to the channel length modulation.

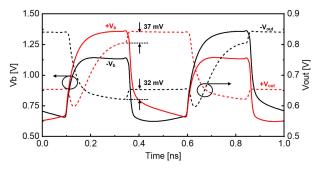

In addition, during the hold phase, the signal is not transferred to the output, but the pre-amplifier and current sources

FIGURE 8. Schematic of the TDPD T/H circuit.

still consume static current. This transfers the signal to the V<sub>b</sub> node and causes a feed-through problem. Fig. 7 shows the simulation results for this limitation. The difference in V<sub>drop</sub> between the +V<sub>b</sub> and  $-V_b$  nodes results in different effects on  $v_{out}$  at 37 and 32 mV. To generate a more constant V<sub>drop</sub>, there were studies [20], [22], at the cost of the current consumption during the hold phase.

Consequently, the first pre-amplifier stage exhibits design difficulties because it not only has a better linearity than the following SF stage, but also makes the specific voltage decrease and is affected by the signal leakage at the hold phase.

#### **III. TWO-STAGE SWITCHED SF T/H CIRCUIT**

This section explained the design of the TDPD T/H circuit and how it addresses the transition from track-to-hold mode and the distortion in hold-mode.

#### A. SCHEMATIC OF T/H CIRCUIT

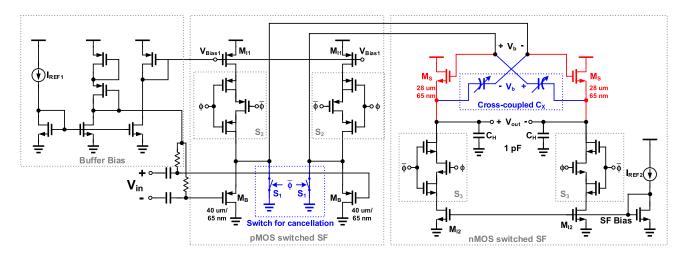

The TDPD T/H circuit based on a two-stage switched SF, as shown in Fig. 8, approached the problems in the hold phase from a different perspective. First, the pMOS SF was employed as the pre-amplifier instead of a common source amplifier to secure bandwidth and drive the subsequent nMOS SF. To start the hold phase, switches  $(S_{1-3})$  are activated to deactivate both M<sub>S</sub> by pulling down differential V<sub>b</sub> nodes and preventing the current from the source. This approach offers several benefits. Firstly, the circuit can be turned off simply with the switch architecture. The voltage drop is achieved using switches only, without the need for resistors or current sources, allowing for flexible design of the current and components in each stage. Secondly, there is no current consumption as the current sources are blocked. Lastly, this method reduces hold-mode feed-through, which will be discussed in the next section.

#### **B. HOLD-MODE FEED THROUGH**

As shown in Fig. 9,  $M_S$  has a negative gate-source voltage  $(V_{gs})$  generated by the hold capacitor  $C_H$  and the pull-down

FIGURE 9. Reduction of hold mode feed-though in the TDPD T/H circuit.

switch S<sub>1</sub>. The voltage of the current source I<sub>S</sub> results in negative V<sub>gs</sub> exceeding 300 mV even considering the input signal. Further, it suppresses the current leakage of the M<sub>S</sub> during the hold phase. Because the pMOS SF stage is turned off together, it helps alleviate the hold-mode feed-through problem with the parasitic capacitance of the M<sub>B</sub> and S<sub>1</sub>. The C<sub>gd</sub> capacitance serves as one of the load impedances for the pMOS source follower in track mode. However, C<sub>gd</sub> capacitance is relatively small (~20fF) compared to other load impedances like C<sub>H</sub> (1pF), resulting in a negligible effect on the pMOS source follower's operation at the operating frequency. Also, the C<sub>gd</sub> capacitance is grounded through the S<sub>1</sub> switch, ensuring it doesn't influence the operation.

Fig. 10 shows simulation results where  $V_b$  node is grounded, reducing the hold-mode feed-through by blocking signal transmission during hold phase. However, the method using S<sub>1</sub> does not completely solve the problems mentioned. It causes an input signal-dependent voltage drop on the V<sub>b</sub> node at the track-to-hold transition, leading to an increase in hold pedestal error and resulting in hold-mode distortion. However, the TDPD utilized this distortion as the cancellation purpose for track-mode distortion of SF and improved the linearity of the T/H circuit.

FIGURE 10. Simulation result for hold-mode feed-though of the TDPD T/H circuit.

FIGURE 11. (a) Diagram of nMOS SF for the track mode and (b) its feedback system representation.

#### **IV. DISTORTION ANALYSIS USING VOLTERRA SERIES**

# A. TRACK-MODE DISTORTION

This section analyzes track-mode operation using Volterra series analysis. The Volterra series can be applied to a small signal weakly nonlinear time-invariant system with a memory effect. In track mode, the circuit functions as a source follower, which can be considered a small signal weakly nonlinear time-invariant system with a memory effect.

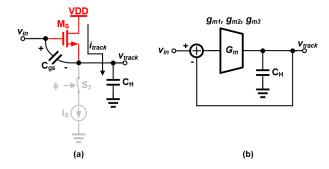

During track phase, T/H operates as SF, transferring input signal to large capacitor ( $C_H$ ). This process causes distortion due to the nonlinear transconductance of the transistor, which is transferred along with the signal. When entering the hold phase, the SF is turned off by the switches, and the transferred signal is stored. This is referred to as the track-mode distortion. In the analysis, only the nMOS SF driving  $C_H$  was considered, as shown in Fig. 11 (a). The first pMOS SF stage was excluded because it has a small effect on the overall distortion due to the small load capacitance originating from the parasitic capacitance of the 2<sup>nd</sup> stage. Even though the transfer function of SF was introduced in previous literatures [26], [30], and [31], this study treats SF as a feedback system and analyzes the distortion based on a loop gain (T) to provide design insights.

The SF and hold capacitances in the track-mode comprise a feedback loop as shown in Fig. 11 (b). The transfer function between the input ( $v_{in}$ ) and output ( $v_{Track}$ ) is defined as follows:

$$v_{Track} \triangleq H_1 (j\omega_a)^\circ v_{in} + H_2 (j\omega_a, j\omega_b)^\circ v_{in}^2 + H_3 (j\omega_a, j\omega_b, j\omega_c)^\circ v_{in}^3$$

(1)

where  $\omega_a$ ,  $\omega_b$ , and  $\omega_c$  are the input frequencies of SF. Volterra kernels  $H_1(j\omega_a)$ ,  $H_2(j\omega_a, j\omega_b)$ , and  $H_3(j\omega_a, j\omega_b, j\omega_c)$  are the linear gain, 2<sup>nd</sup>-order harmonic distortion, and 3<sup>rd</sup>-order harmonic distortion coefficients of the buffer, respectively. These are solved using the current formulas (2) and (3).

$$i_{track} = \frac{\partial C_H v_{track}}{\partial t}$$

(2)

$$i_{track} = G_m (v_{in} - v_{track})$$

$$= g_{m1} (v_{in} - v_{track}) + g_{m2} (v_{in} - v_{track})^2$$

$$+ g_{m3} (v_{in} - v_{track})^3$$

(3)

where  $g_{mn}$  is the nth-order nonlinear coefficient of M<sub>S</sub>. Based on the loop gain of SF expressed in (4), the Volterra kernels are presented as follows: The 1<sup>st</sup> term is (5) and the 2<sup>nd</sup>, 3<sup>rd</sup> terms are obtained as in (6) and (7), respectively. Each term contains loop gains  $T(\omega_a + \omega_b)$  and  $T(\omega_a + \omega_b + \omega_c)$  for the harmonic frequency.  $g_{m1}$  and C<sub>H</sub> determine the bandwidth, as shown in  $T(\omega_a)$  and  $H_1(j\omega_a)$ . Therefore,  $g_{m1}$ must be set by the input frequency and operation speed of the T/H. Since the T/H circuit was measured with a signal frequency input,  $H_3(j\omega_a, j\omega_b, j\omega_c)$ , which relates to 3<sup>rd</sup>order distortion, can be expressed as (8) under the condition  $\omega_a = \omega_b = \omega_c = \omega_1$ .

$$i_{track} = \frac{g_{m1}}{j\omega_a C_H} \tag{4}$$

$$H_1(j\omega_a) = \frac{T(j\omega_a)}{[1+T(j\omega_a)]}$$

(5)

$H_2(j\omega_a, j\omega_b)$

$$= \frac{[g_{m2}/j(\omega_{a} + \omega_{b})C_{H}]}{\{[1+T(\omega_{a})][1+T(\omega_{b})][1+T(\omega_{a} + \omega_{b})]\}}$$

(6)

H<sub>3</sub> (j\omega\_{a}, j\omega\_{b}, j\omega\_{c})

$$=\frac{\left\{g_{m3}\overline{\left[1-H_{1}\left(j\omega_{a}\right)\right]^{3}}-2g_{m2}\overline{\left[1-H_{1}\left(j\omega_{a}\right)\right]H_{2}\left(j\omega_{b},j\omega_{c}\right)}\right\}}{\left\{\left[1+T\left(\omega_{a}+\omega_{b}+\omega_{c}\right)\right]\times j\left(\omega_{a}+\omega_{b}+\omega_{c}\right)C_{H}\right\}}$$

(7)

$$H_{3}(j\omega_{1}) = \frac{\left\{g_{m3} - 2g_{m2}^{2} / [g_{m1} + j2\omega_{1}C_{H}]\right\}}{j3\omega_{1}C_{H}\left[1 + T(\omega_{1})\right]^{3}\left[1 + T(3\omega_{1})\right]}$$

Subsequently, using (5) to (8), the ratio of the 3<sup>rd</sup>-order distortion to the fundamental tone (HD3) can be expressed as in (9).

$$HD3 = \left[\frac{|H_3(j\omega_1)|}{|4H_1(j\omega_1)|}\right] v_{in}^2$$

(9)

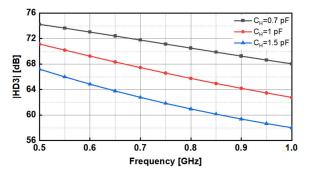

Generally, a differential circuit can neglect the 2<sup>nd</sup>-order harmonic distortion and the 3<sup>rd</sup>-order harmonic distortion is considered as a major nonlinearity term. Therefore, reducing  $H_3$  related to HD3 is important for achieving a high spurious-free dynamic range (SFDR) performance. The 3<sup>rd</sup>-order linearity performance primarily depends on the loop gain ( $T(\omega_1)$ ), which increases as the frequency decreases. As seen in (8), a low input frequency ( $\omega_1$ ) or small

(8)

FIGURE 12. Calculated HD3 of SF according to input frequency and load capacitance.

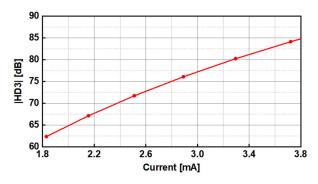

**FIGURE 13.** Calculated HD3 of SF according to current consumption at 1 GHz input frequency.

$C_{\rm H}$  results in a high  $T(\omega_1)$ , improving the HD3 performance. This trend can be confirmed in the calculation results shown in Fig. 12.

However, when striving for a high-speed and highperformance T/H circuit, it is necessary to operate at a high input frequency and implementing a small load capacitance can be challenging due to the large input impedance of the subsequent stage, such as a large C-DAC or interleaving paths in a TI ADC. Therefore,  $H_3(j\omega_1)$  can be reduced by reducing  $g_{m3}$  or increasing  $g_{m1}$ , which increases the loop gain of the feedback. These approaches are greatly influenced by the current, so the linearity is closely related to power consumption. Fig. 13 shows the calculation results of the magnitude of HD3 at an input frequency of 1 GHz. As shown in Fig. 13, HD3 improves by burning more current. Thus, it is important to employ a linearity enhancement technique to improve linearity which can relax the relationship between linearity performance and current consumption.

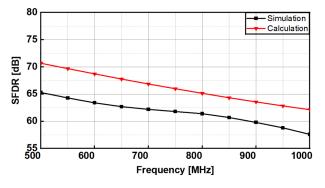

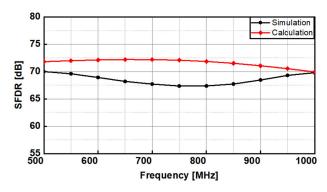

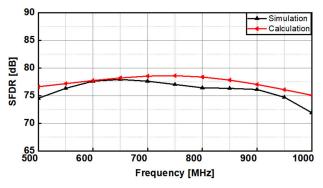

Fig. 14 presents the simulation and calculation result of the SFDR of a track-mode T/H circuit, where the SFDR performance decreases as the frequency increases as the loop gain decrease over the frequency.

### **B. HOLD-MODE DISTORTION**

#### 1) GATE-SOURCE CAPACITOR

The T/H circuit enters the hold mode by lowering the  $V_b$  node to ground, which results in hold-mode distortion due to the hold pedestal error.

FIGURE 14. Calculation and simulation results for SFDRs.

FIGURE 15. (a) Diagram of nMOS SF for the hold phase, (b) the diagram of nonlinear parasitic capacitor.

The TDPD technique attempts to cancel the track-mode distortion that occurred during the previous track phase by using the hold-mode distortion. This section explains the cancellation method through an analysis of the charge sharing process related to the nonlinear capacitor, which is the cause of hold-mode distortion.

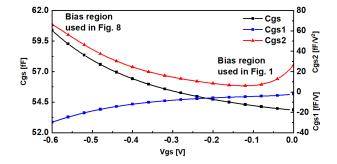

Nonlinear capacitors can be explained using the nMOS SF transistor and the hold-mode generation method. As shown in Fig. 15 (a), when the hold phase is entered, the gate node of the M<sub>S</sub> drops to ground, and V<sub>gs</sub> becomes less than 0 V, thus creating a new capacitance. The vertical diagram of this capacitance is shown in Fig. 15 (b), and it varies according to V<sub>gs</sub>. This can be expressed as (10) with a polynomial for V<sub>gs</sub> (=  $v_{track}$ ), like transconductance (3).

$$C_{gs} = f(v_{gs}) \approx C_{gs0} + C_{gs1}v_{gs} + C_{gs2}v_{gs}^{2}$$

$$\approx C_{gs0} - C_{gs1}v_{track} + C_{gs2}v_{track}^{2}$$

(10)

where  $C_{gs0}$  is the static capacitance,  $C_{gs1}$  and  $C_{gs2}$  are 1<sup>st</sup> and 2<sup>nd</sup>-order derivatives of the gate-source capacitance, respectively. Fig. 16 shows the simulation plot of the  $C_{gs}$  and  $C_{gs2}$  according to  $V_{gs}$ . The coefficients of (10) are determined by the size of the transistor and the static voltage ( $V_{DC}$ ) for the source node of the M<sub>S</sub> in the hold phase, and the static gate voltage applied to the SF during the track phase.

Because  $C_{gs}$  is newly generated in the hold phase, the charge stored in the  $v_{track}$  node (Q<sub>H</sub>) is maintained, as shown in (11), leading to charge sharing between C<sub>H</sub> and C<sub>gs</sub>. Herein, a new distortion arises due to the nonlinearity of C<sub>gs</sub>,

**FIGURE 16.** Simulation result for the gate-source capacitance according to gate-source voltage calculation and simulation results for SFDRs.

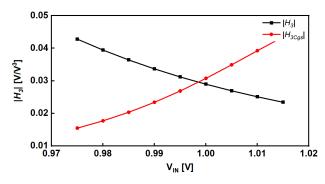

**FIGURE 17.** Calculation results for the distortion parameter to the input voltage.

which can be verified using (12). It represents the hold phase output voltage ( $v_{Hold}$ ).

$$Q_H = C_H v_{track} = (C_H + C_{gs}) v_{Hold} \tag{11}$$

$$\begin{aligned} {}_{Hold} &\cong \left[ 1 - \frac{c_{gs}}{C_H} \right] v_{track} \\ &\cong \left( 1 - \frac{C_{gs0}}{C_H} \right) v_{track} + \left( \frac{C_{gs1}}{C_H} \right) v_{track}^2 \\ &- \left( \frac{C_{gs2}}{C_H} \right) v_{track}^3 \end{aligned}$$

(12)

According to the equation,  $3^{rd}$ -order distortion is generated by the  $2^{nd}$ -order coefficient of  $C_{gs}$ , resulting in hold-mode distortion. The hold-mode distortion can be represented by the coefficient  $H_{3Cgs}$  in (13). By combining this with the transfer function of the previous track phase, the final transfer function of the T/H circuit can be obtained as shown in (14).

$$H_{3C_{gs}} \triangleq \left[ C_{gs2} / C_H \right] \left[ H_1 \left( j \omega_1 \right) \right]^3$$

(13)

$$v_{Hold} cong H_1 \left( j \omega_1 \right)^\circ v_{in} + H_3 \left( j \omega_1 \right)^\circ v_{in}^3 - H_{3C_{gs}} \left( j \omega_1 \right)^\circ v_{in}^3$$

(14)

For simplicity, the impact of charge sharing on the 1<sup>st</sup>-order was ignored, and the 2<sup>nd</sup>-order term was omitted due to the differential structure. As shown in (14), the track-mode 3<sup>rd</sup>-order distortion ( $H_3(j\omega_1)$ ) can be cancelled with the hold-mode 3<sup>rd</sup>-order distortion ( $H_{3Cgs}(j\omega_1)$ ), despite occurring at different time modes. Fig. 17 displays the calculation and simulation results of  $H_3$  and  $H_{3cgs}$  with respect to the static

FIGURE 18. The calculation and simulation results for SFDRs.

input voltage of the SF. Both parameters are complex values, so their absolute values are displayed in the graph for ease of interpretation. Consequently, with proper bias point and size of the transistor, the track mode  $3^{rd}$ -order distortion ( $H_3(j\omega_1)$ ) could be cancelled with the hold-mode 3rd-order distortion  $(H_{3Cgs}(j\omega_1))$ . When it comes to selecting transistor sizes, the suggested cancellation method boosts nonlinearity by counterbalancing the nonlinearity originating from the gate-source capacitance with the transconductance's nonlinearity The third-order distortion from the transconductance is inversely proportional to the square of the transistor size, whereas the third-order distortion from the gate-source capacitance ( $C_{gs}$ ) nonlinearity is directly proportional to the transistor size. Therefore, we meticulously select the optimal transistor size to minimize the overall distortion. Fig. 18 presents a graph comparing the simulation and calculation results of SFDR under cancellation.

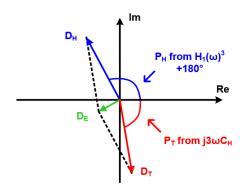

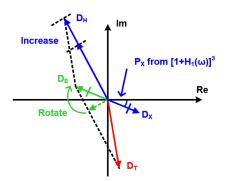

#### 2) CROSS-COUPLED CAPACITOR

Because the hold-mode distortion caused by  $C_{gs}$  and the track-mode distortion caused by  $g_m$  are complex values, if their phases are not properly aligned, the cancellation is not perfect, which limits the linearization. The phases of each term are as follows: as shown in Fig. 19, the track-mode distortion ( $D_T$ ) has a specific phase ( $P_T$ ), which is influenced by the hold capacitor and input frequency. To achieve complete cancellation, a distortion of opposite phase ( $-P_T$ ) and magnitude is required from the hold-mode. However, the hold-mode distortion ( $D_H$ ) has a phase ( $P_H$ ) of  $H_1(j\omega_1)$  in (13), which has some error compared to  $-P_T$ , even if the magnitude is set properly. Therefore, some cancellation is possible, but some residual distortion ( $D_E$ ) remains, limiting the enhancement of linearity.

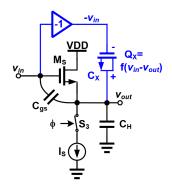

To improve the cancellation further, an additional MOS capacitor  $C_X$  was added between the input  $(v_{in})$  and output  $(v_{out})$  of the nMOS SF, as shown in Fig. 20 which shows an equivalent half circuit diagram. In the equivalent half circuit diagram,  $v_{in}$  is applied through an inverting buffer, which can be implemented using a cross-coupled connection based on a differential structure.

$$C_{X} = f(v_{gs}) \approx C_{X0} + C_{X1}v_{gs} + C_{X2}v_{gs}^{2}$$

(15)

v

FIGURE 19. Phase diagram of track-mode and hold-mode distortion.

**FIGURE 20.** Equivalent Half circuit diagram of nMOS SF with additional capacitor.

FIGURE 21. The modified phase diagram of track-mode and hold-mode distortion.

$$Q_X = C_X(v_{track} + v_{in})$$

= C<sub>X0</sub> (H<sub>1</sub> (j\omega<sub>1</sub>) + 1) v<sub>in</sub> - C<sub>X1</sub> (H<sub>1</sub> (j\omega<sub>1</sub>) + 1)<sup>2</sup> v<sup>2</sup><sub>in</sub>

+ C<sub>X2</sub> (H<sub>1</sub> (j\omega<sub>1</sub>) + 1)<sup>3</sup> v<sup>3</sup><sub>in</sub> (16)

$$H_{3C_X} \triangleq \left[ C_X / C_H \right] \left[ 1 + H_1 \left( j\omega_1 \right) \right]^3 \tag{17}$$

$$v_{Hold} \cong H_1 (j\omega_1)^\circ v_{in} + H_3 (j\omega_1)^\circ v_{in}^3 - H_{3C_{gs}} (j\omega_1)^\circ v_{in}^3 + H_{3C_X} (j\omega_1)^\circ v_{in}^3$$

(18)

The voltage difference between  $v_{in}$  and  $v_{out}$  is experienced by  $C_X$ , causing the signal-dependent charge  $Q_X$  to be stored in its nonlinear capacitance during the track phase. Similar

FIGURE 22. Calculation and simulation results for SFDRs.

FIGURE 23. Measurement setup.

to  $C_{gs}$ , the capacitance of  $C_X$  can also be expressed in terms of  $v_{gs}$ , as shown in (15). As a result,  $Q_X$  can be expressed in relation to  $v_{in}$ , as shown in (16). This charge is transmitted and influences the stored hold voltage based on the change in bias voltage of  $C_X$  in the hold phase. If the effect of  $C_X$ is defined as a coefficient, as shown in (17), the effect of  $C_H$ can be summarized in (18).

Here, it is stated that the addition of a capacitor,  $C_X$ , between the input and output of an nMOS SF circuit can improve the SFDR (Spurious Free Dynamic Range) performance further. The new capacitor, C<sub>X</sub>, experiences a voltage difference between the input and output, which creates a nonlinear charge, Q<sub>X</sub>, that affects the stored hold voltage. This effect is represented as a  $3^{rd}$ -order distortion ( $H_{3CX}$ ) and its phase is determined by  $(1 + H_1(j\omega_1))$ . The phase diagram including the new distortion  $(D_X)$  is shown in Fig. 21, which provides additional cancellation of distortions. The phase of the hold-mode distortion  $(D_H)$  must be partially adjusted so that the vector sum  $(D_E)$  of the track-mode distortion  $(D_T)$ and D<sub>H</sub> is close to the opposite phase and magnitude of D<sub>X</sub>. This can further improve the overall SFDR performance, as shown in Fig. 22 which shows the simulation and calculation result of SFDR including C<sub>X</sub>.

### **V. MEASUREMENT RESULTS**

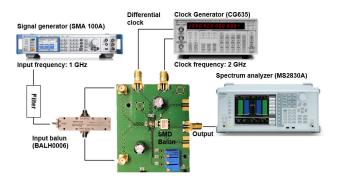

Seventeen sample chips which were fabricated with a 65 nm CMOS were used for measurement. The mean value of the power consumption of the chips is 9mW at a 1.5 V supply. Fig. 23 shows measurement setup of the T/H chip.

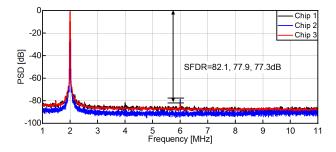

FIGURE 24. The measured output spectrum at 2 GS/s for a 700-mV\_{PP} 998 MHz sinusoidal input with 3 chips.

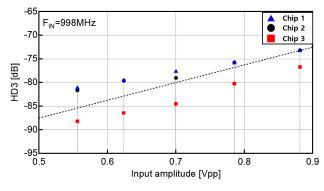

FIGURE 25. The measured HD3 versus the input amplitudes with 3 chips.

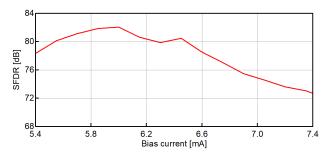

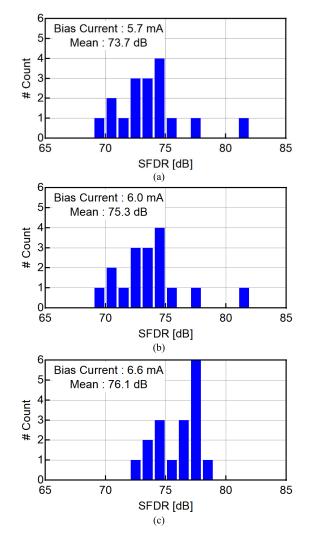

Fig. 24 shows the measurement results of the output spectrum at 2 GS/s (F<sub>S</sub>) for a 998 MHz sinusoidal input (F<sub>IN</sub>) with 700 mV<sub>PP</sub> with three sample chips The results showed SFDRs of 82.1 dB, 77.9 dB, and 77.3 dB respectively. Among the results, the best performance showed an improvement of 20.5 dB in distortion cancellation. As a result, an SFDR-based figure of merit (FoM) of 192.5 was obtained. The FoM was calculated using (19) which took into accounting both power consumption and energy-efficiency. Fig. 25 shows the measured HD3 versus the input amplitude for these chips. Fig. 26 shows the measurement results of the SFDR variation with respect to the bias current. The highest SFDR was achieved at 6 mA, and a lower or higher bias current resulted in a lower SFDR performance. Even though a higher bias current increases the linearity of the SF, it decreases the overall performance due to deviation from the cancellation condition between track-mode distortion and hold-mode distortion. Seventeen samples were used to measure the variation in SFDR, and Fig. 27 shows the measurement results according to the bias condition when a 2 GS/s 700 mV<sub>PP</sub> 998 MHz sinusoidal input was applied for all the samples. The statistic variations of the SFDR shows mean value of 73.7, 75.3 and 76.1 dB with sigma of 2.8, 2.3 and 2.0 dB respectively at 2 G/s for a 700 mV<sub>PP</sub> 998 MHz sinusoidal input according to the bias conditions for (a) 5.7 mA, (b) 6mA, and (c) 6.6 mA. A conventional T/H circuit without cancellation was also measured which shows an SFDR of 61.6 dB at 14mW power consumption. When each sample was set to the optimal bias, an SFDR of 77.1 dB was obtained which is 15.5 dB improvement over the conventional T/H circuit even with 5mW less

FIGURE 26. The measured SFDR according to the bias current.

FIGURE 27. The statistic variations of the SFDR at 2 GS/s for a 700 mV<sub>PP</sub> 998 MHz sinusoidal input for 17 samples according to the bias conditions for (a) 5.7 mA, (b) 6mA, and (c) 6.6 mA.

power consumption. Table 1 summarizes the measurement results of the conventional T/H circuit, the multiple TDPD T/H chips and compares them with other state-of-the-art T/H chips.

$$FoM_{SFDR} = SFDR + 10 \log_{10} \frac{F_S}{2 \times Power}$$

(19)

| Feature              |                     | Tech.<br>[nm] | F <sub>IN</sub> [GHz]<br>/ F <sub>S</sub> [GS/s] | Supply Voltage<br>[V] | Power [mW] | SFDR at F <sub>IN</sub> [dB] | FoM <sub>sfDR</sub><br>[dB]* |

|----------------------|---------------------|---------------|--------------------------------------------------|-----------------------|------------|------------------------------|------------------------------|

| This<br>Work         | w/o<br>Cancellation | 65            | 1/2                                              | 1.5                   | 14         | 61.6                         | 170.1                        |

|                      | Chip1               |               |                                                  |                       | 8.6        | 77.3                         | 188.0                        |

|                      | Chip2               |               |                                                  |                       | 9.5        | 77.9                         | 187.8                        |

|                      | Chip3               |               |                                                  |                       | 9          | 82.1                         | 192.5                        |

|                      | Avg.<br>(17 Chips)  |               |                                                  |                       | 9          | 77.1                         | 187.5                        |

| JSSC20<br>Ali [8]    |                     | 16            | 4/10                                             | 1.8                   | 220        | 65                           | 168.6                        |

| JSSC14<br>Ali [16]   |                     | 65            | 0.14/1                                           | 3.3                   | 99         | 86                           | 183                          |

| JSSC17<br>S. D. [7]  |                     | 28            | 4/10                                             | 3                     | 400        | 66                           | 167                          |

| ISSCC17<br>Vaz [9]   |                     | 16            | 2/4                                              | -                     | 282        | 67                           | 165.5                        |

| RFIC21<br>E. W. [17] |                     | 22            | 3/3                                              | 2.8                   | 167        | 67.5                         | 167.5                        |

#### TABLE 1. Performance summary and comparison.

\* FoM<sub>SFDR</sub> is expressed at equation (19)

#### **VI. CONCLUSION**

This study provides design insight and mathematical analysis of the active T/H circuits based on a switched SF and TDPD technique and shows measurement result of multiple sample chips. The track-mode distortion was explained by expressing the SF through the Volterra series from a feedback viewpoint. During the hold phase, the hold-mode feedthrough can be minimized by the structure. In contrast, the increased hold pedestal error caused by nonlinear parasitic capacitance was analyzed through charge sharing, and it was introduced as hold-mode distortion. The cancellation between track-mode and hold-mode distortion was explained in light of these distortions. Additionally, the explanation and analysis of additional cancellation with an extra capacitance  $(C_X)$  was provided. Seventeen samples were measured and showed stable cancellation operation. When each sample was set to the optimal bias, an average of SFDR of 77.1 dB was obtained which is 15.5 dB (max. 20.5dB) improvement even with 5mW less power consumption over the conventional T/H circuit without cancellation.

The operational frequency of this system is, in fact, constrained by the speed of the clock distribution network for the sampling clock (2Gs/s). Without accounting for this limitation in clock distribution speed, the sampler itself could potentially operate at over 10Gs/s [11]. Additionally, the cancellation technique remains unaffected by the operating frequency, allowing us to enhance the operating frequency by adopting more advanced CMOS technology.

### ACKNOWLEDGMENT

The author Geunhaeng Lee was with the School of Electrical and Electronic Engineering, Yonsei University, Seoul, South Korea. This work performed at Yonsei University. The MPW and CAD tool were supported by IDEC.

#### REFERENCES

- [1] M. Guo, J. Mao, S.-W. Sin, H. Wei, and R. P. Martins, "A 5 GS/s 29 mW interleaved SAR ADC with 48.5 dB SNDR using digital-mixing background timing-skew calibration for direct sampling applications," *IEEE Access*, vol. 8, pp. 138944–138954, 2020.

- [2] K. N. Madsen, T. D. Gathman, S. Daneshgar, T. C. Oh, J. C. Li, and J. F. Buckwalter, "A high-linearity, 30 GS/s track-and-hold amplifier and time interleaved sample-and-hold in an InP-on-CMOS process," *IEEE J. Solid-State Circuits*, vol. 50, no. 11, pp. 2692–2702, Nov. 2015.

- [3] L. Fang, X. Wen, T. Fu, and P. Gui, "A 12-bit 1 GS/s RF sampling pipeline-SAR ADC with harmonic injecting cross-coupled pair achieving 7.5 fj/Conv-step," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 69, no. 8, pp. 3225–3236, Aug. 2022.

- [4] A. T. Ramkaj, J. C. Peña Ramos, M. J. M. Pelgrom, M. S. J. Steyaert, M. Verhelst, and F. Tavernier, "A 5-GS/s 158.6-mW 9.4-ENOB passivesampling time-interleaved three-stage pipelined-SAR ADC with analogdigital corrections in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 55, no. 6, pp. 1553–1564, Jun. 2020.

- [5] L. Breems, M. Bolatkale, H. Brekelmans, S. Bajoria, J. Niehof, R. Rutten, and B. Oude-Essink, "A 2.2 GHz continuous-time ΔΣ ADC with -102 dBc THD and 25 MHz bandwidth," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 2906–2916, Dec. 2016.

- [6] B. Hershberg, D. Dermit, B. van Liempd, E. Martens, N. Markulic, J. Lagos, and J. Craninckx, "A 4-GS/s 10-ENOB 75-mW ringamp ADC in 16-nm CMOS with background monitoring of distortion," *IEEE J. Solid-State Circuits*, vol. 56, no. 8, pp. 2360–2374, Aug. 2021.

- [7] S. Devarajan, L. Singer, D. Kelly, T. Pan, J. Silva, J. Brunsilius, D. Rey-Losada, F. Murden, C. Speir, J. Bray, E. Otte, N. Rakuljic, P. Brown, T. Weigandt, Q. Yu, D. Paterson, C. Petersen, J. Gealow, and G. Manganaro, "A 12-b 10-GS/s interleaved pipeline ADC in 28-nm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3204–3218, Dec. 2017.

- [8] A. M. A. Ali, H. Dinc, P. Bhoraskar, S. Bardsley, C. Dillon, M. McShea, J. P. Periathambi, and S. Puckett, "A 12-b 18-GS/s RF sampling ADC with an integrated wideband track-and-hold amplifier and background calibration," *IEEE J. Solid-State Circuits*, vol. 55, no. 12, pp. 3210–3224, Dec. 2020.

- [9] B. Vaz, A. Lynam, B. Verbruggen, A. Laraba, C. Mesadri, A. Boumaalif, J. Mcgrath, U. Kamath, R. De Le Torre, A. Manlapat, D. Breathnach, C. Erdmann, and B. Farley, "16.1 A 13b 4GS/s digitally assisted dynamic 3-stage asynchronous pipelined-SAR ADC," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 276–277.

- [10] S. Linnhoff, E. Sippel, F. Buballa, M. Reinhold, M. Vossiek, and F. Gerfers, "A 12 bit 8 GS/s randomly-time-interleaved SAR ADC with adaptive mismatch correction," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2021, pp. 1–4.

- [11] S. Ma, H. Yu, and J. Ren, "A 32.5-GS/s sampler with time-interleaved track-and-hold amplifier in 65-nm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 12, pp. 3500–3511, Dec. 2014.

- [12] B. Verbruggen, M. Iriguchi, and J. Craninckx, "A 1.7 mW 11b 250MS/s 2x interleaved fully dynamic pipelined SAR ADC in 40 nm digital CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2012, pp. 466–467.

- [13] C.-C. Liu, S.-J. Chang, G.-Y. Huang, Y.-Z. Lin, C.-M. Huang, C.-H. Huang, L. Bu, and C.-C. Tsai, "A 10b 100MS/s 1.13 mW SAR ADC with binary-scaled error compensation," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2010, pp. 386–387.

- [14] B. Razavi, "Design considerations for interleaved ADCs," *IEEE J. Solid-State Circuits*, vol. 48, no. 8, pp. 1806–1817, Aug. 2013.

- [15] A. Buchwald, "High-speed time interleaved ADCs," *IEEE Commun. Mag.*, vol. 54, no. 4, pp. 71–77, Apr. 2016.

- [16] A. M. A. Ali, H. Dinc, P. Bhoraskar, C. Dillon, S. Puckett, B. Gray, C. Speir, J. Lanford, J. Brunsilius, P. R. Derounian, B. Jeffries, U. Mehta, M. McShea, and R. Stop, "A 14 bit 1 GS/s RF sampling pipelined ADC with background calibration," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 2857–2867, Dec. 2014.

- [17] E. Wittenhagen, P. Artz, P. Scholz, and F. Gerfers, "A 3 GS/s >55 dBFS SNDR time-interleaved RF track and hold amplifier with >67 dBc SFDR up to 3 GHz in 22FDX," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.* (*RFIC*), Jun. 2021, pp. 139–142.

- [18] A. M. A. Ali, A. Morgan, C. Dillon, G. Patterson, S. Puckett, P. Bhoraskar, H. Dinc, M. Hensley, R. Stop, S. Bardsley, D. Lattimore, J. Bray, C. Speir, and R. Sneed, "A 16-bit 250-MS/s IF sampling pipelined ADC with background calibration," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2602–2612, Dec. 2010.

- [19] J. Jang, Y. Chae, and T. W. Kim, "A 1.5 v 2 GS/s 82.1 dB-SFDR track and hold circuit based on the time-divided post-distortion cancelation technique," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 12, pp. 4719–4723, Dec. 2022.

- [20] H. Dinc and P. E. Allen, "A 1.2 GSample/s double-switching CMOS THA with -62 dB THD," *IEEE J. Solid-State Circuits*, vol. 44, no. 3, pp. 848-861, Mar. 2009.

- [21] S. Shahramian, S. P. Voinigescu, and A. C. Carusone, "A 30-GS/sec track and hold amplifier in 0.13-μm CMOS technology," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2006, pp. 493–496.

- [22] A. Moriyama, S. Taniyama, and T. Waho, "A low-distortion switched-source-follower track-and-hold circuit," in *Proc. 19th IEEE Int. Conf. Electron., Circuits, Syst. (ICECS)*, Dec. 2012, pp. 105–108.

- [23] S. Daneshgar, Z. Griffith, and M. J. W. Rodwell, "A high IIP3, 50 GSamples/s track and hold amplifier in 0.25 μm InP HBT technology," in *Proc. IEEE Compound Semiconductor Integr. Circuit Symp. (CSICS)*, Oct. 2012, pp. 1–4.

- [24] T. D. Gathman, "An 8-bit, 12 GSample/sec SiGe track-and-hold amplifier," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 1–34.

- [25] W. Zhen, S. Li, S. Cao, Y. Su, and Z. Jin, "A 25-GSa/s InP DHBT track-and-hold amplifier using active peaking input buffer," *IEEE Microw. Wireless Compon. Lett.*, vol. 31, no. 10, pp. 1142–1145, Oct. 2021.

- [26] H. Liang, R. J. Evans, and E. Skandas, "Distortion analysis of 30Gsample/s CMOS switched source follower," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2010, pp. 4293–4296.

- [27] W. Zhen, L. Xiao, S. Cao, Y. Su, and Z. Jin, "A 35-GHz bandwidth 30 GSa/s InP track-and-hold amplifier using enhanced fT-doubler technique," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 11, pp. 4243–4247, Nov. 2022.

- [28] S. Yamanaka, K. Sano, and K. Murata, "A 20-Gs/s track-and-hold amplifier in InP HBT technology," *IEEE Trans. Microw. Theory Techn.*, vol. 58, no. 9, pp. 2334–2339, Sep. 2010.

- [29] T. Baumheinrich, B. Pregardier, and U. Langmann, "A 1-GSample/s 10-b full Nyquist silicon bipolar track&hold IC," *IEEE J. Solid-State Circuits*, vol. 32, no. 12, pp. 1951–1960, Dec. 1997.

- [30] S. Shahramian, A. C. Carusone, and S. P. Voinigescu, "Design methodology for a 40-GSamples/s track and hold amplifier in 0.18-μm SiGe BiCMOS technology," *IEEE J. Solid-State Circuits*, vol. 41, no. 10, pp. 2233–2240, Oct. 2006.

- [31] X. Fan and P. K. Chan, "Analysis and design of low-distortion CMOS source followers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 8, pp. 1489–1501, Aug. 2005.

**JUNYOUNG JANG** was born in South Korea, in 1990. He received the B.S. and Ph.D. degrees in electrical and electronic engineering from Yonsei University, Seoul, South Korea, in 2014 and 2023, respectively.

Since 2023, he has been a Staff Engineer with System LSI Business, Samsung Electronics, Hwaseong, South Korea. His research interest includes RF/analog circuit and systems for wireless application.

**GEUNHAENG LEE** received the B.S. degree in electronic and electrical engineering from Dankook University, Kyung-ki, Republic of Korea, in 2014, and the Ph.D. degree in electrical and electronic engineering from Yonsei University, Seoul, Republic of Korea, in 2021.

He was a Staff Engineer with System LSI Business, Samsung Electronics, Hwaseong, Republic of Korea, from 2021 to 2023, where he was involved with design of UWB RF transceiver

(IEEE 802.15.4z). Since March 2023, he has been an Assistant Professor with the Department of Electronic Engineering, Andong National University, Republic of Korea. His research interests include RF amplifiers including PA and LNA, mixed-signal circuits, and circuit and system for wireless communication. He is also interested in research on UWB transceiver systems, mm-wave ICs, and digital transmitter.

Dr. Lee received the Bronze Prize of the Circuit Design Division at the 27th Humantech Paper Award hosted by Samsung Electronics, in 2021. He also serves as a Technical Reviewer for IEEE SOLID-STATE CIRCUITS LETTERS, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, and IEEE JOURNAL OF SOLID-STATE CIRCUITS.

**TAE WOOK KIM** (Senior Member, IEEE) was born in Seoul, South Korea, in 1974. He received the B.S. degree in electrical engineering from Yonsei University, Seoul, in 2000, and the M.S. and Ph.D. degrees from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 2002 and 2005, respectively.

He was with Qualcomm Inc., Austin, TX, USA, where he was involved with DVB-H and Medi-

aFLO chip design. Since September 2007, he has been with the School of Electrical and Electronic Engineering, Yonsei University, where he is currently a Professor. His research interests include microwave, RF, analog, and mixed-signal ICs and systems.

Dr. Kim served as a Technical Program Committee Member for IEEE ISSCC and IEEE APMC and a Steering Committee Member for IEEE MWSCAS. He is serving as a TPC Member for A-SSCC and an Organizing Committee Member for IEEE A-SSCC.