Received 14 January 2024, accepted 21 January 2024, date of publication 26 January 2024, date of current version 6 February 2024.

Digital Object Identifier 10.1109/ACCESS.2024.3359157

# A Novel High Performance Standard-Cell Based ULV OTA Exploiting an Improved Basic Amplifier

RICCARDO DELLA SALA<sup>®</sup>, FRANCESCO CENTURELLI<sup>®</sup>, (Senior Member, IEEE), AND GIUSEPPE SCOTTI<sup>®</sup>, (Senior Member, IEEE)

Dipartimento di Ingegneria dell'Informazione Elettronica e Telecomunicazioni (DIET), Sapienza University of Rome, 00184 Rome, Italy Corresponding author: Riccardo Della Sala (riccardo.dellasala@uniroma1.it)

**ABSTRACT** In this paper we introduce an improved standard-cell-based voltage amplifier cell with low output resistance. The proposed amplifier cell exhibits a voltage gain whose value can be accurately set by the number of paralleled inverters, and its output static voltage is well controlled through a replica bias approach. A three-stage fully synthesizable OTA architecture exploiting the improved voltage amplifier is also proposed. The OTA has been designed referring to the standard-cell library of a 180nm CMOS technology with a supply voltage of 0.3V and a nominal power consumption of only 6.63 nW, and exhibits a dc-gain of 73.5 dB with a gain-bandwidth-product of 9.63 kHz. A comparison against the state of the art of ultra-low-voltage OTAs has shown that the proposed amplifier exhibits the best value of the small signal figures of merit.

**INDEX TERMS** OTA, ULV, ULP, inverter-based, fully-synthesizable.

### I. INTRODUCTION

The advent of the Internet-of-Things (IoT) has brought a plethora of advancements in the fields of electronics and communication, prompting researchers to reconsider traditional circuit design methodologies [1], [2]. Recent advancements in compact wireless autonomous devices [3], [4] are poised to facilitate ambulatory and non-invasive health parameter monitoring, leading to enhanced healthcare services [5], [6], [7]. These devices, functioning as wireless sensor nodes (WSN) [8], [9], [10], can be situated on or within the human body, especially in the case of implantable devices [11], [12]. Their primary purpose is to monitor neurological and physiological signals, including electrocardiography (ECG) [13], [14], electroencephalography (EEG) [15], [16], and electro-myography (EMG) [17], [18].

However, before the acceptance of WSN for health monitoring, many challenges including technological challenges and legal challenges must be addressed [19], [20].

The associate editor coordinating the review of this manuscript and approving it for publication was Fabian Khateb.

These challenges encompass issues like privacy concerns and technology-related aspects such as reliability, security, form factor, low energy consumption, and energy autonomy, particularly for devices relying on harvested energy sources [21]. Among these challenges, minimizing the energy consumption of wireless sensor networks is often deemed one of the most critical issues [22]. This reduction in energy consumption holds the key to improving form factors, reliability, and security, for instance, by employing smaller batteries, extending battery life [23]. Substantial research efforts have been dedicated to this area in recent years. Notably, advancements in integrated circuit (IC) technology and circuit design techniques have led to systems with processing capabilities that can supplement or even entirely replace complex biomedical operations. It's essential to highlight that while ICs offer virtually unlimited processing capabilities, energy resources in biomedical electronics are profoundly limited [24], [25], [26].

Specialized low-power design techniques can enable dedicated solutions to operate with power consumption in the order of  $\mu$ W, ensuring over a decade of functionality with

the same battery [27]. Furthermore, the demand for portable and wearable devices with stringent requirements has led to a drive for faster design times and reduced area usage to minimize costs [2]. In addition, since many IoT circuits rely on energy harvesting architectures [1], [2], [28], [29], [30], [31], there is an increasing appeal for the development of Ultra-Low-Voltage (ULV) analog building blocks capable of operating with supply voltages as low as 0.3V, such as OTAs [32], [33], [34], [35], [36], [37], [38], [39], comparators [40], [41], [42] and so on.

The Operational Transconductance Amplifier (OTA) is widely used in a plethora of analog applications, and recently, several high-performance ULV OTAs exploiting body-driven [32], [33], [34], [36], [37], [43], [44], [45], [46] and inverter-based [35], [47], [48], [49], [50], [51] architectures have been presented in the literature. All these OTAs require a full custom design approach in which the layout is carried out manually and often the area occupation is large because separate wells are needed for implementing body-driven stages.

Inverter-based OTAs rely on custom-defined inverters to achieve reasonable performance under process, supply voltage and temperature (PVT) variations [52], [53]. Custom inverters offer more degrees of freedom but have a larger area footprint compared to standard-cell inverters. Standard-cell inverters, on the other hand, are difficult to control in terms of bias point and can result in performance sensitivity to PVT variations. In order to reduce the sensitivity to PVT variations of standard-cell-based analog circuits several techniques to properly set internal node voltages have been proposed, resulting in improved robustness [54], [55].

Researchers have recently concentrated on optimizing and improving novel layout strategies in an effort to find a way to automate the design flow of analog blocks. These strategies include the automatic place and route strategies for standard-cell based circuits, which are typically used in the digital design flow to implement fully-synthesizable comparators [42], ADCs [56], DACs [57], LDOs [58], filters [59], and OTAs [60] for both IoT and biomedical applications. The goal is to speed up design time and drastically reduce the area and power consumption of analog building blocks implemented in the design flow of systems on chip (SoCs) for IoT and biomedical applications.

The recent introduction of the digital OTA (DIG-OTA) in [61] offers a new approach to designing OTAs with minimal area and power usage. In [62], a standard-cell implementation of the DIG-OTA is proposed, demonstrating good performance in terms of area consumption and Figures Of Merits (FOMs). However, DIG-OTAs are highly sensitive to PVT and mismatch variations and often require calibration or supply voltage adjustment for proper functionality [62], [63], [64].

A different approach based on the usage of digital standard-cells to mimic the behavior of analog circuits has been recently introduced [65], [66]. This is typically done by utilizing the inverter gate from a standard-cell library

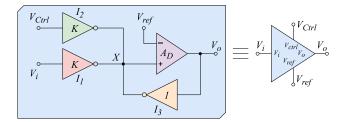

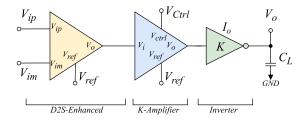

FIGURE 1. Block scheme of the proposed improved K-Amplifier.

**FIGURE 2.** Gate level schematic of the error amplifier  $A_D$ .

as a basic analog amplifier. In [55] a method has been proposed to center the dynamic-range of these inverters, making them more robust against PVT variations. In addition, novel topologies for differential to single-ended converters have been proposed [67] to improve common-mode rejection ratio and input common-mode range of standard-cell-based OTAs.

To increase the gain and GBW of inverter-based OTAs, multiple stages need to be cascaded and additional capacitors are required for stability. In [65], the authors have proposed a standard-cell-based analog amplifier that is able to provide voltage gain without introducing high impedance nodes thus allowing the cascading of several amplifier stages. The main limitation of the standard-cell-based voltage amplifier cell proposed in [65] is its limited maximum gain. To overcome this limitation, an improved version of the voltage amplifier cell in [65] is proposed in this work. The proposed improved standard-cell-based voltage amplifier (denoted as K-Amplifier in the following) can attain a voltage gain whose value can be accurately set by the number K of paralleled inverters which results in a transconductance which is K times higher than the transconductance of the loading inverter.

In the following, Section II introduces the proposed standard-cell-based K-Amplifier, Section III discusses the proposed three stage OTA architecture exploiting the K-Amplifier and presents the results of the simulations, and finally conclusions are drawn in Section V.

## II. PROPOSED K-AMPLIFIER SCHEME

The block scheme of the proposed improved standard-cell-based voltage amplifier cell (K-Amplifier) is depicted in Fig.1. It is composed by three inverters  $I_{1,2,3}$ , and a standard-cell-based differential amplifier  $A_D$ . The inverters  $I_{1,2}$  are

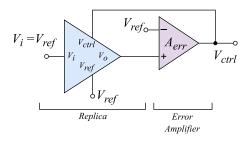

FIGURE 3. Block scheme of the replica biasing approach for the K-Amplifier.

implemented as the parallel of K instances of a reference inverter [65], whereas the  $I_3$  is a single instance of the reference inverter. The inverters  $I_{1,2}$  implement a basic-amplifier [55], in which  $I_1$  is the signal amplifier and  $I_2$  is exploited to properly set the static voltage at node X through a replica bias loop controlling the  $V_{Ctrl}$  voltage. The main difference of the circuit in Fig. 1 with respect to the previous implementation in [65] is the introduction of the error amplifier which allows to minimize the effect of the output conductance of  $I_{1,2}$  at node X, thus enabling the possibility to achieve a voltage gain accurately set by the factor K for voltage gain values ranging from 0dB to 20dB as will be better shown in the following.

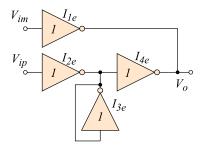

The gate level schematic of the standard-cell-based differential amplifier  $A_D$  is reported in Fig. 2. Looking at Fig. 2, it is evident that the differential to single-ended conversion relies on two signal paths. The path connected to  $V_{ip}$  consists of three inverters,  $I_{2e}$ ,  $I_{3e}$ , and  $I_{4e}$ , the second of which,  $I_{3e}$ , has its input and output shorted between each other, while the path connected to  $V_{im}$  consists of just one inverter,  $I_{1e}$ . Comparing the standard-cell-based differential amplifier  $A_D$  against a conventional pseudo-differential pair with current mirror active load, a correlation can be observed between  $I_{1e}$ - $I_{2e}$  and the pseudo-differential pair and between  $I_{3e}$ - $I_{4e}$  and the current-mirror active load [55].

#### A. THE REPLICA BIAS APPROACH

The  $V_{Ctrl}$  voltage to properly set the static voltage at node X of the K-Amplifier in Fig.1 is generated by the replica bias control loop shown in Fig. 3. A replica bias approach similar to the one adopted in [55] is here exploited by enclosing a replica of the K-Amplifier cell within a negative feedback loop. The input of the replica K-Amplifier is biased with a voltage  $V_{ref}$ , typically set to  $AGND = V_{DD}/2$ , and the output of this replica K-Amplifier is compared with the reference voltage itself through an error amplifier denoted as  $A_{err}$  in Fig. 3, which generates the control voltage  $V_{ctrl}$ . The error amplifier  $A_{err}$  is implemented with the same schematic adopted for the differential amplifier  $A_D$  depicted in Fig. 2.

The purpose of the control voltage is to set the output voltage of the replica amplifier close to  $V_{ref}$  by compensating both the systematic and the PVT dependent components of the output current offset of the replica amplifier. This control voltage is then applied to the inverter  $I_2$  of every

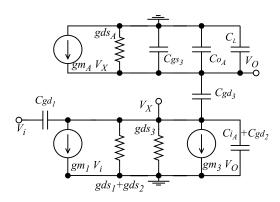

FIGURE 4. Equivalent circuit for small signal analysis.

K-Amplifier adopted in the chip for analog design purposes, thus guaranteeing a stable bias point of the amplifiers in all PVT conditions.

It is important to note that the replica bias loop in Fig. 3 does not necessitate any explicit compensation capacitor. This is due to the large parasitic capacitance driven by the error amplifier at node  $V_{ctrl}$ , which guarantees the minimum phase margin.

#### **B. CIRCUIT ANALYSIS**

The equivalent circuit for small signal analysis of the K-Amplifier is reported in Fig. 4, where the same notation as in [55] has been assumed for small signal parameters of inverters. The differential amplifier  $A_D$  in Fig. 1 is modeled in Fig. 4 with its small signal parameters  $gm_A$ ,  $gds_A$ ,  $Co_A$  and  $Ci_A$ , which denote the transconductance, the output conductance, the output capacitance respectively. The differential voltage gain  $A_D$  of the amplifier is therefore given by  $A_D = gm_A/gds_A$ . Starting from the circuit in Fig. 4, the transfer function of the K-Amplifier can be easily computed as:

$$\frac{Vo}{Vi} = -\alpha \cdot \frac{gm_1}{gm_3} \cdot \frac{(1 - s\tau_{z1})(1 + s\tau_{z2})}{(1 + s\tau_{p1})(1 + s\tau_{p2})} \tag{1}$$

where:

$$\alpha = \frac{1}{1 + \frac{gds_1 + gds_2 + gds_3}{gm_3 A_D}}, \quad \tau_{z1} = \frac{Cgd_1 + Cgd_2}{gm_1},$$

$$\tau_{z2} = -\frac{Cgd_3}{gm_A}, \quad \tau_{p1} = -\frac{\sum_{i=1}^3 Cgd_i + Ci_A}{\sum_{i=1}^3 gds_i}$$

$$\tau_{p2} = -\frac{C_L \sum_{i=1}^3 gds_i}{gm_3 gm_A}$$

(2)

Equation 1 shows that the dc-gain of the K-Amplifier is set by the ratio of the transconductances of  $I_1$  and  $I_3$ , with a non-ideality factor  $\alpha$  which, considering that  $gm_3 = Kgm_1$  and  $gds_3 = Kgds_1$  can be rewritten as:

$$\alpha = \frac{1}{1 + \frac{2Kgds_1 + gds_3}{kgm_1A_D}} \tag{3}$$

According to eq. 3, the non-ideality factor  $\alpha$  tends to 1 if the gain  $A_D$  of the error amplifier is large. Indeed the

role of the error amplifier introduced in this work with respect to the previous standard-cell-based voltage amplifier block presented in [65], is to minimize the negative impact caused by the output conductance of  $I_{1,2}$  at node X, as this significantly restricts the achievable voltage gain of the previous version. However, even if the proposed K-Amplifier outperforms the previous version, a limited value of  $A_D$  still results in a constrained maximum achievable gain for the K-Amplifier as will be better pointed out through simulation results in the next Section.

In terms of frequency response, the dominant pole is determined by  $p_1=1/\tau_{p1}$ , and the two high frequency zeros can be neglected. The second pole of the K-Amplifier is determined by its load capacitance  $C_L$ , and unless  $C_L$  is excessively high, its effect can be disregarded.

Another important feature of the proposed K-Amplifier is its low output resistance. In fact, thanks to the feedback loop closed at node X, the output resistance of the K-Amplifier is lowered with respect to the output resistance of the previous version, and results to be  $R_o \approx \frac{1}{g_{m3}A_D}$ .

Finally, the equivalent input capacitance  $C_{in_1}$  of the proposed K-Amplifier can be easily computed as:

$$C_{in_1} \approx C_{gs_1} + C_{gd_1} \cdot (K+1) \tag{4}$$

where  $C_{gd_1} \cdot (K+1)$  is the equivalent Miller capacitance.

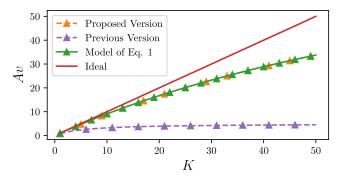

## C. K-AMPLIFIER DESIGN

The proposed K-Amplifier has been designed in a 180nm CMOS technology utilizing the minimum size standard-cell inverter as the reference inverter [65], and assuming a nominal supply voltage  $V_{DD}$  of 0.3V. The error amplifier in Fig. 2 has been also configured with minimum size standard-cell inverters achieving a voltage gain of 21 dB, which, considering also the gain of the inverter  $I_3$ , results in a loop gain in excess of 40dB for the feedback loop closed at node X. With such a loop gain the K-amplifier can be sized for large values of K, ideally approaching 100. Fig. 5 reports the gain of the K-Amplifier (Proposed Version) as a function of K, highlighting the accuracy of the voltage gain obtained with the proposed amplifier cell. The voltage gain predicted by eq. 1 (Model of Eq. 1), the voltage gain of the voltage amplifier block proposed in [65] (Previous Version), and the ideal value K (Ideal), are also reported in Fig. 5. As it can be observed, the maximum achievable gain of the previous version is limited to about 4 [V/V], and the accuracy with respect to the value of K is very low. On the other hand, the proposed K-Amplifier can be sized with K = 10 achieving a gain of 9.34 [V/V] confirming the high accuracy obtained thanks to the adoption of the error amplifier. Indeed, for K = 10, the attained gain is 19.41 dB and just 0.59 dB are lost with respect to the ideal value of 20dB. The maximum achievable gain of the K-Amplifier is in the order of 30 [V/V]. but in this extreme condition the accuracy with respect to the value of K is lowered.

FIGURE 5. Voltage gain of the proposed K-Amplifier as a function of K.

FIGURE 6. Proposed K-Amplifier based OTA.

# D. ROBUSTNESS OF THE K-AMPLIFIER TO PVT AND MISMATCH VARIATIONS

In order to test the robustness of the proposed K-Amplifier under PVT and mismatch variations, the amplifier has been sized with K = 10, and corner and Monte Carlo simulations have been carried out. The voltage gain  $A_{\nu}$  of a single K-Amplifier for different process corners, supply voltages and temperatures is reported in Tab. 1. The mean value  $\mu$  and the standard deviation  $\sigma$  of  $A_{\nu}$  estimated with 200 mismatch Monte Carlo runs are also reported in Tab. 1. The static output voltage of the K-Amplifier under PVT and mismatch variations has been also reported in Tab. 1. As it can be observed, due to the fact that the overall gain is set by the multiplicity (number of instances) of  $I_1$  with respect to  $I_3$ , the proposed amplifier is able to guarantee a very stable voltage gain over the different working conditions, even considering mismatch variations. Results in Tab. 1 also confirm the capability of the replica bias approach to accurately set the static output voltage of the proposed K-Amplifier.

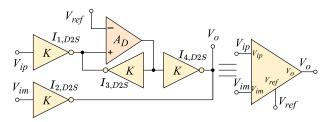

# III. PROPOSED STANDARD-CELL-BASED OTA ARCHITECTURE EXPLOITING THE K-AMPLIFIER

The proposed standard-cell-based OTA architecture exploiting the K-Amplifier is reported in Fig. 6. The first stage is a differential to single ended converter (D2S), which has been implemented according to the topology presented in [67] and depicted in Fig. 7. Also the error amplifier  $A_D$  in Fig. 7 is implemented with the topology reported in Fig. 2.

The aim of the D2S is to convert the input differential signal into a single ended one, thus rejecting common mode input signals. After the D2S block, a K-Amplifier which sets its static output voltage to  $V_{ref}$  due to the replica-bias feedback loop, and whose gain can be set through the multiplicity K

TABLE 1. Voltage gain  $A_V$  and static output voltage of the K-Amplifier under PVT and mismatch variations.

|            | Process Corners |        |        |        |        | Supply Voltage [V] |        | Temperature °C |        | Mismatch |          |

|------------|-----------------|--------|--------|--------|--------|--------------------|--------|----------------|--------|----------|----------|

|            | TT              | FF     | SS     | FS     | SF     | 270m               | 330m   | 0              | 80     | $\mu$    | $\sigma$ |

| Av [dB]    | 19.41           | 19.25  | 19.59  | 17.54  | 19.39  | 19.35              | 19.44  | 19.45          | 19.31  | 19.47    | 1.24     |

| Vo@DC [mV] | 149.99          | 149.93 | 149.89 | 144.96 | 142.59 | 133.51             | 166.48 | 149.99         | 149.91 | 150.3    | 5.12     |

FIGURE 7. Enhanced D2S converter presented in [67].

of  $I_1$  (see Fig. 1) is exploited as the second gain stage of the OTA. The final stage is a conventional standard-cell inverter  $I_o$ . This architecture is therefore a three stage OTA whose gain is typically higher than 60dB. In fact the overall dc-gain of the OTA can be expressed as:

$$Av = K \cdot \frac{gm_{4,D2Se}}{2 \cdot gds_{4,D2Se}} \cdot \frac{gm_o}{gds_o}$$

(5)

where  $gm_{4,D2S}$  and  $gds_{4,D2S}$  are the transconductance and the output conductance of  $I_{4,D2S}$  in Fig. 7,  $gds_o$  is the output conductance of  $I_o$  and  $gm_o$  is the trunsconductance of  $I_o$  in Fig. 6. The common mode rejection ratio (CMRR) is provided only by the D2S, and can be written as [67]:

$$CMRR = A_D \cdot \frac{gm_{3,D2S}}{gds_{1,D2S} + gds_{3,D2S}} \tag{6}$$

where the small signal parameters refer to the inverters  $I_{1,D2S}$  and  $I_{3,D2S}$  in Fig. 7.

An important feature of the proposed OTA architecture is that, despite it can achieve high dc-gain, it does not require Miller compensation and can be compensated by a single large capacitive load. This is due to the low output resistance of the second stage of the proposed architecture, which results in a phase margin set by the value of the load capacitance  $C_L$  and by the sizing of the inverter  $I_O$ . In fact, it can be shown that the Gain Bandwidth Product (GBW) of the proposed OTA can be expressed as:

$$GBW = K \cdot \frac{gm_{4,D2S}}{2 \cdot gds_{4,D2S}} \cdot \frac{gm_o}{C_L}$$

(7)

Equation 7 confirms that the proposed three stage OTA exhibits just one internal high impedence node, at the output of the D2S, and an high impedance output node at the output of the OTA. The phase margin of the OTA can thus be expressed as:

$$m\varphi = 180 - \arctan\left\{GBW \cdot \frac{C_{in_1}}{gds_1 + gds_4}\right\} +$$

$$-\arctan\left\{GBW \cdot \frac{C_L}{gds_o}\right\}$$

(8)

FIGURE 8. Differential and Common Mode gain of the proposed OTA.

where  $C_{in_1}$  is the equivalent input capacitance of the K-Amplifier computed in Section II-B. According to Eq. 7 and 8, a minimum load capacitance has to be guaranteed in order to attain the phase margin required to assure the stability of the OTA. The subthreshold current of the NMOS and PMOS transistors of the generic inverter from the standard-cell library can be expressed as:

$$I_{d_n(p)} \approx I_{0n(p)} e^{\frac{|Vgs_{n(p)}| - |Vth_{n(p)}|}{nUt}}$$

(9)

where  $I_{0n(p)}$  can be written as:

$$I_{0n(p)} = \mu_{n(p)} \frac{W_{n(p)}}{L_{n(p)}} \sqrt{\frac{q\epsilon_{si}NDEP}{2\phi_s}} (k_B T/q)^2$$

(10)

where  $\mu_{n(p)}$  denotes the mobility of electrons (holes),  $W_{n(p)}$ ,  $L_{n(p)}$  are the widths and lengths of NMOS and PMOS of the inverter, q the electron charge, T denotes the absolute temperature, NDEP is the channel doping concentration,  $\epsilon_{si}$  is the dielectric constant of the silicon and  $\phi_s$  is the surface potential.

The positive slew and negative slew rate can then be derived as:

$$SR_p = \frac{I_{0p}}{C_L} e^{\frac{V_{DD} - Vth_p}{nUt}}; \quad SR_m = \frac{I_{0n}}{C_L} e^{\frac{V_{DD} - Vth_n}{nUt}}$$

(11)

where, defining with  $I_{0n(p)}^*$  the subthreshold current of the NMOS (PMOS) of the minimum sized inverter from the standard-cell library, it follows that the output slew rate will be K times the slew rate of the minimum sized standard-cell inverter, being  $I_{0n(p)} = KI_{0n(n)}^*$ .

## **IV. SIMULATION RESULTS**

## A. DESIGN FLOW AND NOMINAL SIMULATIONS

The proposed standard-cell-based OTA architecture exploiting the K-Amplifier whose schematic is reported in Fig. 6 has

|                                | TYP   | Mismatch |          | FF    | SS    | FS    | SF    | 0 deg  | 80 deg | $V_{DD} = 270mV$ | $V_{DD} = 330mV$ |  |

|--------------------------------|-------|----------|----------|-------|-------|-------|-------|--------|--------|------------------|------------------|--|

|                                |       |          | $\sigma$ | 11    |       |       |       |        | oo deg | VDD = 210miv     |                  |  |

| $P_D[nW]$                      | 6.63  | 6.86     | 0.401    | 25.23 | 1.565 | 12.15 | 6.16  | 1.828  | 47.47  | 4.396            | 10.43            |  |

| Offset [mV]                    | 0.234 | 0.1      | 4.71     | 0.223 | 0.229 | 3.40  | 0.068 | 0.2183 | 0.263  | 0.34             | 0.29             |  |

| Av [dB]                        | 73.52 | 73.48    | 2.078    | 69.87 | 79.57 | 74.90 | 69.63 | 75.07  | 70.67  | 72.4             | 74.34            |  |

| GBW [kHz]                      | 9.63  | 9.875    | 2.48     | 32.69 | 2.99  | 8.45  | 7.96  | 3.146  | 51.61  | 5.727            | 15.84            |  |

| mφ [deg]                       | 58.14 | 57.12    | 5.12     | 64.63 | 43    | 54.63 | 64.93 | 54.74  | 63.32  | 65.55            | 51.28            |  |

| CMRR [dB]                      | 42.01 | 37.11    | 9.81     | 39.87 | 42.57 | 31.10 | 43.40 | 42.24  | 40.26  | 37.81            | 43.75            |  |

| PSRR [dB]                      | 49.90 | 44.34    | 8.87     | 47.85 | 51.1  | 36.50 | 46.92 | 51.42  | 47.31  | 41.07            | 53.72            |  |

| IRN@1kHz [ $\mu V/\sqrt{Hz}$ ] | 0.969 | 0.970    | 23.38    | 0.702 | 0.914 | 0.963 | 1.75  | 1.42   | 0.715  | 1.049            | 0.869            |  |

| $SR_p$ [V/ms]                  | 0.146 | 0.146    | 0.011    | 0.757 | 0.022 | 0.038 | 0.540 | 0.050  | 0.669  | 0.062            | 0.112            |  |

| $SR_m$ [V/ms]                  | 0.429 | 0.448    | 0.098    | 3.25  | 0.172 | 0.084 | 0.351 | 0.162  | 1.98   | 0.229            | 0.335            |  |

TABLE 2. Performance of the OTA with respect to mismatch and process variations.

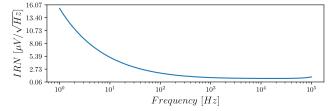

**FIGURE 9.** Equivalent input referred noise (IRN) in  $\mu V / \sqrt{Hz}$ .

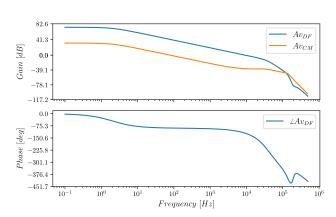

been designed in a 180nm CMOS technology utilizing the minimum size standard-cell inverter as the reference inverter, and assuming a nominal supply voltage  $V_{DD}$  of 0.3V, and K = 10 in all the three stages (see Fig. 6).

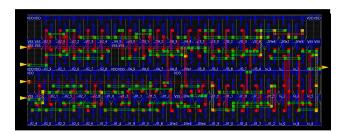

The circuit in Fig. 6 has been described in structural Verilog language and the Verilog netlist has been used to generate the layout by means of an automatic place and route flow for digital circuits in the Cadence Innovus environment. The layout of the proposed OTA resulting from the automatic place and route flow is reported in Fig. 11, with a layout area of 17.78  $\mu m$  x 47.46  $\mu m$ .

The differential-mode gain  $Av_{DF}$  and the common-mode gain  $Av_{CM}$  of the OTA are reported in Fig. 8. It is worth noting that  $Av_{DF}$  exceeds 70 dB, whereas  $Av_{CM}$  ensures a minimum CMRR of about 40 dB. The minimum load capacitance, considering 45 [deg] of phase margin is about 175 pF. The equivalent input referred noise (IRN) is depicted in Fig. 9. Its value at the corner frequency (of about 1 KHz) is  $969nV/\sqrt{Hz}$ .

# B. PVT AND MISMATCH PERFORMANCE CHARACTERIZATION

The main performance parameters under PVT and mismatch variations are summarized in Tab. 2. Notably, the voltage gain of the OTA is very stable under PVT and mismatch variations. Power consumption and GBW are dependent on the PVT conditions as in all standard-cell-based OTAs in which the bias current is not controlled.

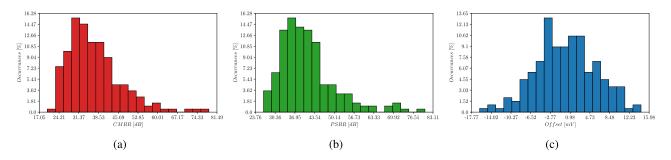

The OTA exhibits excellent offset performance under PVT and mismatch variations, with a standard deviation below 5 mV. This offset stability is primarily attributed to the implementation of a replica bias loop, as described in [55], which precisely sets the static output voltage of the standard-cells to  $V_{ref} = V_{DD}/2$ . In Fig. 10a it has been

depicted the CMRR vs mismatch variations and as it can be observed the mean value of the CMRR is about 37 dB whereas the standard deviation is about 9.78 dB. The worst case CMRR is about 20 dB whereas the best case is about 78.56 dB. For what concerns the power supply rejection ratio (PSRR), it is depicted in Fig. 10b. As it can be observed, the PSRR has a mean value of about 44.34 dB with a standard deviation of about 8.87 dB. The worst case for the PSRR is about 26.46 dB whereas its best case is about 80.41 dB. The offset under mismatch and PVT variations has been reported in Tab. 1 and depicted in Fig. 10c. As it can be observed, the standard deviation of the offset is lower than 4.71 mV. For what concerns the GBW under mismatch variations, values reported in Tab. 1 a mean value of 9.875 kHz whereas the standard deviation is about 2.48 kHz, with a best case and worst case respectively equal to 5.26 kHz and 17.4 kHz.

#### C. COMPARISON WITH THE LITERATURE

To compare the performance of OTAs, the small-signal and large-signal Figures of Merit ( $FOM_S$  and  $FOM_L$ ) are commonly adopted [33]. However, these metrics do not consider the amplifiers' area footprint, which is an essential aspect for a more comprehensive comparison. To address this limitation, the area-normalized  $FOM_{S,A}$  and  $FOM_{L,A}$  were proposed in [61]. These normalized FOMs are defined as:

$$FOM_{S,A} = \frac{GBW \cdot C_L}{P_D \cdot Area}; \quad FOM_{L,A} = \frac{SR_{avg} \cdot C_L}{P_D \cdot Area}$$

(12)

A comparison between recently published ULV OTAs is reported in Table 3, in which OTAs are classified in the fully synthesizable (Automatic Layout Flow Available) and not fully synthesizable (Automatic Layout Flow Not Available) categories. Notably, the proposed OTA achieves the highest dc-gain and the highest  $FOM_S$  and  $FOM_{S,A}$  values, with good overall performances. With respect to other works, it can be observed that only [68] reaches an higher gain, but it can be also observed that, with respect to a capacitance of about 8 times lower than the one driven by the proposed OTA, the GBW results about 4 times lower. This is the proof that, the proposed technique, results in an effective GBW enhancement with respect to a minimum load capacitance. Similar considerations follow for other OTAs depicted in Table 3.

FIGURE 10. CMRR a) PSRR b) and offset c) of the proposed K-Amplifier based OTA under mismatch variations.

**TABLE 3.** Comparison table.

|                                                                                               | Au         | ıtomatic Layou | ıt Flow Availal   | Automatic Layout Flow Not Available |                   |        |        |                   |       |

|-----------------------------------------------------------------------------------------------|------------|----------------|-------------------|-------------------------------------|-------------------|--------|--------|-------------------|-------|

|                                                                                               | This Work† | [65] †         | [67] <sup>†</sup> | [66] <sup>†</sup>                   | [69] <sup>†</sup> | [70]‡  | [32]†  | [61] <sup>‡</sup> | [68]‡ |

| Year                                                                                          | 2023       | 2023           | 2022              | 2022                                | 2023              | 2023   | 2022   | 2021              | 2020  |

| Technology [µm]                                                                               | 0.18       | 0.13           | 0.13              | 0.13                                | 0.028             | 0.13   | 0.13   | 0.18              | 0.18  |

| $V_{DD}$ [V]                                                                                  | 0.3        | 0.3            | 0.3               | 0.3                                 | 0.3               | 0.3    | 0.3    | 0.3               | 0.3   |

| $DC_{gain}$ [dB]                                                                              | 73.52      | 50.33          | 34.97             | 28.3                                | 66                | 86.83  | 52.92  | 30                | 64.7  |

| $C_L$ [pF]                                                                                    | 250        | 150            | 2                 | 1.5                                 | 250               |        | 50     | 150               | 30    |

| GBW [kHz]                                                                                     | 9.63       | 10.40k         | 12.69k            | 15.42k                              | 12.3              | 10.32  | 35.16  | 0.25              | 2.96  |

| $m\varphi$ [deg]                                                                              | 58.14      | 56.33          | 62.56             | 54                                  | 68                | 58.27  | 52.40  | 90                | 52    |

| $SR_p$ [V/ms]                                                                                 | 0.146      | 631.4          | 4.54k             | 9.08k                               | -                 | 2.32   | 18.61  | -                 | 1.9   |

| $SR_n$ [V/ms]                                                                                 | 0.429      | 811.3          | 6.82k             | 9.08k                               | -                 | 5.14   | 11.51  | -                 | 6.4   |

| $SR_{avg}$ [V/ms]                                                                             | 0.288      | 721.35         | 5.68k             | 9.08k                               | 3.2               | 3.73   | 15.06  | 0.085             | 4.15  |

| CMRR [dB]                                                                                     | 42.01      | 42.88          | 27.08             | 41.07                               | 105               | 57.80  | 42.11  | 41                | 110   |

| $P_D$ [nW]                                                                                    | 6.63       | 12.09k         | 6.10k             | 4.41k                               | 44                | 33.73  | 21.89  | 2.4               | 12.6  |

| Mode                                                                                          | STD-CELL   | STD-CELL       | STD-CELL          | STD-CELL                            | DIGITAL           | BD     | BD     | DIGITAL           | BD    |

| $FOM_S\left[\frac{MHz \cdot pF}{mW}\right]$                                                   | 363.12k    | 128.2k         | 4.16k             | 5.25k                               | 69.88k            | 10.70k | 80.29k | 15.89k            | 7.05k |

| $FOM_S\left[rac{MHz \cdot pF}{mW} ight] \ FOM_L\left[rac{V \cdot pF}{\mu s \cdot mW} ight]$ | 10.859k    | 8.949k         | 1.86k             | 3.09k                               | 18.18k            | 3.88k  | 34.40k | 5.40k             | 9.88k |

| $Area~[\mu m^2]$                                                                              | 844        | 598            | 217.85            | 164                                 | 625               | 2340   | 5200   | 982               | 8500  |

| $FOM_{S,A} \left[ \frac{MHz \cdot pF}{mW \cdot \mu m^2} \right]$                              | 430.23     | 214.38         | 19.10             | 32.01                               | 111.81            | 4.57   | 15.44  | 16.18             | 0.83  |

| $FOM_{L,A} \left[ \frac{V \cdot pF}{\mu s \cdot mW \cdot \mu m^2} \right]$                    | 12.87      | 14.96          | 8.54              | 18.84                               | 29.09             | 1.66   | 6.62   | 5.50              | 1.16  |

<sup>†</sup> Simulated; ‡Measured.

FIGURE 11. Layout of the proposed standard-cell-based OTA resulting from the automatic place and route flow.

## **V. CONCLUSION**

In this work an improved standard-cell-based voltage amplifier with low output resistance has been proposed. The proposed K-Amplifier cell exhibits a voltage gain whose value can be accurately set by the number of paralleled inverters, and its output static voltage is well controlled through a replica bias approach. A three stage fully synthesizable OTA architecture exploiting the improved voltage amplifier has also been presented. Due to the low output impedance of the K-Amplifier, the proposed three stage OTA can be compensated through a single large capacitance at the

output of the OTA. Simulation results in a 180nm CMOS process have demonstrated that, compared to previously published ULV OTAs, the proposed architecture achieves the highest Figures of Merit,  $FOM_S$  and  $FOM_{S,A}$ , while maintaining a consumption of merely 6.63 nW and a limited area footprint of 844  $\mu m^2$ . This underscores the effectiveness of the K-Amplifier, which significantly enhances the OTA's GBW by a factor of K, resulting in a  $FOM_S$  approximately 10 times higher than the ones reported by previous ULV OTAs in the literature.

## **REFERENCES**

- R. Want, B. N. Schilit, and S. Jenson, "Enabling the Internet of Things," *Computer*, vol. 48, no. 1, pp. 28–35, Jan. 2015.

- [2] P. Toledo, R. Rubino, F. Musolino, and P. Crovetti, "Re-thinking analog integrated circuits in digital terms: A new design concept for the IoT era," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 68, no. 3, pp. 816–822, Mar. 2021.

- [3] M. A. M. Vieira, C. N. Coelho, D. C. da Silva, and J. M. da Mata, "Survey on wireless sensor network devices," in *IEEE Conf. Emerg. Technol. Factory Automation. Proc.*, Sep. 2003, pp. 16–19.

- [4] F. Bastianini, S. Sedigh, G. Pascale, and G. Perri, "Cost-effective dynamic structural health monitoring with a compact and autonomous wireless sensor system," in *Proc. Non-Destructive Test. Mater. Struct. (NDTMS)*, Istanbul, Turkey, Sep. 2011, pp. 1065–1070.

- [5] B. Pradhan, S. Bhattacharyya, and K. Pal, "IoT-based applications in healthcare devices," *J. Healthcare Eng.*, vol. 2021, pp. 1–18, Mar. 2021.

- [6] P. Kumar and K. Silambarasan, "Enhancing the performance of healthcare service in IoT and cloud using optimized techniques," *IETE J. Res.*, vol. 68, no. 2, pp. 1475–1484, Mar. 2022.

- [7] E. McAdams, "Biomedical electrodes for biopotential monitoring and electrostimulation," in *Bio-Medical CMOS ICs* (Integrated Circuits and Systems), H. J. Yoo and C. van Hoof, Eds. Boston, MA, USA: Springer, 2011, doi: 10.1007/978-1-4419-6597-4\_3.

- [8] M. Healy, T. Newe, and E. Lewis, "Wireless sensor node hardware: A review," in *Proc. SENSORS IEEE*, Oct. 2008, pp. 621–624.

- [9] S. D. Glaser, "Some real-world applications of wireless sensor nodes," in *Proc. Smart Struct. Mater. Sensors Smart Struct. Technol. Civil, Mech. Aerosp. Syst.*, Jul. 2004, pp. 344–355.

- [10] C. Knight, J. Davidson, and S. Behrens, "Energy options for wireless sensor nodes," *Sensors*, vol. 8, no. 12, pp. 8037–8066, Dec. 2008.

- [11] T. Wu, J.-M. Redouté, and M. R. Yuce, "A wireless implantable sensor design with subcutaneous energy harvesting for long-term IoT healthcare applications," *IEEE Access*, vol. 6, pp. 35801–35808, 2018.

- [12] S. Lee, Q. Shi, and C. Lee, "From flexible electronics technology in the era of IoT and artificial intelligence toward future implanted body sensor networks," APL Mater., vol. 7, no. 3, Mar. 2019, Art. no. 031302.

- [13] A. Khanna, P. Selvaraj, D. Gupta, T. H. Sheikh, P. K. Pareek, and V. Shankar, "Internet of Things and deep learning enabled healthcare disease diagnosis using biomedical electrocardiogram signals," *Expert Syst.*, vol. 40, no. 4, May 2023, Art. no. e12864.

- [14] G. Xu, "IoT-assisted ECG monitoring framework with secure data transmission for health care applications," *IEEE Access*, vol. 8, pp. 74586–74594, 2020.

- [15] S. Khiani, M. Mohamed Iqbal, A. Dhakne, B. V. Sai Thrinath, P. Gayathri, and R. Thiagarajan, "An effectual IoT coupled EEG analysing model for continuous patient monitoring," *Meas. Sensors*, vol. 24, Dec. 2022, Art. no. 100597.

- [16] P. K. Yong and E. T. Wei Ho, "Streaming brain and physiological signal acquisition system for IoT neuroscience application," in *Proc. IEEE EMBS Conf. Biomed. Eng. Sci. (IECBES)*, Dec. 2016, pp. 752–757.

- [17] M. Jiang, T. N. Gia, A. Anzanpour, A.-M. Rahmani, T. Westerlund, S. Salanterä, P. Liljeberg, and H. Tenhunen, "IoT-based remote facial expression monitoring system with sEMG signal," in *Proc. IEEE Sensors Appl. Symp. (SAS)*, Apr. 2016, pp. 1–6.

- [18] T. Huertas and D. Mendez, "Biomedical IoT device for self-monitoring applications," in *Proc. VII Latin Amer. Congr. Biomed. Eng. (CLAIB), Bucaramanga, Santander, Colombia*, Singapore: Springer, Apr. 2017, pp. 357–360.

- [19] D. De, A. Mukherjee, S. K. Das, and N. Dey, "Wireless sensor network: Applications, challenges, and algorithms," in *Proc. Nature Inspired Comput. Wireless Sensor Netw.*, Singapore: Springer, Feb. 2020, pp. 1–18.

- [20] S. Ahmad Salehi, M. A. Razzaque, P. Naraei, and A. Farrokhtala, "Security in wireless sensor networks: Issues and challanges," in *Proc. IEEE Int. Conf. Space Sci. Commun. (IconSpace)*, Jul. 2013, pp. 356–360.

- [21] A.-S. Khan Pathan, H.-W. Lee, and C. Seon Hong, "Security in wireless sensor networks: Issues and challenges," 2007, arXiv:0712.4169.

- [22] T. Hiramoto, K. Takeuchi, T. Mizutani, A. Ueda, T. Saraya, M. Kobayashi, Y. Yamamoto, H. Makiyama, T. Yamashita, H. Oda, S. Kamohara, N. Sugii, and Y. Yamaguchi, "Ultra-low power and ultra-low voltage devices and circuits for IoT applications," in *Proc. IEEE Silicon Nanoelectronics Workshop (SNW)*, Jun. 2016, pp. 146–147.

- [23] I. Lee, D. Sylvester, and D. Blaauw, "A subthreshold voltage reference with scalable output voltage for low-power IoT systems," *IEEE J. Solid-State Circuits*, vol. 52, no. 5, pp. 1443–1449, May 2017.

- [24] M. A. Hannan, S. Mutashar, S. A. Samad, and A. Hussain, "Energy harvesting for the implantable biomedical devices: Issues and challenges," *Biomed. Eng. OnLine*, vol. 13, no. 1, pp. 1–23, Dec. 2014.

- [25] S. Panda, S. Hajra, K. Mistewicz, P. In-na, M. Sahu, P. M. Rajaitha, and H. J. Kim, "Piezoelectric energy harvesting systems for biomedical applications," *Nano Energy*, vol. 100, Sep. 2022, Art. no. 107514.

- [26] J. Selvarathinam and A. Anpalagan, "Energy harvesting from the human body for biomedical applications," *IEEE Potentials*, vol. 35, no. 6, pp. 6–12, Nov. 2016.

- [27] L. S. Y. Wong, S. Hossain, A. Ta, J. Edvinsson, D. H. Rivas, and H. Naas, "A very low-power CMOS mixed-signal IC for implantable pacemaker applications," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2446–2456, Dec. 2004.

- [28] N. Garg and R. Garg, "Energy harvesting in IoT devices: A survey," in Proc. Int. Conf. Intell. Sustain. Syst. (ICISS), Dec. 2017, pp. 127–131.

- [29] F. Centurelli, A. Fava, P. Monsurrò, G. Scotti, P. Tommasino, and A. Trifiletti, "Low power switched-resistor band-pass filter for neural recording channels in 130nm CMOS," *Heliyon*, vol. 6, no. 8, Aug. 2020, Art. no. e04723.

- [30] T. Sanislav, G. D. Mois, S. Zeadally, and S. C. Folea, "Energy harvesting techniques for Internet of Things (IoT)," *IEEE Access*, vol. 9, pp. 39530–39549, 2021.

- [31] H. Elahi, K. Munir, M. Eugeni, S. Atek, and P. Gaudenzi, "Energy harvesting towards self-powered IoT devices," *Energies*, vol. 13, no. 21, p. 5528, Oct. 2020.

- [32] F. Centurelli, R. Della Sala, P. Monsurrò, G. Scotti, and A. Trifiletti, "A tree-based architecture for high-performance ultra-low-voltage amplifiers," *J. Low Power Electron. Appl.*, vol. 12, no. 1, p. 12, Feb. 2022.

- [33] T. Kulej and F. Khateb, "A 0.3-V 98-dB rail-to-rail OTA in 0.18  $\mu$  m CMOS," *IEEE Access*, vol. 8, pp. 27459–27467, 2020.

- [34] T. Kulej, F. Khateb, D. Arbet, and V. Stopjakova, "A 0.3-V high linear rail-to-rail bulk-driven OTA in 0.13 μm CMOS," *IEEE Trans. Circuits Syst. II*, Exp. Briefs, vol. 69, no. 4, pp. 2046–2050, Apr. 2022.

- [35] L. H. Rodovalho, O. Aiello, and C. R. Rodrigues, "Ultra-Low-Voltage inverter-based operational transconductance amplifiers with voltage gain enhancement by improved composite transistors," *Electronics*, vol. 9, no. 9, p. 1410, Sep. 2020.

- [36] T. Kulej and F. Khateb, "Design and implementation of sub 0.5-V OTAs in 0.18-μm CMOS," *Int. J. Circuit Theory Appl.*, vol. 46, no. 6, pp. 1129–1143, Jun. 2018.

- [37] T. Kulej, "0.5-V bulk-driven CMOS operational amplifier," *IET Circuits*, *Devices Syst.*, vol. 7, no. 6, pp. 352–360, Nov. 2013.

- [38] T. Kulej, "0.5-V bulk-driven OTA and its applications," *Int. J. Circuit Theory Appl.*, vol. 43, no. 2, pp. 187–204, Feb. 2015.

- [39] F. Khateb, T. Kulej, M. Kumngern, D. Arbet, and W. Jaikla, "A 0.5-V 95-dB rail-to-rail DDA for biosignal processing," AEU-Int. J. Electron. Commun., vol. 145, Feb. 2022, Art. no. 154098.

- [40] R. D. Sala, C. Bocciarelli, F. Centurelli, V. Spinogatti, and A. Trifiletti, "A novel ultra-low voltage fully synthesizable comparator exploiting NAND gates," in *Proc. 18th Conf. Ph. D Res. Microelectron. Electron.* (PRIME), Jun. 2023, pp. 21–24.

- [41] O. Aiello, P. Crovetti, and M. Alioto, "Fully synthesizable low-area analogue-to-digital converters with minimal design effort based on the dyadic digital pulse modulation," *IEEE Access*, vol. 8, pp. 70890–70899, 2020

- [42] O. Aiello, P. Crovetti, P. Toledo, and M. Alioto, "Rail-to-rail dynamic voltage comparator scalable down to pW-range power and 0.15-V supply," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 68, no. 7, pp. 2675–2679, Jul. 2021.

- [43] R. D. Sala, F. Centurelli, G. Scotti, P. Tommasino, and A. Trifiletti, "A differential-to-single-ended converter based on enhanced body-driven current mirrors targeting ultra-low-voltage OTAs," *Electronics*, vol. 11, no. 23, p. 3838, Nov. 2022.

- [44] T. Kulej, "0.4-V bulk-driven operational amplifier with improved input stage," *Circuits, Syst. Signal Process.*, vol. 34, no. 4, pp. 1167–1185, Apr. 2015.

- [45] T. Kulej and F. Khateb, "0.4-V bulk-driven differential-difference amplifier," *Microelectron. J.*, vol. 46, no. 5, pp. 362–369, May 2015.

- [46] F. Centurelli, R. D. Sala, P. Monsurrò, G. Scotti, and A. Trifiletti, "A novel OTA architecture exploiting current gain stages to boost bandwidth and slew-rate," *Electronics*, vol. 10, no. 14, p. 1638, Jul. 2021.

- [47] L. H. Rodovalho, C. R. Rodrigues, and O. Aiello, "Self-biased and supply-voltage scalable inverter-based operational transconductance amplifier with improved composite transistors," *Electronics*, vol. 10, no. 8, p. 935, Apr. 2021.

- [48] X. Fu, K. El-Sankary, and Y. Yin, "A high-performance OTA with hybrid of inverter-based OTA and nauta OTA for high speed applications," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2021, pp. 1–5.

- [49] P. C. C. Aguirre and A. A. Susin, "PVT compensated inverter-based OTA for low-voltage CT sigma-delta modulators," *Electron. Lett.*, vol. 54, no. 22, pp. 1264–1266, Nov. 2018.

- [50] H. Barthélemy, S. Meillère, J. Gaubert, N. Dehaese, and S. Bourdel, "OTA based on CMOS inverters and application in the design of tunable bandpass filter," *Anal. Integr. Circuits Signal Process.*, vol. 57, no. 3, pp. 169–178, Dec. 2008.

- [51] L. Lv, X. Zhou, Z. Qiao, and Q. Li, "Inverter-based subthreshold amplifier techniques and their application in 0.3-V ΔΣ -Modulators," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1436–1445, May 2019.

- [52] R. A. S. Braga, L. H. C. Ferreira, G. D. Coletta, and O. O. Dutra, "A 0.25-V calibration-less inverter-based OTA for low-frequency G-C applications," *Microelectron. J.*, vol. 83, pp. 62–72, Jan. 2019.

- [53] A. Ismail and I. Mostafa, "A process-tolerant, low-voltage, inverter-based OTA for continuous-time," *IEEE Trans. Very Large Scale Integr. VLSI Syst.*, vol. 24, no. 9, pp. 2911–2917, Feb. 2016.

- [54] F. Centurelli, G. Giustolisi, S. Pennisi, and G. Scotti, "A biasing approach to design ultra-low-power standard-cell-based analog building blocks for nanometer SoCs," *IEEE Access*, vol. 10, pp. 25892–25900, 2022.

- [55] R. Della Sala, F. Centurelli, and G. Scotti, "Enabling ULV fully synthesizable analog circuits: The BA cell, a standard-cell-based building block for analog design," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 12, pp. 4689–4693, Dec. 2022.

- [56] A. Correia, V. G. Tavares, P. Barquinha, and J. Goes, "All-standard-cell-based analog-to-digital architectures well-suited for Internet of Things applications," *J. Low Power Electron. Appl.*, vol. 12, no. 4, p. 64, Dec. 2022.

- [57] O. Aiello, P. Crovetti, and M. Alioto, "Standard cell-based ultra-compact DACs in 40-nm CMOS," *IEEE Access*, vol. 7, pp. 126479–126488, 2019.

- [58] L. Sood and A. Agarwal, "A CMOS standard-cell based fully-synthesizable low-dropout regulator for ultra-low power applications," AEU - Int. J. Electron. Commun., vol. 141, Nov. 2021, Art. no. 153958.

- [59] J. Liu, B. Park, M. Guzman, A. Fahmy, T. Kim, and N. Maghari, "A fully synthesized 77-dB SFDR reprogrammable SRMC filter using digital standard cells," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 26, no. 6, pp. 1126–1138, Jun. 2018.

- [60] P. Toledo, P. S. Crovetti, H. D. Klimach, F. Musolino, and S. Bampi, "Low-voltage, low-area, nW-power CMOS digital-based biosignal amplifier," *IEEE Access*, vol. 10, pp. 44106–44115, 2022.

- [61] P. Toledo, P. Crovetti, O. Aiello, and M. Alioto, "Design of digital OTAs with operation down to 0.3 V and nW power for direct harvesting," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 68, no. 9, pp. 3693–3706, Sep. 2021.

- [62] G. Palumbo and G. Scotti, "A novel standard-cell-based implementation of the digital OTA suitable for automatic place and route," J. Low Power Electron. Appl., vol. 11, no. 4, p. 42, Oct. 2021.

- [63] P. Toledo, O. Aiello, and P. S. Crovetti, "A 300 mV-supply standard-cell-based OTA with digital PWM offset calibration," in *Proc. IEEE Nordic Circuits Syst. Conf. (NORCAS)*, *NORCHIP Int. Symp. System-on-Chip (SoC)*, Oct. 2019, pp. 1–5.

- [64] P. Toledo, P. Crovetti, H. Klimach, and S. Bampi, "Dynamic and static calibration of ultra-low-voltage, digital-based operational transconductance amplifiers," *Electronics*, vol. 9, no. 6, p. 983, Jun. 2020.

- [65] R. D. Sala, F. Centurelli, and G. Scotti, "A high performance 0.3 V standard-cell-based OTA suitable for automatic layout flow," *Appl. Sci.*, vol. 13, no. 9, p. 5517, Apr. 2023.

- [66] F. Centurelli, R. D. Sala, and G. Scotti, "A standard-cell-based CMFB for fully synthesizable OTAs," *J. Low Power Electron. Appl.*, vol. 12, no. 2, p. 27, May 2022.

- [67] R. D. Sala, F. Centurelli, and G. Scotti, "A novel differential to single-ended converter for ultra-low-voltage inverter-based OTAs," *IEEE Access*, vol. 10, pp. 98179–98190, 2022.

- [68] T. Kulej and F. Khateb, "A compact 0.3-V class AB bulk-driven OTA," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 28, no. 1, pp. 224–232, Jan. 2020.

- [69] M. Privitera, P. Crovetti, and A. D. Grasso, "A novel digital OTA topology with 66-dB DC gain and 12.3-kHz bandwidth," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 70, no. 11, pp. 3988–3992, Nov. 2023, doi: 10.1109/TCSII.2023.3283566.

- [70] R. D. Sala, F. Centurelli, P. Monsurrò, G. Scotti, and A. Trifiletti, "A 0.3 V rail-to-rail three-stage OTA with high DC gain and improved robustness to PVT variations," *IEEE Access*, vol. 11, pp. 19635–19644, 2023.

RICCARDO DELLA SALA was born in Naples, in 1996. He received the bachelor's and M.S. degrees (summa cum laude) in electronics engineering and the Ph.D. degree from the University of Rome "La Sapienza," Italy, in 2018, 2020, and November 2023, respectively. In November 2023, he holds the position of a Research Fellow with the Sapienza University of Rome. He has coauthored more than 30 publications in international journals and conference proceedings. His primary research

interests include designing and developing PUFs and TRNGs for hardware security both on ASIC and FPGA, ultra-low voltage, ultra-low power topologies for IoT, and biomedical applications within the context of analog design. This involves standard-cell based architectures for fully synthesizable designs, including OTAs, comparators, filters, and ADCs.

FRANCESCO CENTURELLI (Senior Member, IEEE) was born in Rome, in 1971. He received the Laurea (cum laude) and Ph.D. degrees in electronic engineering from Sapienza Universită di Roma, Rome, Italy, in 1995 and 2000, respectively. In 2006, he became an Assistant Professor with the DIET Department, Sapienza Universită di Roma. He has been also involved in research and development activities held in collaboration between Sapienza Universită di Roma and some industrial

partners. He has published more than 140 papers on international journals and refereed conferences. His research interests include system-level analysis and the design of clock recovery circuits and high-speed analog integrated circuits, now concern the design of analog-to-digital converters, and very low-voltage circuits for analog and RF applications.

GIUSEPPE SCOTTI (Senior Member, IEEE) received the M.S. and Ph.D. degrees in electronic engineering from the University of Rome "La Sapienza," Italy, in 1999 and 2003, respectively. In 2010, he became a Researcher (Assistant Professor) with the DIET Department, University of Rome "La Sapienza" and an appointed Associate Professor with the DIET Department, in 2015. His research interests include integrated circuits design and focused on design method-

ologies able to guarantee robustness with respect to parameter variations in both analog circuits and digital VLSI circuits. In the context of cryptographic hardware his focus has been on novel PAAs methodologies and countermeasures. He has coauthored more than 60 publications in international journals, about 70 contributions in conference proceedings, and is the co-inventor of two international patents.

• •

Open Access funding provided by 'Università degli Studi di Roma "La Sapienza" 2' within the CRUI CARE Agreement