Received 4 December 2023, accepted 30 December 2023, date of publication 8 January 2024, date of current version 18 January 2024.

Digital Object Identifier 10.1109/ACCESS.2024.3350779

# **RESEARCH ARTICLE**

# Benchmarking of Multi-Bridge-Channel FETs Toward Analog and Mixed-Mode Circuit Applications

VAKKALAKULA BHARATH SREENIVASULU<sup>®1</sup>, (Member, IEEE), ARUNA KUMARI NEELAM<sup>®2</sup>, (Member, IEEE), ASISA KUMAR PANIGRAHY<sup>®3</sup>, LOKESH VAKKALAKULA<sup>4</sup>, (Member, IEEE), JAWAR SINGH<sup>®5</sup>, (Senior Member, IEEE), AND SHIV GOVIND SINGH<sup>®6</sup>, (Senior Member, IEEE)

<sup>1</sup>School of Electronics and Communication Engineering, REVA University, Bengaluru, Karnataka 632014, India

<sup>2</sup>School of Electronics Engineering, Vellore Institute of Technology, Vellore 632014, India

<sup>3</sup>Department of ECE, Faculty of Science and Technology (Icfaitech), ICFAI Foundation for Higher Education, Hyderabad 501203, India

<sup>4</sup>Bosch Global Software Technologies, Bengaluru, Karnataka 632014, India <sup>5</sup>Department of Electrical Engineering, Indian Institute of Technology Patna, Patna 801106, India

<sup>6</sup>Department of Electrical Engineering, Indian Institute of Technology Hyderabad, Hyderabad 502285, India

Corresponding author: Asisa Kumar Panigrahy (asisa@ifheindia.org)

**ABSTRACT** In this study, for the very first time developing of n- and p-type 3-D single-channel (SC) FinFET and gate-all-around (GAA) Multi-Bridge-Channel FETs (MBCFET) like nanowire FET (NWFET) and nanosheet FET (NSFET) are benchmarked towards device and circuit levels which are emulated with International Road map for Devices and Systems (IRDS) for sub-5-nm technology nodes. Compared to the FinFET, the MBCFETs exhibits higher ON-current  $(I_{ON})$ , switching ratio  $(I_{ON}/I_{OFF})$ , lower subthresholdswing (SS) and drain-induced barrier lowering (DIBL). Except for extended parasitic capacitances ( $C_{\text{para}}$ ), our benchmarking results show that the NWFET and NSFET achieve the high-performance (HP) and low-power (LP) goals of IRDS. Furthermore, the NSFET delivers superior performance towards DC and analog/RF metrics. The cut-off frequency ( $f_T$ ) and gain bandwidth product (GBW) are higher (because of high  $I_{\rm ON}$  in the case of NSFET, even though the capacitive effect is significant. Further, the logic circuit applications like CMOS inverter and ring oscillator (RO) circuits are analyzed and compared in detail. The CMOS inverters propagation delays ( $\tau_p$ ) is reduced to 31% from FinFET to NWFET and 12% from NWFET to NSFETs is noticed. Also, the NWFET and NSFET based ROs offer 39% and 56% high oscillation frequency ( $f_{osc}$ ) compared to that of FinFET counterpart. Finally, the single stage current mirror performance and operational transconductance amplifiers (OTA) gain and common mode rejection ratio (CMRR) are carried out towards analog and mixed-mode circuit applications.

**INDEX TERMS** CMRR, CMOS inverter, IRDS, GAAFET, operational transconductance amplifier (OTA), ring oscillator.

### I. INTRODUCTION

The FinFET became the promising architecture at sub-22-nm nodes as it offered robust gate control over the channel and enabled scaling to the 7-nm technology node. Also, the FinFET played a remarkable role in high-performance (HP) applications. The FinFETs are still being used and more

prominently used at the 7-nm technology node, as per the foundry publications (N7) [1], [2]. However, it is shown that the FinFET is incapable of downscaling further as it became challenging to maintain the device's electrostatic control in future technology nodes. To maintain good electrostatics, a thinner fin is necessary. However, this reduces carrier mobility and causes threshold voltage ( $V_{th}$ ) fluctuation [3], [4], [5]. The GAA Multi-Bridge-Channel FET (MBCFET) [4] like nanowire FET and nanosheet

The associate editor coordinating the review of this manuscript and approving it for publication was Shuo Sun.

FET (NSFET) architectures emerged as potential candidates for sub-5-nm nodes to improve the performance [6], [7], [8], [9], [10], [11]. Therefore, physically based 3D simulations are essential for assessing the performance of these devices. The GAA NWFET exhibits superior electrostatic integrity at sub-5-nm nodes. However, due to the reduced channel area, the drive current is limited in NWFET and restricts its usage for HP applications. In 2017, IBM proposed the construction of stacked NSFETs, which outperformed FinFETs and stacked NWFETs [12]. For a given active width, NSFETs may have a smaller parasitic capacitance, resulting in a better  $C_{\rm eff}$ - $I_{\rm eff}$  relationship. Hence, for scaling sub-5-nm technology nodes, NSFET emerged as a viable contender [12]. Meanwhile, silicon (Si) NSFET has been established to improve effective channel widths  $(W_{eff})$  for higher current drivability while ensuring optimum electrostatics through gate-all-around (GAA) architecture. Moreover, NSFET modulates the drive current by varying NS width, which allows CMOS layout compatibility designs [13]. Although some works compared FinFET, NW and NSFET with a single channel [14], three-channel [15], [16], four-channel [17], two-channel (Bulk and SOI) [18], [19], however very few have compared FinFET, nanowire and two-channel SOI NSFET with equal effective widths (i.e., same area or equal footprint) for sub-5-nm nodes towards IRDS goals in the literature for both p- and n-type FETs. In GAA FETs with multiple vertically stacked silicon NWFET and NSFET, the desired performance in DC, analog, and RF applications can be achieved [14], [15]. Although three, four, five and more channel NSFETs have larger I<sub>ON</sub> than the FinFETs, due to their larger effective width  $(W_{eff})$ , it will degrade the gate capacitance  $(C_{gg})$ , overlap, and outer-fringing capacitances arising from more channels [20]. Thus, in the proposed design, two-channel NSFET is focused for sub-5-nm nodes. Moreover, GAA NSFETs is a transition step between FinFET and NWFET designs because of their higher performance and adaptive minimal fabrication technique [16]. Additionally, NSFETs have also been developed to improve the  $W_{\rm eff}$  of channels, enabling larger current drivability under an equal footprint while retaining good electrostatics [17], [18], [19]. The NSFET's broader design compared to the NW enables better transistor performance at higher power levels. [20].

Several works devoted to study the performance of Fin-FET, NW and NSFETs like *I-V* characteristics of bulk [21] and SOI [22], [23] FinFET, NW, and NSFET architectures. However, the p- and n-type FETs benchmark comparison by keeping in view of 2025 International Roadmap for Devices and Systems (IRDS) goals [24] towards DC and analog/RF performance needs to be explored in detail for sub-2-nm nodes. Thus, in this study, both p- and n-type FETs are designed for FinFET, NW and NSFET architectures with equal  $W_{\text{eff}}$ . Moreover, to analyze analog and mixed-mode circuit behavior of emerging FETs at sub-5-nm technology nodes we show the CMOS inverter propagation delay ( $\tau$ ), switching current ( $I_{\text{SC}}$ ), energy-delay product (EDP), powerdelay product (PDP) and the ring oscillator (RO) frequency

#### TABLE 1. Device parameters.

| Device Parameter                    | FinFET                                | NWFET                              | NSFET              |  |

|-------------------------------------|---------------------------------------|------------------------------------|--------------------|--|

| Gate Length $(L_G)$                 | 16 nm                                 | 16 nm                              | 16 nm              |  |

| Fw/NWw/NSw                          | 6 nm                                  | 7 nm                               | 10 nm              |  |

| Channel height                      | 27 nm                                 | 8 nm                               | 5 nm               |  |

| $(F_{\rm H}/NW_{\rm T}/NS_{\rm T})$ |                                       |                                    |                    |  |

| EOT                                 | 0.78 nm                               | 0.78 nm                            | 0.78 nm            |  |

| Spacer dielectric                   | Nitride                               | Nitride                            | Nitride            |  |

| Source/drain Length                 | 12 nm                                 | 12 nm                              | 12 nm              |  |

| (L)                                 |                                       |                                    |                    |  |

| Length of underlap                  | 5 nm                                  | 5 nm                               | 5 nm               |  |

| spacer                              |                                       |                                    |                    |  |

| Source/drain doping                 | $2 \times 10^{19} \text{ cm}^{-3}$    | $2 \times 10^{19} \text{ cm}^{-3}$ | $2 \times 10^{19}$ |  |

|                                     |                                       |                                    | cm <sup>-3</sup>   |  |

| Channel doping                      | 1 × 10 <sup>15</sup> cm <sup>-3</sup> | $1 \times 10^{15} \text{ cm}^{-3}$ | $1 \times 10^{15}$ |  |

|                                     |                                       |                                    | cm <sup>-3</sup>   |  |

| Effective Width $(W_{eff})$         | 60 nm                                 | 60 nm                              | 60 nm              |  |

| Gate work function                  | 4.685 eV                              | 4.47 eV                            | 4.456 eV           |  |

of oscillation ( $f_{OSC}$ ) performance for the first time. The manuscript is constructed as follows: The device dimensions and physical models are demonstrated in section II. In section III, DC and analog/RF FOMs comparison is performed for FinFET, NWFET, and NSFET. Section IV describes the circuit level comparison of FinFET, NW and NSFETs and benchmarking with IRDS. Section V describes the conclusion of the results and performances.

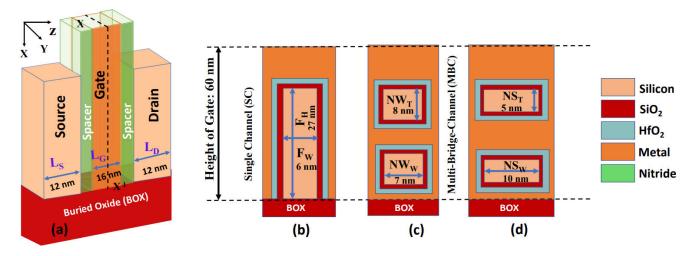

# II. DEVICE STRUCTURE AND SUMULATION METHODOLOGY

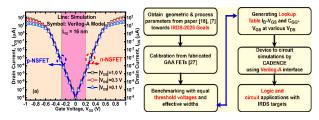

All the results of FinFET, NWFET and NSFET are simulated through the Cogenda Visual TCAD simulator 25. Table. 1 lists the device characteristics and dimensions that were employed in the simulations. A gate length of 16 nm is predicted to fall under sub-5-nm technology node range by IRDS 2025 [24] targets. For FinFET a channel height of 27 nm and fin width of 6 nm is chosen, which cannot be scaled beyond 7-nm-node due to severe fin bending issues [18]. An optimized width of 6 nm for FinFET and 7 nm width for NWFET are considered towards larger saturation currents [18]. For NSFET an optimized height of 5 nm and 10 nm width is considered accordance with [7]. For a better comparison an equal Vth of 275 mV is maintained, near to IRDS 2025 target  $(\sim 212 \text{ mV})$  by tuning gate work function. The effective widths ( $W_{eff}$ ) of p- and n-type of FinFET ( $W_{eff} = 2F_H + F_W$ ), NWFET ( $W_{eff} = 2 \times (2NW_W + 2NW_H)$ ) and NSFETs ( $W_{eff} =$  $2 \times (2NS_W + 2NS_H))$  [26] are maintained equal of 60 nm. All the structures are maintained an EOT of 0.78 nm with a highk gate stack combination with  $SiO_2$  and  $HfO_2$ . The doping of  $2 \times 10^{19}$  cm<sup>-3</sup> in source and drain and  $1 \times 10^{15}$  cm<sup>-3</sup> for the channel is considered for both n and p-type FETs.

An equal metal gate height of 60 nm is taken for Fin-FET, NW, and NSFETs. The spacers are fundamental to improve the subthreshold performance and are a prerequisite for sub-10-nm devices [26]. Due to the closer proximity of the source and drain contacts in the sub-20-nm region, the electrical behaviour of FETs starts to deteriorate. With higher DIBL, the gate has inadequate control on the channel region,

FIGURE 1. (a) 3-D schematic and 2-D cut views of (b) FinFET (c) NWFET and (d) NSFET (MBCFET).

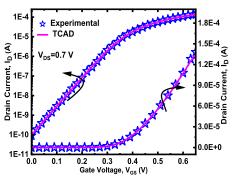

FIGURE 2. The calibration of TCAD simulation models with the experimental results of NSFET (MBCFET).

resulting in higher I<sub>OFF</sub>, lower I<sub>ON</sub>, lower I<sub>ON</sub>/I<sub>OFF</sub>, and SS deterioration [26]. The proposed FinFET, NWFET and NSFETs are maintained with nitride spacer to mitigate series resistance and parasitic capacitance effects [26]. The simulation of a 3D quantum-mechanically corrected device is carried out in detail by solving a series of density-gradient drift-diffusion equations. To account for carriers' lifetime and current densities, the Auger model is invoked. To consider generation and recombination effects, Shockley-Read-Hall models are incorporated. To account for bandgap narrowing effects due to heavy doping, Schenk's model and for velocity saturation effects, Caughey-Thomas models are involved. All the device parameters are initially validated through the non-equilibrium Greens function approach. To consider interface mobility degradation phenomena, the thin-layer mobility model is invoked. Fig. 2 depicts the calibration of transfer characteristics of the MBC GAA NSFET with the Visual TCAD simulation approach [27]. In addition, the NWFET is well also well calibrated with experimental results of [5] and shown in our recent works [3]. For gate and drain voltages, the simulated  $I_{\rm D}-V_{\rm GS}$  curve shows a good match with the experiment results. This demonstration ensures that the simulation analysis effectively captures the NSFETs short channel physics.

#### **III. RESULT ANALYSIS AND DISCUSSION**

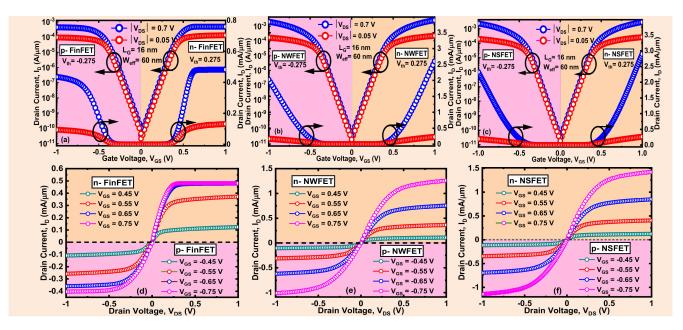

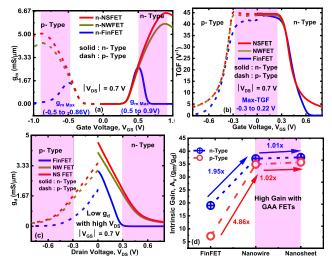

Fig. 3(a)-(c) show the  $I_{\rm D}$ - $V_{\rm GS}$  characteristics of FinFET, NW, and NSFET in log and linear scale at  $|V_{\rm DS}| = 0.7$  V and  $|V_{\rm DS}| = 0.05$  V for both n- and p-type FETs. For a fair comparison, the  $V_{\rm th}$  of FinFET, NWFET and NSFETs are matched by modifying the gate work function. Fig 3(d)-(f) show the  $I_{\rm D}$ - $V_{\rm DS}$  characteristics of FinFET, NW, and NSFET at various  $V_{\rm GS}$ . The NSFET exhibits the highest output characteristics, followed by NWFET and FinFET.

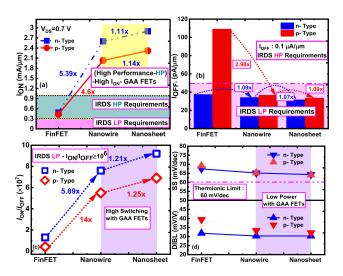

A comparison of I<sub>ON</sub>, I<sub>OFF</sub>, I<sub>ON</sub>/I<sub>OFF</sub> for p and n-type FinFET, NWFET, and NSFETs are depicted in Fig. 4. The  $I_{\rm ON}$  is extracted at  $V_{\rm DS} = V_{\rm GS} = 0.7$  V for n-type FETs and  $V_{\rm DS} = V_{\rm GS} = -0.7$  V for p-type FETs. Figure 4(a) shows that n-type NWFET and NSFET exhibit higher modulation in I<sub>ON</sub> compared to FinFET. The  $I_{ON}$  of 0.482 mA/ $\mu$ m, 2.6 mA/ $\mu$ m, and 2.9 mA/ $\mu$ m with n-type FETs and 0.435 mA/ $\mu$ m, 2.03 mA/ $\mu$ m, and 2.32 mA/ $\mu$ m with p-type FETs are noticed with FinFET, NWFET, and NSFETs respectively. Moreover, compared to p-type FETs, the n-type FETs exhibit better  $I_{\rm ON}$  due to better electron mobility. The NWFET exhibits a rise in  $I_{ON}$  of 5.39× with n-type and 4.6× with p-type compared to FinFET. Moreover, from NWFET to NSFET, a marginal rise in  $I_{ON}$  of  $1.1 \times$  with n-type and  $1.14 \times$  with p-type is observed. Both NW and NSFETs exhibit better ION compared to IRDS HP requirements. Furthermore, the FinFET, NWFET, and NSFETs show better performance compared to IRDS LP requirements. Figure 4(b) shows the IOFF with p- and n-type FinFET, NW, and NSFETs. The  $I_{\text{OFF}}$  of 37.3 pA/ $\mu$ m, 34 pA/ $\mu$ m, and 31.5 pA/ $\mu$ m with n-type FETs and 109 pA/ $\mu$ m, 36.5 pA/ $\mu$ m, 33.3 pA/ $\mu$ m with p-type FETs is noticed. The variation in IOFF is higher for FinFET compared to NWFET and NSFETs due to trigate nature. Moreover, higher gate drain induced drain leakage for p-type FETs at low  $V_{GS}$  is due to higher junction gradient of boron penetrating/diffusing into FinFET, NWFET and NSFET channels [13]. A fall of  $1.09 \times$  with p-type and  $2.98 \times$  with n-type is noticed from FinFET to NW. Furthermore,  $1.07 \times$  with n-type and  $1.09 \times$  p-type from NW to

FIGURE 3. (a, b and c) Transfer characteristics (I<sub>D</sub>-V<sub>GS</sub>) (d, e and f) Output characteristics (I<sub>D</sub>-V<sub>DS</sub>) of FinFET, NW and NSFET (MBCFET).

FIGURE 4. (a)  $I_{\rm OFF}$  (b)  $I_{\rm OFF}$  (c)  $I_{\rm ON}/I_{\rm OFF}$  (d) SS and DIBL of FinFET, NW and NSFET (MBCFET).

NSFET is noticed. Except for p-type FinFET, the  $I_{OFF}$  shows better performance with NWFET and NSFETs compared to IRDS LP requirements. Figure 4(c) depicts the  $I_{ON}/I_{OFF}$ ratio of FinFET, and NWFET and NSFETs at  $V_{DS} = 0.7$  V. An  $I_{ON}/I_{OFF}$  ratio of  $1.29 \times 10^7$ ,  $7.6 \times 10^7$ , and  $9.2 \times 10^7$  with n-type and  $3.9 \times 10^6$ ,  $5.5 \times 10^7$ , and  $6.9 \times 10^7$  with p-type are obtained with FinFET, NWFET and NSFET respectively. The NWFET and NSFET exhibit the highest  $I_{ON}/I_{OFF}$  ratio with n-type FET. Even for FinFET, the  $I_{ON}/I_{OFF} > 10^7$  is possible due to higher work function of 4.6 e V is considered while matching threshold voltages ( $V_{th}$ ) with NWFET and NSFET. The SS and DIBL are the fundamental DC metrics to estimate subthreshold performance at lower technology nodes. The expressions for DIBL and SS are [26]:

$$DIBL(mV/V) = \left| \frac{V_{th1} - V_{th2}}{V_{DS1} - V_{DS2}} \right|$$

(1)

$$SS = \left[\frac{\partial \log_{10}I_D}{\partial V_{GS}}\right]^{-1} \tag{2}$$

The DIBL is calculated by using (1), where  $V_{th1}$  and  $V_{th2}$  are the threshold voltages extracted at  $V_{DS}$  of 0.7 V and 0.05 V, respectively, at N×( $W_{eff}/L_G$ ) × 10<sup>-7</sup> A using the constant current method, where 'N' denotes the number of channels. As evident from Fig 4(d), the NWFET and NSFETs show a fall in SS and DIBL with p- and n-type compared to FinFET due to better electrostatic integrity by GAA architecture. Both GAA NWFET and NSFETs exhibit SS near to thermionic limit of 60 mV/dec.

The various analog/RF performance metrics of FinFET, NWFET, and NSFETs are compared for both p- and n-type FETs. The transconductance  $(g_m)$  is considered as one of the crucial analog metrics for device evaluation, which relates the change in drain current to the corresponding change in  $V_{GS}$ . The  $g_m$  is a measure of the device speed and higher  $g_m$  values are preferred for better performance of logic operations. Moreover, for devices with higher  $g_m$ , the gate transfer efficiency will be high. Furthermore, the amplifying capacity of the device is also determined by  $g_m$ . From figure 5(a), it is noticed that NSFET exhibits the highest  $g_m$ compared to NWFET and FinFET. The device offers a  $g_{mMax}$ of 2.63 mS/ $\mu$ m, 5.75 mS/ $\mu$ m, and 6.53 mS/ $\mu$ m with n-type FETs, and 1.51 mS/ $\mu$ m, 4.38 mS/ $\mu$ m, and 5.04 mS/ $\mu$ m with p-type FETs for FinFET, NWFET, and NSFETs respectively. Compared to p-type FETs, the n-type FETs exhibit better  $g_m$  and ensures better gain and amplifying capabilities.

**FIGURE 5.** (a)  $g_m$  (b) TGF (c)  $g_d$  (d)  $A_V$  of p and n-type FinFET, NW and NSFET (MBCFET).

A maximum operating voltage of  $g_m$  to obtain the highest gain  $(A_V)$  is found around 0.5 to 0.9 V for n-type and around -0.5 to -0.86 V for p-type NWFET and NSFETs, respectively. The transconductance generation factor (TGF) =  $g_m/I_D$  of a device determines how well a drain current is used to achieve an acceptable  $g_m$  and accessible  $A_V$  per unit power dissipation. Figure 5(b) depicts the TGF values at  $V_{\rm DS}$  = 0.7 V. The device with the highest TGF value can function at lower voltages without losing performance. Moreover, TGF is often used to estimate the power necessary to attain high speeds. The NSFET exhibits a marginal increment in TGF compared to NWFET and FinFET devices due to more  $g_m$ . The TGF of 41.8  $V^{-1}$ , 43.9  $V^{-1}$ , 44.5  $V^{-1}$  for p-type and 43.9  $V^{-1}$ , 44.1  $V^{-1}$ , 44.6  $V^{-1}$  for n-type FinFET, NWFET, and NSFET respectively are obtained. The maximum TGF is obtained from around -0.3 V to 0.22 V for all three devices.

For analog circuit design perspective,  $g_d$  is an important metric, and its variation with  $V_{DS}$  is illustrated in Fig. 5(c). Moreover, for the shorter channel, the influence of  $V_{DS}$  on the channel is high. Hence, it is fundamental to estimate the behaviour of  $g_d$  on FinFET, NWFET, and NSFET. The NSFET exhibits higher  $g_d$  compared to NWFET and FinFET. Moreover, p-type FinFET, NWFET, and NSFET show lower  $g_d$  compared to n-type FETs and ensures better gain. The intrinsic gain  $(A_V = g_m/g_d)$  depicts the overall performance of a device and is shown in Fig 5(d). It can be observed that for FinFET and NWFET, the  $A_{\rm v}$  decreases due to the significant dependence of  $I_D$  on  $V_{DS}$ . Moreover, a slight increment of  $1.95\times$  from FinFET to NWFET and  $1.01\times$  from NW to NSFET in n-type is observed. Whereas an increment of  $4.86 \times$ from FinFET to NWFET and  $1.02 \times$  from NW to NSFET for p-type is observed. Higher amount of  $A_v$  is noticed from FinFET to NWFET due to better  $g_m$ .

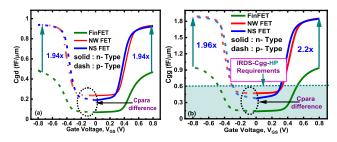

To understand the AC performance, the total effective capacitance of FinFET, NW, and NSFETs are calculated and depicted in Fig. 6(a)-(b). The total gate intrinsic capacitance ( $C_{intr}$ ) is the sum of the gate to source capacitance ( $C_{gs}$ )

FIGURE 6. (a)  $C_{gd}$  (Miller Capacitance) and (b)  $C_{gg}$  characteristics of n- and p-type FinFET, NW and NSFET (MBCFET) at  $V_{DS} = 0.05$  V.

**FIGURE 7.** (a) Quality factor (Q), (b)  $f_T$  and GBW characteristics of n- and p-type for FinFET, NW and NSFET (MBCFET).

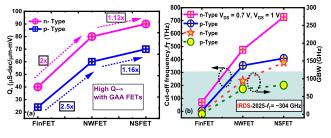

and gate to drain capacitance  $(C_{gd})$ . The  $C_{gd}$  is miller capacitance or parasitic capacitance. The  $C_{gg} = (C_{intr} + C_{para})$ and C<sub>gd</sub> values are low for FinFET compared to NW and NSFETs. Unlike FinFETs, in GAA NSFETs the outer fringing capacitances dominate due to larger NS width. Moreover,  $C_{gg}$  and  $C_{gd}$  are almost similar for NW and NSFETs. According to IRDS requirements, the  $C_{gg}$  for HP applications is 0.6 fF/ $\mu$ m. The FinFET shows lower  $C_{gg}$ , whereas NW and NS exhibit a rise over HP requirements. The p-type FETs have larger parasitic capacitances compared to n-type due to diffusion of boron into the channel deeper than phosphorus [20]. Furthermore, the  $C_{\text{para}}$  is more for NWFET and NSFET compared to FinFET in the OFF state. The quality factor  $Q = (g_m/SS)$  [12], determines the qualitative behaviour of a device and its behaviour with FinFET, NWFET and NSFETs is depicted in Fig 7(a). A rise in Q of  $2.5 \times$  with n-type and  $2\times$  with p-type from FinFET to NWFET is noticed. Furthermore, an increment in Q of 1.12× with n-type and  $1.16 \times$  with p-type from NWFET to NSFET is noticed. Higher improvement is noticed from FinFET to NWFET and NSFETs due to the better electrostatic integrity offered by the GAA structure. Higher Q obtained with NSFET is due to improved  $g_m$  and lower SS. The cut-off frequency  $(f_T)$ and gain-bandwidth product (GBW) are crucial metrics for the RF performance of any MOS device. The  $f_{\rm T}$  comparison of FinFET, NWFET and NSFET for both n-type and p-type FETs is illustrated in Fig. 7(b). Larger width by NSFET of 10 nm invokes more carriers and offers high I<sub>ON</sub>. Compared to FinFET and NWFET, the NSFET shows better  $f_{\rm T}$  due to the larger  $I_{ON}$ . Moreover, the n-type FETs dominate p-type FETs in  $f_{\rm T}$  due to better  $g_m$ .

The GBW indicates a MOS device's constant gain operation region [28]. The GBW product determines the device's constant gain region. The significance of GBW on FinFET,

FIGURE 8. (a) Calibration of Verilog-A model characteristics with TCAD simulation results (b) process followed from TCAD to circuit level simulation.

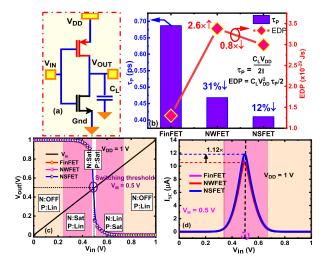

**FIGURE 9.** (a) Inverter schematic diagram (b) Propagation delay ( $T_p$ ) and Energy-delay product (EDP) (c) DC response and (d) Switching current ( $I_{SC}$ ) of CMOS inverter for FinFET, NW and NSFET (MBCFET).

NWFET, and NSFETs is shown in Fig. 7(b). The GBW for NSFET is higher than NWFET and FinFET due to higher  $g_m$ . Moreover, NSFET exhibits better performance than NWFET and FinFET for both n and p-type FETs. The GBW of n-type FinFET, NWFET, and NSFETs are 6.7 GHz, 94 GHz, and 146 GHz, respectively. For p-type FETs, the GBW deteriorates compared to n-type FETs with 1.42 GHz, 71 GHz, and 82 GHz for FinFET, NWFET and NSFET and NSFET, respectively. Finally, it is proved that chosen NWFET and NSFET design metrics meet multiple IRDS goals towards logic and RF performance.

#### **IV. CIRCUIT LEVEL ANALYSIS**

The circuit level simulations for FinFET, NWFET and NSFETs are done using a look-up table-based Verilog-A model in the CADENCE simulator [29]. The parallel simulations are carried out using the VisualFab tool to obtain currents and capacitances at different drain voltages for all the devices. The  $I_D$ - $V_{GS}$  characteristics from both TCAD and CADENCE tools are depicted in Fig. 8(a) and are matched well. The steps followed from device to circuit level simulations are shown in Fig. 8(b).

The inverter schematic diagram is shown in Fig. 9(a). The sum of both n-FET and p-FET's  $C_{gg}$  is considered as the load capacitance ( $C_L$ ) [30]. The propagation delay of the inverter for FinFET, NWFET and NSFETs is shown in Fig. 9(b).

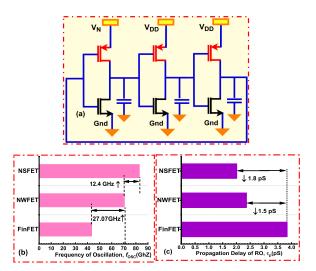

**FIGURE 10.** (a) 3- stage ring oscillator (RO) (b) Frequency of oscillation ( $f_{OSC}$ ) (c) Propagation delay ( $\tau_p$ ) of FinFET, NWFET and NSFET (MBCFET) respectively.

The average propagation delay ( $\tau_P$ ) is calculated using the formula shown in Figure 9(b) [31], where *I* and  $C_L$  are the average current and the load capacitance, respectively. As  $\tau_p \alpha C_L \times (1/I_{ON} (n-FET) + 1/I_{ON} (p-FET))$  [32], the significant rise in "*I*" for NSFET is predominant compared to a marginal rise in  $C_L$ , which leads to a fall in  $\tau_p$  for NSFET based inverter. The  $\tau_p$  declined by 31% from FinFET to NWFET and 12% from NWFET to NSFET. Also, the energy delay product (EDP) calculated as show in Fig. 9(b) [26]. An increment of 2.8× in EDP is observed from FinFET to NWFET due to marginal fall in  $\tau_p$  and significant rise in " $C_L$ " and a decrement of 0.8× observed from NWFET to NSFET due to significant fall in  $\tau_p$  and marginal rise in  $C_L$ .

The output characteristics of inverters are depicted in Fig. 9(c), and the switching threshold  $V_{\rm M}$  is noticed at 0.5 V. Moreover, various operating regions of both p and n-type FETs in the inverter are shown in Fig. 9(c). Further, the switching current  $(I_{SC})$  of the CMOS inverter is depicted in Fig. 9(d) for FinFET, NW and NSFETs at  $V_{DD} = 1$  V. The static current (at  $V_{in} = 0$  V,  $V_{in} = V_{DD}$ V) is less than 10 pA, resulting in significantly lower static power dissipation and improved energy efficiency for all the FinFET, NW and NSFET based inverters. Similar  $I_{SC}$  has been observed for FinFET and NW based inverters at switching threshold voltage. However, an increment of  $1.12 \times$  in  $I_{SC}$  is observed for NSFET based inverter compared to FinFET and NW based inverters. Fig. 10a shows the 3-stage ring oscillator (RO) schematic diagram. Fig. 10b shows the  $f_{OSC}$  of FinFET, NW and NSFETs respectively. Compared to FinFET, the NWFET exhibits 27.07 GHz rise in  $f_{OSC}$  and compared to NWFET, the NSFET exhibits 12.4 GHz rise in f<sub>OSC</sub>. Fig. 10c depicts the propagation delay ( $\tau$ ) of the 3-stage RO circuit of FinFET, NWFET and NSFET. A fall of 1.5 pS and 1.8 pS is noticed from FinFET to NW and NSFET respectively. Thus, the NSFET based circuits outperform in circuit applications and ensure further scaling of the device.

| Examined<br>Features                                        | [24]                       | [12]                       | [14]                       | [33]                      | [34]                                                                              | [35]                                    | [36]             | This<br>work                                          |

|-------------------------------------------------------------|----------------------------|----------------------------|----------------------------|---------------------------|-----------------------------------------------------------------------------------|-----------------------------------------|------------------|-------------------------------------------------------|

| Explored<br>devices                                         | NSFET                      | FinFET,<br>NW and<br>NSFET | FinFET,<br>NW and<br>NSFET | NSFET                     | NWFET                                                                             | NSFET                                   | NSFET            | FinFET,<br>NW and<br>NSFET                            |

| Technology<br>node                                          | Sub-5-nm                   | Sub-5-<br>nm               | Sub-5-<br>nm               | 7-nm                      | Sub-5-nm                                                                          | Sub-2-<br>nm                            | Sub-2-<br>nm     | Sub-5-<br>nm                                          |

| IRDS<br>Benchmarking                                        | No                         | Yes                        | No                         | No                        | No                                                                                | Yes                                     | Yes              | Yes                                                   |

| p- and n-type                                               | No                         | No                         | No                         | Yes                       | No                                                                                | No                                      | Yes              | Yes                                                   |

| Circuit for DC<br>and transient<br>analysis                 | Yes                        | No                         | No                         | Yes                       | Yes                                                                               | Yes                                     | Yes              | Yes                                                   |

| Circuit<br>implementation<br>(Digital, analog<br>and mixed) | CMOS<br>inverter and<br>RO |                            |                            | CMOS<br>inverter,<br>SRAM | CMOS inverter<br>and resistive<br>load inverter,<br>common<br>source<br>amplifier | Resistive<br>load<br>inverter<br>and RO | CMOS<br>inverter | CMOS<br>inverter,<br>RO,<br>current<br>mirror,<br>OTA |

TABLE 2. Comparision of emerging fet with literature.

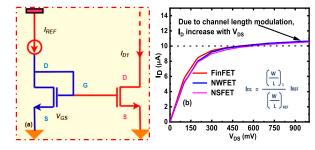

In an integrated circuits the current mirrors are an integral part to maintain constant currents instead of varying loads. Fig. 11(a) depicts the current mirror  $V_{\text{DS}}$  with  $I_{\text{DS}}$  with Fin-FET, NWFET and NSFET respectively. For current mirror circuit we have assumed  $V_{\text{DD}} = 1$  V and  $I_{\text{ref}}$  of 10  $\mu$ A. For FinFET, NWFET and NSFET almost have  $I_{\text{D1}} = I_{\text{ref}}$ , when  $V_{\text{DS}}$  approaching 1 V. However, the NSFET has constant output compared to NWFET and FinFET which shows NSFETs robustness for driving analog circuit applications (Fig. 11(b)).

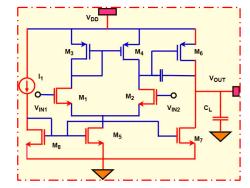

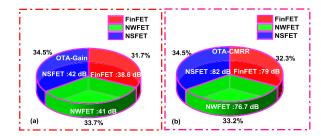

The operational transconductance amplifier (OTA) is one of the fundamental components of any electronic circuit as it increases the output current with respect to the applied differential input voltage. Figure 12 depicts the schematic of OTA. In many circuits it can also be serves as voltage-controlled current source in many of the circuits. Figure 13 shows the performance comparison of FinFET, NWFET and NSFET towards gain (Fig. 13(a)) and CMRR (Fig. 13(b)) respectively. Compared to FinFET and NWFET, the NSFET (MBCFET) exhibits better gain and CMRR and can be feasible for ultra-lower power analog and mixed-mode circuit applications. The contribution of our

**FIGURE 12.** The schematic of operational transconductance amplifier (OTA).

FIGURE 13. (a) The operational transconductance amplifier (OTA) gain and (b) common mode rejection ratio (CMRR) comparison for FinFET, NWFET and NSFET (MBCFET).

study is highlighted with comparison of existing FETs in the latest literature is depicted in Table 2. Thus, the comparison of GAA FETs is presented towards device and circuit perspective with satisfying IRDS 2025 goals.

## **V. CONCLUSION**

This article demonstrates the performance comparison of FinFET and GAA NWFET, and NSFET (MBCFET) at both

device and circuit levels. Various crucial DC and analog/RF FOMs are compared and benchmarked with IRDS guidelines. The NSFET exhibits better DC and analog performance compared to NW and FinFET. Compared to FinFET and NWFET, NSFET offers more  $g_m$ , TGF, Q, and intrinsic gain. Circuit level comparison has been made for circuits like inverter and ring oscillator. The NSFET based inverter offers the lowest propagation delay despite having more gate capacitances. Also, the NWFET and NSFET based ring oscillators outperform with an oscillation frequency of 70.46 GHz and 82.86 GHz, respectively. The performance benchmarking reveals that NSFET is a potential candidate to continue the scaling for sub-5-nm node technologies. Moreover, the circuits like OTA and current mirror performance for NSFET is better which can be feasible for ultra-lower power analog and mixed circuit applications. Finally, various parameters reach the IRDS goals with NSFET which ensures its robustness for continued scaling.

## ACKNOWLEDGMENT

The authors would like to thank ICFAI Foundation for Higher Education Hyderabad, REVA University and IIT Patna for the resources to carry out the research.

#### REFERENCES

- [1] A. Asenov, B. Cheng, X. Wang, A. R. Brown, C. Millar, C. Alexander, S. M. Amoroso, J. B. Kuang, and S. R. Nassif, "Variability aware simulation based design-technology cooptimization (DTCO) flow in 14 nm FinFET/SRAM cooptimization," *IEEE Trans. Electron Devices*, vol. 62, no. 6, pp. 1682–1690, Jun. 2015, doi: 10.1109/TED.2014.2363117.

- [2] R. K. Jaisawal, S. Rathore, N. Gandhi, P. N. Kondekar, S. Banchhor, V. B. Sreenivas, Y. S. Song, and N. Bagga, "Self-heating and interface traps assisted early aging revelation and reliability analysis of negative capacitance FinFET," in *Proc. 7th IEEE Electron Devices Technol. Manuf. Conf. (EDTM)*, Mar. 2023, pp. 1–3, doi: 10.1109/EDTM55494.2023.10103127.

- [3] V. B. Sreenivasulu and V. Narendar, "Characterization and optimization of junctionless gate-all-around vertically stacked nanowire FETs for sub-5 nm technology nodes," *Microelectron. J.*, vol. 116, Oct. 2021, Art. no. 105214, doi: 10.1016/j.mejo.2021.105214.

- [4] G. Bae, D. I. Bae, M. Kang, S. M. Hwang, S. S. Kim, B. Seo, T. Y. Kwon, T. J. Lee, C. Moon, Y. M. Choi, and K. Oikawa, "3 nm GAA technology featuring multi-bridge-channel FET for low power and high performance applications," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2018, p. 28, doi: 10.1109/IEDM.2018.8614629.

- [5] S. Barraud, M. Berthome, R. Coquand, M. Casse, T. Ernst, M.-P. Samson, P. Perreau, K. K. Bourdelle, O. Faynot, and T. Poiroux, "Scaling of trigate junctionless nanowire MOSFET with gate length down to 13 nm," *IEEE Electron Device Lett.*, vol. 33, no. 9, pp. 1225–1227, Sep. 2012, doi: 10.1109/LED.2012.2203091.

- [6] D. Yakimets, M. G. Bardon, D. Jang, P. Schuddinck, Y. Sherazi, P. Weckx, K. Miyaguchi, B. Parvais, P. Raghavan, A. Spessot, D. Verkest, and A. Mocuta, "Power aware FinFET and lateral nanosheet FET targeting for 3nm CMOS technology," in *IEDM Tech. Dig.*, Dec. 2017, pp. 501–504.

- [7] H. Mertens, R. Ritzenthaler, V. Pena, G. Santoro, K. Kenis, A. Schulze, E. D. Litta, S. A. Chew, K. Devriendt, S. Demuynck, and D. Yakimets, "Vertically stacked gate-all-around Si nanowire transistors: Key process optimizations and ring oscillator demonstration," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2017, p. 37, doi: 10.1109/IEDM.2017.8268511.

- [8] K. Kalna, L. Yang, and A. Asenov, "Monte Carlo simulations of sub-100 nm InGaAs MOSFETs for digital applications," in *Proc. 35th Eur. Solid-State Device Res. Conf.*, 2005, pp. 169–172.

- [9] S.-G. Jung, D. Jang, S.-J. Min, E. Park, and H.-Y. Yu, "Performance analysis on complementary FET (CFET) relative to standard CMOS with nanosheet FET," *IEEE J. Electron Devices Soc.*, vol. 10, pp. 78–82, 2022, doi: 10.1109/JEDS.2021.3136605.

- [10] M. Rau, E. Caruso, D. Lizzit, P. Palestri, D. Esseni, A. Schenk, L. Selmi, and M. Luisier, "Performance projection of III-V ultra-thin-body, FinFET, and nanowire MOSFETs for two next-generation technology nodes," in *IEDM Tech. Dig.*, Dec. 2016, p. 30.

- [11] S. Barraud, V. Lapras, B. Previtali, M. P. Samson, J. Lacord, S. Martinie, M.-A. Jaud, S. Athanasiou, F. Triozon, O. Rozeau, J. M. Hartmann, C. Vizioz, C. Comboroure, F. Andrieu, J. C. Barbe, M. Vinet, and T. Ernst, "Performance and design considerations for gate-all-around stacked-NanoWires FETs," in *IEDM Tech. Dig.*, Dec. 2017, p. 29, doi: 10.1109/IEDM.2017.8268473.

- [12] A. Goel, A. Rawat, and B. Rawat, "Benchmarking of analog/RF performance of fin-FET, NW-FET, and NS-FET in the ultimate scaling limit," *IEEE Trans. Electron Devices*, vol. 69, no. 3, pp. 1298–1305, Mar. 2022, doi: 10.1109/TED.2021.3140158.

- [13] J.-S. Yoon, J. Jeong, S. Lee, and R.-H. Baek, "Multi-V<sub>th</sub> strategies of 7-nm node nanosheet FETs with limited nanosheet spacing," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 861–865, 2018, doi: 10.1109/JEDS.2018.2859799.

- [14] D. Nagy, G. Espineira, G. Indalecio, A. J. Garcia-Loureiro, K. Kalna, and N. Seoane, "Benchmarking of FinFET, nanosheet, and nanowire FET architectures for future technology nodes," *IEEE Access*, vol. 8, pp. 53196–53202, 2020, doi: 10.1109/ACCESS.2020.2980925.

- [15] J.-S. Yoon and R.-H. Baek, "Device design guideline of 5-nm-node FinFETs and nanosheet FETs for analog/RF applications," *IEEE Access*, vol. 8, pp. 189395–189403, 2020, doi: 10.1109/ACCESS.2020.3031870.

- [16] P. Kushwaha, A. Dasgupta, M.-Y. Kao, H. Agarwal, S. Salahuddin, and C. Hu, "Design optimization techniques in nanosheet transistor for RF applications," *IEEE Trans. Electron Devices*, vol. 67, no. 10, pp. 4515–4520, Oct. 2020, doi: 10.1109/TED.2020.3019022.

- [17] U. K. Das and T. K. Bhattacharyya, "Opportunities in device scaling for 3-nm node and beyond: FinFET versus GAA-FET versus UFET," *IEEE Trans. Electron Devices*, vol. 67, no. 6, pp. 2633–2638, Jun. 2020, doi: 10.1109/TED.2020.2987139.

- [18] V. Vashishtha and L. T. Clark, "Comparing bulk-Si FinFET and gate-allaround FETs for the 5 nm technology node," *Microelectron. J.*, vol. 107, Jan. 2021, Art. no. 104942, doi: 10.1016/j.mejo.2020.104942.

- [19] V. C. P. Silva, W. F. Perina, J. A. Martino, E. Simoen, A. Veloso, and P. G. D. Agopian, "Analog figures of merit of vertically stacked silicon nanosheets nMOSFETs with two different metal gates for the sub-7 nm technology node operating at high temperatures," *IEEE Trans. Electron Devices*, vol. 68, no. 7, pp. 3630–3635, Jul. 2021, doi: 10.1109/TED.2021.3077349.

- [20] J.-S. Yoon, J. Jeong, S. Lee, and R.-H. Baek, "Systematic DC/AC performance benchmarking of sub-7-nm node FinFETs and nanosheet FETs," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 942–947, 2018.

- [21] A. Goel, S. K. Gupta, and K. Roy, "Asymmetric drain spacer extension (ADSE) FinFETs for low-power and robust SRAMs," *IEEE Trans. Electron Devices*, vol. 58, no. 2, pp. 296–308, Feb. 2011, doi: 10.1109/TED.2010.2090421.

- [22] V. B. Sreenivasulu, A. K. Neelam, S. R. Kola, J. Singh, and Y. Li, "Exploring the performance of 3-D nanosheet FET in inversion and junctionless modes: Device and circuit-level analysis and comparison," *IEEE Access*, vol. 11, pp. 90421–90429, 2023, doi: 10.1109/ACCESS.2023.3306050.

- [23] W.-L. Sung, Y. Li, and M.-H. Chuang, "Nanosized-metal-grain-patterndependent threshold-voltage models for the vertically stacked multichannel gate-all-around Si nanosheet MOSFETs and their applications in circuit simulation," *IEEE Trans. Electron Devices*, vol. 71, no. 1, pp. 350–358, Jan. 2024, doi: 10.1109/TED.2023.3328586.

- [24] (2022). International Roadmap for Devices and Systems. [Online]. Available: https://irds.ieee.org/editions/2020

- [25] 3-D Device Simulator, Version1.9.0, Genius, Reference Manual, Cogenda, Singapore, 2018.

- [26] V. B. Sreenivasulu and V. Narendar, "Design insights of nanosheet FET and CMOS circuit applications at 5-nm technology node," *IEEE Trans. Electron Devices*, vol. 69, no. 8, pp. 4115–4122, Aug. 2022, doi: 10.1109/TED.2022.3181575.

- [27] N. Loubet, T. Hook, P. Montanini, C. W. Yeung, S. Kanakasabapathy, M. Guillom, T. Yamashita, J. Zhang, X. Miao, J. Wang, and A. Young, "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET," in *Proc. Symp. VLSI Technol.*, Kyoto, Japan, Jun. 2017, pp. 230–231, doi: 10.23919/VLSIT.2017.7998183.

- [28] A. Nandi, A. K. Saxena, and S. Dasgupta, "Design and analysis of analog performance of dual-k spacer underlap N/P-FinFET at 12 nm gate length," *IEEE Trans. Electron Devices*, vol. 60, no. 5, pp. 1529–1535, May 2013.

- [29] Cadence Virtuoso Spectre Circuit Simulator, Cadence Des. Syst., San Jose, CA, USA, 2016.

- [30] N. A. Kumari, V. B. Sreenivasulu, and P. Prithvi, "Impact of scaling on nanosheet FET and CMOS circuit applications," *ECS J. Solid State Sci. Technol.*, vol. 12, no. 3, Mar. 2023, Art. no. 033001.

- [31] N. Chowdhury, G. Iannaccone, G. Fiori, D. A. Antoniadis, and T. Palacios, "GaN nanowire n-MOSFET with 5 nm channel length for applications in digital electronics," *IEEE Electron Device Lett.*, vol. 38, no. 7, pp. 859–862, Jul. 2017, doi: 10.1109/LED.2017.2703953.

- [32] A. Kumari and J. Singh, "Analog and mixed circuit analysis of nanosheet FET at elevated temperatures," *Phys. Scripta*, vol. 98, no. 10, Oct. 2023, Art. no. 105409, doi: 10.1088/1402-4896/acf73f.

- [33] W.-L. Sung and Y. Li, "Characteristics of stacked gate-all-around Si nanosheet MOSFETs with metal sidewall source/drain and their impacts on CMOS circuit properties," *IEEE Trans. Electron Devices*, vol. 68, no. 6, pp. 3124–3128, Jun. 2021, doi: 10.1109/TED.2021.3074126.

- [34] V. B. Sreenivasulu, N. A. Kumari, V. Lokesh, J. Ajayan, M. Uma, and V. Vijayvargiya, "Design of resistive load inverter and common source amplifier circuits using symmetric and asymmetric nanowire FETs," *J. Electron. Mater.*, vol. 52, no. 11, pp. 7268–7279, Nov. 2023, doi: 10.1007/s11664-023-10618-0.

- [35] M. Ehteshamuddin, K. Sheelvardhan, A. Kumar, S. Guglani, S. Roy, and A. Dasgupta, "Machine learning-assisted multiobjective optimization of advanced node gate-all-around transistor for logic and RF applications," *IEEE Trans. Electron Devices*, early access, doi: 10.1109/TED.2023.3345288.

- [36] H. Xu, W. Gan, L. Cao, C. Yang, J. Wu, M. Zhou, H. Qu, S. Zhang, H. Yin, and Z. Wu, "A machine learning approach for optimization of channel geometry and source/drain doping profile of stacked nanosheet transistors," *IEEE Trans. Electron Devices*, vol. 69, no. 7, pp. 3568–3574, Jul. 2022, doi: 10.1109/TED.2022.3175708.

#### VAKKALAKULA BHARATH SREENIVASULU

(Member, IEEE) received the B.Tech. degree in electronics and communication engineering and the M.Tech. degree in VLSI and embedded systems from Jawaharlal Nehru Technological University Anantapur, Andhra Pradesh, India, in 2013 and 2016, respectively, and the Ph.D. degree from the National Institute of Technology (NIT) Warangal, Warangal, India, in 2022. He was a Postdoctoral Research Associate with the Indian

Institute of Technology (IIT) Patna, Patna, India. Currently, he is an Assistant Professor with the School of Electronics and Communication Engineering, REVA University, Bengaluru, India. He has published several peer-reviewed articles on topics, such as trigate FET, FinFET, multi-fin FET, nanowire, nanosheet, TreeFET, and CombFET toward CMOS circuit applications. Some of his works are recognized as the most popular and top cited list of articles in the IEEE TRANSACTIONS ON ELECTRON DEVICES, *Microelectronics Journal*, and *International Journal of RF and Microwave Computer-Aided Engineering*. His current research interests include the design of novel device architectures and circuits for sub-2-nm technology regime, compact modelling, artificial neural networks, and neuromorphic computing approaches for semiconductor devices.

**ARUNA KUMARI NEELAM** (Member, IEEE) received the B.Tech. degree in electronics and communication engineering from RGUKT Nuzivid, Andhra Pradesh, India, in 2017, the M.Tech. degree in VLSI design from Vignan University, in 2020, and the Ph.D. degree from NIT Warangal, in 2023. She is currently an Assistant Professor with the School of Electronics Engineering, VIT Vellore. Her research interests include simulation of nanoscale devices like multi-gate

FETs and their circuit applications at advanced technology nodes, machine learning integration with devices, in-memory computing, beyond CMOS, and VLSI architectures.

**ASISA KUMAR PANIGRAHY** received the B.Tech. degree in electronics and communication engineering from the National Institute of Science and Technology, Berhampur, Odisha, in 2010, the M.Tech. degree in VLSI and embedded system design from BPUT, Rourkela, Odisha, in 2012, and the Ph.D. degree in microelectronics and VLSI from the Electrical Engineering Department, Indian Institute of Technology Hyderabad, in 2017. Currently, he is an Associate Profes-

sor and the Head of the Department of Electronics and Communication Engineering, ICFAI Foundation for Higher Education, Hyderabad, India. He received the Gandhian Young Technological Innovation Award for the research work "A Low-Cost Disposable Microfluidic Biochip for Malaria Diagnosis" from the Honorable President of India Shri Ram Nath Kovind Ji at Rhastrapati Bhavan, in March 2018. He received the Distinguished Japanese Society for the Promotion of Science (JSPS) Award by the Prof. T. Suga from The University of Tokyo, Japan, as invited Speaker, in 2017. He has authored 25 peer-reviewed and SCI-indexed articles in prestigious publications, including IEEE, Elsevier, and Springer. His research interests include vertical IC (3D IC) integration, semiconductor device simulations and modeling, and sensors based on micro-nano materials. Currently, he is handling research project funded by BIRAC, Government of India. He is also an Academic Editorial Board Member of Nanomaterials (Hindawi). He received the Excellence in Research Award from the Director of Indian Institute of Technology Hyderabad during Foundation Day of Institute, in 2015 and 2016. He received the DST Young Scientist Award by the Department of Science and Technology, Government of India, in 2016. In 2016, the CSIR, Government of India, presented him with the CSIR Young Scientist Award.

**LOKESH VAKKALAKULA** (Member, IEEE) received the B.Tech. degree in electronics and communication engineering from JNTU Anantapur, India, and the master's degree in embedded systems from TU Chemitz, Germany. He wrote his master's thesis "Respiration rate estimation from remote photoplethysmogram using deep neural networks" with Fraunhofer, IGD Rostock, Germany. He was with Tech Mahindra, Pune, India, and Harman International, Bengaluru, Kar-

nataka, India, toward various AI and ML projects. Currently, he is a Senior Engineer with Bosch Global Software Technologies, Bengaluru. He has an industrial experience of three years in Johnson and Jhonson in Germany and six years overall experience in IT industry. His research interests include machine learning approaches for devices and circuits, signal processing, and neuromorphic computing.

JAWAR SINGH (Senior Member, IEEE) received the Ph.D. degree from the University of Bristol, Bristol, U.K., in 2010. He is currently a Professor with the Indian Institute of Technology Patna, Patna, India. He holds two U.S. patents on SRAM cells. His current research interests include exploration of classical and nonclassical device structures and their applications for CMOS enhancement or replacement. He was a recipient of the prestigious Indo–U.S. BHAVAN-2016 Fellowship.

SHIV GOVIND SINGH (Senior Member, IEEE) received the Ph.D. degree in electrical engineering from the Indian Institute of Technology Bombay, Mumbai, India, in 2008. He is currently a Professor with the Indian Institute of Technology Hyderabad, Hyderabad, India. He is also the Head of the Department of Electrical Engineering, Indian Institute of Technology Hyderabad, Telangana, India. His current research interests include 3-D IC integrations, thermal imagers, sensors, lab-

on-chips, MEMS, RF MEMS, and energy harvesting devices.