Received 11 October 2023, accepted 28 October 2023, date of publication 1 November 2023, date of current version 7 November 2023. Digital Object Identifier 10.1109/ACCESS.2023.3329233

# SURVEY

# A Survey on Dynamic Application Mapping Approaches for Real-Time Network-on-Chip-Based Platforms

# SHAROON SALEEM<sup>®</sup><sup>1</sup>, FAWAD HUSSAIN<sup>®</sup><sup>1</sup>, (Senior Member, IEEE), WAQAR AMIN<sup>®</sup><sup>1</sup>, REHAN AHMED<sup>®</sup><sup>2</sup>, YOUSAF BIN ZIKRIA<sup>3</sup>, (Senior Member, IEEE), FARRUH ISHMANOV<sup>®</sup><sup>4</sup>, AND HEEJUNG YU<sup>®</sup><sup>5</sup>, (Senior Member, IEEE)

<sup>1</sup>Department of Computer Engineering, University of Engineering and Technology, Taxila (UET Taxila), Taxila 47050, Pakistan

<sup>2</sup>School of Electrical Engineering and Computer Science, National University of Science and Technology, Islamabad 44000, Pakistan <sup>3</sup>Victorian Institute of Technology (VIT), The Rocks, NSW 2000, Australia

<sup>5</sup>Department of Electronics and Communication Engineering, Kwangwoon University, Seouro 1977, South <sup>5</sup>Department of Electronics and Information Engineering, Korea University, Sejong 30019, South Korea

Corresponding authors: Heejung Yu (heejungyu@korea.ac.kr) and Farruh Ishmanov (farruh@kw.ac.kr)

This work was supported in part by the "Regional Innovation Strategy (RIS)" through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (MOE) under Grant 2021RIS-004; in part by the Ministry of Science and ICT (MSIT), South Korea, through the Information Technology Research Center (ITRC) Support Program, Supervised by the Institute for Information and Communications Technology Planning and Evaluation (IITP), under Grant IITP-2023-RS-2022-00164800; in part by the Korea University Grant; and in part by the Research Grant of Kwangwoon University, Seoul, South Korea, in 2023.

**ABSTRACT** Network-on-Chip (NoC) has been unfolded as a superior alternative for integrating a considerably greater extent of cores on a single chip. Recently, multi-core systems have become prevalent because of the increased processing demands for high-performance embedded applications. Application mapping techniques play a significant role in enhancing the extensive performance of such complex multi-core platforms. Developing and implementing efficient application mapping techniques are required for system design to meet the demand of such complicated multi-core systems. The paper primarily focuses on dynamic application mapping techniques, classifying them into a number of subcategories. It highlights such approaches and techniques that aim to enhance the performance of the NoC-based systems by optimizing them in terms of communication cost, latency, energy consumption, power, execution, and computational time. Future challenges, trends, and simulation tools have also been spotlighted.

**INDEX TERMS** Network-on-chip, application mapping, system-on-chip, VOPD.

#### I. INTRODUCTION

Due to the rise in complexity of embedded This is some system devices, system-on-chip (SoC) incorporating the numerous processing cores on a single chip to perform various functions is the primary paradigm of today's digital world. The SoC uses a shared medium bus to communicate intellectual property (IP) cores and is widely utilized in domain-specific devices [1], [2], such as aerospace, medical sciences, microprocessors-based technology, and wireless communications. Due to the higher density of components

The associate editor coordinating the review of this manuscript and approving it for publication was Gian Domenico Licciardo<sup>10</sup>.

in SoC, the implementation of a shared-bus architecture is getting complicated. As the number of cores increases on the chip, the performance is not enhanced and scaled by the increased processing cores due to the limitations of the shared-bus architecture. Network-on-chip (NoC) has emerged as a feasible substitute to cater to the new inter-core communication demands of the growing number of components on a chip and faster communication between the cores [3]. NoC architecture is considered a part of or a subset of SoC-based technology [4]. NoC uses IP cores connected with the routers and inter-switch links [5], and the communication between the cores is done by transferring packets with these routers and links. Messages are divided

<sup>&</sup>lt;sup>4</sup>Department of Electronics and Communication Engineering, Kwangwoon University, Seoul 01897, South Korea

into smaller packets to be transmitted between various cores that allow for the efficient use of network resources. NoC employs a routing algorithm for the determination of the path that each packet follows from the source to the destination. Various switching techniques are developed to transfer packets such as circuit and packet switching. A physical path from source to destination is reserved before the data transmission in circuit switching. While in packet switching, each message is partitioned into fixed-length packets which are transmitted without reserving the entire path. Buffers are placed at the NoC routers to temporarily store packets that need transmission. NoC provides considerable refinement in SoC communication infrastructure, mainly by replacing the bus-based architecture. NoC design and development are undoubtedly one of the significant research areas of digital system design in the current era. The research problems in a NoC domain are broadly distributed into different categories. One of the categories belongs to communication infrastructure, such as the architecture of the router, optimization of buffer utilization, topology in NoC, clocking, floor planning, and layout. Another category deals with a communication archetype, such as packet routing policies, network congestion, switching techniques, ensuring reliability in NoC systems, and thermal and power management. The evaluation framework is another category that deals with the system's bandwidth, throughput, and latency. Once these design and communication infrastructure-related requirements are fulfilled and finalized, a key challenge in the final design and architecture of a NoC platform is the association of IP cores to routers. Thus, application mapping is a significant step in the overall design process [6] that directly affects the communication time, cost, bandwidth, and overall NoC performance. Many surveys [4], [7], [8] and textbooks [9], [10] related to NoC have been published. However, there have been various advanced research problems in the field of NoC that need to be addressed. Besides other research problems reported in the literature, the mapping takes on a significant and distinguished place amongst other research problems. It presents a multitude of complexities and numerous challenges, particularly when faced with dynamic scenarios. These include fault occurrences, network congestion, load balancing, and the management of high energy consumption caused by task placements. The main purpose of this survey is to furnish an extensive overview of the major traits of NoC mapping, and the main emphasis is on Application Mapping in such dynamic scenarios. The distinct techniques on the basis of dynamic scenarios are first segregated into different categories, and their various dimensions, along with their contributions to enhancing the performance metrics are presented, which is the main contribution in a real-time mapping domain. Also, research directions are provided extensively in this survey paper. The rest of the survey is organized as follows: Section I presents the broader overview and some essential components related to application mapping problems in a NoC-based multicore platform. Detail discussion on application mapping techniques is presented in Section II. Section III presents details related to the simulators and performance metrics. Section IV presents the latest trends and future related to application mapping. Finally, Section V concludes this article.

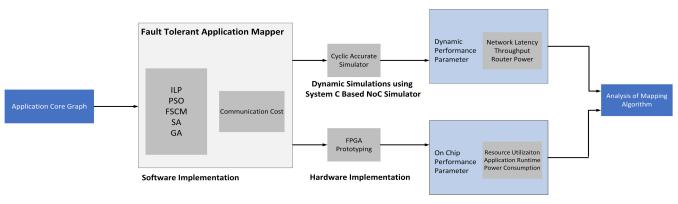

# A. SCOPE

In this study, we focus on the implementation of application mapping techniques and strategies in NoC systems in dynamic scenarios. To accurately approximate area and overall power usage for NoC platforms, the simulation work is carried out to evaluate and derive latency, power consumption, and communication bandwidth. The initial steps are to develop communication infrastructure, methodology, and evaluation setup. After the initial steps, one of the highly significant steps is to obtain the optimal placement and mapping of application tasks to processing cores in a NoC platform. This helps to improve the communication cost, the overall latency, and system performance.

#### **B. APPLICATION MAPPING OVERVIEW**

An application mapping design problem has become a crucial aspect of NoC architecture and design. It is required to efficiently map and place the application tasks onto the appropriate processing elements to fully exploit the resources incorporating NoC. The application task mapping is allocating tasks of an application onto cores while considering the various optimization factors and criteria, such as total execution time, latency, and energy consumption [6]. The parameters mentioned above are directly affected by optimal task mapping decisions. Numerous algorithms and techniques have been designed and developed to achieve optimal task mappings. The application mapping problem is known as a non-deterministic polynomial-time (NP)-hard problem [7].

In [11] and [12], research problems related to NoC and a general discussion on NoC architectures, platforms, and applications are provided. A comprehensive survey of application mapping techniques and their classifications into static and dynamic categories is presented in [13]. The authors of [14] and [15] have presented various mapping techniques on multi-core systems. A survey on fault tolerant-based application mapping techniques for NoC platforms has been presented in [16], which discusses techniques used to recover the system from the faults. Several approaches are discussed comprehensively in the survey, such as mapping techniques integrated with routing, redundancy techniques, and remapping configurations. In addition, a performance comparison is also spotlighted. A survey on optimization of mapping and scheduling techniques for NoC platforms has been provided in [17]. The survey also classifies mapping techniques into static and dynamic domains. A comprehensive survey on application mapping techniques and their comparative analysis have been presented in [18]. The survey discusses the classification of application mapping techniques focusing

on static mapping techniques. Moreover, a comparison in terms of communication cost, power, latency, and energy consumption is also presented for implementation of real-time applications, such as video object plane decoder (VOPD) and moving picture expert group-4 (MPEG-4).

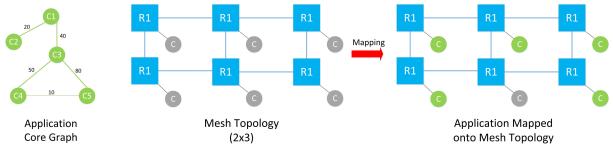

Many surveys and reviews are available related to the other three research dimensions of NoC architecture and design. However, the fourth dimension, i.e., application mapping, is not reviewed to that extent. Although many comprehensive surveys are available that discuss the application mapping problem and approaches in detail, there still exists room to further elaborate and discuss the application mapping techniques in dynamic scenarios. The primary aim and emphasis of this study is to present a classification of application mapping techniques, especially in real-time dynamic scenarios. This study mainly targets different domains concerning several measures, such as the execution of new enabling applications in the system, fault avoidance, critical thermal conditions, and readiness. This paper also presents application mapping in congestion-based scenarios and cases where the NoC status in terms of loaded links and cores is taken into account. These are the real-time challenges confronted by the system, and dynamic mapping approaches that are efficient and effective can address them. Finally, futuristic trends in the NoC mapping domains are also highlighted. Figure 1 depicts the NoC application mapping process that consists of an application core graph to be mapped onto  $2 \times 3$  mesh topology. The cores are mapped to various available locations as shown in the mesh topology.

# C. GENERATION OF TASKS GRAPHS

Any application that runs on the NoC platform is characterized by a task graph consisting of an instruction set that sequentially executes on the processor [19]. The communication task graph (CTG) shows the application divided into various specific tasks and the application's communication sample. It represents the data volume exchanged between the applications' tasks. A task graph N can be represented as N = N(T, C); the vertexes of a task graph stand for a set of tasks ( $T = \{T1, T2, T3, \dots, Tn\}$ ) and tasks have the associated information regarding their communication. The directed arcs ( $C = \{c_{i,j} | i, j = 1, 2, 3, \dots, n\}$ ) which occur amongst the tasks characterize interdependencies and volume of data between two application tasks or nodes.

Application task graphs are obtained in the following way:

- 1) By the use of the embedded system synthesis benchmarks suite (E3S)

- 2) By generating the task graphs using the task graphs for free (TGFF) tool [20]

- 3) By real-world applications having multi-threaded features, attained by using the communication extraction from threaded applications (CETA) tool [21].

- 4) The use of a scaling algorithm such as the benchmark scaling algorithm in [22] for the generation of extensive and large task graphs.

In a NoC design, task graphs are often linked with deadlines to ensure the timely execution of tasks in a multicore platform. These deadlines are significant for real-time and time-sensitive applications. There are tasks in real-time systems with hard deadlines that must be completed within a specified time frame; otherwise, the system may fail to produce the correct results. Scheduling techniques can be employed to ensure the tasks meet their deadlines efficiently, adjusting computational and communication resources with real-time requirements. Such methods optimize the task deadline, considerations of task dependencies, delays, and resource allocation are required, and scheduling analysis is incorporated to ensure the efficient execution of applications.

Generating and simulating task graphs have varying complexities to deal with, such as type and size of application, communication bandwidth measurement between tasks, and their deadline requirements. Also, it would require certain NoC setups, such as selecting appropriate topology, routing protocol, and injection rate with various other run-time parameters. One important consideration is task modeling complexity of representing real-world applications such as task graphs with accurate timing and dependencies constraints for complex dynamic systems. The other challenge could be realistic workload generation that mimics the behavior of actual real-time systems. In order to accurately simulate it on real-time systems, the simulation of real-time task graphs requires precise modeling of underlying resourceintensive hardware/ software modules. Even scaling up the simulation to cater to large-scale systems with numerous tasks and modules while maintaining real-time responsiveness is one of the significant challenges. Addressing these challenges while looking into the constraints in task graph generation and simulation requires effective design and analysis of real-time systems.

This survey mainly emphasizes run-time-based application techniques and their various dimensions. For detailed literature regarding task generation tools, the readers may explore graph generation research presented in [23], [24], and [25] in which information related to generations of synthetic graphs is presented.

# II. CLASSIFYING THE APPLICATION MAPPING STRATEGIES

Mapping application tasks to cores in the NoC platform can either be performed at the design time (i.e., static or offline mapping) or at the run-time (i.e., dynamic or online mapping). Design time techniques use static platforms and predefined tasks with specific communication characteristics. Thus, the static techniques are unsuitable for dynamic scenarios with variable workloads and other variable factors in which new applications may emerge at the system's runtime that need execution on the NoC platform. In the case of static mapping, placement of application tasks onto the cores in NoC is defined at the design time, i.e., the decision regarding mapping tasks is made before the execution.

FIGURE 1. Application mapping onto NoC.

It means that the mapping is performed offline before the application execution. The static mapping policy always attempts to define the finest possible positioning of tasks in the offline design time mode for a particular application and the target inter-communication infrastructure. Once the mapping is finalized, the mapped tasks are executed at run-time, and the mapping cannot be changed. Due to the algorithm complexity and the lengthy execution time of the mapping solutions, the static mapping techniques may not be appropriate for dynamic workload scenarios [26].

# A. CHALLENGES AND CONSTRAINTS OF REAL-TIME/RUN-TIME MAPPING

A dynamic mapping technique can allocate each application task onto a core at run-time in contrast to static mapping. A system may encounter various challenges and face constraints at run-time that arise from dynamic variations of system conditions in its operation. Real-time NoC mapping is a complex optimization problem as it requires specialized strategies and techniques to meet real-time constraints while adapting to varying conditions. At a high level, some of the key constraints and challenges while generating an optimal mapping for real-time systems are resource and timing constraints, dynamic workload-related challenges and constraints, fault tolerance, resource sharing, and reconfiguration-related challenges.

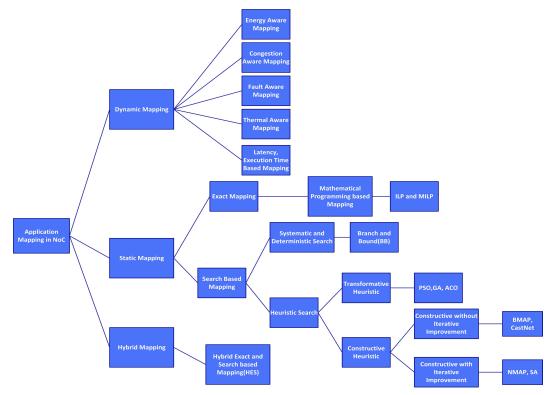

Availability of resources and satisfying task deadlines are significant challenges that need to be addressed using state-of-the-art mapping methods. One significant challenge is the potential performance degradation brought on by an overwhelming workload on some cores while others remain underutilized. Also, faults may occur at any core, further impacting the system's performance. Another major issue is congestion, which may occur when links between the cores become overloaded, leading to reduced system efficiency. One other challenge of thermal variations that may threaten the system's performance and reliability. Addressing these challenges during run-time is a crucial issue. The system must be able to adapt to these changing conditions. The adaption is necessary in order to optimize performance, balance workload, mitigate faults and critical thermal conditions, and alleviate congestion on heavily utilized links. Optimal dynamic application mapping algorithms offer a solution to these run-time variations and critical challenges. These algorithms involve intelligent algorithms and techniques that allocate tasks to the cores more effectively. Dynamic reconfiguration of the system's resources is performed in order to mitigate all the issues and challenges discussed. However, the algorithm may increase the computational complexity at the run-time, thus increasing the energy usage and the run-time execution delay. These challenges can be solved by designing and developing efficient NoC Application Mapping techniques. Many such techniques that address the complex challenges are presented in this research work and organized into sub-categories. Design time mapping, i.e., static mapping, is generally recommended and widely used for NoC multi-core systems because dynamic mapping may significantly cause excess communication overhead, eventually increasing the system's overall delay, thus affecting system performance. However, the static mapping techniques do not consider the overall network load, average channel load between the cores, and load balancing amongst the cores. Therefore, the dynamic mapping techniques have significant advantages over the static mapping algorithms. In summary, Figure 2 presents the categorization of various mapping techniques.

#### **B. DYNAMIC MAPPING TECHNIQUES IN NOC**

Dynamic (run-time) mapping approaches are needed when application tasks are required to be inserted into the system at their run-time. After the tasks have been mapped, task migration strategies can revise the placement of tasks that are already mapped if there are changes in the user requirement or application execution is needed to enter the system. Dynamic mapping can be either distributed or centralized, depending upon the type of control management unit that performs mapping-related activities at run-time. In centralized dynamic mapping, a centralized core, referred to as a manager core, makes the mapping decisions, whereas, in distributed mapping, multiple agents or nodes share network information or status to make the optimal mapping decision. Applications, such as multimedia and networking that run on heterogeneous multi-processor SoCs (MPSoCs), usually have a diverse workload. This means that a variable number of tasks are simultaneously being executed at the MPSoC. For dynamical workloads, this can necessitate the execution of task mapping at run-time to satisfy realtime constraints. A multi-core processor also uses task

FIGURE 2. Classifications of application mapping techniques.

migration strategies to enhance run-time efficiency. It entails either relocating tasks when the performance obstruction is found or distributing the workload more evenly among the multiple processors. In contrast to task migration, dynamic task mapping allows the insertion of new tasks into the system on the fly. Various heuristic mapping algorithms are prominently used in run-time mappings. These heuristics are rule-based mechanisms that consider certain factors such as task communication patterns, load balancing, and proximity. They help to optimize tasks to PE allocation in real-time systems while ensuring faster communication, and then the system performance is improved.

The primary cost function in mapping techniques is optimizing the occupation of links in NoC systems. Performance improvement can be achieved if a mapping algorithm can minimize NoC congestion. MPSoC architectures can be considered as processing nodes that communicate with one another through a network. The processing nodes or cores can run either hardware or software tasks. The hardware operations are carried out in reconfigurable units or by dedicated IPs. The tasks are allocated to the MPSoC resources, though the number of tasks may surpass the number of available processing elements. One processor may be nominated as a manager processor, which manages and controls the system's resources. When the MPSoC begins its implementation, only the immediately required activities are assigned to the processing elements. When the execution is started, only initially needed tasks are mapped to the system. When a given task attempts to interact with another task that is not yet present, a new task is assigned. The main responsibilities of a multi-processor (MP) are resource control/management, task binding and mapping, task relocation or migration, and managing the reconfiguration process. When tasks begin to execute, the communication requests made by the application tasks are first carried to the MP, and they can dynamically change the configurations. If the destination is not present, the MP executes a dynamic mapping algorithm to map the tasks to the cores.

First free (FF) mapping in [27] finds the first available core and assigns it a task. It is one of the basic and simplest mapping algorithms. The task mapping follows the sequential order from the origin of the NoC, i.e., (0,0) location, to the end of the NoC platform. The mapping technique does not consider the congestion or cost evaluation while the mapping is performed. In the nearest neighbor (NN) mapping technique, the free node is searched, and the task is allocated to that free node around the node requesting the task execution. The algorithm aims to map the tasks as close as possible to each other within a small area. The FF and NN mapping techniques are discussed in [27] and [28]. Although the tasks in the NN algorithm are mapped closer to one another, this approach does not consider the inter-communication cost among the tasks. Thus, the tasks may be placed at a distance from each other, and then it results in increased overhead. In [29], the authors proposed a smart NN-based task mapping approach. The proposed algorithm divides an architecture into virtual clusters with virtual boundaries such that the tasks of the multiple

applications can share the resources in different clusters. Each cluster provisions one initial task allocated to its central PE. Once the initial mapped task executes and requests for its corresponding communicating task, the algorithm maps the next incoming requested task onto the same PE if the PE has the required capacity. This results in the decreased overhead of communication. By mapping multiple tasks on the same PEs, the approach can be beneficial as it mainly allows mappings of tasks closer enough to each other for the sake of communication overhead reduction.

Communication-aware technique [30] having packingbased NN technique, which investigates the available resources before suggesting the near to communicating tasks on the same PE, is presented. Moreover, the proposed approach prioritizes the application tasks in close proximity to further minimize the communication overhead. The experimentations and analysis show that the proposed technique is more effective in alleviating the congestion in NoC than the other existing alternative techniques. The communication energy mapping technique discussed in [31] maps tasks with higher communication close to each other. The algorithm maps the task having the highest communication volume to the first available PE. The neighboring tasks of the already mapped task get sorted in order of the communication volume. The task with the highest communication is selected and mapped to the core having the smallest distance from the already mapped Processing element or core. Similarly, all tasks are mapped to the nearest available PE.

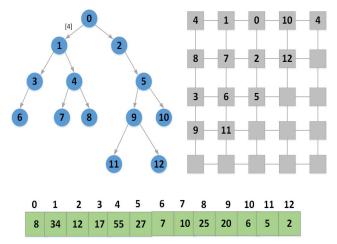

Consider the application task graph [31] as shown in Figure 3. It contains the task graph showing tasks (circled nodes) from 0 to 12. The communication volume of all the independent tasks, which is computed by all the incoming and outgoing volumes of data at the specific node, is represented in the form of a list (green-colored array/list shown at the bottom of the task graph). Because task 4 has the highest communication volume, i.e., 55, it is first mapped to the mesh-based NoC platform in Figure 3 (shown on the right-hand side by grey interconnected blocks). Its neighbors are nodes 1, 7, and 8, and the node 1 has a higher communication volume, so node 1 is mapped next in the nearest possible location to the already mapped task 4 in the mesh-based NoC. The other two neighbors are 7 and 8, which need to be mapped next. Now, node 8 has higher communication than node 7, so task 8 will be mapped with task 4 next on mesh-based NoC. Then, task 7 will be mapped at the closest possible location. Similarly, all the tasks are mapped based on the communication volume with the already mapped tasks.

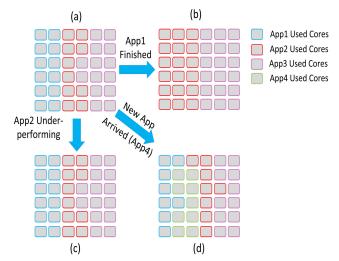

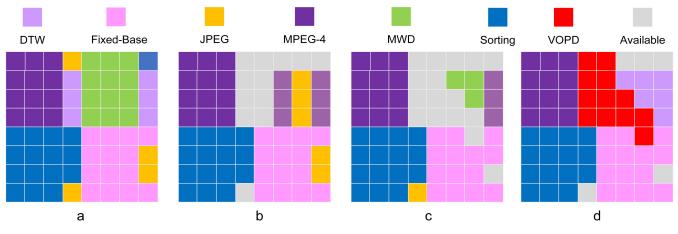

Mapping of different Applications-a motivational Example: An example of a NoC-based heterogeneous system consisting of two types of cores is presented in [32]. Multiple performance-constrained applications are concurrently executed on the cores, as shown in Figure 4. Consider such a multitasking multi-core-based scenario in which a computer system user runs an integrated development environment, e.g., a music player, an email

FIGURE 3. Task placement in a communication energy algorithm.

FIGURE 4. Various dynamic execution scenarios, (a) System with 3 running Apps, (b) App1 finishes execution, (c) App2 under-performing needing more resources, (d) New App enters the system.

service such as round cube, or starts downloading a file. The initial mapping for three applications, i.e., App1, App2, and App3, may be decided according to their performance constraints at the design time. While the application tasks execute on cores, three run-time execution scenarios might be possible that need dynamic or run-time mapping: 1) one of the applications finishes its execution; 2) an application(s) may face degradation in performance due to Congestion in the network or variation in the workload, and 3) a new application(s) arrives in the platform to be executed.

In the case where App1 completes its execution, the resources which it occupies can now be dynamically assigned to App2 and App3, which might be helpful for them to finish their execution in a short time, as shown in Figure 4 (b). Dynamic remapping is performed to allocate free cores to the running application tasks to perform their tasks faster. This may enhance the performance and be beneficial in reducing energy consumption because the two applications are able to execute and finish earlier. Dynamic mapping or remapping is also required in the case where there might be

performance degradation due to congestion or variation in workload in the network as presented in [32]. In this case, applications might face different workloads in the execution phase. The contention or workload is monitored, and action is taken so the tasks are remapped to the cores to avoid performance degradation. Figure. 4 (c) shows a case where App2 gets more resources to deal with the performance degradation problem faced during execution. The cores can also be acquired from the over-performing application, which is App3, if there are no free cores available in the system. In the last case, the user launches a new application while the other application tasks are also running and being executed on the cores. Suppose the running applications have acquired all the cores. In that case, the dynamic algorithm might check for available possibilities to remap the current tasks and assign PEs to the newly inserted application tasks to satisfy the performance constraints. Figure 4 (d) shows such a case where new App4 gets added to the system while the other applications, i.e., App1, App2, and App3, are already executing. The dynamic algorithm makes such decisions to allocate PEs of over-performing applications, i.e., App1 and App2, to App4. At the same time, App3 continues to execute with the same number of cores. Dynamic mapping techniques comprise a variety of approaches designed to address the various challenges encountered by run-time systems. Consequently, these techniques can be further categorized based on the specific conditions or circumstances that necessitate the use of dynamic application mapping. One such category is congestion-aware dynamic application mapping. In such dynamic mapping, the application tasks are assigned to the PEs considering the congestion in the network links. Also, once the cores are mapped and executed, any link faces more congestion, and then the tasks can be re-mapped to the other cores having links with lesser congestion. Therefore, dynamic mapping facilitates the development of congestion-aware mapping solutions in run-time or real-time execution of the NoC. Another category is thermal-aware dynamic mapping, which considers the thermal characteristics of the components used in the NoC when mapping application tasks. Dynamic mapping also has significant importance for mapping techniques that adapt based on the occurrence of faults in the cores or routers. So, once the cores on which a task is mapped are prone to any defect or fault, the task is re-mapped to the other available cores so that the system is fault-aware and avoids any permanent fault by using fault-aware dynamic mapping techniques. Dynamic application mapping is also applied to scenarios where the mapping can be adapted at a run-time based on the load balancing performed amongst the network cores. Application mapping techniques are further discussed as follows:

# 1) ENERGY-AWARE DYNAMIC APPLICATION MAPPING TECHNIQUES

Reduction of energy consumption and management of network load are key challenges in designing multi-core

NoC systems. Application mapping plays a vital part in the design of such systems. Efficient and optimal task mapping helps significantly minimize the total energy consumption and communication overhead between interdependent tasks; hence it plays a major role in the performance enhancement of the system.

In [30], the proposed technique investigates the available cores ahead of recommending the adjacent tasks of the application on the same PEs. The technique tries to place tasks in close proximity to deal with and reduce the overhead involved in communication. The proposed algorithm works to decrease energy consumption as well as the total application execution time. However, as the degree of nodes in the application graph increases, more tasks are mapped onto the same processing cores and potentially leads to deadlinebased misses. Compiler-based task mapping technique [33] is presented in one of the works, which reduces energy consumption and improves the efficiency of the system. The experimental outcomes and analysis show that energy consumption is calculated based on the scenarios with and without packet routing and task-to-core mapping. The authors in [31] have systematically studied selected run-time application mapping techniques using the same collection of assumptions, platform, and device models. An extension of one of the algorithms, i.e., communicationaware packing based nearest neighbor (CPNN) technique, has also been proposed that helps to minimize communication overhead between the interlinked tasks. In addition, the authors incorporated high-level Petri nets to perform systematic verification and abstraction of the proposed methodology. The proposed mapping algorithm achieves a reduction in communication cost as well as end-to-end packet latency. It also reduces energy consumption for small mesh NoCs.

The authors in [34] proposed an efficient knapsackbased bin-packing technique for workload management that positions tasks so that available processing cores are exploited to the greatest extent possible. An algorithm with task swapping capability has also been presented that attempts to further refine the task placement as decided by bin packing algorithms. The experimentation is performed to improve the energy and network load. An energy-aware based scheme [35] is presented for NoC that aims to obtain the reduction in the communication energy. In the first phase of the technique, the evaluation of the connectivity state of applications at run-time is performed, and the task having the largest amount of communication is picked and mapped. In the next phase, the tasks adjacent to the already selected tasks are sorted by communication volume and allocated to the nearest PEs. In [36], the authors proposed a task assignment scheme while incorporating user behavior. The capability of having a user behavior effect empowers the system to react to real-time changes more quickly, and then the system adapts dynamically according to the user requirements. By using the sequence of events, the algorithm determines the user behavior once it interacts with the system.

Several techniques are proposed and presented for the solution of the task allocation problem while considering communication energy optimization. The incorporation of user behavior in the algorithm further reduces communication energy. However, additional computational overhead is introduced due to the machine learning schemes and techniques for processing user behavior. The Mesh network can be divided into multiple clusters so the applications are able to run in their specific clusters. In some cases, the application's tasks exceed the number of the selected cluster's processors. In such cases, if the tasks from the same application are assigned to different clusters, they may cause performance degradation. This issue is addressed in [37] in which an efficient mapping approach incorporating multiple clusters is presented in which the placement of the tasks belonging to the same application is performed in the same cluster's region. In the first phase of the algorithm, static clustering is performed to collect the data regarding the count of tasks per application. In the next phase, dynamic clustering is implemented to accommodate the desired applications in the clusters. The technique achieves energy reduction while enhancing the performance of the system.

A dynamic cluster size-based technique [38] is presented for a multi-core NoC platform that incorporates distributed resource control and management. The architecture of the NoC is distributed into several clusters of the same size at the initialization phase. The clusters can then borrow cores from neighboring clusters to efficiently assign the application tasks at run-time. The technique effectively balances the workload of NoC and the Energy consumption reduction.

For the application task mapping of tera-scale-based NoC platforms, a reclustering-based approach having decentralized-agent phenomena is presented in [39]. The authors suggested a cluster-based task mapping strategy for task mapping in which the NoC cluster's size changes at run-time accordingly based on the load of the system and the communication-based pattern, thus minimizing overall energy consumption. In [40], a run-time mapping heuristic is proposed based on a tradeoff between processor load and communication volume. The presented architectures are divided into clusters with fixed sizes at design time. Then, a reclustering process can change the cluster size at run-time based on the application mapping. Energyaware scheduling is investigated in [41], and the scheme is applied to real-time streaming applications executed on edge devices. A revolutionary re-timing-enabled strategy is designed to convert the dependent-based workload to an independent task-based model to free up energy and unused slack in processors. In addition, ARSH-FATI, which is a novel population-based algorithm, is presented that can dynamically switch between exploitative and explorative search approaches in real-time to maximize efficiency. In addition. a contention-conscious earliest edge consistent deadline first (EECDF) scheduling technique is also proposed that jointly performs application task mapping and ordering. An efficient mapping technique [42], which is known as a hierarchical and dependency-aware (HAD) technique, is presented. In this technique, one core is dedicated to being a global manager that runs the HAD scheme. The number of transitions of the tasks is contrasted with the available cores in the initial step, while in the second step, the mean occupied position (MP) is calculated to decide the placement of the cores. In some cases, application tasks are not always executed on allocated PEs simultaneously. Thus, there can be PEs having mapped tasks that are still idle and waiting for the data to be received for processing. These situations may arise in NoC and may lead to low utilization issues of PEs while application mapping schemes are applied. A hierarchical and dependency-aware application mapping algorithm has been reported in [43] that covers the above-mentioned issues and aspects of spatial mapping and task interdependency. The proposed algorithm works such that when an already mapped task completes the execution, the allocated PE is released, and another unmapped task is allowed to be mapped. Thus, fewer PEs are required in the region in the region selection phase. The algorithm helps to increase the elasticity of future tasks and creates an impact on the latency and higher utilization of the resources.

### 2) RELIABILITY-AWARE OR FAULT-TOLERANT APPLICATION MAPPING TECHNIQUES

The emergence of deep sub-micron-based technology has aggravated various reliability-related concerns in multi-core platforms, including NoC. Due to the quick rise in the elevation of permanent faults, aggressive technology scaling has spotlighted the issues and concerns of Reliability. Many factors, such as accelerated aging effects, including electromigration, manufacturing, and testing-based challenges, are the major causes of these faults. The overall reliability is also concerned with the existence of soft upsets produced due to the cross talks, coupling noise, and transient faults. To overcome the major issues that can degrade the system in terms of reliability, the above-mentioned factors are quickly becoming an issue to be reckoned with [44]. Considering these faults, the system's reliability has become one of the key challenges in NoC architecture and design [45], due to which extensive research in this area is carried out in today's era.

Various research works presented fault models and categorization related to NoC design. The major problems and factors causing reliability issues have been discussed in the research work [46], [47], [48] fault-tolerant models and various techniques are also presented that relate to the diagnosis and avoidance of faults to intensify Reliability. To deal with faults at the application level, dynamic application mapping techniques have emerged to be prominent and efficient techniques that have contributed to enhancing the overall Reliability of the system. If any core in the NoC becomes faulty, its mapped tasks can be remapped to any other available non-faulty core. So, unlike static mapping, the decision of migrating tasks of the faulty cores to the available cores can be made at the run-time considering the status of the NoC platform, multiple events triggered, which includes different fault scenarios, availability of the resources or new enabling applications, etc. Failures in single and multiple PEs are addressed by incorporating a general manager [49] that performs the remapping. A highly efficient mapping technique is implemented to identify the initial mapping region in the offline mode. The second step maps applications dynamically by using the optimized algorithm Kuhn-Munkres that remaps applications to PE in a newer region nearer to the initial region. The scheme makes an effort to minimize the communication overhead and the energy while dealing with the faults at the same time.

A dynamic decentralized resource based [50] and application-driven task mapping technique is presented for three-structured-based streaming applications. The technique's major aim is to reduce contention and communication costs while considering faults. To mitigate faults at the systems level, a system-level run-time fault-tolerant application mapping technique [51] is presented. The main objective is to optimize the NoC performance and consumption while considering specific permanent, intermittent, and transient faults in NoC. As a dynamic technique, it identifies spare core placement and performs migration of faulty cores to spare ones, thus reducing the failure contamination area (FCA). The paper emphasizes various scenarios of spare core placement for faulty cores. The proposed technique is highly efficient, and significant throughput improvements are achieved as compared to the techniques not incorporating faults. A methodology for heterogeneous multi-core processors has been proposed in [52] that estimates near-optimal task mappings intending to enhance the factor, mean workload to failure (MWTF). An artificial neural network (ANN) can estimate the vulnerability factor in RISC-V processing cores at run-time to achieve this. An optimized run-time application mapping has been achieved using the proposed technique, mainly targeting better MWTF and MWTF/energy tradeoffs.

In [53], a dynamic fault tolerant mapping technique has been presented that considers the application tasks' temporal attribute and the faults' timing record. Regarding the state of the cores, a fault-aware technique has been presented that reduces the overall communication energy and improves the quality of service for the running applications. A faulttolerant-enabled mapping scheme is introduced in [54], which proposes the placement of spare cores flexibly in the mesh of tree-based NoC. The algorithm incorporates integer linear programming (ILP) and particle swarm optimization (PSO)-based application mapping under fault scenarios so that the tasks on the faulty cores can be executed at the spare cores in case of failure. The experiments are carried out in static as well as dynamic scenarios to optimize latency and throughput. In [40], a run-time mapping heuristic is proposed based on a trade-off between processor load and communication volume. The proposed architectures are divided into clusters having fixed sizes at design time. Then, a re-clustering process can change the cluster size at run-time based on the application mapping. The presented work aims to increase system reliability while making a trade-off between processors' load and communication volume. Several fault-tolerant application mapping approaches are presented that aim to mitigate permanent faults. They are also implanted in field programmable gate arrays (FPGAs). However, architectural-based aspects are limited in certain approaches. The fault-tolerant-based mapping approach for NoC has been reported in [55] that offers to place the spare cores flexibly onto NoC having torus topology and takes into account the faults as well. ILP and PSO have been presented in order to place spare cores while mapping. In the next phase, the routing algorithm and spare ore placement are performed on FPGA, incorporating real-time fault injection and fault-tolerant mechanism. The algorithm is analyzed and compared with other techniques in dynamic scenarios and is found to be efficient with regard to communication cost and run-time. The experimental flow of the proposed fault-based application mapping is shown in Figure 5.

Fault tolerance core mapping (FTCM) is a system-level fault-based task mapping scheme introduced in [56]. In order to manage faults in a multi-core-based NoC platform, the scheme offers core mapping based on variable-sized applications while taking into account the spare cores taking responsibility for the failed cores' tasks. The mapping is first performed using weighted communication energy and the average distance between the nodes. Secondly, it incorporates the spare core placement strategy. The tasks of the cores having higher failure probability are shifted to the spare cores in the network, thus enhancing the overall reliability.

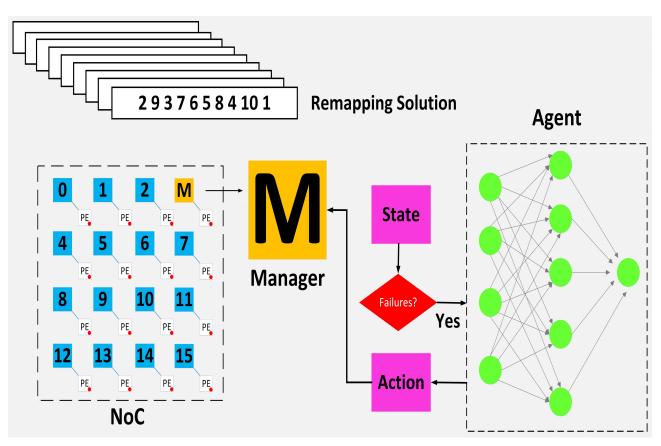

To achieve reliability in NoC, a hybrid reliability-based mapping approach has been presented in [57] that employs multi-objective based optimization along with reinforcement learning (RL) to provide optimal mapping solution in fault scenarios. The algorithm works in two phases. In the initial step, a set of best remapping solutions are generated offline for various fault scenarios that use a biogeography-based optimization algorithm to reduce energy and migration costs. In the next step, an artificial neural network agent has been trained to select the optimal remapping solution from the already generated ones. Using the proposed algorithm, this algorithm features to recover from the failures at the run-time. This technique proves to be better in terms of reliability and ensures a reduction in overhead that is caused by re-mapping the solution's storage. The RLbased run-time application mapping platform is shown in Figure 6. Many research efforts have been made in order to solve application mapping problems, but they do not always consider other dimensions, such as topology or routing algorithm, in their approach. However, one of the research works [58] delves into fault-tolerant techniques for application-specific NoCs (ASNoCs) while also considering routing algorithms. The work addresses persistent defects in ASNoC interconnection links by offering a meta-heuristic

**FIGURE 5.** Experimental flow of fault-tolerant application mapping onto torus topology based NoC.

approach based on particle swarm optimization (PSO) to deploy spare links and introducing fault-tolerant routing algorithms. The approach is implemented using an FPGA board. The experimental outcomes show considerable gains in performance measures, validating the efficacy of their strategy in comparison to earlier efforts. Overall, the research provides insightful recommendations for improving the efficiency and reliability of ASNoCs in the presence of link problems. Some techniques are developed for the already-known task graphs. However, researchers strive to develop techniques in order to tackle unseen graphs as well. One such technique, i.e., fault-tolerant multiapplication onto regular NoC (FANC) [59], has been proposed, which introduces a fault-tolerant application mapping approach based on Machine Learning (ML). The technique carries adaptability to unseen graphs and topologies while offering robustness as well as an improved convergence rate. It incorporates an ML-based model to extract pertinent information from the search data, integrating it into the search process efficiently. The experimental results prove the technique to be effective in terms of better communication cost, latency, throughput, and power usage. The fault-aware mapping techniques in NoC improve system reliability by seamlessly transferring tasks of faulty cores to the available free cores. However, it entails a trade-off between performance and workload distribution. Energy and power consumption. The techniques are efficiently developed such that they can mitigate faults but, at the same time, require careful consideration of these tradeoffs.

### 3) CONGESTION-AWARE DYNAMIC MAPPING TECHNIQUES

NoC platforms allow multiple PEs to exchange and process information simultaneously communicated over multiple links. Hence, it is highly desirable to entail such a mechanism or functionality that parallel communication between different numbers of PEs is free of congestion or has the least possible congestion. The occurrence of congestion and network contention within NoC can remarkably affect the entire system's performance in terms of degradation in efficiency and throughput [60], [61]. Network contention can be one of the causes of the start-up time being delayed or the completion time of tasks being held up for longer than expected. Thus, a reduction of network contention within NoC is one of the main concerns of researchers today. Network congestion is one of the major challenges [62] and occurs when some other data transaction occupies a channel or a link, and the remaining data packets have to wait and are queued up until the required link is available.

Dynamic or run-time application mapping can be carried out while considering the congestion and contention among the various cores or links. Different dynamic application mapping approaches are presented in the literature, which attempts to map the task of the applications on the processing cores considering the congestion in the NoC Platform. The work in [27] aims to reduce execution time and congestion by implementing a congestion-aware application mapping approach in NoC-based systems with dynamic variable workloads. Moreover, comparisons of various application mapping algorithms, such as path load (PL), minimum maximum channel load (MMC), and minimum average channel load (MAC), are conducted based on average channel occupation. Furthermore, a clustering approach for mapping multiple applications on multiple clusters is also presented. To reduce congestion and the communication energy in NoC, the author in [63] proposed a task mapping heuristic and a definite switch-based platform that can reduce the congestion occurrence due to simultaneous access to the shared memory in NoC Platform. The proposed technique is limited to the single task execution mapped to each processing element. Only single shared memory is incorporated while conducting experiments for the smaller Mesh sizes such as  $4 \times 4$ . In [29] the author has proposed a dynamic task mapping technique that maps multiple higher communicating tasks onto that same PE or at PEs closer to it. The approach reduces overall communication overhead, congestion in the network, and energy. However, load balancing between the available cores is not considered in the proposed technique. Communication energy-based global optimization is not achieved for all the processing cores, as only the cores nearby are considered for placement on the same PEs. The author in [64] proposed a run-time application mapping technique that employs a preprocessing step, which helps minimize the communication

FIGURE 6. RL Based run-time application mapping [57].

overhead and evenly balance the load between the PEs. This dynamic technique helps to enhance the system performance by optimizing application execution time, resource usage, and energy consumption. However, computation time and algorithm execution time are increased due to pre-processing steps in the algorithms. Experiments have been conducted on the smaller NoC sizes with a limited number of applications. To deal with communication overhead and to optimize NoC in terms of congestion, run-time mapping heuristics have been proposed in [65]. In this technique, the application's communicating tasks are assigned to the same processing cores or close to each other within a particular region. The proposed algorithm creates virtual clusters to map the initial tasks. The analysis has been performed with a 8times8 NoC, and the work only considers the single task to be mapped on PEs.

Similarly, in [66], a dynamic application algorithm is proposed that considers NoC contention. The presented algorithm is divided into two stages. The first step involves identifying a rectangular area appropriate for mapping the incoming application. Then, in the following steps, application tasks are assigned to processing cores within the specified area of the algorithm based on the communication between the tasks. To reduce internal and external NoC congestion, another run-time application mapping approach is proposed in [67] that attempts to reduce the internal and external NoC congestion. The main drawback of the technique is that for mapping the first task, its highest number of edges is considered. However, the communication of the tasks is not considered for selecting the first task.

In [68], an efficient dynamic task mapping approach is presented, which incorporates congestion speculation (DTMCS). The algorithm not only maps application tasks to the PEs efficiently but also takes into account future traffic patterns based on link utilization. Instead of only focusing on improving the current packet blocking situation, the presented algorithm attempts to improve the overall congestion by the link usage-based speculation window in NoC platforms executing applications with real-time traffic. The analysis is done using a large communication volume with complex traffic patterns, and the presented algorithm shows minimal communication latency. In [69], an optimized platform CAP-W for wireless NoC is presented with congestion-aware features that aim to reduce internal and external congestion. The algorithm consists of three phases. An adaptive routing algorithm capable of balancing the usage of wired and wireless network links is proposed as the first step of the algorithm. In the second phase, a runtime application mapping technique is implemented that minimizes congestion probability. In the third phase, a task migration scheme is implemented that considers the dynamic variation regarding application behaviors. The analysis shows

significant improvement in congestion in the platform over processing cores of wireless NoC.

A congestion-aware mapping scheme has been proposed in [70], which optimizes the core mapping using link betweenness centrality to relieve congestion from heavily loaded NoC links. The data volume traversing through the NoC links is monitored. The mapping is performed based on that information to optimize the NoC in latency and congestion. Mapping and scheduling of the applications in dynamic schemes either do not consider communication workload or approximate network congestion while not considering its effect on the performance of tasks regarding their timings. An enhanced technique for dynamic task allocation as well as the scheduling [71] is developed, having the capability of link contention awareness, which together assigns the tasks on the PEs while scheduling the communications on the links. The proposed technique can select a route to mitigate network contention while the application tasks are being executed. The analysis shows the proposed technique's efficacy regarding deadline satisfaction and improving the latency of the executed applications. A task mapping technique [67], for a proximate mapping region, is presented that attempts to minimize internal as well as external congestion. For initiating the allocation process, the algorithm chooses the first processing element with the largest number of free neighbors close to it. However, the technique can cause disintegrated free processing cores as the algorithm selects the initial PE with sufficient neighboring PEs for the allocation of all application tasks. In [72], a contiguity adjustable based square allocation (CASqA) technique has been proposed that aims to allocate the application's task onto the multi-core architecture within a square region. The algorithm allows enough flexibility to customize mapped processors while focusing on the application mapping solution's internal congestion and energy dissipation reduction. Congestionaware mapping techniques address various contention-related issues in NoC at loaded links. These techniques effectively mitigate congestion occurrences, minimize computational complexity, reduce remapping overhead, and help to achieve balance amongst system objectives such as energy efficiency and response time.

### 4) THERMAL-BASED OR TEMPERATURE-AWARE DYNAMIC MAPPING TECHNIQUES

Due to technological advancements, it is now achievable to integrate a significant range of IP cores, processing elements, and memory modules on a single chip. However, the close placement of the cores has produced thermal hotspots within the multi-core platform. Ensuring and establishing thermal protection in real-time systems is a difficult challenge, particularly in scenarios where multiple applications are in execution at different times. Due to technological advancements and technology scaling, integrated circuits are becoming vulnerable to many thermal-based hazards, which

factors, along with the close spacing among the cores. Critical temperature rises have a number of major consequences, including a decrease in transmission speed, a decline in reliability, and an increase in energy usage. The research work in [73] demonstrated that with a 10 percent rise in temperature, the latency of on-chip interconnects rises by 5 percent. The rise in temperature of the on-chip elements can be the major cause of the permanent failures that deteriorate the system performance and are irreversible. In certain scenarios, the failed core may cause the system to totally collapse. Therefore, the temperate rise has become a significant concern in NoC. In multi-core real-time-based platforms, the applications are dynamically entered into the system for the execution [74]. Therefore, application mapping is one of the major steps in the NoC multi-core platform design that influences the

may occur due to increased power density and many other

in the NoC multi-core platform design that influences the overall system performance. While the applications arrive and enter the system to be executed, they exhibit variable thermal attributes that are unknown ahead of the execution. Static approaches are not fruitful as they consider the thermal profiles in the offline mode instead of the run-time scenarios. Therefore, in real-time platforms, it is of major concern to use dynamic thermal-based task mapping strategies for managing the temperature of on-chip elements while dynamically executing the application on the NoC multi-core-based platform. Thermal aware mapping ensures that the on-chip interconnect meets the thermal specifications. However, the time involved in the migration of the tasks might negatively impact the efficiency of the application in terms of timing. Hence, thermal aware task mapping is a challenging task in terms of real-time dynamic framework.

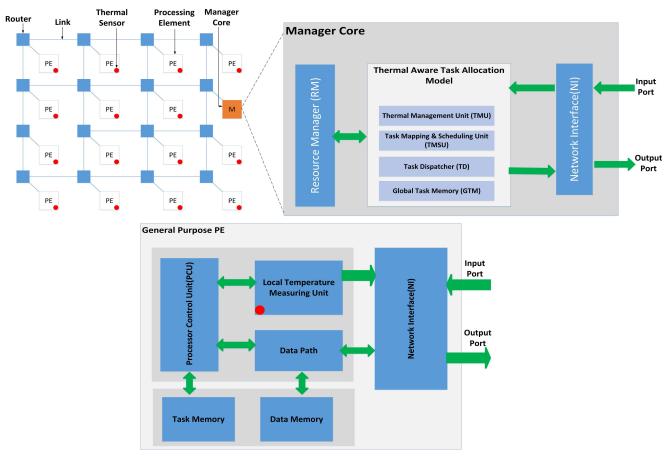

To deal with the thermal instability issues of the multi-core platforms, various system-level thermal mapping techniques, scheduling techniques having thermal-aware characteristics, and dynamic voltage scaling techniques may be employed. In [74], an improved thermal-based dynamic approach incorporating task mapping and scheduling has been presented that uses a non-profiling scheme for NoC platforms. The presented thermal-based technique maintains the integrated circuit's thermal safety specifications by jointly considering the threshold-based thermal control scheme along with a run-time task (re)allocation technique. The research work reduces the chip's peak temperature compared to the other dynamic approaches and reduces the application's average packet delay while satisfying the task deadlines. Figure 7 shows the overview of the system model.

Communication latency and chip peak temperature optimization may be difficult in certain dynamic scenarios. In certain cases, mapping tasks close to each other can reduce the latency, but it may lead to poor heat dissipation. To resolve this issue, an efficient dynamic application mapping scheme is proposed in [75] that reduces the application's communication latency and running time while managing the thermal attributes. This technique first selects the 3D cuboid area within the NoC network for each incoming

FIGURE 7. Overview of system model [74].

application by having a certain number of occupied vertical layers along with its distance to the heat sink. This is done to allow optimization regarding both the performance and the peak temperature. In the later phase, exact core regions are determined, and task to core mapping algorithm executes for the final mapping. This algorithm gives optimized results in terms of total running time and communication time while also taking into account the thermal constraints.

In [76], a power-thermal task allocation technique has been proposed with a reconfigurable NoC framework. Balanced mapping is provided for multiple applications in multicore CPU-GPU-based NoC systems in the dark silicon era. Task mapping and resource configuration are formulated by incorporating LP to look for the optimum solution. Distributed resource management with an efficient, balanced mapping technique is proposed to minimize the thermal hotspots and improve the run-time performance considering the thermal budget and communication constraints of multicore NoC. For the purpose of comparisons, implementation of minimum path contiguous task mapping has also been implemented. A fault self-testing/ recovery mechanism [77], [78], is proposed, and a remapping technique is implemented that ensures the migration of tasks in dynamic scenarios to cope with permanent Faults of the processing elements. The proposed work presents two modules, and one is the task migration module incorporated in each PE that is responsible for extracting critical data from faulty PEs. The other module is run-time-based task remapping, which searches for the optimum remapping for that given fault scenario. The work reduces power consumption, maintains load balancing, and avoids thermal hot spots.

To obtain a balanced thermal profile while the applications are in the execution phase, a distributed thermal management framework is presented in [79]. A neural network is implemented for the thermal throttling, and the algorithm assesses the task migration based on benefits between neighboring cores. Although the algorithm performs well in terms of thermal management of the cores, but additional functionality is needed for the neural networks of each core to be trained. For real-time chip temperature estimation, a thermal management-based technique is presented in [80]. which uses a support vector machine (SVM). Dynamic thermal control on overheated cores entails voltage/frequency minimization to keep the chip's temperature within limits. The real-time mapping and scheduling problem incorporating a temperature-aware mechanism is methodized in [81]. It proposes an efficient phased steady-state mixed ILP approach that performs effective scheduling and allocation decisions based on the thermal profiles of the cores to affect the chip peak temperature directly. Application task

assignment and scheduling technique are presented that allows the designers to solve the large instances-based mapping problem but at the cost of accuracy for the running time improvements.

In [82], a highly efficient technique to enhance the lifetime and reliability has been presented that dynamically migrates the workload in a predictable fashion such that assignments and executions of the tasks are completed on time. While this strategy considers the availability of the destination core for meeting the task's deadline, its scalability regarding the platform size is constrained. In [83], a temperature-aware task-mapping algorithm is presented that can prevent hotspots by using adaptive multi-threshold values to achieve a highly uniform thermal distribution. The algorithm measures the temperature of cores and switches tasks as soon as the core's temperature exceeds the normal temperature of the chip. If a core reaches an absolute maximum temperature, it is turned off. Thus, by achieving an extremely evenly thermal distribution and stopping hot cores from reaching a certain threshold, the algorithm enhances the overall reliability of the NoC.

In [84], the proposed work uses an adaptive thermalbased scheduling technique for multi-core-based systems (A-TMS) that incorporates a number of run-time controllers to modify the service levels of the applications based on core temperature and device usage. To consider the criticality regarding the timing constraints and the tasks, the study in [85] employs a process based on workload reassignment. It employs a thermal-based application mapping approach which reduces temperate overheads and minimizes energy, enhancing the system's reliability. However, to avert and deal with the thermal emergencies that occur on the running core, the algorithm has the provision to drop the tasks to maintain reliability. In the run-time, reconfiguration of the mapping solution is done on the basis of dynamic variations in the system in terms of resources and latency of the system. In [86], the mapping reconfiguration approach is used such that a set of mapping solutions is produced at the design stage for a number of applications considering resource usage and performance characteristics. The tasks are migrated to the other PEs based on predictable reconfigurations. At the design stage, low latency-based migration routes having minimum allocated overhead between the source and target mappings are calculated. These are used at the run-time to apply mapping reconfiguration for a certain application if needed. The proposed algorithm is efficient in terms of low allocation overhead and acceptable latency. To deal with the temperature-related issues in 3D NoC platforms, an earlier constraint programming-based approach from 2D NoC is extended and applied for efficient core mapping in 3D NoC Architecture presented in [87]. In this approach, the processing cores are categorized and set to low power, medium power, and high power. They are assigned to certain places at mesh-based NoC to reduce overall communication cost and computational time while considering the thermal constraints. Moreover, tasks are scheduled on the cores based

on the matching performance level to optimize the overall computation time. Thermal-aware application mapping approaches offer various advantages such as improved system reliability, optimal thermal management, and enhanced performance. However, the implementation of these techniques increases the complexity of the design, requires additional resources, and adds greater overhead in terms of power and latency. In addition, certain thermally-aware mapping techniques may encounter scale difficulties with larger and more complex systems, limiting their applicability in certain circumstances.

# 5) SCHEDULING TECHNIQUES INCORPORATED IN NOC SYSTEMS

The performance of the system can be depicted using certain metrics, such as time consumed by computation and communication in NoC to run and execute a certain application. It is one of the major factors involved in the design. The computation time is normally dependent upon the design of the IP cores. However, the communication time is not only determined by the routing protocol, but task scheduling methods also have a major impact on it. The tasks must be executed in a certain well-established order to achieve optimal performance. This comes under the umbrella of a scheduling problem. The optimized solution to such a problem is using an efficient scheduling algorithm. A novel adaptive approach has been proposed [97], that has the ability to handle dynamism for multiple applications on the NoC platform under throughput or energy consumption constraints. First, at the design time, a set of non-dominated schedules for the tasks and their mappings are computed. During the run-time, a lightweight, adaptive scheduler is implemented to reconfigure the allocation of run-time applications on the basis of the status of a network for available cores. The run-time adaptive scheduler chooses the optimum topology for the specific application and performs task mapping using the Tetris algorithm. The algorithm works in an adaptive manner that can alter and remap the mapping of the applications at the run-time, thus delivering enough power to achieve the application's constraints.

contention and energy-aware task mapping and edge scheduling (CA-TMES) approaches called CA-TMES-quick search and CA-TMES search are presented in [88] that are used to allocate tasks to PEs in the NoC platform. The inter-voltage frequency island (inter-VFI) communication and overall makespan reduction have been achieved by mapping the tasks on the processors of VFI. In [89], an efficient scheduling technique has been proposed that schedules the periodic tasks onto the NoC architecture while employing an earlier deadline first task ordering policy. The computation of the useful temporal attributes is also performed in the presented work, allowing the tasks to satisfy the relevant constraints while monitoring the communication cost. A heuristic technique for improving energy and contention-based tasks with precedence constraints has been developed in [90]. The analysis shows that the algorithm optimizes energy usage using efficient task mapping and scheduling approaches. However, re-timings based on task level to reduce overall energy have not been considered. An energy-aware based scheduling approach is proposed for real-time applications in [41]. A re-timing-based approach is designed to convert the workload having dependencies into an independent model to get the resources. A populationbased scheme known as ARSH-FATI has also been proposed that can dynamically switch between the explorative and exploitative capabilities of search schemes for performance tradeoffs. In addition, an algorithm that is communication and contention aware based on EECDF is also developed for efficient scheduling between the tasks. In [91], an agingaware scheduling method that considers the negative bias temperature instability (NBTI) aging effect and its influence on the task scheduling framework in NoC is presented. The task scheduling model has been developed with the help of the NBTI aging model, which helps to analyze the core degradation. Considering the performance degradation and the communication overhead between the cores, a metaheuristic scheduling technique is developed based on PSO. The technique proves to be better regarding the completion time and enhanced throughput of the system compared to non-aging-aware scenarios. To deal with real-time scheduling in multi-core systems, an algorithm for the homogeneous platform is proposed in [89], with reconfigurable dependent and periodic tasks to be assigned to multiple processing cores in a NoC-based system. Reconfigurations are automated operations that allow the addition and/or removal of application tasks and their shared messages in the NoC platform. The proposed platforms incorporate a periodic task model and a novel scheduling strategy for the computation of useful temporal attributes that allow the tasks to satisfy the constraints, and the technique worked while managing the communication cost in NoC. Scheduling-based NoC application approaches can enhance resource efficiency, task distribution to cores, and communication overhead. However, challenges include scheduling complexity, overhead, and dynamic workload variations, or system uncertainty.

# 6) DYNAMIC MAPPING TECHNIQUES FOR PERFORMANCE ENHANCEMENT (TECHNIQUES IMPROVING LATENCY AND TIME, LOAD BALANCING, INCREASING THROUGHPUT, ETC.)

In [92], the best neighbor (BN) task mapping technique has been introduced that attempts to place the tasks on the best possible neighbors. The technique helps to reduce the execution time. Performance evaluation with different benchmark applications has been presented, including VOPD, MPEG-4, etc. A homogeneous NoC platform-based run-time dynamic task mapping scheme for heterogeneous NoCs is presented in [93]. The algorithm incorporates the User behavior during the application task assignment process, allowing the system to adapt more effectively according to the changes and adjust suitably at run-time. In [94], another homogeneous NoC platform-based two-step run-time approach has been proposed that is able to assign various applications tasks on the NoC in an incremental fashion while incorporating multiple voltage levels. The first step is to find a suitable area of NoC for mapping followed by a greedy dynamic-based heuristic that performs the final mapping tasks. The proposed algorithm helps reduce the overall execution time, and significant communication energy has also been estimated to be reduced. A distributed agent-based mapping technique to address the dynamic application mapping problems in NoC is proposed in [95].

In the agent-based mapping technique, agents are actually constituted of a small task that manages and keeps a record of the information about resources and their state. These agents can be placed on any node in the platform. The agents interact with one another to explore computing elements suitable for the mapping purpose. Global agents (GAs) are incorporated to keep all the clusters' global information. In contrast, the mapping requests for the local clusters are maintained by cluster agents that share these requests and information with the GAs. In an attempt to minimize communication, run-time mapping time, and task relocation time, a spiral mapping algorithm known as dynamic spiral application mapping (DSM) is proposed in [96]. The technique searches for suitable placement of tasks so as to assign the tasks in a spiral fashion, taking the start from the center towards the boundaries of the NoC-based network. The work in [65] describes the blend of hardware and software processing elements formulated on MPSoC Platform. The proposed architecture nominates one of the processing nodes out of all the nodes to act as a managing node whose responsibility is to keep the status of resource management, task binding, task resettling, and reconfiguration control. On the basis of the above-mentioned information, the manager node assigns new mapping to the application tasks. A mapping algorithm based on two phases is also proposed. In the initial phase of the algorithm, preliminary mapping on the basis of the first available place in the network is accomplished. New tasks that request allocation are mapped in the second step by employing the run-time technique. Similar to this, more comprehensive work with new mapping methods has been proposed in [30].

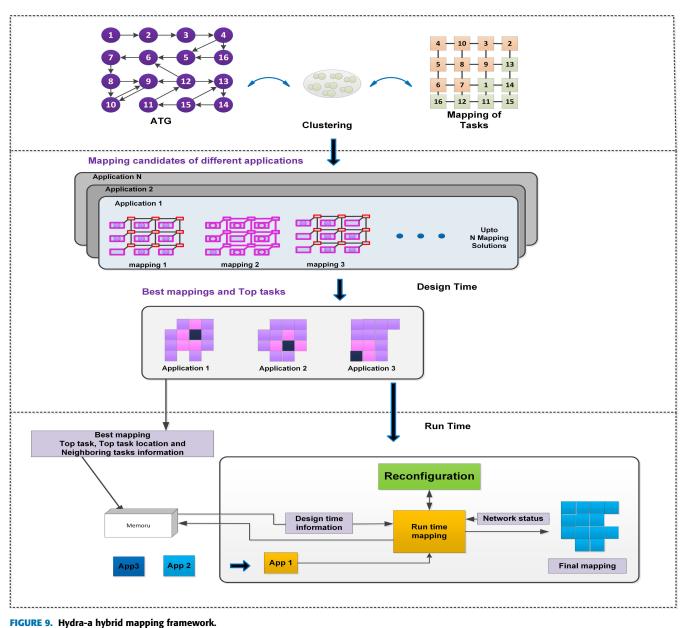

In [97], a distributed run-time mapping technique is introduced, which incorporates a strategy involving local managers and controllers. The technique is further divided into three sub-classes: the initial core, controller-based core, and manager core. The initial cores are the selection of cores for mapping purposes. While the resources are managed by the manager core, the controller core observes the status and activity of distinct subregions of the NoC. Another proactive region selection scheme (MapPro) presented in [98] is the first node selection-based technique, and the technique aims to reduce execution time and congestion. This scheme exploits the idle time between the two consecutive mapping requests to look for suitable candidate mapping regions. A dynamic multi-agent and distributed resource