Received 1 October 2023, accepted 18 October 2023, date of publication 23 October 2023, date of current version 2 November 2023. Digital Object Identifier 10.1109/ACCESS.2023.3327303

# **RESEARCH ARTICLE**

# High Step-Up Common Grounded Switched Quasi Z-Source DC–DC Converter Using Coupled Inductor With Small Signal Analysis

ATAOLLAH SAMADIAN<sup>®</sup><sup>1</sup>, MILAD GHAVIPANJEH MARANGALU<sup>®</sup><sup>1</sup>, HADI TARZAMNI<sup>®</sup><sup>2</sup>, (Student Member, IEEE), SEYED HOSSEIN HOSSEINI<sup>®</sup><sup>1,3</sup>, (Senior Member, IEEE), MEHRAN SABAHI<sup>1</sup>, AND ALI MEHRIZI-SANI<sup>®</sup><sup>4</sup>, (Senior Member, IEEE) <sup>1</sup>Faculty of Electrical and Computer Engineering, University of Tabriz, Tabriz 51666-16471, Iran <sup>2</sup>Department of Electrical Engineering and Automation, Aalto University, 02150 Espoo, Finland

<sup>3</sup>Engineering Faculty, Near East University, North Cyprus, 99138 Nicosia, Turkey

<sup>4</sup>Bradley Department of Electrical and Computer Engineering, Virginia Tech, Blacksburg, VA 24061, USA

Corresponding author: Hadi Tarzamni (hadi.tarzamni@aalto.fi)

This work was supported by the Finnish Electronic Library (FinELib) and Aalto University, Finland, under the FinELib Consortium's Agreement with IEEE.

**ABSTRACT** In this article, a new common grounded switched quasi Z-source DC-DC converter is proposed. In the proposed converter, an additional switch and a diode are used compared to the conventional quasi Z-source converter. The proposed converter provides some benefits by using a coupled inductor and switched capacitor unit. These features are providing voltage-boosting capability using a small range of duty cycles, low voltage stress on semiconductors (switches and diodes), and continuous input current waveform. In this topology, the null of the load is connected to the negative terminal of the input DC source, directly. So, the common mode voltage is kept constant. In this case, the proposed DC-DC converter is suitable for photovoltaic (PV) power generation systems to boost the voltage of PV panels. In this paper, the proposed converter and operation modes are described completely. Also, in order to show the advantages and differences of the proposed topology with other DC-DC high-step up converters, a comparative comparison study is considered. Also, the small signal analysis and control strategy of the proposed converter are provided. In addition, design considerations of the used components are given. Then, the power loss analysis of the converter is provided. Finally, in order to prove the accurate performance of the suggested topology and verify the advantages and analysis, an experimental prototype is built at 250 W output power and the related results are provided.

**INDEX TERMS** DC-DC converter, common grounded converter, coupled inductor, quasi Z-source converter.

#### I. INTRODUCTION

Recently, high step-up power electronics converters are most applicable in various fields such as electric vehicles (EVs), photovoltaic (PV) grid-tied systems, microgrids, and uninterruptible power supplies (UPSs) [1], [2], [3], [4], [5], [6], [7], [8]. For this purpose, many types of research and articles are published regarding to the high step-up DC-DC converters with different topologies [9], [10], [11],

The associate editor coordinating the review of this manuscript and approving it for publication was Jiann-Jong Chen<sup>(D)</sup>.

[12], [13]. In isolated DC-DC topologies, increasing the turns ratio of the transformer leads to emerging a large parasitic inductance, which can generate high voltage spikes, high switching losses, and intensify the electromagnetic interference (EMI) [14]. These topologies have some benefits such as high step-up feature, and isolation of the input DC supply from the output. Meanwhile, compared with non-isolated structures, these topologies usually have lower power density, higher voltage and current stress on the semiconductors, higher cost per watt, higher power losses, and lower overall efficiency [15]. Compared with single-stage topologies, multi-stage converters have some drawbacks such as higher power losses and lower efficiency, lower reliability, and using a large number of circuit components [16]. As a result, the single-stage structures with the reduced number of circuit components provide low cost and a large value of duty cycle (close to 1). This issue leads to low efficiency with high value of current ripple.

Some other high step-up non-isolated single-stage switched inductor-based, switched capacitor-based, or coupled inductor-based DC-DC converters with large duty cycles have been presented in [17], [18]. Among single-stage topologies, the Z-source converters usually operate with a low range of the duty cycle (less than 0.5) [19]. Note that, Z-source topologies can be used as DC-DC converters [20]. In order to overcome the drawbacks of Z-source topology, a quasi Z-source structure with continuous input current has been introduced in [21]. Meanwhile, Z-source-based topologies provide low voltage gain and high voltage stress on the power switches and diodes.

In order to improve the voltage gain and decrease the voltage stress of the semiconductors, some other topologies based on quasi Z-source structure are proposed. An isolated quasi Z-source-based converter using an H-bridge inverter is presented in [22]. This converter uses a large count of switches and diodes, but it cannot provide the voltage boosting feature. Furthermore, to enhance the voltage gain, the turns ratio of the transformer should be increased which causes high parasitic inductance and low efficiency. A new isolated Z-source topology has been presented in [23]. This topology uses two power switches and the range of the duty cycle is more than 0.5. Note that, this converter cannot provide high step-up voltage feature. In [24], a cascaded quasi Z-source DC-DC converter is processed which has low efficiency due to the large number of elements. A wide input voltage range quasi Z-source DC-DC converter with two switches is proposed in [25] which can't produce high voltage gain and the voltage stress on switches is high.

In addition, in [26] and [27], new Z-source structures using switched inductor and switched capacitor units are proposed. All these converters are introduced with the aim of voltage gain increasing and have own disadvantages such as high voltage stress on switches and lack of common ground between input and output. In [28], a non-isolated Z-source converter with a coupled-inductor leads to low voltage stresses on the semiconductors. But this topology requires more components and the ground nodes of load and input ports are not the same. A switched quasi Z-source converter with small duty cycle is presented in [29], which cannot reach high voltage gain. Also, the voltage across the switches is high and the topology is not common ground. In [30], a new Z-source switched capacitor-based topology has been introduced. This converter provides a high voltage boosting gain using two power switches. The topology uses a large number of inductors and capacitors. This issue leads to increase the total power loss, volume and cost of the system. Also, the power density and overall efficiency are decreased.

In this paper, a new high step-up common ground switched quasi Z-source converter with a coupled inductor and a voltage multiplier cell is proposed. This converter can reach high voltage gain with a small range of duty cycle, continuous input current, low voltage stress across power switches and the output diode. In addition, it doesn't need high turns ratio for the coupled inductor to realize high voltage levels. Note that, this paper is the expansion of our previous conference paper [10] where the theoretical analysis and comparison study are improved, the small signal model and closed-loop control are added, and comprehensive experimental tests are performed.

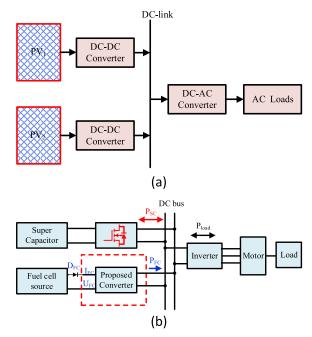

**FIGURE 1.** (a) Photovoltaic panels with DC-DC converters, (b) Fuel cell vehicles with DC-DC converter.

In most of the coupled inductor-based converters, leakage inductance is one of the critical issues; because, increasing the leakage inductance causes higher output voltage drop, higher current passing through the power switches, large duty cycle. All these disadvantages induce the converter operation with high losses and low efficiency. The higher turns ratio and the number of windings turns are important factors for higher leakage creation. In the proposed converter, the magnetic inductance of the coupled inductor is low in the continuous conduction mode (CCM) operation which causes a smaller number of windings turns for the primary side of the coupled inductor. On the other hand, the turns ratio of the coupled inductor is low due to the high voltage gain. Consequently, the leakage inductance of the presented converter is lower than the most of other high step-up converters. High voltage gain with small duty cycle, low leakage inductance of coupled inductors, continuous input current, low voltage stress

on power switches, low voltage stress on some diodes, low voltage stress of some capacitors, common ground between input voltage source and output terminals are the main advantages of the proposed converter.

For the above-mentioned properties, the proposed converter can be used in renewable energy applications such as photovoltaic panels which is illustrated in Fig. 1(a). When one photovoltaic panel is connected to a DC-DC converter, it needs a large duty cycle to increase the level of the input voltage source to the desired DC link voltage value. In the proposed converter not only the total conduction losses of the switches will be decreased due to the lower duty cycle, but also the cost of the converter will be decreased. These advantages decrease the total losses of the converter and decrease the volume and cost of the DC-DC converter instead of a converter with a large duty cycle and low efficiency. As well as in Fig. 1(a), the DC link can be considered as a high voltage DC micro-grid that can be connected to the AC grid or AC load with an inverter.

In addition, the proposed converter can be utilized in the electrical fuel cell vehicles which have two input voltage sources. These two input voltage sources consist of a supercapacitor and a fuel cell. In this case, the proposed converter can be used instead of the converters with fuel cell voltage sources which are shown in Fig. 1(b). To return the energy from the output port to the supercapacitor or input energy source and better operation, the diodes of the proposed converter are replaced with the power MOSFETs and a diode is connected to a fuel cell in series. Using a series diode in a fuel cell is an important way to connect a common ground DC-DC converter between a high voltage DC link and a fuel cell. As a result, the proposed topology can be an interesting converter for these kinds of industries. For EV applications with battery or supercapacitors input source, it is better to use isolated bidirectional DC-DC converters. This kind of application is used in reference [25], because the input voltage of the presented converter can be in a wide range, and the output voltage can be controlled for a constant voltage of the DC link.

For the proposed converter, the operating principle and steady-state analysis are evaluated in detail. Also, parameters design and the comparison with some Z-source DC-DC converters are given. Finally, the experimental results are presented which verifies the theoretical analysis.

# II. SUGGESTED TOPOLOGY, STEADY STATE ANALYSIS, AND OPERATION MODES

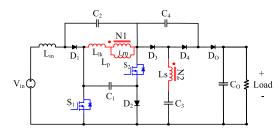

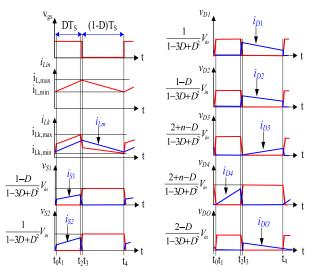

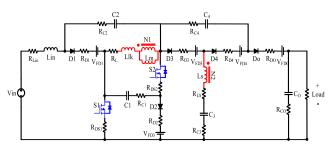

Fig. 2 illustrates the proposed switched quasi Z-source topology. Considering this figure, the proposed converter uses two power switches, five diodes, five capacitors, one inductor, and one coupled inductor. Compared with the basic topology of the Z-source topology, the proposed converter uses an additional power switch and one more diode. Furthermore, the proposed converter uses a switched capacitor unit. Considering Fig. 2, the Z-source network consists of the capacitors  $C_1$  and  $C_2$ , switch  $S_2$ , diode  $D_1$ , input inductor  $L_{in}$ , and the primary side of the coupled inductor  $L_p$ . Based on Fig. 2, the primary side of the coupled inductor is modeled by a leakage inductance  $L_{lk}$ . Note that, the magnetizing inductance and secondary side of the coupled inductor  $L_s$  is applied to boost the voltage level which is tied to the diodes  $D_3$ ,  $D_4$  and capacitor  $C_3$ . Considering Fig. 1, it can be seen that the switched capacitor consists of two capacitors ( $C_3$  and  $C_4$ ) and two diodes ( $D_3$  and  $D_4$ ). In the proposed converter, the output capacitor  $(C_0)$  is considered with a high capacitance value. The suggested topology operates in the CCM. As a result, the input inductor is chosen large enough and the input voltage is fixed to a constant value. In a full switching cycle, the proposed converter has four operational modes. Fig. 3 illustrates the voltage and current waveforms of the proposed topology. Moreover, the operation modes of the proposed converter are depicted in Fig. 3. In the following, the description of each operation mode is provided completely.

FIGURE 2. The power circuit of the proposed converter.

FIGURE 3. Voltage and current operational waveforms of proposed converter.

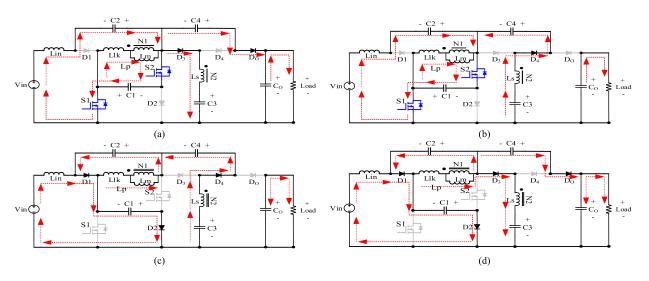

# A. FIRST OPERATION MODE $[t_0 - t_1]$

The First operation mode is shown in Fig. 4 (a). In this operation mode, the power switches  $S_1$  and  $S_2$  are in the onstate. Also, the diodes  $D_3$  and  $D_0$  are in the on-state, and the diodes  $D_1$ ,  $D_2$  and  $D_4$  are in the reverse bias. During this operation mode, the input inductor is charged through the capacitors  $C_1$  and  $C_2$ , and the input DC source  $(V_{in})$ . Also,

FIGURE 4. The equivalent circuits of the proposed converter: (a) First mode; (b) Second mode; (c) Third mode; (d) Forth mode.

the inductor  $L_m$  is charged by the stored energy of capacitor  $C_1$  during this mode. In addition, the stored energies of the capacitors  $C_1$ ,  $C_2$  and  $C_4$  are pumped to the output terminal. Note that, this operation mode ends at the moment  $t_1$ .

## **B.** SECOND OPERATION MODE $[t_1 - t_2]$

The electrical schematic of the second operation mode is demonstrated in Fig. 4(b). Based on this figure, it can be seen that in this mode the switches  $S_1$  and  $S_2$  should be turned on. Moreover, the diodes  $D_1$ ,  $D_2$ ,  $D_3$  and  $D_0$  are in the off-state and the diode  $D_4$  turns on. In this mode, the input inductor is in the charging state as the same as the first operation mode. As a result, the current of  $L_{in}$  increases linearly.

Furthermore, the primary side of the coupled inductor is still in the charging state through the capacitor  $C_1$ . During this mode, the currents of the leakage inductor and magnetizing inductor increase linearly. The capacitor  $C_4$  is in the charging state through the capacitors  $C_1$  and  $C_3$ ; hence, the current of the secondary side of the coupled inductor reduces. Moreover, the output load is supplied by the stored energy of the output capacitor  $C_0$ .

# C. THIRD OPERATION MODE $[t_2 - t_3]$

The electrical circuit of this operation mode is illustrated in Fig. 4(c), where the switches  $S_1$  and  $S_2$  are in the offstate. Also, the diodes  $D_1$ ,  $D_2$ , and  $D_4$  are in the on-state and the diodes  $D_3$  and  $D_0$  are in the off-state. Note that, the capacitor  $C_1$  is in the charging state through the input power supply and input inductor. In this mode, the capacitor  $C_2$  is in the charging state through the primary side of the coupled inductor. It should be mentioned that, mode three ends at the moment  $t_3$ .

## D. FOURTH OPERATION MODE $[t_3 - t_4]$

The current path of this operation mode is expressed in Fig. 4(d). Considering this figure, the switches  $S_1$ ,  $S_2$  and the

diode  $D_4$  are in the OFF state. Also, the diodes  $D_1$ ,  $D_2$ ,  $D_3$  and  $D_0$  are in the on-state. Regarding Fig. 4(d), the capacitor  $C_1$  is still in the charging state by the stored energy of the input inductor and the input DC source. In addition, the capacitor  $C_2$  is charged by the primary side of the coupled inductor; therefore, the primary side current reduces linearly. In this mode, the capacitor  $C_0$  and the load are fed by the input DC source,  $L_{in}$ , the primary side of the coupled inductor and capacitor  $C_4$ .

Regarding the second and fourth operation modes, as the main CCM operational modes, and applying the voltage-second balance law to the aforementioned inductors in a full switching period, the voltage values of the capacitors  $C_1$ ,  $C_2$  are attained with respect to the input voltage  $V_{in}$  as follows:

$$\begin{cases} V_{C1} = \frac{1 - D}{1 - 3D + D^2} V_{in} \\ V_{C2} = \frac{D}{1 - 3D + D^2} V_{in} \end{cases}$$

(1)

In the above equations, *D* denotes the switching duty cycle of the involved switches. The equations of the voltage across  $L_{in}$ ,  $V_{LP}$ ,  $V_{LS}$ , and  $V_{LO}$  can be obtained by using KVL in the fourth operation mode. By using these obtained equations and (3), and by omitting the  $L_{lk}$ , the voltage across the capacitor  $C_3$  can be expressed as

$$V_{C3} = \frac{1+nD}{1-3D+D^2} V_{in}$$

(2)

Here,  $n = N_2/N_1$  denotes the turns ratio of the coupled inductor. By considering the Kirchhoff voltage law (KVL) in the second operation mode, and applying (1), and (2), the voltage across the capacitor  $C_4$  is obtained as:

$$V_{C4} = \frac{2+n-D}{1-3D+D^2} V_{in}$$

(3)

By substituting (1), (3), and the equations of the voltage across  $L_{in}$ ,  $V_{LP}$ ,  $V_{LS}$ , and  $V_{LO}$  which can be obtained by using

KVL, the output voltage of the proposed converter is obtained as:

$$V_O = \frac{3 + n - D}{1 - 3D + D^2} V_{in} \tag{4}$$

Hence, the voltage gain of the suggested topology is concluded as:

$$G = \frac{V_O}{V_{in}} = \frac{3+n-D}{1-3D+D^2}$$

(5)

Assuming that the losses are negligible and by applying the Kirchhoff voltage law (KVL) in the second operation mode, the input current of the converter can be expressed as:

$$I_{in} = \frac{3+n-D}{1-3D+D^2} I_O$$

(6)

Then, the average value of the input inductor current is equal to I<sub>in</sub>:

$$i_{Lin} = \frac{3+n-D}{1-3D+D^2} I_O \tag{7}$$

Using KCL law in the fourth operation mode, the average current of  $L_{lk}$ , magnetizing inductance and the secondary side of the coupled inductor are calculated as:

$$\begin{aligned}

i_{lk-off} &= i_{C2-off} + c_{3-off} + c_{4-off} \\

i_{lk-off} &= \frac{2 - (3 - n)D + D^2}{(1 - 3D + D^2)(1 - D)} I_O \\

i_{Lm} &= i_{lk-off} + ni_{NS-off} \\

i_{Lm} &= \frac{2 + n - (2n + 3)D + (1 + n)D^2}{(1 - 3D + D^2)(1 - D)} I_O

\end{aligned}$$

(8)

In one switching cycle, the average current of the inductor  $L_m$  is constant.

#### **III. DESIGN OF PARAMETERS**

For the appropriate operation of the proposed converter, the input inductor, the magnetizing inductance and the capacitors should be designed. By using the voltage and current equations (which can be obtained by applying KVL rule in the second operation mode) and (7) for the input inductor, the value of the input inductance can be calculated as follows:

$$L_{in} = \frac{D(2 - 3D + D^2)V_{in}^2}{(1 - 3D + D^2)P_{in}f_S I_r}$$

(9)

In addition, by ignoring the leakage inductance and using the voltage and current equation (which can be obtained by applying KVL and KCL in the fourth operation mode) and (8) for the magnetizing inductor, the magnetizing inductance can be calculated as follows:

$L_m$

$$= \frac{D(1-D)^2(3+n-D)V_{in}^2}{(1-3D+D^2)(2+n-(2n+3)D+(1+n)D^2)P_{in}f_SI_r}$$

(10)

where,  $P_{in}$  is the input power,  $f_S$  is the switching frequency, and  $I_r$  is the current ripple percentage of the inductors.

By consideration of the equations (1)-(3), all capacitors can be designed as below:

$$\begin{cases} C_{1} \geq \frac{\left(1+n+(2-n)D-D^{2}\right)(3+n-D)}{(1-D)\left(1-3D+D^{2}\right)V_{r}f_{S}R_{L}} \\ C_{2} \geq \frac{(3+n-D)^{2}}{\left(1-3D+D^{2}\right)V_{r}f_{S}R_{L}} \\ C_{3} \geq \frac{(3+n-D)}{(1+nD)V_{r}f_{S}R_{L}} \\ C_{4} \geq \frac{(3+n-D)}{(2+n-D)V_{r}f_{S}R_{L}} \\ C_{o} \geq \frac{D}{V_{r}f_{S}R_{L}} \end{cases}$$

(11)

where,  $R_L$  is the load resistance,  $V_r$  is the voltage ripple percentage of the capacitors, and  $f_S$  is the switching frequency.

#### **IV. SMALL SIGNAL ANALYSIS AND CONTROL METHOD**

In the proposed converter, the input and the magnetizing inductors currents ( $i_{Lin}$  and  $i_{Lm}$ ), and the capacitors voltages  $(V_{C1} \text{ and } V_{C2})$  are chosen as state variables. Therefore, the state variables vector (x), input vector (u), and output vector (y) are considered as follows:

$$\begin{cases} x^{T} = [i_{\text{Lin}}i_{\text{Lm}}V_{C1}V_{C2}] \\ u^{T} = [d] \\ y^{T} = [V_{out}] \end{cases}$$

(12)

By using the main modes for the presented converter (modes 2 and 4), the average state space of the system can be considered as  $\begin{cases} \dot{x} = Ax + Bu\\ y = Cx + Du \end{cases}$ where, matrixes A, B, C and D are constant and can be

attained as (13) and (14).

$$\begin{bmatrix} \frac{di_{Lin}}{dt} \\ \frac{di_{Lin}}{dt} \\ \frac{du_{C1}}{dt} \\ \frac{du_{C1}}{dt} \\ \frac{du_{C2}}{dt} \end{bmatrix} = \begin{bmatrix} 0 & 0 & \frac{2d-1}{L_{m1}} & \frac{d}{L_{m1}} \\ 0 & 0 & \frac{d}{L_{m2}} & \frac{d-1}{L_{m2}} \\ \frac{1-d}{L_{m2}} & \frac{d-1}{L_{m2}} \\ \frac{1-d}{C_{1}} & \frac{-d}{C_{1}} & -\frac{(3+n)(2+n)}{C_{1}R_{Load}} & -\frac{(2+n)^{2}}{C_{1}R_{Load}} \\ \frac{-d}{C_{2}} & \frac{1-d}{C_{2}} & -\frac{(3+n)(2+n)}{C_{2}R_{Load}} & -\frac{(2+n)^{2}}{C_{2}R_{Load}} \end{bmatrix}$$

$$\times \begin{bmatrix} i_{Lm1}(t) \\ i_{Lm2}(t) \\ u_{C1}(t) \\ u_{C2}(t) \end{bmatrix} + \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix} [u_{in}(t)] \qquad (13)$$

$$y^{T} = [V_{out}] = [00(3+n)(2+n)] \begin{bmatrix} i_{Lin}(t) \\ i_{Lm}(t) \\ u_{C1}(t) \\ u_{C2}(t) \end{bmatrix}$$

$$+ \begin{bmatrix} 0 \\ 0 \end{bmatrix} [u_{in}(t)] \qquad (14)$$

Based on the method of small-signal modeling, the state variables, output, input voltages and duty cycles contain of two parts of DC (X, Y, U, D) and AC ( $\tilde{x}, \tilde{y}, \tilde{u}, d$ ).

It is supposed that the AC values are small and do not change considerably during one switching period. Therefore, the small-signal model can be displayed as  $\begin{cases} \dot{\tilde{x}} = A'\tilde{x} + B'\tilde{u} \\ \tilde{y} = C'\tilde{x} + D'\tilde{u} \end{cases}$

TABLE 1. The nominal resistance values of various components.

| Devices               | values                                                    |

|-----------------------|-----------------------------------------------------------|

| Power                 | $R_{DS} = 0.097 \Omega$                                   |

| MOSFETs               | $t_{f} = 74 \ ns$ , $t_{r} = 105 \ ns$                    |

| $S_1 \& S_2$          | $l_f = 74 \text{ ns}, l_r = 103 \text{ ns}$               |

| Diode D <sub>1</sub>  | $R_{D1} = 0.0047 \Omega$                                  |

| Diode D <sub>1</sub>  | $V_{FD1} = 1.1 \text{ V}$                                 |

| Diode D <sub>3,</sub> | $R_D = 0.025 \Omega$                                      |

| $D_4$ & $D_0$         | $V_{FD1} = 0.95 \text{ V}$                                |

| Diode D <sub>2</sub>  | $R_D = 0.025 \Omega$                                      |

| $Diode D_2$           | $V_{FD1} = 0.95 \text{ V}$                                |

| Capacitors            | $r_{C1} = r_{C2} = r_{C3} = r_{C4} = r_{C0} = 0.02\Omega$ |

| L <sub>in</sub> ,     | $r_{Lin} = 0.02 \Omega$                                   |

| $L_{lk}$ & $L_{NS}$   | $r_{Llk} = r_{LNS} = 0.02 \Omega$                         |

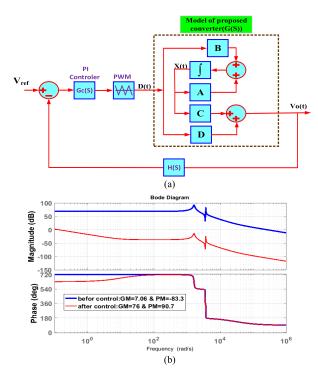

FIGURE 5. (a) Bode plots of presented converter (b) Closed-loop control system block diagram.

where, A', B' and C' are calculated in (15) and (16).

$$A' = \begin{bmatrix} 0 & 0 & \frac{2\bar{D}-1}{L_{in}} & \bar{D} \\ 0 & 0 & \bar{D} & \bar{D}-1 \\ \frac{1-\bar{D}}{C_1} & -\bar{D} & -\frac{(3+n)(2+2n)}{C_1R_{Load}} & -\frac{(2+n)^2}{C_1R_{Load}} \\ \frac{-\bar{D}}{C_2} & \frac{1-\bar{D}}{C_2} & -\frac{(3+n)(2+2n)}{C_2R_{Load}} & -\frac{(2+n)^2}{C_2R_{Load}} \end{bmatrix}$$

(15)

$$B' = \begin{bmatrix} \frac{2\bar{V}_{C1}+\bar{V}_{C2}}{L_{m1}} \\ \frac{\bar{V}_{C1}+\bar{V}_{C2}}{L_{m2}} \\ -\frac{\bar{L}_{in}}{C_1} & -\frac{\bar{L}_{in}}{C_1} \\ -\frac{\bar{L}_{in}}{C_2} & -\frac{\bar{L}_{m1}}{C_2} \end{bmatrix}, C' = [00 (3+n) (2+n)]$$

(16)

Considering the specifications of the devices from Table 1, the matrixes A', B' and C' can be calculated. Therefore, the transfer function of the presented converter before the

FIGURE 6. Proposed converter with resistances consideration for loss calculation.

implementation of the control system can be attained as (17).

$$G(s) = \frac{-2.5 \times 10^5 s^3 + 7.5 \times 10^9 s^2 - 3.3 \times 10^{12} s + 9.6 \times 10^{16}}{s^4 + 114.9 s^3 + 1.6 \times 10^7 s^2 + 1.3 \times 10^9 s + 3.6 \times 10^{13}}$$

(17)

According to (52), it can be observed that all the poles are located on the left side of the  $j\omega$  axis; however, some of them are close to the imaginary axis. This means the open-loop system is stable, but it is not desirable. The control block diagram for the presented converter is shown in Fig. 5(a). According to the closed-loop system,  $G_C(s)$  is the PI (Proportional-Integral) controller transfer function, H(s) is the feedback transfer function,  $V_{ref}$  is the voltage reference signal and  $V_O$  is the output voltage signal.

In the PI controller,  $K_i$  (integrator coefficient) is set as 0.0002,  $K_p$  (proportional coefficient) is set as 0.00001 and H(s) is considered as 0.5. Therefore, the corresponding transfer function of the voltage-loop control system can be expressed in (18), as shown at the bottom of the next page.

The bode plots of the presented converter before and after applying the control system are illustrated in Fig. 5(b). The phase margin (PM) and gain margin (GM) should be positive (PM>0, GM>0) in order to achieve stability. However, these values are  $-83.3^{\circ}$  and 7.6 dB, respectively, for the suggested converter before applying control system. After applying the control system, the values of the PM and GM reach to 90.7° and 76 dB, respectively. Therefore, the closed-loop gain and phase margins are positive and the overall system with PI controller would be desirably stable.

#### **V. POWER LOSS ANALYSIS**

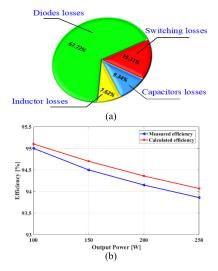

In this section, the power losses for all components are calculated. Then, the efficiency of the proposed converter with respect to the output power and the associated total losses can be achieved. At last, the theoretical efficiency is compared with experimental efficiency. Fig. 6 shows the proposed converter with all series resistances for each component to calculate the losses. The nominal resistance values and RMS current values for various components are summarized in Table 1 and Table 2, respectively. By using these nominal values and considering Table 2, the power losses for the power switches, diodes, capacitors and inductors, and the

TABLE 2. RMS Current values for various components.

| Device                | RMS currents                                                                           |

|-----------------------|----------------------------------------------------------------------------------------|

| $S_I$                 | $\frac{1+nD}{\left(1-3D+D^2\right)D}\sqrt{D}I_O$                                       |

| $S_2$                 | $\frac{1\!+\!n\!+\!(2\!-\!n)D\!-\!D^2}{\left(1\!-\!3D\!+\!D^2\right)D}\sqrt{D}I_o$     |

| $D_{I}$               | $\frac{3+n-D}{(1-D)(1-3D+D^2)}\sqrt{1-D}I_o$                                           |

| $D_2$                 | $\frac{1 + n + (2 - n)D - D^2}{(1 - 3D + D^2)(1 - D)}\sqrt{1 - DI_O}$                  |

| $D_3$                 | $\frac{\frac{\sqrt{1-D}}{1-D}I_o}{\frac{\sqrt{D}}{D}I_o}$                              |

| $D_4$                 | $rac{\sqrt{D}}{D}I_o$                                                                 |

| $C_l$                 | $\left(\frac{1+n+(2-n)D-D^{2}}{(1-3D+D^{2})}\right)\sqrt{\frac{1}{D(1-D)}}I_{O}$       |

| <i>C</i> <sub>2</sub> | $\frac{\left(3+n-D\right)}{\left(1-3D+D^2\right)}\sqrt{\frac{D}{\left(1-D\right)}}I_o$ |

| C3 & C4               | $\frac{1}{\sqrt{D(1-D)}}I_{o}$                                                         |

| Со                    | $\sqrt{\frac{D}{1-D}}I_o$                                                              |

| $L_{ m in},$          | $\sqrt{\frac{1}{3}[(2GI_{o})^{2}-GI_{o}^{2}+(DV_{o}/2Lf_{s}G)^{2}]}$                   |

| $L_{ m lk}$           | $i_{Lk} = \sqrt{i_{Lm}^{2} + (nI_{o})^{2} \left(\frac{1}{D(1-D)}\right)}$              |

| $L_{\rm NS}$          | $i_{LNS} = \frac{I_O}{\sqrt{D(1-D)}}$                                                  |

total power loss are calculated as

$$\begin{cases} P_{S} = P_{Con} + P_{Sw} = R_{DS-on}i_{S,RMS}^{2} \\ +0.5f_{s}\left(t_{r} + t_{f}\right)i_{S,av}V_{s} \\ P_{D} = \sum_{n}^{n} \left(V_{FD}i_{Dn,av} + r_{d}i_{Dn,RMS}^{2}\right) \\ P_{C} = \sum_{n}^{n} r_{C}i_{Cn,RMS}^{2} \\ P_{L} = r_{Lin}i_{Lin,RMS}^{2} + r_{Llk1}i_{Llk1,RMS}^{2} + r_{Llk2}i_{Llk2,RMS}^{2} \\ P_{Loss-Total} = P_{S} + P_{D} + P_{C} + P_{L} \end{cases}$$

(19)

By using above mentioned equations, the power losses of switches  $S_1$ , and  $S_2$ , total power losses of diodes, total power losses of capacitors, power losses of inductors, and total power losses of proposed converter can be obtained and are equal to 0.7W, 1.71W, 10.66W, 1.47W, 1.2W, and 15.74W,

**FIGURE 7.** (a) Different component Loss for proposed converter, (b) measured efficiency of proposed converter.

respectively. Therefore, the theoretical efficiency of the proposed converter is obtained and equal to 94.07%. From the theoretical equations and nominal values for the omponent, the calculated efficiency at output power of 250 W is obtained as 94.07%. Furthermore, the loss distribution for all components is depicted in Fig. 7(a). Moreover, Fig. 7(b), shows the experimental measured efficiency of the proposed converter for various output power values. The maximum efficiency for the proposed converter is about 95% at 100 W and the measured efficiency at 250 W is about 93.86% where it is 0.39% lower than the estimated efficiency.

# VI. COMPARISON STUDY FOR PROPOSED CONVERTER

In this section, in order to show the features of the proposed converter and its differences from other topologies, a comprehensive comparison is done. This comparison is based on some items such as the number of components, voltage gain, duty cycle limitation, maximum normalized voltage stress across the switches and output diode, and component stress for the presented converter and other Z-source-based converters which are listed in Table 3. The numbers of the magnetic cores in the presented converters in [25], [28], [30], and [31] are more than the proposed converter and other converters, considering that an extra magnetic core increases the total losses and cost of the system.

The numbers of the capacitors in [28], [30], and [31] are more than the proposed converter and other converters. Also, the number of switches in [25], [27], [29], [30], and [31] and the proposed converter are the same. Although,

$$G_{CV}(s) = G_C(s) G(s) H(s)$$

$$= \frac{-1.2s^4 + 3.7 \times 10^4 s^3 - 1.5 \times 10^7 s^2 + 4.7 \times 10^{11} s + 9.4 \times 10^{12}}{s^5 + 114.9s^4 + 1.6 \times 10^7 s^3 + 1.3 \times 10^9 s^2 + 3.6 \times 10^{13} s}$$

(18)

120522

# TABLE 3. Comparison of proposed converter with Z-source based converters.

| Ref      |                                                                                                                                                                                                                                                                                                                                                                                        | Num | ber o | f | Voltage                          | Duty cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Maximum Normalized Stress            |                                                          | Component stress                                                                                                              |                                                                                          |                             |                     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|---|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------|---------------------|

| Kei      | М                                                                                                                                                                                                                                                                                                                                                                                      | С   | S     | D | gain $(G)$                       | limitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VSwitch                              | <b>I</b> Switch                                          | VDiode                                                                                                                        | IDiode                                                                                   | Vc1                         | <b>i</b> Lin        |

| [21]     | 2                                                                                                                                                                                                                                                                                                                                                                                      | 3   | 1     | 2 | $\frac{1}{1-2D}$                 | 0 <d<0.5< td=""><td><math>GV_{in}</math></td><td><math display="block">\frac{G^2}{(G-1)}I_{in}</math></td><td><math display="block">D_o = GV_{in}</math><math display="block">D_1 = GV_{in}</math></td><td><math display="block">D_o = I_o</math><math display="block">D_1 = GI_o</math></td><td><math>GV_{in}</math></td><td><math>GI_o</math></td></d<0.5<>                                                                                                                                                                                                                                                                           | $GV_{in}$                            | $\frac{G^2}{(G-1)}I_{in}$                                | $D_o = GV_{in}$ $D_1 = GV_{in}$                                                                                               | $D_o = I_o$ $D_1 = GI_o$                                                                 | $GV_{in}$                   | $GI_o$              |

| [25]     | 3                                                                                                                                                                                                                                                                                                                                                                                      | 4   | 2     | 3 | $\frac{2n}{3-4D}$                | 0.5 <d<0.7< td=""><td><math display="block">\frac{GV_{in}}{2n}</math></td><td><math display="block">\frac{(3G-2n+2)G}{(3G-2n)}I_{in}</math></td><td><math display="block">D_2 = GV_{in}</math><math display="block">D_3 = \frac{GV_{in}}{2}</math><math display="block">D_1 = \frac{GV_{in}}{2n}</math></td><td><math display="block">D_1 = GI_o</math><math display="block">D_2 = I_o</math><math display="block">D_3 = I_o</math></td><td><math display="block">\frac{GV_{in}}{2n}</math></td><td>GI<sub>o</sub></td></d<0.7<>                                                                                                        | $\frac{GV_{in}}{2n}$                 | $\frac{(3G-2n+2)G}{(3G-2n)}I_{in}$                       | $D_2 = GV_{in}$ $D_3 = \frac{GV_{in}}{2}$ $D_1 = \frac{GV_{in}}{2n}$                                                          | $D_1 = GI_o$ $D_2 = I_o$ $D_3 = I_o$                                                     | $\frac{GV_{in}}{2n}$        | GI <sub>o</sub>     |

| [27]     | 2                                                                                                                                                                                                                                                                                                                                                                                      | 5   | 2     | 5 | $\frac{3-3D}{1-3D}$              | 0 <d<0.33< td=""><td><math display="block">\frac{(G-1)\mathcal{V}_{in}}{2}</math></td><td><math display="block">\frac{4G^2 - 9G + 3}{G(G - 3)}I_{in}</math></td><td><math display="block">D_{1} = D_{2} = \frac{(G-1)V_{in}}{2}</math><math display="block">D_{3} = D_{4} = \frac{(G-1)V_{in}}{2}</math><math display="block">D_{0} = (G-1)V_{in}</math></td><td><math display="block">D_1 = (G-1)I_o</math><math display="block">D_2 = D_3 = GI_o</math><math display="block">D_4 = D_o = I_o</math></td><td><math display="block">\frac{(G-3)V_{in}}{6}</math></td><td>(G-1)I<sub>0</sub></td></d<0.33<>                              | $\frac{(G-1)\mathcal{V}_{in}}{2}$    | $\frac{4G^2 - 9G + 3}{G(G - 3)}I_{in}$                   | $D_{1} = D_{2} = \frac{(G-1)V_{in}}{2}$ $D_{3} = D_{4} = \frac{(G-1)V_{in}}{2}$ $D_{0} = (G-1)V_{in}$                         | $D_1 = (G-1)I_o$ $D_2 = D_3 = GI_o$ $D_4 = D_o = I_o$                                    | $\frac{(G-3)V_{in}}{6}$     | (G-1)I <sub>0</sub> |

| [28]     | 3                                                                                                                                                                                                                                                                                                                                                                                      | 7   | 1     | 5 | $\frac{1+2n-D}{1-2D}$            | 0 <d<0.5< td=""><td><math display="block">\frac{(2G-1)V_{in}}{1+4n}</math></td><td><math display="block">\frac{\left(2G-1\right)^2}{G\left(G-2n-1\right)}I_{in}</math></td><td><math display="block">D_{1} = \frac{(2G-1)V_{in}}{1+4n}</math><math display="block">D_{2} = D_{3} = \frac{n(2G-1)V_{in}}{1+4n}</math><math display="block">D_{4} = D_{0} = \frac{n(2G-1)V_{in}}{1+4n}</math></td><td><math display="block">D_1 = GI_o</math><math display="block">D_2 = D_3 = I_o</math><math display="block">D_4 = D_o = I_o</math></td><td><math display="block">\frac{(2G-1)V_{in}}{1+4n}</math></td><td>GI<sub>o</sub></td></d<0.5<> | $\frac{(2G-1)V_{in}}{1+4n}$          | $\frac{\left(2G-1\right)^2}{G\left(G-2n-1\right)}I_{in}$ | $D_{1} = \frac{(2G-1)V_{in}}{1+4n}$ $D_{2} = D_{3} = \frac{n(2G-1)V_{in}}{1+4n}$ $D_{4} = D_{0} = \frac{n(2G-1)V_{in}}{1+4n}$ | $D_1 = GI_o$ $D_2 = D_3 = I_o$ $D_4 = D_o = I_o$                                         | $\frac{(2G-1)V_{in}}{1+4n}$ | GI <sub>o</sub>     |

| [29]     | 2                                                                                                                                                                                                                                                                                                                                                                                      | 3   | 2     | 3 | $\frac{1}{1-4D}$                 | 0 <d<0.25< td=""><td><math>GV_{in}</math></td><td><math display="block">\frac{4G}{(G-1)}I_{in}</math></td><td><math display="block">D_o = GV_{in}</math><math display="block">D_1 = D_2 = GV_{in}</math></td><td><math display="block">D_1 = GI_O</math><math display="block">D_2 = I_O</math><math display="block">D_3 = I_O</math></td><td><math>{GV}_{\it in}</math></td><td>GI<sub>o</sub></td></d<0.25<>                                                                                                                                                                                                                           | $GV_{in}$                            | $\frac{4G}{(G-1)}I_{in}$                                 | $D_o = GV_{in}$ $D_1 = D_2 = GV_{in}$                                                                                         | $D_1 = GI_O$ $D_2 = I_O$ $D_3 = I_O$                                                     | ${GV}_{\it in}$             | GI <sub>o</sub>     |

| [30]     | 4                                                                                                                                                                                                                                                                                                                                                                                      | 7   | 2     | 5 | $\frac{3+2D}{1-2D}$              | 0 <d<0.5< td=""><td><math display="block">\frac{(G+1)V_{in}}{4}</math></td><td><math display="block">\frac{(G-1)(1+G)}{G(G-3)}I_{in}</math></td><td><math display="block">D_{1} = D_{2} = \frac{(G+1)V_{in}}{4}</math><math display="block">D_{3} = \frac{(G+1)V_{in}}{2}</math><math display="block">D_{4} = D_{0} = \frac{(G+1)V_{in}}{2}</math></td><td><math display="block">D_2 = GI_O</math><math display="block">D_4 = D_3 = I_O</math></td><td><math display="block">\frac{(G+1)V_{in}}{4}</math></td><td><math>\frac{GI_o}{2}</math></td></d<0.5<>                                                                             | $\frac{(G+1)V_{in}}{4}$              | $\frac{(G-1)(1+G)}{G(G-3)}I_{in}$                        | $D_{1} = D_{2} = \frac{(G+1)V_{in}}{4}$ $D_{3} = \frac{(G+1)V_{in}}{2}$ $D_{4} = D_{0} = \frac{(G+1)V_{in}}{2}$               | $D_2 = GI_O$ $D_4 = D_3 = I_O$                                                           | $\frac{(G+1)V_{in}}{4}$     | $\frac{GI_o}{2}$    |

| [31]     | 4                                                                                                                                                                                                                                                                                                                                                                                      | 6   | 2     | 4 | $\frac{2}{1-2D}$                 | 0 <d<0.5< td=""><td><math>\frac{GV_{in}}{2}</math></td><td><math display="block">\frac{2G}{(G-2)}I_{in}</math></td><td><math display="block">D_1 = D_3 = GV_{in}</math><math display="block">D_2 = D_4 = \frac{GV_{in}}{2}</math></td><td><math display="block">D_1 = D_2 = \frac{GI_o}{2}</math><math display="block">D_4 = D_3 = I_o</math></td><td><math>\frac{GV_{in}}{2}</math></td><td><math>\frac{GI_o}{2}</math></td></d<0.5<>                                                                                                                                                                                                  | $\frac{GV_{in}}{2}$                  | $\frac{2G}{(G-2)}I_{in}$                                 | $D_1 = D_3 = GV_{in}$ $D_2 = D_4 = \frac{GV_{in}}{2}$                                                                         | $D_1 = D_2 = \frac{GI_o}{2}$ $D_4 = D_3 = I_o$                                           | $\frac{GV_{in}}{2}$         | $\frac{GI_o}{2}$    |

| [32]     | 2                                                                                                                                                                                                                                                                                                                                                                                      | 5   | 1     | 4 | $\frac{2+n}{1-2D}$               | 0 <d<0.5< td=""><td><math display="block">\frac{GV_{in}}{2+n}</math></td><td><math display="block">\frac{(4+2n)G-2n^2-6n-4}{(G-n-2)(2+n)}I_{in}</math></td><td><math display="block">D_1 = D_o = \frac{GV_{in}}{n+2}</math><math display="block">D_3 = D_4 = \frac{(n+1)GV_{in}}{n+2}</math></td><td><math>D_{i} = D_{i} = I_{i}</math></td><td><math display="block">\frac{GV_{in}}{n+2}</math></td><td><math>GI_o</math></td></d<0.5<>                                                                                                                                                                                                | $\frac{GV_{in}}{2+n}$                | $\frac{(4+2n)G-2n^2-6n-4}{(G-n-2)(2+n)}I_{in}$           | $D_1 = D_o = \frac{GV_{in}}{n+2}$ $D_3 = D_4 = \frac{(n+1)GV_{in}}{n+2}$                                                      | $D_{i} = D_{i} = I_{i}$                                                                  | $\frac{GV_{in}}{n+2}$       | $GI_o$              |

| [33]     | 3                                                                                                                                                                                                                                                                                                                                                                                      | 4   | 1     | 5 | $\frac{M+1}{\left(1-D\right)^2}$ | 0 <d<1< td=""><td><math display="block">\frac{GV_{in}}{M+1}</math></td><td>D(2-D) lin</td><td><math display="block">D_{M1} = D_{M2} = D_0 = \frac{GV_{in}}{M+1}</math><math display="block">D_1 = D_2 = \frac{DGV_{in}}{M+1}</math></td><td><math display="block">D_2 = (1 - D)GI_0</math><math display="block">D_0 = I_0</math></td><td>M + 1</td><td><math>GI_o</math></td></d<1<>                                                                                                                                                                                                                                                    | $\frac{GV_{in}}{M+1}$                | D(2-D) lin                                               | $D_{M1} = D_{M2} = D_0 = \frac{GV_{in}}{M+1}$ $D_1 = D_2 = \frac{DGV_{in}}{M+1}$                                              | $D_2 = (1 - D)GI_0$ $D_0 = I_0$                                                          | M + 1                       | $GI_o$              |

| [34]     | 2                                                                                                                                                                                                                                                                                                                                                                                      | 3   | 2     | 3 | $\frac{1+D}{\left(1-D\right)^2}$ | 0 <d<1< td=""><td><math display="block">\frac{(1-D)GV_{in}}{1+D}</math><math display="block">GV_{in}</math></td><td><math>\frac{G}{1-D}</math>lin</td><td><math display="block">D_{1} = D_{2} = \frac{(1-D)GV_{in}}{1+D}</math><math display="block">D_{O} = \frac{(1+D)GV_{in}}{2}</math></td><td><math display="block">D_{1} = \frac{(1-D)}{(1+D)}GI_{o}</math><math display="block">D_{2} = \frac{(1-D)}{D(1+D)}GI_{o}</math><math display="block">D_{O} = I_{O}</math></td><td><math display="block">\frac{(1-D)GV_{in}}{1+D}</math></td><td><math>GI_o</math></td></d<1<>                                                          | $\frac{(1-D)GV_{in}}{1+D}$ $GV_{in}$ | $\frac{G}{1-D}$ lin                                      | $D_{1} = D_{2} = \frac{(1-D)GV_{in}}{1+D}$ $D_{O} = \frac{(1+D)GV_{in}}{2}$                                                   | $D_{1} = \frac{(1-D)}{(1+D)}GI_{o}$ $D_{2} = \frac{(1-D)}{D(1+D)}GI_{o}$ $D_{O} = I_{O}$ | $\frac{(1-D)GV_{in}}{1+D}$  | $GI_o$              |

| proposed | 2                                                                                                                                                                                                                                                                                                                                                                                      | 5   | 2     | 5 | $\frac{3+n-D}{1-3D+D^2}$         | 0 <d<0.38< td=""><td>Eqs (20)-(21)</td><td>Eq (22)</td><td>Eq (23)-(26)</td><td><math display="block">D_1 = GI_o</math><math display="block">D_2 = I_{s2}</math><math display="block">D_4 = D_3 = I_o</math><math display="block">D_o = I_o</math></td><td><math display="block">V_{C1} = V_{D2}</math></td><td>GI<sub>o</sub></td></d<0.38<>                                                                                                                                                                                                                                                                                           | Eqs (20)-(21)                        | Eq (22)                                                  | Eq (23)-(26)                                                                                                                  | $D_1 = GI_o$ $D_2 = I_{s2}$ $D_4 = D_3 = I_o$ $D_o = I_o$                                | $V_{C1} = V_{D2}$           | GI <sub>o</sub>     |

|          | S: switch, D: Diode, C: Capacitor, M: Magnetic core, Cm Gnd: Common Ground.<br>$I_{S1} = \frac{2G(2G^2 + 3nG^2 - nG - G\sqrt{5G^2 + (6+4n)G+1})I_o}{(3G + 2nG + 1\sqrt{5G^2(6+4n)G+1})(3G - 1 - \sqrt{5G^2(6+4n)G+1})}, I_{S2} = \frac{G(2G^2 - 2nG^2 - 2nG - 28G - 1 + (2G + 2nG + 2)\sqrt{5G^2 + (6+4n)G+1})I_o}{(3G + 2nG + 1\sqrt{5G^2(6+4n)G+1})(3G - 1 - \sqrt{5G^2(6+4n)G+1})}$ |     |       |   |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |                                                          |                                                                                                                               |                                                                                          |                             |                     |

| D = -    | $D = \frac{2G - \sqrt{4G^2 - 4G(G - M - 1)}}{2G}  for[33], \ D = \frac{2G + 1 - \sqrt{8G + 1}}{2G}  for[34]$                                                                                                                                                                                                                                                                           |     |       |   |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |                                                          |                                                                                                                               |                                                                                          |                             |                     |

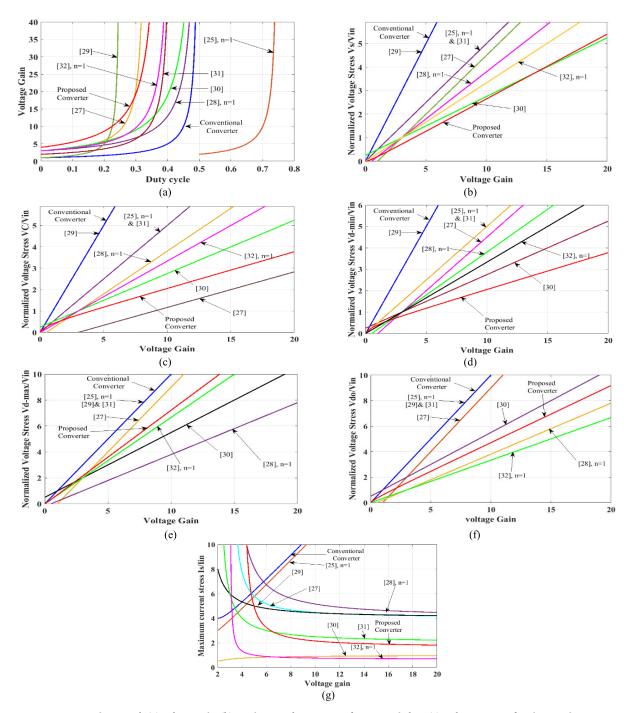

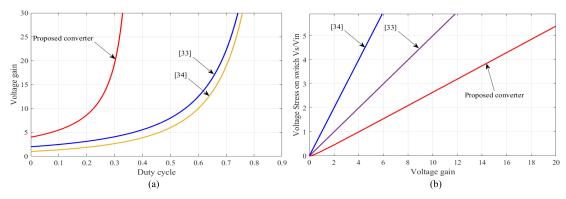

FIGURE 8. Comparison result (a) Voltage gain, (b) Maximum voltage stress of power switches, (c), Voltage stress of main capacitor, (d) Minimum voltage stress of diodes, (e) Maximum voltage stress of diodes, (f) Voltage stress of output diode, (g) Maximum current stress of switches.

the presented converter in [28] have a single power switch, the number of its magnetic cores is higher than the proposed converter. In compare to converters in [33] (considering M = 1) and [34], the proposed converter not only can achieve high voltage gain but also the voltage stresses on semiconductors are lower. Also, the number of inductors in reference [33] are larger than the presented converter which causes higher losses and lower efficiency. From table 4, the output power and efficiency of the presented converter is higher than the converters in [33] and [34].

Considering Table 3, the equations (20)-(26) can be expressed as follows:

$$V_{S1} = \frac{\left(G - G^2 + G\sqrt{5G^2(6+4n)G+1}\right)V_{in}}{\left(3G + 2nG + 1 + \sqrt{5G^2(6+4n)G+1}\right)}$$

(20)

| Ref      | Frequency (Hz) | Input voltage (V) | Output voltage (V) | Output power (W) | Efficiency (%) | Common ground |  |

|----------|----------------|-------------------|--------------------|------------------|----------------|---------------|--|

| [21]     | 50             | 24                | 120                | 40               | 94.5           | Yes           |  |

| [25]     | 10             | 60                | 400                | 800              | 87             | No            |  |

| [27]     | 100            | 40                | 240                | 140              | 98             | No            |  |

| [28]     | 50             | 24                | 300                | 100              | 89             | No            |  |

| [29]     | 25             | 45                | 225                | 185              | 92.4           | No            |  |

| [30]     | 100            | 20                | 300                | 200              | 78             | No            |  |

| [31]     | 50             | 40                | 400                | 200              | 92.3           | No            |  |

| [32]     | 50             | 60                | 650                | 500              | 96.1           | Yes           |  |

| [33]     | 50             | 12                | 96                 | 40               | 88             | Yes           |  |

| [34]     | 50             | 12                | 69                 | 150              | 92             | Yes           |  |

| proposed | 40             | 48                | 410                | 250              | 93.8           | Yes           |  |

TABLE 4. Efficiency Comparison of proposed converter with otherZ-source based converters.

FIGURE 9. Comparison results of proposed converter with quadratic converters, a) Voltage gain, b) Maximum voltage stress on power switch.

| TABLE 5. Spec | ifications o | f devices | for experiment. |

|---------------|--------------|-----------|-----------------|

|---------------|--------------|-----------|-----------------|

| Components                              | Specifications                                  |

|-----------------------------------------|-------------------------------------------------|

| Output Power                            | 250 W                                           |

| Input-output voltage                    | 48V                                             |

| Output voltage                          | 410 V                                           |

| Switching frequency                     | 40 kHz                                          |

| Capacitors C1&C2                        | 220 µF                                          |

| Capacitors C3&Co                        | 100µF                                           |

| Capacitor C4                            | 68µF                                            |

| Input inductor                          | <i>Lin</i> =550 μH                              |

| Coupled inductor                        | <i>Lm</i> =250 µH & <i>L</i> <sub>lk</sub> =3µH |

| Coupled inductor                        | Turns ratio N1:N2=1:1                           |

| Power MOSFETS                           | IRFP4668PbF                                     |

| Power diode for $D_1$ ,                 | DSEI60-06A                                      |

| Power diode for $D_2$                   | SFAF2004G                                       |

| Power diode for $D_4$ , $D_3$ , & $D_0$ | SFAF1606G                                       |

$$V_{S2} = \frac{2G^2 V_{in}}{\left(3G + 2nG + 1 + \sqrt{5G^2 (6 + 4n) G + 1}\right)}$$

(21)

$$\frac{\left(2G+3nG-n-\sqrt{5G^2(6+4n)G+1}\right)I_{in}}{\left(3G+2nG+1+\sqrt{5G^2(6+4n)G+1}\right)D}$$

(22)

$$D_{1} = \frac{2G^{2}V^{in}}{(23)}$$

$$D_{2} = \frac{\left(G - G^{2} + G\sqrt{5G^{2} + (6 + 4n)G + 1}\right)}{3G + 2nG + 1 + \sqrt{5G^{2} + (6 + 4n)G + 1}} \qquad (24)$$

$$D_{3} = \frac{\left(G + 2nG^{2} + G\sqrt{5G^{2} + (6 + 4n)G + 1}\right)V_{in}}{3G + 2nG + 1 + \sqrt{5G^{2}(6 + 4n)G + 1}} \quad (25)$$

$$D_{O} = \frac{\left(G^{2} + G + G\sqrt{5G^{2} + (6 + 4n)G + 1}\right)V_{in}}{3G + 2nG + 1 + \sqrt{5G^{2}(6 + 4n)G + 1}} \quad (26)$$

Comparison of the voltage gain of the proposed converter with other topologies is illustrated in Fig. 8(a). Regarding to Fig. 8(a), it can be seen that the proposed converter has the highest voltage gain in lower range of duty cycle compared with other converters. Also, the maximum voltage stress across the power switches of the converters is shown in Fig. 8(b). Considering this figure, under the same input voltage for all converters, the slop of the voltage stress curve for the proposed converter is less than the other topologies. Therefore, the maximum voltage stress of the power switches for proposed converter is lower than the others.

Although, at the voltage gain of greater than 15, the maximum voltage stress across the power switches of the proposed converter is higher than the presented structure in [26], this converter not only isn't common grounded, but also the number of its elements is more than the proposed converter that may result in high conduction losses and cost. The comparison of the voltage stress of main capacitor of the proposed converter with other topologies is illustrated in Fig. 8(c). Regarding to this figure, it can be understood that compared to other structures, except the converter presented

in [27] for high voltage gain range, the voltage stress of the main capacitor of the proposed structure has the lowest value.

The comparison of the minimum voltage stress across the diodes for all suggested converters is shown in Fig. 8(d). The voltage stress of the output diode for the converter in [29], and the conventional converter is equal to the output voltage and higher than the others. Based on Fig. 8(d), the minimum voltage stress across the output diode of the proposed converter is the lowest value compared with other converters.

Fig. 8(e) illustrates the comparison of the maximum voltage stress of the diodes in terms of the voltage gain with other converters. Considering Fig. 8(e), the maximum voltage stress of the diodes for the converters in [25], [29], and [31], and the conventional converter is equal to the output voltage and higher than the others. As well, the voltage stress across the output diode in [27] is higher than the proposed converter.

Fig. 8(f) shows the comparison of the normalized voltage stress of the output diode in terms of the voltage gain for the proposed converter with other topologies. Regarding to this figure, it can be seen that the normalized voltage stress for the converters in [25], [29], and [31] are the same and higher than the others. Also, compared with topologies in [25], [27], [29], [30], and [31], the proposed converter has the lower value of normalized voltage stress.

The comparison of maximum current stress of the switches for the proposed converter with other structures is indicated in Fig. 8(g). Considering this figure, it can be seen that compared other topologies, expect [30], and [32], the proposed converter has the lowest value of maximum current stress of the switches. In general, the voltage gain of proposed converter is higher than the abovementioned converters and its switches and output diode voltage stresses are lower.

Comparison of the voltage gain of the proposed converter with topologies [33], and [34] is illustrated in Fig. 9(a). Considering this figure, the proposed converter has the largest gain voltage between topologies [33] and [34]. Also, the maximum voltage stress across the power switches of the proposed converter, [33], [34] is shown in Fig. 9(b). Considering this figure, under the same input voltage for all converters, the slop of the voltage stress curve for the proposed converter is less than the topologies [33] and [34]. Therefore, the maximum voltage stress of the power switches for proposed converter is lower than the converters of [33] and [34].

In addition, the efficiency, frequency, output voltage, input voltage, power and common grounding features of the proposed converter and the other competitors are gathered in Table 4. As can be seen, the efficiency of the proposed converter is higher than the most recent converters. Although the efficiency in the converters of [27] and [32] is better than the proposed converter, the output voltage and power of the converter in [27] are less than the proposed converter. Also, the input voltage and output voltage in converter of [32] is higher than the proposed converter which causes lower passing current through the elements. Therefore, in the same condition for both converters, they may have same efficiency. Based on Table 4, in the proposed converter, topologies of

**FIGURE 10.** The photograph of experimental prototype of proposed converter.

[21] and [32], the neutral point of output is connected to the input DC source directly. So, the proposed converter, [21] and [32] can provide common grounded feature. However, other compared topologies cannot provide common grounded feature.

# **VII. EXPERIMENTAL RESULTS**

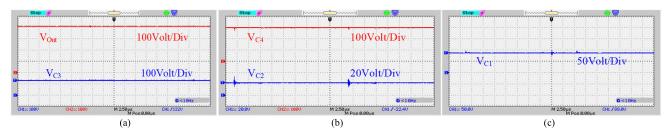

Based on the theoretical analysis, the experimental prototype of 250 W has been tested in the laboratory to validate the performance of the proposed converter which is demonstrated in Fig. 10. As well, the utilized devices specifications for the proposed converter are tabulated in Table 4. According to the voltage gain relationship, the duty cycle is set in 0.21 under the approximated 40 kHz switching frequency and the input voltage is 48 V. The output voltage and the voltage of all capacitors are shown in Fig. 11. As it can be seen from Fig. 11(a), the output voltage is approximately 410 V and the voltage of capacitor  $C_3$  is about 133V. From theoretical analysis, the voltage gain value of the presented converter is about 9.15 and the experimental voltage gain value is about 8.54. Based on Fig. 11(a), it can be seen that the experimental value is near to theoretical value and they verify each other. Fig. 11(b), shows the voltage of capacitors  $C_2$  and  $C_4$  which are 22 V and 300 V approximately. The voltage of capacitor  $C_1$  is shown in Fig. 11(c), which is about 88 V. All these capacitors voltage values comply the theoretical equations.

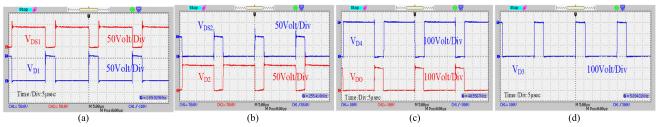

Fig. 12, shows the experimental waveforms of the voltage stress of the switches and diodes. It can be seen from Fig. 12(a), the voltage of drain-source for the  $S_1$  switch ( $V_{S1}$ ) is about 88 V and the voltage stress of diode  $D_1$  is about 110 V. Also, from Fig. 12(b), the voltage of drain-source for the  $S_2$  switch ( $V_{S2}$ ) and voltage stress of diode  $D_2$  are about 110 V and 88 V, respectively. In addition, the voltage stress across the diodes  $D_4$  and  $D_0$  are shown in Fig. 12(c), which are about 300 V and 200 V, respectively. It can be observed that the output diode voltage is half of the output voltage. Fig. 12(d), shows the voltage waveform of diode  $D_3$  and it is about 300 V. All these experimental values are near to theoretical equations and affirm the performance of the suggested converter.

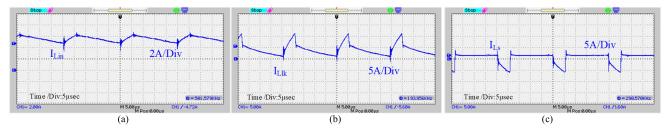

The experimental current waveforms of the input inductor  $L_{in}$  and the coupled inductor are shown in Fig. 13. It is noted from Fig. 13(a), when switches are ON, the input inductor current is raised linearly and when switches are OFF, the input inductor current is decreased linearly. The maximum amount of input inductor current is about 6.4 A and the minimum is

FIGURE 11. The voltage waveforms of output and capacitors (a) Output voltage and voltage of capacitor C3, (b) Voltage of capacitor C2 and C4, (c) Voltage of capacitor C1.

FIGURE 12. The voltage stress waveforms of semiconductors (a) Power switch  $S_1$  and diode  $D_1$ , (b) Power switch  $S_2$  and diode  $D_2$ , (c) Diodes  $D_4$  and  $D_0$ , (d) Diode  $D_3$ .

FIGURE 13. The current waveforms of inductors (a) Current of inductor  $L_{in}$ , (b) Current of primary side of coupled inductor  $L_{lk}$ , (c) Current of secondary side of coupled inductor  $L_s$ .

FIGURE 14. Experimental results: (a) the output voltage waveform with change in input voltage in open loop control system. Output voltage control of the proposed structure: (b) Changing input voltage, and (c) Changing the output load.

about 4.72 A. Also, the average value of this current is about 5.56 A. The experimental current waveforms of the primary and secondary side of the coupled inductor are observed in Fig. 13(b) and 13(c), respectively. As it can be seen, these currents change linearly and when the switches are ON the slope of the primary side current is positive and the current of the secondary side is negative.

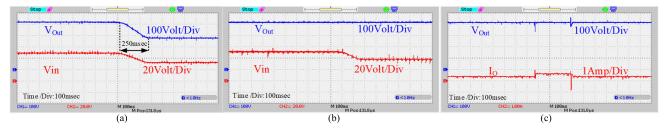

In Fig. 14(a), the dynamic response of the open-loop system of the second proposed structure is evaluated. In this figure, initially when the input voltage is 48 V, the output voltage is 408 V and the output power is 250 W. After a short time interval, the input voltage suddenly drops to 32 V and the output voltage drops to 280 V after 250 mSec. and

remains constant. Therefore, the time of transient changes in this converter is about 250 mSec., after which the voltage is stabilized and the voltage gain follows the theoretical values and the output power reaches 60 W.

Finally, the results of the control system of the closed-loop system of the proposed structure are evaluated in Fig. 14 (b) and (c). As can be seen in Fig. 14(b), by changing the input voltage from 48 V to 32V, the output voltage is constant and it is not changed. During this period, the output voltage of the converter is fixed at 408 V. As can be seen in Fig. 14 (c), by changing the output load, the load current first increases and reaches to the full load (0.6 A) value, and then decreases to the half load value (0.3 A). During this period,

when the load has changed, the output voltage of the converter is fixed at 408 V.

# **VIII. CONCLUSION**

In this paper, a high gain switched quasi Z-source DC-DC converter with a coupled inductor and a switched capacitor cell is proposed which has added one extra diode and one power switch to the quasi Z-source network. In addition, this converter can reach the following characteristics: high voltage gain with small duty cycle, continuous input current, low voltage stress across the power switches, low voltage stress on the output diode and common ground between the load and input energy source. The presented converter has been compared with other Z-source based converter comprehensively and experimental results of 250 W prototype prove the above-mentioned characteristics. Also, the control strategy and stability of the proposed converter are evaluated. Eventually, the calculated and measured efficiency have been provided. As consequence, the measured efficiency is near to the calculated amount and the full load efficiency is 93.86%.

#### REFERENCES

- M. G. Marangalu, N. V. Kurdkandi, P. Alavi, S. Khadem, H. Tarzamni, and A. Mehrizi-Sani, "A new single DC source five-level boost inverter applicable to grid-tied systems," *IEEE Access*, vol. 11, pp. 24112–24127, 2023, doi: 10.1109/ACCESS.2023.3253806.

- [2] N. V. Kurdkandi, M. G. Marangalu, S. Mohammadsalehian, H. Tarzamni, Y. P. Siwakoti, M. R. Islam, and K. M. Muttaqi, "A new six-level transformer-less grid-connected solar photovoltaic inverter with less leakage current," *IEEE Access*, vol. 10, pp. 63736–63753, 2022, doi: 10.1109/ACCESS.2022.3182240.

- [3] H. Tarzamni, H. S. Gohari, M. Sabahi, and J. Kyyrä, "Non-isolated high step-up DC–DC converters: Comparative review and metrics applicability," *IEEE Trans. Power Electron.*, early access, Apr. 3, 2023, doi: 10.1109/TPEL.2023.3264172.

- [4] M. G. Marangalu, S. Rahimpour, N. V. Kurdkandi, A. Mehrizi-Sani, M. Najafzadeh, and S. H. Hosseini, "A single-stage transformer-less fivelevel grid-tied inverter with boosting capability," in *Proc. 13th PEDSTC*, Feb. 2022, pp. 651–655.

- [5] R. Rahimi, S. Habibi, M. Ferdowsi, and P. Shamsi, "Z-source-based high step-up DC–DC converters for photovoltaic applications," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 10, no. 4, pp. 4783–4796, Aug. 2022, doi: 10.1109/JESTPE.2021.3131996.

- [6] Y. Azadeh, E. Babaei, H. Tarzamni, and M. Sabahi, "Single-inductor dualoutput DC–DC converter with capability of feeding a constant power load in open-loop manner," *IEEE Trans. Ind. Electron.*, vol. 66, no. 9, pp. 6906–6915, Sep. 2019.

- [7] M. Sabahi, H. Tarzamni, and P. Kolahian, "Operation and design analysis of an interleaved high step-up DC–DC converter with improved harnessing of magnetic energy," *Int. J. Circuit Theory Appl.*, vol. 49, no. 2, pp. 221–243, Feb. 2021.

- [8] M. R. Islam, Y. Guo, and J. Zhu, "A high-frequency link multilevel cascaded medium-voltage converter for direct grid integration of renewable energy systems," *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 4167–4182, Aug. 2014.

- [9] A. Nafari and R. Beiranvand, "An extendable interleaved quasi Z-source high step-up DC–DC converter," *IEEE Trans. Power Electron.*, vol. 38, no. 4, pp. 5065–5076, Apr. 2023, doi: 10.1109/TPEL.2023.3235832.

- [10] A. Samadian, M. G. Marangalu, S. H. Hosseini, M. Sabahi, Md. R. Islam, and R. Shah, "High step-up common grounded switched quasi Z-source DC–DC converter using coupled inductor," in *Proc. IEEE 1st Ind. Electron. Soc. Annu. On-Line Conf. (ONCON)*, Kharagpur, India, Dec. 2022, pp. 1–7, doi: 10.1109/ONCON56984.2022.10126773.

- [11] H. S. Gohari, N. A. Mardakheh, H. Tarzamni, N. V. Kurdkandi, K. Abbaszadeh, and J. Kyyra, "Non-isolated ultra-high voltage gain coupled inductor-based DC–DC converter," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, early access, Jun. 12, 2023, doi: 10.1109/TCSII.2023.3285169.

- [12] H. Tarzamni, N. V. Kurdkandi, H. S. Gohari, M. Lehtonen, O. Husev, and F. Blaabjerg, "Ultra-high step-up DC–DC converters based on center-tapped inductors," *IEEE Access*, vol. 9, pp. 136373–136383, 2021.

- [13] X. Ding, M. Zhou, Y. Cao, B. Li, Y. Sun, and X. Hu, "A high step-up coupled-inductor-integrated DC–DC multilevel boost converter with continuous input current," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 10, no. 6, pp. 7346–7360, Dec. 2022, doi: 10.1109/JESTPE.2022.3184699.

- [14] J.-H. Lee, T.-J. Liang, and J.-F. Chen, "Isolated coupled-inductorintegrated DC–DC converter with nondissipative snubber for solar energy applications," *IEEE Trans. Ind. Electron.*, vol. 61, no. 7, pp. 3337–3348, Jul. 2014.

- [15] M. Maalandish, S. H. Hosseini, S. Pourjafar, S. Nouri, S. M. Hashemzadeh, and M. G. Marangalu, "A non-isolated high step-up DC–DC converter recommended for photovoltaic systems," in *Proc. 12th PEDSTC*, Feb. 2021, pp. 1–5.

- [16] G. R. Walker and P. C. Sernia, "Cascaded DC–DC converter connection of photovoltaic modules," *IEEE Trans. Power Electron.*, vol. 19, no. 4, pp. 1130–1139, Jul. 2004.

- [17] Y. Tang, D. Fu, T. Wang, and Z. Xu, "Hybrid switched-inductor converters for high step-up conversion," *IEEE Trans. Ind. Electron.*, vol. 62, no. 3, pp. 1480–1490, Mar. 2015.

- [18] A. Ajami, H. Ardi, and A. Farakhor, "A novel high step-up DC/DC converter based on integrating coupled inductor and switchedcapacitor techniques for renewable energy applications," *IEEE Trans. Power Electron.*, vol. 30, no. 8, pp. 4255–4263, Aug. 2015, doi: 10.1109/TPEL.2014.2360495.

- [19] X. P. Fang, Z. M. Qian, and F. Z. Peng, "Single-phase Z-source PWM AC-AC converters," *IEEE Power Electron Lett.*, vol. 3, no. 4, pp. 121–124, Dec. 2005.

- [20] V. P. Galigekere and M. K. Kazimierczuk, "Analysis of PWM Z-source DC–DC converter in CCM for steady state," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 4, pp. 854–863, Apr. 2012.

- [21] D. Cao and F. Z. Peng, "A family of Z-source and quasi-Z-source DC–DC converters," in *Proc. 24th Annu. IEEE APEC*, Feb. 2009, pp. 1097–1101.

- [22] D. Vinnikov and I. Roasto, "Quasi-Z-source-based isolated DC/DC converters for distributed power generation," *IEEE Trans. Ind. Electron.*, vol. 58, no. 1, pp. 192–201, Jan. 2011.

- [23] Y. P. Siwakoti, F. Blaabjerg, P. C. Loh, and G. E. Town, "High-voltage boost quasi-Z-source isolated DC/DC converter," *IET Power Electron.*, vol. 7, no. 9, pp. 2387–2395, Sep. 2014.

- [24] D. Vinnikov, I. Roasto, R. Strzelecki, and M. Adamowicz, "Step-up DC/DC converters with cascaded quasi-Z-source network," *IEEE Trans. Ind. Electron.*, vol. 59, no. 10, pp. 3727–3736, Oct. 2012.

- [25] Y. Zhang, J. Shi, L. Zhou, J. Li, M. Sumner, P. Wang, and C. Xia, "Wide input-voltage range boost three-level DC–DC converter with quasi-Z source for fuel cell vehicles," *IEEE Trans. Power Electron.*, vol. 32, no. 9, pp. 6728–6738, Sep. 2017.

- [26] Y. Wang, Q. Bian, X. Hu, Y. Guan, and D. Xu, "A high-performance impedance-source converter with switched inductor," *IEEE Trans. Power Electron.*, vol. 34, no. 4, pp. 3384–3396, Apr. 2019.

- [27] F. A. A. Meinagh, J. Yuan, and Y. Yang, "Analysis and design of a high voltage-gain quasi-Z-source DC–DC converter," *IET Power Electron.*, vol. 13, no. 9, pp. 1837–1847, 2020.

- [28] A. Torkan and M. Ehsani, "A novel nonisolated Z-source DC–DC converter for photovoltaic applications," *IEEE Trans. Ind. Appl.*, vol. 54, no. 5, pp. 4574–4583, Sep. 2018.

- [29] J. Liu, J. Wu, J. Qiu, and J. Zeng, "Switched Z-source/quasi-Z-source DC-DC converters with reduced passive components for photovoltaic systems," *IEEE Access*, vol. 7, pp. 40893–40903, 2019.

- [30] J. M. de Andrade, R. Francisco Coelho, and T. B. Lazzarin, "New high step-up DC–DC converter with quasi-Z-source network and switchedcapacitor cell," in *Proc. IEEE APEC*, Mar. 2020, pp. 2062–2066.

- [31] Y. Huangfu, R. Ma, B. Zhao, Z. Liang, Y. Ma, A. Wang, D. Zhao, H. Li, and R. Ma, "A novel robust smooth control of input parallel output series quasi-Z-source DC–DC converter for fuel cell electrical vehicle applications," *IEEE Trans. Ind. Appl.*, vol. 57, no. 4, pp. 4207–4221, Jul. 2021, doi: 10.1109/TIA.2021.3073643.

- [32] A. Samadian, S. H. Hosseini, M. Sabahi, and M. Maalandish, "A new coupled inductor nonisolated high step-up quasi Z-source DC–DC converter," *IEEE Trans. Ind. Electron.*, vol. 67, no. 7, pp. 5389–5397, Jul. 2020.

- [33] J. D. Navamani, K. Vijayakumar, and R. Jegatheesan, "Non-isolated high gain DC–DC converter by quadratic boost converter and voltage multiplier cell," *Ain Shams Eng. J.*, vol. 9, no. 4, pp. 1397–1406, Dec. 2018, doi: 10.1016/j.asej.2016.09.007.