Received 27 August 2023, accepted 11 September 2023, date of publication 15 September 2023, date of current version 29 September 2023.

Digital Object Identifier 10.1109/ACCESS.2023.3316015

# **RESEARCH ARTICLE**

# **Power-Imbalance Stimulation and Internal-**Voltage Response Relationships Based **Modeling Method of PE-Interfaced Devices** in DC Voltage Control Timescale

# JIN HUANG<sup>(D)</sup>, XIAOMING YUAN<sup>(D)</sup>, (Senior Member, IEEE), AND SICHENG WANG<sup>(D)</sup> School of Electrical and Electronic Engineering, Huazhong University of Science and Technology, Wuhan 430074, China

Corresponding author: Xiaoming Yuan (yuanxm@hust.edu.cn)

This work was supported by the Science and Technology Project of State Grid, Huazhong University of Science and Technology (HUST)-State Grid Future of Grid Institute under Grant 5100-202199548A-0-5-ZN.

**ABSTRACT** In power systems with high penetration of renewable energy, dynamic issues associated with multi-device interaction involving DC voltage control (DVC) and AC current control (ACC) of power electronic (PE)-interfaced devices are constantly emerging. The device participates in the interaction dynamics based on the way that DVC adjusts the current reference of ACC to regulate the internal voltage amplitude/frequency under the active/reactive power imbalance. Thus, to analyze the effect mechanism of the device on system dynamics, the device should be characterized as internal voltage in response to power imbalance stimulation. However, the existing modeling works fail to recognize the process of the device participating in system dynamics, so the regulation mechanism of the internal voltage by the device under power imbalance for the system dynamics analysis remains unclear. Therefore, this paper proposes a modeling method of the PE-interfaced device based on the recognition of the regulation process of the internal voltage amplitude/frequency by the device under the active/reactive power imbalance. The model based on power-imbalance stimulation and internal-voltage response relationships is first established to characterize the regulation by detailed controls. Since the stimulation-response relationships are dominated by DVC, to directly describe the regulation by DVC, the model with ideal ACC is further proposed through the infinity gain equivalence of ACC. Based on the model, the characteristics of the device in DVC timescale and the impact mechanism of the device on system dynamics by regulating the internal voltage amplitude/frequency are revealed. Simulation results for verification are also included.

**INDEX TERMS** Characteristic, DC voltage control (DVC) timescale, modeling, participation mechanism, power electronic (PE)-interfaced devices, stimulation-response relationship, system dynamics.

## **I. INTRODUCTION**

With the rapid development of renewable energy generation and the weakening of power grid, more and more fast dynamic issues (around 100ms) associated with power electronic (PE)-interfaced devices are emerging in power systems [1], [2], [3], [4], [5]. For the analysis of system dynamics, it remains unclear what controls of the PE-interfaced device are involved in these dynamic issues

The associate editor coordinating the review of this manuscript and approving it for publication was Guangya Yang<sup>D</sup>.

and how the device affects system dynamics, which poses a challenge to the ambitious targets of a larger percentage of renewables. Models that illustrate the mechanism of the PE-interfaced device participating in and affecting system dynamics are urgently needed.

Under a power disturbance to the grid, the AC current control (ACC) of the PE-interfaced device regulates the internal voltage to adjust the current. In this process, the output power of the DC capacitor changes, and there may be a continuous power imbalance in the DC capacitor, which causes the DC voltage control (DVC) to participate in the system dynamics.

References [6] and [7] observed the dynamic phenomenon caused by the action of DVC in a very weak grid case. The action of DVC affects the power imbalances of the device itself and other devices in the system [8], [9]. Thus, the system dynamics are associated with the multi-device interaction involving not only ACC but also DVC of PE-interfaced devices.

In this interaction process, the system focuses on the active and reactive powers as well as the voltage amplitude and frequency [10], [11], [12]. To maintain the power balance and a certain voltage amplitude and frequency level, PE-interfaced devices form and adjust the internal voltage amplitude/frequency according to the active/reactive power imbalance [9], [12]. Specifically, the main DVC modifies the active/reactive current reference, and the auxiliary ACC regulates the amplitude/frequency of the internal voltage according to the current reference. The grid then changes the active/reactive power corresponding to the internal voltage amplitude/frequency [8]. In the above process, the basic way of the device participating in the system dynamics is to regulate the internal voltage under power imbalance. Therefore, the model of the PE-interfaced devices should be characterized as the relationships between the active/reactive power imbalance and the internal voltage amplitude/frequency to reflect the role of the device in the system dynamics.

Concerning the power system dynamics study, models of the PE-interfaced device for simulation were first released by device manufacturers and relevant working groups [13], [14], [15], [16], [17]. These simulation models based on detailed connections of hardware and controls are good at reflecting the accurate responses of the device but do not focus on the mechanism analysis of dynamic issues. To address this, analytical models have been developed in various forms. References [18], [19], and [20] established state-space models of the PE-interfaced device to mathematically describe the device with a set of differential-algebraic equations. In [21], the model with power as stimulation and current as response was developed in the frequency domain to analyze the influence of the device on system stability. References [22], [23], [24], [25], and [26] obtained models of the PE-interfaced device by borrowing the concept of impedance in DC systems, which describes the impedance characteristics of the device. However, these models do not focus on the process of the PE-interfaced device participating in the system dynamics, so the regulation mechanism of the internal voltage by the device under power imbalance for the system dynamics analysis remains unclear.

Several modeling works [27], [28] have focused on the way of the PE-interfaced device participating in system dynamics and developed models of the device considering ACC. However, these models do not consider the involvement of DVC in system dynamics under continuous power disturbance, which makes the models unsuitable for analyzing dynamic issues associated with DVC. In summary, most device modeling works do not focus on the way in which the PE-interfaced device participates in the system dynamics, and a few

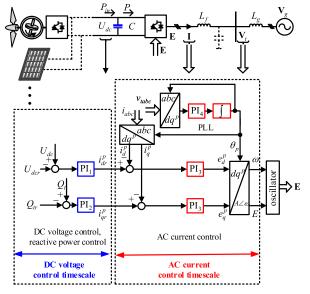

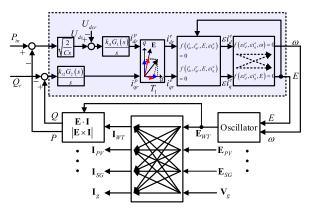

**FIGURE 1.** Diagram of a PE-interfaced device utilizing a typical vector control scheme.

modeling studies based on the way do not consider DVC. The confusion that remains unclarified in these studies is how the PE-interfaced device with DVC action regulates the internal voltage under the power imbalance and further affects the system dynamics.

Therefore, this study focuses on the process of the PE-interfaced device with DVC action participating in system dynamics to propose the modeling method of the device for the analysis of dynamic issues in DVC timescale. By establishing the model of the PE-interfaced device based on power-imbalance stimulation and internal-voltage response relationships, the regulation mechanism of the internal voltage amplitude/frequency by the device according to the active/reactive power imbalance can be depicted. Moreover, the regulation of the internal voltage is dominated by DVC. The effect of ACC dynamics makes the way DVC regulates the internal voltage unintuitive. So, it is necessary to further neglect ACC dynamics and establish the stimulation-response relationships with ideal ACC to directly describe the regulation by DVC. Subsequently, the characteristics of the PE-interfaced device in DVC timescale and its impact on the dynamics of the system can be analyzed.

The rest parts of this paper are organized as follows. Section II briefly introduces the control scheme of the PE-interfaced device. In Section III, the process of the PE-interfaced device participating in system dynamics, which determines the modeling requirements of the device, is analyzed. According to these requirements, the detailed modeling steps are presented and the characteristics of the PE-interfaced device are further revealed in Section IV. Combined with the simulation, Section V shows the feasibility of the proposed models and analyzes the role of the PE-interfaced device with DVC action in system dynamics. Finally, conclusions are drawn in Section VI.

# II. CONTROL PRINCIPLE OF PE-INTERFACED DEVICE

# A. CONTROL STRUCTURE OF PE-INTERFACED DEVICE

PE-interfaced devices such as direct-drive permanent magnet synchronous generator (PMSG)-based wind turbines (WTs) and photovoltaics (PVs) are connected to the grid through the power electronic converter as shown in Fig. 1. When analyzing dynamic issues with grid disturbance, the main consideration of PE-interfaced devices is the grid-side control due to the isolation of the DC capacitor [29]. To simplify the analysis, this study starts with the normal controls such as DVC and does not consider the switch elements such as chopper. Fig. 1 depicts a typical vector control scheme of the PE-interfaced device such as PMSG-based WT and PV [19], [30]. Based on the control parameter settings, different control loops have different bandwidths and response speeds [31]. The dual-loop vector control can be divided into the DVC and ACC timescale components according to the different response speeds of the controllers [31]. The DVC timescale component consists of the DC voltage controller and the reactive power controller. The DC voltage controller controls the voltage of the DC capacitor  $U_{dc}$  by adjusting the *d*-axis current reference  $i_{dr}^p$ . The reactive power controller controls the reactive power at terminal voltage node  $Q_t$ according to its reference  $Q_{tr}$  by adjusting the q-axis current reference  $i_{ar}^p$ . The ACC timescale component contains the AC current controller and the phase-locked loop (PLL). The AC current controller detects the current I of the filter inductor and adjusts the *d*-axis/*q*-axis internal voltage  $e_d^p/e_q^p$  to make the *d*-axis/*q*-axis current  $i_d^p/i_q^p$  track the current reference. The PLL provides the phase information  $\theta_p$  based on the terminal voltage. The internal voltage amplitude E and frequency  $\omega$  are composed of  $e_d^p$ ,  $e_q^p$ , and  $\theta_p$  according to the following equation:

$$E \cdot e^{j \int \omega dt} = \left(e_d^p + j e_q^p\right) \cdot e^{j\theta_p} \tag{1}$$

The detailed mathematical expressions of the DVC and ACC timescale components are given in Appendix A.

As shown in Fig. 1. the DVC and ACC timescale components are interrelated. The DVC timescale component determines the current references of the ACC timescale component. Meanwhile, their inputs are constrained by the circuit structure of the PE-interfaced device. If the power loss of the switch is neglected, the output power of the DC capacitor is equal to the active power determined by the internal voltage vector **E** and current vector **I** at AC side. The imbalance between  $Q_t$  and  $Q_{tr}$  is equivalent to the imbalance between the reactive power at internal voltage node Q and its reference  $Q_r$  [32]. Q is calculated from **E** and **I**. Thus, P/Q (input of the DVC timescale component) and **I** (input of the ACC timescale component) are mutually constrained. The relationship between them can be written as follows:

$$P + jQ = \left(E \cdot e^{j\int \omega dt}\right) \cdot \left(I \cdot e^{-j\int \omega_i dt}\right)$$

(2)

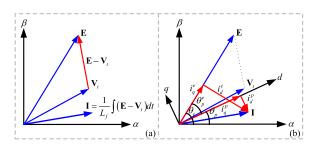

FIGURE 2. Relationships between different vectors and different coordinates.

# B. ORGANIZATION OF ACC TIMESCALE COMPONENT IN THE FORM OF INTERNAL VOLTAGE DEPENDING ONLY ON CURRENT ERROR

In a PE-interfaced device, the DVC timescale component aims to balance the input and output active powers as well as the reactive power and its reference. To match the DVC timescale component, the ACC timescale component makes the active/reactive current track the active/reactive current reference determined by the DVC timescale component. Although the ACC timescale component is an adjunct to the DVC timescale component, the ACC timescale component is an important bridge between the DVC timescale component and grid interactions. However, since PLL requires the acquisition of the terminal voltage phase  $\theta_t$ , it appears that the internal voltage formed by the ACC timescale component depends not only on the current error but also on the grid information. The indeterminate relationships of the ACC timescale component make it unclear how the DVC timescale component participates in system dynamics.

Due to the constrained relationship of filter inductance between terminal voltage vector  $\mathbf{V}_t$  and  $\mathbf{I}$  given in Fig 2 (a),  $\theta_t$  detected by PLL depends on  $\mathbf{I}$ . Hence, the relationships of the ACC timescale component are the stimulation-response relationships, where the internal voltage depends only on the current and its reference. Fig 2 (b) shows the relationships between the variables of the current vector at different coordinates. The detailed mathematical expressions of the transformation in different coordinates are given in Appendix A. Based on these, both *d*-axis/*q*-axis current error  $\varepsilon t_d^p / \varepsilon t_q^p$  and the phase error  $\theta_p^t$  can be expressed by the active/reactive current  $i_d^e / i_q^e$  and the active/reactive current reference  $i_{dr}^e / i_{qr}^e$  as follows:

$$\varepsilon i_{dr}^{p} + \varepsilon j i_{qr}^{p} = \left(\varepsilon i_{dr}^{e} + j\varepsilon i_{qr}^{e}\right) \cdot e^{j\left(\theta_{p} - \theta_{e}\right)}$$

(3)

$$\theta_p^t = f\left(\varepsilon i_d^e, \varepsilon i_q^e, i_{dr}^e, i_{qr}^e\right) \tag{4}$$

The detailed mathematical expression of  $f\left(\varepsilon i_d^e, \varepsilon i_q^e, i_{dr}^e, i_{qr}^e\right)$  is provided in Appendix B and the detailed derivation process has been given in [27]. Then, the ACC timescale component can be equivalently expressed as the relationships in the form of the internal voltage frequency/amplitude depending only on the active/reactive current error. The derivation process and mathematical expression of the ACC timescale component are given in detail in the later modeling section.

# III. REGULATION MECHANISM OF INTERNAL VOLTAGE BY PE-INTERFACED DEVICE ACCORDING TO POWER IMBALANCE IN SYSTEM DYNAMICS AND MODELING IDEAS

Based on the control structure of the PE-interfaced device, this section recognizes the mechanism of the device participation in system dynamics and modeling requirements. First, we demonstrate how the PE-interfaced device forms and controls the amplitude and frequency of the internal voltage to satisfy the system requirements with the DVC and ACC timescale components. Then, the action process of the DVC and ACC timescale components participating in system dynamics is analyzed. Based on these insights, modeling requirements are proposed.

# A. MECHANISM OF THE FORMATION OF INTERNAL VOLTAGE IN RESPONSE TO POWER IMBALANCE STIMULATION

Power systems require balancing the active and reactive power flows and maintaining the voltage magnitude and frequency [10], [11]. The PE-interfaced device is designed to transfer active and reactive powers and regulate the internal voltage magnitude and frequency for the system requirements [9], [33], [34], [35]. A PE-interfaced device can output active and reactive powers by establishing an internal voltage and can further adjust the powers by changing the internal voltage magnitude and frequency [9], [12].

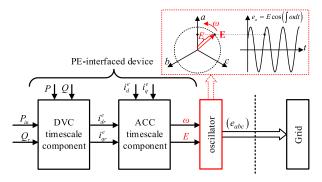

Based on the control structure of the PE-interfaced device described in Section II, the formation of the internal voltage by the ACC and DVC timescale components is shown in Fig 3. Due to the power-current constraint, grid disturbance affects both the active/reactive power imbalance  $\varepsilon P/\varepsilon Q$  of the DVC timescale component and the active/reactive current imbalance  $\varepsilon i_d^e/\varepsilon i_q^e$  of the ACC timescale component. The DVC timescale component adjusts  $i_{dr}^e/i_{qr}^e$  according to  $\varepsilon P/\varepsilon Q$ . The ACC timescale component regulates  $E/\omega$  according to  $\varepsilon i_d^e/\varepsilon i_q^e$ . Eventually, the AC instantaneous value of the internal voltage  $e_{abc}$  is formed by the oscillator according to  $E/\omega$  and connected to the grid [36], [37].

Therefore, the internal voltage is determined by both the ACC and DVC timescale components of the PE-interfaced device. As with the ACC timescale component, the dynamics of the DVC timescale component are reflected in the amplitude and frequency of the internal voltage.

# B. MODELING IDEAS BASED ON THE REGULATION PROCESS OF INTERNAL VOLTAGE BY PE-INTERFACED DEVICE ACCORDING TO POWER IMBALANCE IN SYSTEM DYNAMICS

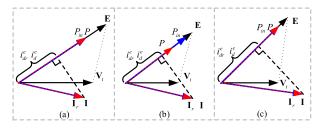

When the PE-interfaced device is connected to a weak grid, Fig. 4 shows the dynamic processes of electrical variables under the continuous power imbalance caused by an increase of reactive load. Before the disturbance,  $i_d^e$  equals  $i_{dr}^e$ , and *P* is balanced with input power  $P_{in}$ , as shown in Fig. 4 (a). When the power grid is disturbed,  $i_d^e$  and *P* change instantly. The fast-responding ACC timescale component detects the

FIGURE 3. Formation of the internal voltage by the ACC and DVC timescale components in response to power imbalance stimulation.

FIGURE 4. Dynamic processes of electrical variables under continuous power disturbance in a weak grid.

current imbalance and adjusts the internal voltage to restore the current balance. Due to the weak grid condition, the amplitude of  $\mathbf{V}_t$  decreases after disturbance, and the ACC timescale component requires a reduction in the amplitude of  $\mathbf{E}$  to rebalance  $i_d^e$  and  $i_{dr}^e$ , as shown in Fig. 4 (b). *P* is lower than  $P_{in}$  because the amplitude of  $\mathbf{E}$  is reduced, even though  $i_d^e$ is balanced with  $i_{dr}^e$ . Thus, the regulation of the internal voltage by the ACC timescale component alone cannot achieve power balancing, and the continuous power imbalance causes the action of the DVC timescale component.

Based on the formation mechanism of the internal voltage shown in Fig. 3, when the DVC timescale component changes  $i_{dr}^e/i_{qr}^e$ , the ACC timescale component immediately regulates  $E/\omega$ , forcing  $i_d^e/i_q^e$  to track  $i_{dr}^e/i_{qr}^e$ . Since the ACC timescale component regulates  $E/\omega$  depending only on  $\varepsilon i_d^e/\varepsilon i_q^e$ , once the DVC timescale component changes  $i_{dr}^e/i_{qr}^e$  according to  $\varepsilon P/\varepsilon Q$ , there is always a corresponding  $E/\omega$ . In this way, the DVC timescale component regulates  $E/\omega$  until the power is rebalanced, as shown in Fig. 4 (c). Hence, the DVC timescale component of the PE-interfaced device acts to participate in system dynamics by regulating the internal voltage amplitude/frequency according to the active/reactive power imbalance.

Due to the participation of DVC timescale component, the system appears to have corresponding dynamics in DVC timescale (around 100ms). For the dynamic problems in DVC timescale, the relationships between the active/reactive power imbalance and the internal voltage amplitude/frequency involving the DVC timescale component need to be proposed to reflect the characteristic and role of the PE-interfaced device. Moreover, because the regulation of the internal voltage amplitude/frequency under active/reactive power imbalance is dominated by the DVC timescale component, the model of the PE-interfaced device with the ideal ACC timescale component should be further established to directly reflect the characteristic in DVC timescale determined by the DVC timescale component.

# IV. MODELING OF PE-INTERFACED DEVICE BASED ON POWER-IMBALANCE STIMULATION AND INTERNAL-VOLTAGE RESPONSE RELATIONSHIPS IN DVC TIMESCALE

According to the modeling requirements, this section presents the detailed modeling steps of the PE-interfaced device. We first replace the active/reactive current with active/reactive power to establish stimulation-response relationships of the PE-interfaced device where the internal voltage depends solely on the power imbalance. Then, we neglect the influence of ACC timescale component dynamics and obtain the model of the PE-interfaced device with ideal ACC. Based on the model, the characteristics of the device in DVC timescale are revealed.

# A. REPLACEMENT OF ACTIVE/REACTIVE CURRENT BY ACTIVE/REACTIVE POWER TO ESTABLISH STIMULATION-RESPONSE RELATIONSHIPS WHERE INTERNAL VOLTAGE DEPENDS SOLELY ON POWER IMBALANCE

Based on the control structure of the PE-interfaced device, the device includes the ACC and DVC timescale components. The DVC timescale component is composed of DC capacitance, DVC, and reactive power control. The equation of the DC capacitance can be written as

$$U_{dc} = \sqrt{(2/C) \int (P_{in} - P) dt}$$

(5)

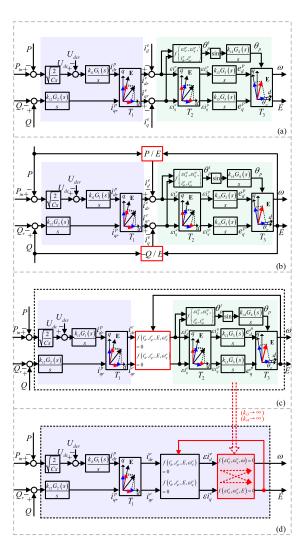

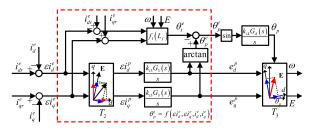

This equation constrains the relationship between  $U_{dc}$  (input of DVC) and *P*. Combining (5) with the equations of DVC, reactive power control, and  $T_1\left(i_{dr}^p, i_{qr}^p \rightarrow i_{dr}^e, i_{qr}^e\right)$ , which are given in Appendix A, the relationships of the DVC timescale component between  $\varepsilon P/\varepsilon Q$  and  $i_{dr}^e/i_{qr}^e$  are obtained and shown in the blue box in Fig. 5 (a).

The ACC timescale component includes ACC and PLL. According to (3) and (4),  $\varepsilon t_d^p / \varepsilon t_q^p$  and  $\theta_p^t$  depend on  $\varepsilon i_d^e / \varepsilon i_q^e$ . Combining (3) and (4) with the equations of ACC, PLL, and  $T_3(e_d^p, e_q^p \to E, \omega)$  which are given in Appendix A, the relationships of the ACC timescale component between  $\varepsilon i_d^e / \varepsilon i_q^e$ and  $E/\omega$  are also obtained, as shown in the green box in Fig. 5 (a). Therefore, the relationships of the PE-interfaced device shown in Fig 5 (a) can be obtained.

However, the stimulation-response relationships are not explicit because the relationships take both P/Q and  $i_d^e/i_q^e$  as stimulations. In fact, during the regulation of the internal voltage, the dynamics of P/Q and  $i_d^e/i_q^e$  are constrained by (2), which can be further expressed as:

$$P + jQ = E \cdot I \cdot e^{j \int (\omega - \omega_i)dt} = E\left(i_d^e - ji_q^e\right) \tag{6}$$

FIGURE 5. Septs of establishing the model of the PE-interfaced device in DVC timescale.

Under the joint constraint of this relationship and that of the ACC and DVC timescale components, there exist stimulation-response relationships where the internal voltage amplitude/frequency depends solely on the active/reactive power imbalance.

Based on (6),  $i_d^e/i_q^e$  can be expressed in terms of P/Q and E as follows:

$$\begin{cases} i_d^e = P/E \\ i_q^e = -Q/E \end{cases}$$

(7)

By converting the input of the ACC timescale component into P/Q, the relationships shown in Fig. 5 (a) can be transformed into those shown in Fig. 5 (b).

Because P/Q and  $i_{dr}^e/i_{qr}^e$  are constrained by the relationships of the DVC timescale component and P/Q and  $i_d^e/i_q^e$  are constrained by (7),  $i_{dr}^e/i_{qr}^e$  and  $\varepsilon i_d^e/\varepsilon i_q^e$  are also constrained and the constraint relationships can be further collated as

$$f\left(i_{dr}^{e}, i_{qr}^{e}, E, \varepsilon i_{d}^{e}\right) = 0$$

(8)

$$f\left(i_{dr}^{e}, i_{qr}^{e}, E, \varepsilon i_{q}^{e}\right) = 0 \tag{9}$$

FIGURE 6. Simulation scenario of renewable energy generations transmitting power through long lines.

The stimulation-response relationships in Fig. 5 (b) can then be converted into those shown in Fig. 5 (c).

The relationships of the PE-interfaced device shown in Fig. 5 (c) explicitly describe how the DVC timescale component regulates the internal voltage amplitude/frequency according to the active/reactive power imbalance with the assistance of the ACC timescale component.

# B. NEGLECTION OF THE INFLUENCE OF ACC TIMESCALE COMPONENT DYNAMICS TO OBTAIN RELATIONSHIPS BETWEEN POWER IMBALANCE AND INTERNAL VOLTAGE WITH IDEAL ACC

The ACC timescale component dynamics affect the regulation of the internal voltage amplitude/frequency by the DVC timescale component. In this regulation process, the current error in DVC timescale may be large or small in different scenarios. If the current error in DVC timescale is small, the ACC timescale component enables the active and reactive currents to track their references given by the DVC timescale component in almost real time. In other words, it can be assumed that the ACC timescale component is nearly ideal. The relationships between power imbalance and internal voltage with the ideal ACC timescale component can be further established based on the relationships with the nonideal ACC timescale component, by eliminating the influence of ACC timescale component dynamics.

Specifically, the ACC integrator gain approaches infinity, which makes  $\varepsilon t_d^p / \varepsilon t_q^p$  zero. Likewise, the PLL integrator gain tends to infinity, so that  $\theta_t$  and  $\theta_p$  are equal in real time. The equations are as follows:

$$e_d^p = (k_{i3}/p) G_3(s) (i_{dr}^p - i_d^p) \quad (k_{i3} \to \infty)$$

(10)

$$e_q^p = (k_{i3}/p) G_3(s) \left( i_{qr}^p - i_q^p \right) \quad (k_{i3} \to \infty)$$

(11)

$$\theta_p = (k_{i4}/p) G_4(s) \sin(\theta_t - \theta_p) \quad (k_{i4} \to \infty)$$

(12)

Combining these with (1), (3), and (4), we obtain:

$$f\left(\varepsilon i_d^e, \varepsilon i_q^e, \omega\right) = 0 \tag{13}$$

$$f\left(\varepsilon i_d^e, \varepsilon i_q^e, E\right) = 0 \tag{14}$$

Whenever  $i_d^e/i_q^e$  deviates from  $i_{dr}^e/i_{qr}^e$ , the ideal ACC timescale component adjusts  $E/\omega$  to the position where  $i_d^e/i_q^e$  equals  $i_{dr}^e/i_{qr}^e$  immediately. Thus, the relationships of the ideal ACC timescale component are obtained, as shown by the red box in Fig 5 (d). The ideal ACC timescale component can be considered as an energy storage component with an

infinitesimal energy storage capacity that can act without delay, similar to [38]. Then, the relationships between the active/reactive power imbalance and the internal voltage frequency/amplitude with the ideal ACC timescale component can be established, as shown in Fig. 5 (d).

The proposed model with ideal ACC can directly illustrate the adjustment of the internal voltage amplitude/frequency by the DVC timescale component under active/reactive power imbalance. It should be noted that although the proposed model with ideal ACC ignores the influence of ACC timescale component dynamics, it retains the basic way in which the PE-interfaced device originally participates in the system dynamics. This is important for the analysis of the characteristic and role of the PE-interfaced device in the dynamics of the multi-device interaction.

# C. CHARACTERISTIC OF RELATIONSHIPS BETWEEN POWER IMBALANCE AND INTERNAL VOLTAGE IN DVC TIMESCALE

Based on the model of the PE-interfaced device with ideal ACC, the characteristic of the PE-interfaced device in regulating the internal voltage amplitude/frequency in DVC timescale can be further revealed.

As shown in Fig 5 (d), in the process of the DVC timescale component regulating E and  $\omega$ , both  $i_{dr}^e$  and  $i_{qr}^e$  affect E via the ACC timescale component. Subsequently, the change in E influences both  $\varepsilon i_d^e$  and  $\varepsilon i_a^e$  through the feedback path indicated by the red arrow in Fig. 5 (d). Under these current imbalances caused by the change of E, both E and  $\omega$ vary simultaneously. Therefore, there are couplings between the  $\varepsilon P$  stimulation and  $\omega$  response relationship and the  $\varepsilon Q$ stimulation and E response relationship. Moreover, the relationships between  $\varepsilon P/\varepsilon Q$  and  $E/\omega$  are jointly determined by the DC capacitance and controls in DVC timescale. It makes the order of the stimulation-response relationships higher than first-order. Therefore, the PE-interfaced device exhibits coupling and high-order characteristics for the regulation of the internal voltage amplitude/frequency under the active/reactive power imbalance in DVC timescale. The coupling and high-order characteristics of the device increase the order of system dynamics, which may increase the risk of system instability.

In the following simulation section, the feasibility of the proposed models is illustrated, and how the stimulation-response characteristics of the device in DVC timescale affect the system dynamics is preliminarily explored based on the proposed model.

#### **V. SIMULATION ANALYSIS**

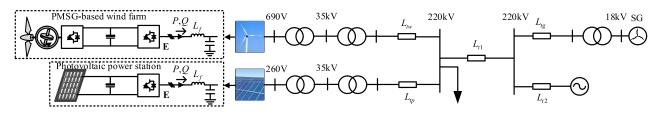

#### A. SIMULATION SCENARIO DESCRIPTION

The cases in [3], [4], [5], [6], and [7] with dynamic problems share a common feature: renewable energy generations transmit power through long lines and the synchronous generators (SGs) are distant from the renewable energy sources. So, the system shown in Fig. 6 is used as the simulation scenario for the analysis in this section. In the system, a PMSG-based wind farm and a PV power station are connected to the point of common coupling (PCC) bus, which is then connected to an SG and power grid through long lines. Two 30+i30 MVA local loads are also attached to the PCC bus. For simplicity, the wind farm with 50 PMSG-based WTs rated at 2 MW is simply represented by a single aggregated PMSG-based WT rated at 100 MW. The PV power station is represented by a PV device rated at 100 MW in the same manner. Moreover, the SG is rated at 200 MW. The parameters of PE-interfaced devices and network are listed in Appendix C.

# B. MODEL VERIFICATION AND SIMULATION OF THE REGULATION OF INTERNAL VOLTAGE UNDER POWER IMBALANCE

By organizing and deforming the original structure of the PEinterfaced device, the proposed model can directly depict the mechanism of the device participating in system dynamics and reveal the role and characteristics of the device in DVC timescale. Therefore, to illustrate the feasibility of the proposed models, the comparison of the simulation results is given to demonstrate that the proposed models are consistent with the original structure of the device in terms of DVC timescale dynamics. Then, we show that the participation mechanism determined by the original structure of the device can be represented on the proposed models.

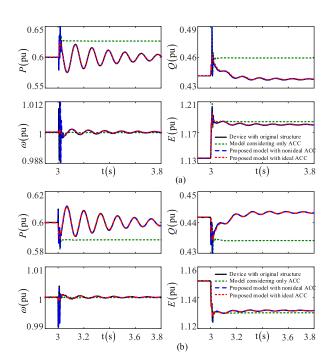

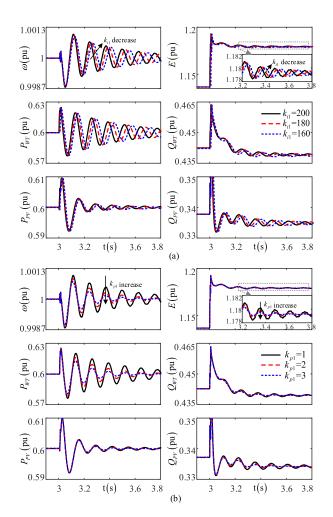

The PMSG-based WT in Fig. 6 is taken as an observation object to illustrate the feasibility of the proposed models of the PE-interfaced device. Fig. 7 shows the comparison results with the proposed models and the device with original structure in different disturbance scenarios. The simulation results of the proposed models with the nonideal ACC and ideal ACC are high consistent with those of the device with original structure regarding DVC timescale dynamics. The high coincidence of simulation results proves that the proposed models remain consistent with the original device in terms of DVC timescale dynamics, despite the collation and deformation in modeling. In contrast, the device model considering only ACC in [27] is completely unable to capture the DVC timescale dynamics of the device, as shown by the green dashed line in Fig. 7.

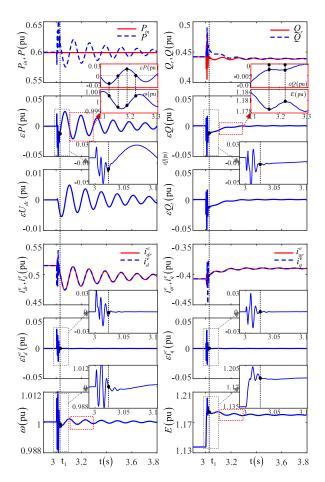

Taking the case where a 30+j30 MVA local load cuts out at 3 s as an example, Fig 8 shows the simulation waveforms of each variable of the device with the original structure when regulating the internal voltage under power imbalance. Some of the simulation waveforms near the time of disturbance are zoomed in. When the local load is cut out, P/Qgets unbalanced with  $P_{in}/Q_r$ , and  $i_d^e/i_q^e$  gets unbalanced with  $i_{dr}^e/i_{ar}^e$ . As shown in Fig 8, at t1, although the ACC timescale

**FIGURE 7.** Comparison of simulation results with the proposed models and the device with original structure under (a) Case 1 (A 30+j30 MVA load cuts out at 3 s) and (b) Case 2 (The SG cuts out at 3 s).

component makes  $i_d^e/i_q^e$  equal to  $i_{dr}^e/i_{qr}^e$  by regulating  $E/\omega$ , P/Q is still greater than  $P_{in}/Q_r$  because of the increase in E. The continuous power imbalance causes the action of the DVC timescale component.

As shown in Fig 8, the DVC timescale component adjusts  $i_{dr}^{e}/i_{qr}^{e}$  according to  $\varepsilon P/\varepsilon Q$ . The ACC timescale component then regulates  $E/\omega$  according to  $\varepsilon i_d^e/\varepsilon i_a^e$ . As long as  $\varepsilon i_d^e/\varepsilon i_a^e$ is not zero, the ACC timescale component regulates  $E/\omega$ until  $i_d^e/i_q^e$  equals  $i_{dr}^e/i_{qr}^e$ . With the assistance of the ACC timescale component, the dynamics of the DVC timescale component would be eventually reflected in the dynamics of  $E/\omega$ . As shown in the simulation results in Fig 8, the waveforms of  $E/\omega$  present DVC timescale dynamics in addition to ACC timescale dynamics. The above regulation process of the internal voltage provided by the simulation of the device with original structure is consistent with that described by the proposed model. Therefore, the proposed model with the nonideal ACC can represent the actual regulation of the internal voltage amplitude/frequency by the PE-interfaced device with DVC action under active/reactive power imbalance stimulation.

In the process of regulating the internal voltage by the DVC timescale component, there are current errors due to the dynamics of the ACC timescale component. As shown in Fig. 8, the dynamics of  $\varepsilon i_d^e / \varepsilon i_q^e$  in ACC timescale are relatively large, while the dynamics of  $\varepsilon i_d^e / \varepsilon i_q^e$  in DVC timescale are almost zero. For the dynamics in DVC timescale focused on in this study, the ACC timescale component can effectively assist the DVC timescale component in regulating the internal voltage amplitude and frequency, and the effect of ACC timescale component dynamics is so small that it can

FIGURE 8. Time domain simulation of each variable in the regulation process of the internal voltage amplitude/frequency under the active/reactive power imbalance.

be ignored. Therefore, in this situation, the proposed model with the ideal ACC can directly represent the regulation of the internal voltage by DVC timescale controls under power imbalance and the characteristics of the device in DVC timescale.

The magnified red diagrams in Fig. 8 shows the detailed correspondence between the power imbalance and the internal voltage in DVC timescale. Due to the coupling and high-order characteristics of the PE-interfaced device in DVC timescale, the correspondence between the waveforms of the active/reactive power imbalance and the internal voltage magnitude/frequency is not simply a 90-degree phase shift of first-order integration, but a more complex correspondence.

# C. PRELIMINARY UNDERSTANDINGS OF THE ROLE OF PE-INTERFACED DEVICE WITH DVC IN SYSTEM DYNAMICS

In an actual system, different control parameters of the PE-interfaced device result in different system dynamics. Furthermore, the diversity of control schemes adopted by different device manufacturers makes the dynamic issue more complex. It is difficult to analyze how the DVC timescale controls of the PE-interfaced device affect the system dynamics based directly on the detailed connections of hardware

FIGURE 9. Block diagram of the closed loop for the multi-device system.

and controls of the device, without a mechanism description of the device. Because the proposed model directly illustrates the mechanism of the PE-interfaced device with DVC action participating in system dynamics, how the device with coupling and high-order characteristics in DVC timescale affects system dynamics can be further analyzed based on the proposed model.

According to the proposed model in DVC timescale, the block diagram of the closed loop for the multi-device system can be obtained, as shown in Fig 9. When the system is disturbed and deviates from the steady-state operating point, active/reactive power imbalance acts on the PE-interfaced device. The DVC timescale component of the device regulates the magnitude/frequency of the internal voltage according to the active/reactive power imbalance. The variation of the internal voltage magnitude/frequency further alters the AC instantaneous value of the internal voltage through the oscillator. The AC instantaneous values of the internal voltages of the device and other devices act on the network to change the AC instantaneous values of the currents. The AC instantaneous values of the internal voltages and currents determine the output powers of the devices, which in turn affect the power imbalances of the devices. The cycle continues until the system reaches a steady-state operating point. Therefore, in this multi-device interaction process, the basic way in which DVC timescale controls of the PE-interfaced device affect the active/reactive power and voltage amplitude/frequency in the system is by regulating the internal voltage amplitude/frequency.

Fig 10 shows the waveforms of the internal voltage amplitude/frequency of the studied device and the waveforms of the active/reactive powers of PE-interfaced devices for different DVC parameters under the same disturbance. It can be seen that the changes of the DVC parameters are directly reflected in the internal voltage amplitude/frequency. Regardless of which control parameters are selected, the DVC timescale controls always regulate the internal voltage amplitude/frequency to affect the system dynamics.

The proposed model reveals a unified mechanism for the PE-interfaced device such as PMSG-based WT and PV with different DVC parameters influencing system dynamics.

**FIGURE 10.** Time domain simulation of the internal voltage amplitude/ frequency and active/reactive powers for different control parameters.

The different characteristics of the PE-interfaced device in DVC timescale illustrated by the stimulation-response relationships of the proposed model can lead to different system dynamics. This implies that we can further tune and optimize the characteristics of the PE-interfaced device in DVC timescale for the dynamic stability of the multi-device system based on our model. These studies will be conducted in the near future.

#### **VI. CONCLUSION**

For dynamic issues in DVC timescale associated with multi-device interaction involving DVC and ACC of PEinterfaced devices, this paper proposes a modeling method of the PE-interfaced device to analyze the characteristic and role of the device in the dynamics of the multi-device interaction. The main conclusions are listed as follows:

(1) The mechanism of the PE-interfaced device to participate in system dynamics is recognized. Both the ACC and DVC timescale components act on the grid by regulating the internal voltage amplitude/frequency. The characteristics of the PE-interfaced device are manifested as the regulation of

105222

the internal voltage magnitude/frequency according to the active/reactive power imbalance.

(2) The model of the PE-interfaced device based on the relationships between power-imbalance stimulation and internal-voltage response, which depicts the regulation of the internal voltage amplitude/frequency by the detailed controls under the active/reactive power imbalance, is established. To directly depict the regulation by the main DVC timescale component, the model of the PE-interfaced device with ideal ACC is further proposed through the infinity gain equivalence of ACC.

(3) The coupling and high-order characteristics the PEinterfaced device in DVC timescale are revealed based on the proposed model. The characteristics of the device affected by the control parameters are reflected in the internal voltage amplitude/frequency. No matter what control parameters are chosen, the PE-interfaced device affects system dynamics by regulating the internal voltage amplitude/frequency.

The regulation of the internal voltage amplitude/frequency according to the active/reactive power imbalance, which illustrates the characteristics of the PE-interfaced device, can be optimized based on the proposed model. The optimization of the characteristics of the PE-interfaced device for the dynamic stability of the multi-device system in DVC timescale will be studied in the near future.

# APPENDIX A DETAILED MATHEMATICAL EXPRESSIONS OF THE DVC AND ACC TIMESCALE COMPONENTS

A. DVC TIMESCALE COMPONENT

$$C_{dc}: U_{dc} = \sqrt{(2/C) \int (P_{in} - P) dt}$$

DC voltage control:  $i_{dr}^{p} = (k_{p1} + k_{i1}/s) (U_{dc} - U_{dcr})$

$= (k_{i1}/s) (T_{1}s+1) (U_{dc} - U_{dcr})$

$= (k_{i1}/s) G_{1} (s) (U_{dc} - U_{dcr})$

Reactive power control:  $i_{qr}^{p} = (k_{p2} + k_{i2}/s) (Q_{t} - Q_{tr})$

$= (k_{i2}/s) (T_{2}s + 1) (Q - Q_{r})$

$= (k_{i2}/s) G_{2} (s) (Q - Q_{r})$

## B. ACC TIMESCALE COMPONENT

$$d\text{-axis current control}: e_d^p = (k_{p3} + k_{i3}/s) (t_{dr}^p - t_d^p) = (k_{i3}/s) (T_{3s} + 1) (t_{dr}^p - t_d^p) = (k_{i3}/s) (T_{3s} + 1) \varepsilon t_d^p = (k_{i3}/s) G_3 (s) \varepsilon t_d^p$$

$q\text{-axis current control}: e_q^p = (k_{p3} + k_{i3}/s) \left(i_{qr}^p - i_q^p\right)$  $= (k_{i3}/s) (T_3s + 1) \left(i_{qr}^p - i_q^p\right)$  $= (k_{i3}/s) (T_3s + 1) \varepsilon i_q^p$

$$= (k_{i3}/s) G_3(s) \varepsilon i_q^p$$

PLL control :  $\theta_p = 1/s \cdot (k_{p4} + k_{i4}/s) \cdot \\ \times \sin(\theta_t - \theta_p)$

$$= (k_{i4}/s) [(T_4s + 1)/s] \\ \times \sin(\theta_t - \theta_p)$$

$$= (k_{i4}/s) [(T_4s + 1)/s] \sin(\theta_p^t)$$

$$= (k_{i4}/s) G_4(s) \sin(\theta_p^t)$$

$$L_{f}: V_{t} \cdot e^{j\theta_{t}} = E \cdot e^{j\int \omega dt} - L_{f}d\left(I \cdot e^{j\int \omega_{i}dt}\right)/dt$$

#### C. TRANSFORMATION

$$T_{1}\left(i_{dr}^{p}, i_{qr}^{p} \rightarrow i_{dr}^{e}, i_{qr}^{e}\right) : i_{dr}^{e} + ji_{qr}^{e} = \left(i_{dr}^{p} + ji_{qr}^{p}\right) \\ \cdot e^{j(\theta_{p} - \theta_{e})}$$

$$T_{2}\left(\varepsilon i_{d}^{e}, \varepsilon i_{q}^{e} \rightarrow \varepsilon i_{d}^{p}, \varepsilon i_{q}^{p}\right) : \varepsilon i_{d}^{p} + j\varepsilon i_{q}^{p} = \left(\varepsilon i_{d}^{e} + j\varepsilon i_{q}^{e}\right) \\ \cdot e^{j(\theta_{e} - \theta_{p})}$$

$$T_{3}\left(e_{d}^{p}, e_{q}^{p} \rightarrow E, \omega\right) : E \cdot e^{j\int \omega dt} = \left(e_{d}^{p} + je_{q}^{p}\right) \cdot e^{j\theta_{p}}$$

$$T_{4}\left(i_{d}^{e}, i_{q}^{e} \rightarrow I, \omega_{i}\right) : I \cdot e^{j\int \omega_{i}dt} = \left(i_{d}^{e} + ji_{q}^{e}\right) \cdot e^{j\int \omega dt}$$

#### **APPENDIX B**

## RELATIONSHIP BETWEEN ACTIVE/REACTIVE CURRENT ERROR AND PHASE ERROR

Combining equations of  $L_f$  and  $T_4$ , the equation of  $f_1(L_f)$  can be obtained as

$$\theta_t^e = \theta_e - \theta_t = \arctan\left[\left(sL_f i_q^e + \omega L_f i_d^e\right) / \left(E - sL_f i_d^e + \omega L_f i_q^e\right)\right]$$

where  $\theta_e = \int \omega dt$ . The relationship in the red dashed box is  $\theta_p^t = f\left(\varepsilon i_d^e, \varepsilon i_q^e, i_{dr}^e, i_{qr}^e\right)$ .

FIGURE 11. Relationship between active/reactive current error and phase error in the ACC timescale component.

#### APPENDIX C PARAMETERS OF THE STUDY SYSTEM

A. PARAMETERS VALUES OF THE TRANSMISSION LINES B. PARAMETERS VALUES OF THE PMSG-BASED WT

Rated values:  $S_{base_WT} = 2$  MW,  $V_{base_WT} = 690$  V,  $f_{base} = 50$  Hz,  $U_{dcbase_WT} = 1200$  V.

#### TABLE 1. Parameters values of the transmission lines.

| Line name | Value<br>(km) | Line name | Value<br>(km) |

|-----------|---------------|-----------|---------------|

| $L_{tw}$  | 10            | $L_{lg}$  | 10            |

| $L_{tp}$  | 10            | $L_{t1}$  | 210           |

| $L_{t2}$  | 30            |           |               |

TABLE 2. Controller parameters values of the PMSG-based WT.

| Parameter                       | Value<br>(pu) | Parameter          | Value<br>(pu) |

|---------------------------------|---------------|--------------------|---------------|

| DC voltage control              | (1, 200)      | AC current control | (1, 500)      |

| $(k_{p1}, k_{i1})$              |               | $(k_{p3}, k_{i3})$ |               |

| Reactive power                  | (0.1, 10)     | PLL control        | (100,         |

| control ( $k_{p2}$ , $k_{i2}$ ) |               | $(k_{p4}, k_{i4})$ | 4800)         |

## C. PARAMETERS VALUES OF THE PV

Rated values:  $S_{base_PV} = 400 \text{ kW}$ ,  $V_{base_PV} = 260 \text{ V}$ ,  $f_{base} = 50 \text{ Hz}$ ,  $U_{dcbase_PV} = 500 \text{ V}$

#### TABLE 3. Controller parameters values of the PV.

| Parameter                       | Value<br>(pu) | Parameter          | Value<br>(pu) |

|---------------------------------|---------------|--------------------|---------------|

| DC voltage control              | (5, 200)      | AC current control | (1, 200)      |

| $(k_{_{p1}}, k_{_{i1}})$        |               | $(k_{p3}, k_{i3})$ |               |

| Reactive power                  | (1, 50)       | PLL control        | (50,          |

| control ( $k_{p2}$ , $k_{i2}$ ) |               | $(k_{p4}, k_{i4})$ | 1200)         |

#### REFERENCES

- F. Blaabjerg and K. Ma, "Future on power electronics for wind turbine systems," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 1, no. 3, pp. 139–152, Sep. 2013.

- [2] X. Zhou, S. Chen, Z. Lu, Y. Huang, S. Ma, and Q. Zhao, "Technology features of the new generation power system in China," *Proc. CSEE*, vol. 38, no. 7, pp. 1893–1904, Apr. 2018.

- [3] M. J. Li, Z. Yu, T. Xu, J. B. He, C. Wang, X. R. Xie, and C. Liu, "Study of complex oscillation caused by renewable energy integration and its solution," *Power Syst. Technol.*, vol. 42, no. 4, pp. 1035–1042, Apr. 2017.

- [4] A. Jalali, B. Badrzadeh, J. Lu, N. Modi, and M. Gordon, "System strength challenges and solutions developed for a remote area of Australian power system with high penetration of inverter-based resources," *CIGRE Sci, Eng.*, vol. 20, pp. 27–37, Feb. 2021.

- [5] Y. Cheng, L. Fan, J. Rose, S.-H. Huang, J. Schmall, X. Wang, X. Xie, J. Shair, J. R. Ramamurthy, N. Modi, C. Li, C. Wang, S. Shah, B. Pal, Z. Miao, A. Isaacs, J. Mahseredjian, and J. Zhou, "Real-world subsynchronous oscillation events in power grids with high penetrations of inverter-based resources," *IEEE Trans. Power Syst.*, vol. 38, no. 1, pp. 316–330, Jan. 2023.

- [6] V. Diedrichs, A. Beekmann, and S. Adloff, "Loss of (angle) stability of wind power plants-the underestimated phenomenon in case of very low short circuit ratio," in *Proc. 10th Int. Workshop Large-Scale Integr. Wind Power Into Power Syst.*, Jul. 2011, pp. 395–402.

- [7] C. Li, "Unstable operation of photovoltaic inverter from field experiences," *IEEE Trans. Power Del.*, vol. 33, no. 2, pp. 1013–1015, Apr. 2018.

- [8] H. Yang and X. M. Yuan, "Power characteristic with excitation of time-varying amplitude-frequency internal voltages during electromechanical dynamic process in power systems," *Proc. CSEE*, vol. 41, no. 9, pp. 3079–3089, May 2021.

- [9] X. M. Yuan and S. Li, "An amplitude/frequency modulation based method of voltage source converter for power systems dynamic analysis in current control timescale," *Proc. CSEE*, vol. 40, no. 15, pp. 4732–4743, Aug. 2020.

- [10] P. Kundur, Power System Stability and Control. New York, NY, USA: McGraw-Hill, 1994.

- [11] P. M. Anderson and A. A. Fouad, *Power System Control and Stability*, 2nd ed. New York, NY, USA: IEEE Press, 2003.

- [12] X. M. Yuan and W. He, "Amplitude/frequency as prerequisites of operation and thus classification of stability problems and capability opportunities for new generations," *J. Power Supply*, vol. 19, no. 6, pp. 1–9, Nov. 2021.

- [13] F. Blaabjerg and Z. Chen, *Power Electronics for Modern Wind Turbines*. San Rafael, CA, USA: Morgan & Claypool, 2006.

- [14] K. Clark, N. W. Miller, and J. J. Sanchez-Casca, "Modeling of GE wind turbine-generators for grid studies," GE Inc., Schenectady, NY, USA, Tech. Rep., Apr. 2010.

- [15] A. Ellis, Y. Kazachkov, E. Muljadi, P. Pourbeik, and J. J. Sanchez-Gasca, "Description and technical specifications for generic WTG models— A status report," in *Proc. IEEE/PES Power Syst. Conf. Expo.*, Mar. 2011, pp. 1–8.

- [16] K. Sano, S. Horiuchi, and T. Noda, "Comparison and selection of grid-tied inverter models for accurate and efficient EMT simulations," *IEEE Trans. Power Electron.*, vol. 37, no. 3, pp. 3462–3472, Mar. 2022.

- [17] S. K. Gurumurthy, M. Mirz, B. S. Amevor, F. Ponci, and A. Monti, "Hybrid dynamic phasor modeling approaches for accurate closed-loop simulation of power converters," *IEEE Access*, vol. 10, pp. 101643–101655, 2022.

- [18] N. Pogaku, M. Prodanovic, and T. C. Green, "Modeling, analysis and testing of autonomous operation of an inverter-based microgrid," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 613–625, Mar. 2007.

- [19] E. I. Batzelis, G. Anagnostou, I. R. Cole, T. R. Betts, and B. C. Pal, "A statespace dynamic model for photovoltaic systems with full ancillary services support," *IEEE Trans. Sustain. Energy*, vol. 10, no. 3, pp. 1399–1409, Jul. 2019.

- [20] W. Du, Y. Wang, H. F. Wang, B. Ren, and X. Xiao, "Small-disturbance stability limit of a grid-connected wind farm with PMSGs in the timescale of DC voltage dynamics," *IEEE Trans. Power Syst.*, vol. 36, no. 3, pp. 2366–2379, May 2021.

- [21] Z. Yang, R. Ma, S. Cheng, and M. Zhan, "Nonlinear modeling and analysis of grid-connected voltage-source converters under voltage dips," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 4, pp. 3281–3292, Dec. 2020.

- [22] J. Sun, "Small-signal methods for AC distributed power systems— A review," *IEEE Trans. Power Electron.*, vol. 24, no. 11, pp. 2545–2554, Nov. 2009.

- [23] X. Wang, F. Blaabjerg, and W. Wu, "Modeling and analysis of harmonic stability in an AC power-electronics-based power system," *IEEE Trans. Power Electron.*, vol. 29, no. 12, pp. 6421–6432, Dec. 2014.

- [24] D. Lu, X. Wang, and F. Blaabjerg, "Impedance-based analysis of DClink voltage dynamics in voltage-source converters," *IEEE Trans. Power Electron.*, vol. 34, no. 4, pp. 3973–3985, Apr. 2019.

- [25] M. Eskandari, A. V. Savkin, H. H. Alhelou, and F. Blaabjerg, "Explicit impedance modeling and shaping of grid-connected converters via an enhanced PLL for stabilizing the weak grid connection," *IEEE Access*, vol. 10, pp. 128874–128889, 2022.

- [26] Y. Lei, G. H. Li, W. S. Wang, G. Q. He, and Z. X. Guo, "Impedance modeling and characteristics analysis of photovoltaic generation considering photovoltaic array," *Proc. CSEE*, 2023. [Online]. Available: http://kns.cnki.net/kcms/detail/11.2107.TM.20230517.1748.008.html

- [27] X. Gong, X. M. Yuan, and S. C. Wang, "Modeling of VSC with active/reactive current excitation and internal voltage response for analyzing amplitude/frequency modulation dynamics of the grid," *CSEE J. Power Energy Syst.*, 2022, doi: 10.17775/CSEEJPES.2022.00560.

- [28] X. M. Yuan and S. C. Wang, "Operating-point identification from dimensions of alternating signal based on the incremental iterative mapping mechanism for analyzing dynamics of AC systems," CSEE J. Power Energy Syst., 2022, doi: 10.17775/CSEEJPES.2022.01270.

- [29] J. W. Kolar, T. Friedli, J. Rodriguez, and P. W. Wheeler, "Review of threephase PWM AC–AC converter topologies," *IEEE Trans. Ind. Electron.*, vol. 58, no. 11, pp. 4988–5006, Nov. 2011.

- [30] B. Wu, Y. Q. Lang, N. Zargari, and S. Kouro, Power Conversion and Control of Wind Energy Systems. Hoboken, NJ, USA: Wiley, 2011.

- [31] X. M. Yuan, J. B. Hu, and S. J. Cheng, "Multi-time scale dynamics in power electronics-dominated power systems," *Frontiers Mech. Eng.*, vol. 12, no. 3, pp. 303–311, 2017.

- [32] M. H. Wan, X. M. Yuan, and J. B. Hu, "Relationships of internal voltage dependence on power imbalance illustrating characteristics and roles in system dynamics of inertial-controlled DFIG-based wind turbines," *CSEE J. Power Energy Syst.*, 2021, doi: 10.17775/CSEEJPES.2021.05250.

- [33] Grid Code: High and Extra High Voltage, E. ON Netz GmbH, Bayreuth, Germany, 2006.

- [34] Technical Requirements for Connecting Photovoltaic Power Station to Power System, Standard GB/T 19964-2012, 2012.

- [35] Technical Specification for Connecting Wind Farm to Power System—Part 1: On Shore Wind Power, Standard GB/T 19963.1-2021, 2021.

- [36] R. Wu, S. B. Dewan, and G. R. Slemon, "Analysis of an AC-to-DC voltage source converter using PWM with phase and amplitude control," *IEEE Trans. Ind. Appl.*, vol. 27, no. 2, pp. 355–364, Mar./Apr. 1991.

- [37] M. P. Kazmierkowski and L. Malesani, "Current control techniques for three-phase voltage-source PWM converters: A survey," *IEEE Trans. Ind. Electron.*, vol. 45, no. 5, pp. 691–703, Oct. 1998.

- [38] D. Wang, X. Yuan, and M. Zhang, "Power-balancing based induction machine model for power system dynamic analysis in electromechanical timescale," *Energies*, vol. 11, no. 2, p. 438, Feb. 2018.

**JIN HUANG** received the B.Eng. degree from the School of Electrical Engineering, Beijing Jiaotong University (BJTU), Beijing, China, in July 2016. He is currently pursuing the Ph.D. degree with the State Key Laboratory of Advanced Electromagnetic and Technology, School of Electrical and Electronic Engineering, Huazhong University of Science and Technology (HUST), Wuhan, China. His aurent research interacts include control

His current research interests include control and stability of power systems with renewable

energy generations, in particular on dynamic modeling of power electronic (PE)-interfaced device and analysis of dynamics in DC voltage control timescale of power systems with high penetration of PE-interfaced device.

**XIAOMING YUAN** (Senior Member, IEEE) received the B.Eng. degree in electrical engineering from Shandong University, Jinan, China, in 1986, the M.Eng. degree in electrical engineering from Zhejiang University, Hangzhou, China, in 1993, and the Ph.D. degree in electrical engineering from the Federal University of Santa Catarina, Florianópolis, Brazil, in 1998.

He has been a Full Professor with the Huazhong University of Science and Technology, since 2011.

He served as a Chief Engineer of electrical engineering for the global research center of the General Electric company prior to his university career. He is a pioneer in the area of dynamics of power electronics dominated large power systems, and he developed the "amplitude/frequency modulation theory" for analyzing dynamics of general AC power systems.

**SICHENG WANG** received the B.Eng. degree from the School of Electrical Engineering, Southwest Jiaotong University (SWJTU), Chengdu, China, in July 2017. He is currently pursuing the Ph.D. degree with the State Key Laboratory of Advanced Electromagnetic and Technology, School of Electrical and Electronic Engineering, Huazhong University of Science and Technology (HUST), Wuhan, China.

His current research interests include control and stability of power systems with renewable energy generations and high-voltage dc (HVDC) transmission, in particular on dynamic modeling and analysis of small disturbance stability in the current control timescale of voltage source converter (VSC) interfaced power systems.