Received 24 August 2023, accepted 1 September 2023, date of publication 7 September 2023, date of current version 13 September 2023.

Digital Object Identifier 10.1109/ACCESS.2023.3312727

## **RESEARCH ARTICLE**

# A Subthreshold Operation Series-Parallel Charge Pump Incorporating Dynamic Source-Fed Oscillator for Wide-Input-Voltage Energy Harvesting Application

YONG JACK KEE<sup>1</sup>, (Student Member, IEEE),

HARIKRISHNAN RAMIAH<sup>®</sup><sup>1</sup>, (Senior Member, IEEE), KISHORE KUMAR PAKKIRISAMI CHURCHILL<sup>1</sup>, (Member, IEEE), GABRIEL CHONG<sup>2</sup>, (Member, IEEE), SAAD MEKHILEF<sup>®3</sup>, (Fellow, IEEE), NAI SHYAN LAI<sup>4</sup>, YONG CHEN<sup>®5</sup>, (Senior Member, IEEE), PUI-IN MAK<sup>®5</sup>, (Fellow, IEEE), AND RUI P. MARTINS<sup>®5,6</sup>, (Life Fellow, IEEE)

<sup>1</sup>Department of Electrical Engineering, Faculty of Engineering, University of Malaya, Kuala Lumpur 50603, Malaysia

<sup>2</sup>Nexperia Research and Development Penang, Bayan Lepas 11900, Malaysia

<sup>3</sup>School of Science, Computing and Engineering Technologies, Swinburne University of Technology, Melbourne, VIC 3122, Australia

<sup>4</sup>School of Engineering, Asia Pacific University of Technology and Innovation, Kuala Lumpur 57000, Malaysia

<sup>5</sup>Institute of Microelectronics, State Key Laboratory of Analog and Mixed Signal VLSI, Faculty of Science and Technology–ECE, University of Macau, Macau, China

<sup>6</sup>Instituto Superior Técnico, Universidade de Lisboa, 1649-004 Lisbon, Portugal (On leave)

Corresponding authors: Harikrishnan Ramiah (hrkhari@um.edu.my) and Yong Chen (ychen@um.edu.mo)

This work was supported in part by the Research University (RU) Grant-Faculty Program under Grant GPF056B-2020, and in part by the Collaborative Research In Engineering, Science and Technology (CREST) Program under Grant T05C2-19(PV026-2020).

**ABSTRACT** This work proposes a CMOS reconfigurable charge pump (CP) for a low-voltage energy harvesting system. It utilizes the low effective resistance from the parallel CP to enhance its power conversion efficiency (PCE). The CP exhibits an adaptive configuration with different stages depending on the input voltage, changing its voltage conversion ratio (VCR) to limit the output voltage under 1.8-V. Additionally, this work develops a novel dynamic source-fed oscillator that modulates the oscillating frequency by utilizing a dynamic source for the ring-voltage controlled oscillator (RVCO). The independent source from the RVCO and the clock-generating units from the proposed technique permit the implementation of frequency modulation without affecting the clock amplitude. Fabricated in 65-nm CMOS, the proposed prototype measures 62% peak PCE with an input voltage range of 0.26-V to 0.64-V.

**INDEX TERMS** Reconfigurable charge pump (CP), ring-voltage controlled oscillator (RVCO), dc-to-dc converter, low power energy harvesting, CMOS, power conversion efficiency (PCE).

#### I. INTRODUCTION

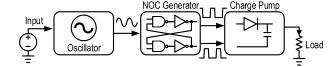

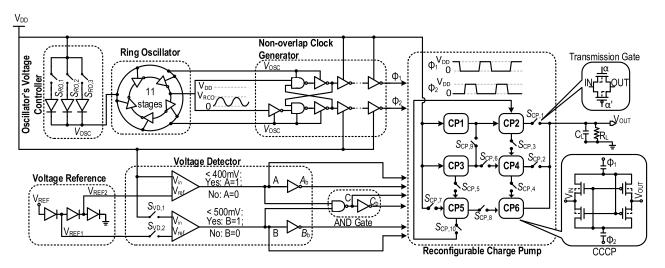

Acapacitive-based CMOS DC-DC boost converter, also called a charge pump (CP) plays an important role in energy harvesting (EH) applications to step up the input voltage to a higher voltage level suitable for load applications. The conventional CP block shown in Fig. 1 consists of an oscillator

The associate editor coordinating the review of this manuscript and approving it for publication was Agustin Leobardo Herrera-May<sup>(D)</sup>.

that generates clock signals to govern the pumping operation, a non-overlap clock (NOC) generator that converts the sinusoidal clock signals into two non-overlapping square waves [1], and the CP itself, which boosts the scavenged DC voltage to a usable level for the load [2].

Cross-coupled charge pump (CCCP) [3], [4], [5], [6], [7], [8] and Dickson CP [9] are the two conventional CP topologies in vogue for EH applications. In low input voltage applications, switch-based CCCP is preferred over diode-based

FIGURE 1. The basic block diagram of a conventional charge pump.

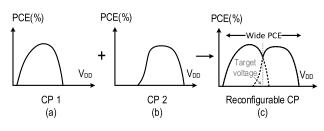

FIGURE 2. The PCE vs input voltage curve of (a) individual CP1 (b) individual CP2 (c) reconfigurable CP by combining CP1 and CP2.

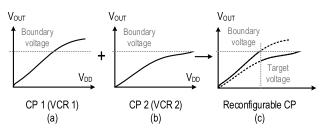

**FIGURE 3.** The output voltage of (a) individual CP1 (b) individual CP2 (c) reconfigurable CP by combining CP1 and CP2.

Dickson CP as the diode-based Dickson topology suffers from high V<sub>TH</sub> conduction loss. On the other hand, Dickson CP has an advantage in high input voltage applications due to its minimal reversion loss. To reduce the conduction loss, some studies have incorporated low voltage threshold (LVT) devices to enhance the performance of charge pumps in subthreshold operation [4], [8], [10]. Nevertheless, the attempt to minimize conduction loss entails a compromise of increased reversion loss, which negatively impacts the charge pump's overall performance. Over the past few decades, a wide range of techniques for improving CP performance has been documented in the literature [2], [11], [12], [13], [14], [15], [16], aimed at addressing the aforementioned challenges. Despite significant research focused on optimizing CP topologies, there remains potential for further innovation in architectural improvements.

In energy harvesting applications, the input voltage of the CP varies due to the fluctuation in the harvested power, which is an external influence on the system. For instance, weather conditions can have an impact on the harvesting of solar energy, while the harvesting of kinetic energy can be affected by factors such as humans. There are several problems accommodated with a wide input voltage range CP. Firstly, their power conversion efficiency (PCE) cannot remain high over a wide input voltage range, as it depends on the CP topology. Additionally, the frequency generated by the oscillator is influenced by the input voltage. Therefore, a wide

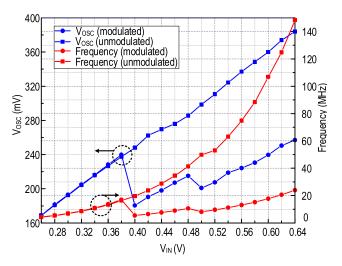

FIGURE 4. Plots of the relationship between input voltage, oscillator source voltage and the modulated and unmodulated oscillating frequencies.

input voltage range would cause the oscillator to produce a broad frequency range, which would further degrade the CP's performance. Furthermore, a high input voltage would result in a highly boosted output voltage, which can cause voltage overstress on the operating transistors, as well as cause output load breakdown. This effect is more pronounced in circuits designed for low voltage performance, where devices with low voltage overstress thresholds such as LVT devices or short gate length transistors are used [17], [18].

Some of the recent EH CP works [3], [4], [5], [19] proposed charge pumps that lack consideration in the oscillator circuit; instead, two non-overlapping clocks with a stable frequency are supplied by a function generator to model the generated clock signals from the oscillator for pumping. This is important to evaluate the CP's performance, especially for EH applications [6], [7] that have a fluctuating input voltage. Furthermore, the unstable frequency generated from the fluctuating input voltage will affect the CP's performance. The work in [7] provides constant 10 MHz clock signals to its reconfigurable CP despite having an input voltage ranging from 0.45 V to 0.75 V. Another work in [6] reveals the high power loss caused by the high frequency from increasing input voltage. Yet, the work used external trimming to suppress the increasing oscillation frequency. Some works incorporated a proper frequency modulation technique in the reconfigurable CP, such as the variable delay stages configuration from [20] and the dynamic delay block's sources from [21] and [22]. However, these frequency modulation techniques lead to some performance hindrances, which will be discussed later in this paper.

The previously mentioned issues highlight the need for a reconfigurable CP. Hence, this work proposed a reconfigurable CP that exploits the low effective resistance in the parallel CP to reduce the forward conduction loss and the high voltage conversion ratio (VCR) of the series CP for subthreshold operation wide input voltage energy harvester.

FIGURE 5. Top architecture of the proposed series-parallel reconfigurable CP.

TABLE 1. Control logic high signal for stage reconfigurable CP.

| V <sub>DD</sub> State                                         | S <sub>CP,1</sub> | S <sub>CP,2</sub> | S <sub>CP,3</sub> | S <sub>CP,4</sub> | S <sub>CP,5</sub> | S <sub>CP,6</sub> | S <sub>CP,7</sub> | S <sub>CP,8</sub> | S <sub>CP,9</sub> | S <sub>CP,10</sub> | S <sub>VD,1</sub> | S <sub>VD,2</sub> | S <sub>RO,1</sub> | S <sub>RO,2</sub> | S <sub>RO,3</sub> |

|---------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| $V_{DD} < 0.4 V$                                              | 1                 | 1                 | 0                 | 0                 | 0                 | 1                 | 1                 | 1                 | 0                 | 0                  | 1                 | 1                 | 0                 | 0                 | 1                 |

| $0.4\mathrm{V} \leq \mathrm{V}_{\mathrm{DD}} < 0.5\mathrm{V}$ | 0                 | 1                 | 1                 | 0                 | 1                 | 0                 | 0                 | 1                 | 0                 | 0                  | 1                 | 1                 | 0                 | 1                 | 0                 |

| $V_{DD} \ge 0.5V$                                             | 0                 | 0                 | 1                 | 1                 | 0                 | 0                 | 1                 | 0                 | 1                 | 1                  | 0                 | 0                 | 1                 | 0                 | 0                 |

| Control HIGH<br>Signal                                        | С                 | Ab                | Cb                | A                 | В                 | С                 | Bb                | Ab                | A                 | A                  | Ab                | Ab                | A                 | В                 | С                 |

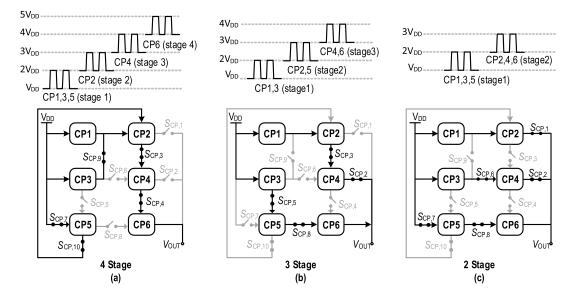

By configuring the six-stage parallel CP into 4 stages, 3 stages, and 2 stages, the proposed reconfigurable CP limits the output voltage under 1.8 V while attaining high efficiency in a low input voltage range.

In this study, we address the issue of unstable frequency resulting from fluctuating input and present an innovative frequency modulation approach by employing a dynamic source-fed oscillator. This technique can suppress the high generated clock frequency during high input voltage to reduce the switching loss effect in the CP. Moreover, the proposed technique incorporates an independent source for the oscillator and the clock-generating unit, allowing for the provision of a high-amplitude clock signal from the input voltage to the CP while limiting the source voltage of the oscillator.

The rest of this paper is organized as follows. Section II reviews the conventional reconfigurable CPs. Section III discusses the design methodology of reconfigurable CP. Section IV describes the operation of the proposed reconfigurable CP. Section V details the operation principle of a clock generation unit in the CP, and the proposed dynamic source-fed oscillator. Section VI presents the measurement results and the performance comparison. Section VII concludes the work.

#### **II. CONVENTIONAL RECONFIGURABLE CP**

The main objective of a reconfigurable CP is to enhance the efficiency and control the VCR to limit the output voltage.

Reference [23] introduces a power-efficient reconfigurable CP that configures between linear CP and Fibonacci CP in high voltage and low voltage ranges respectively. However, the work only concentrates on achieving maximum efficiency, without taking into account the need to limit  $V_{OUT}$  to prevent transistor overstress and load breakdown.

An adaptive VCR reconfigurable CP was implemented in [24], capable of switching between 1, 2, and 3 stages to achieve maximum efficiency, but the diode-based design restricts its use in low voltage energy harvesting applications. Reference [25] introduces a circuit with a reconfigurable soft transition VCR, but it is for step-down CP. Reference [22] proposed a hybrid Dickson and Cockcroft-Walton CP capable of configuring between 4 and 6 stages. Despite having multiple VCRs, the work only tested at a narrow input voltage range of 0.9, 1, and 1.1 V. Similarly [26] proposed a reconfigurable CP with VCRs of 2 and 3 while [27] proposed a stage selection CP that can configure between 1 to 3 stages. However, these CPs were only tested on the high input voltage ranges. Besides limiting the output voltage with adaptive VCR, [27] also included transistor electrical overstress and gate-oxide unreliability consideration in the design for the 1.8V/3.3V CMOS process. Reference [19] presents an intriguing output voltage regulation by utilizing the trans-conductive loop implemented through the bulk terminal of the PMOS transistor in CCCP. The work, however, ignored the impact of variable frequency in a wide input

#### TABLE 2. Truth table for reconfigurable CP's control signals.

| Scenario | V <sub>DD</sub> State          | No. stage | Α | Ab | B | Bb | C | Cb |

|----------|--------------------------------|-----------|---|----|---|----|---|----|

| III      | $V_{\rm DD} \ge 0.5 V$         | 2 stages  | 0 | 1  | 0 | 1  | 1 | 0  |

| II       | $0.4 V \le V_{\rm DD} < 0.5 V$ | 3 stages  | 0 | 1  | 1 | 0  | 0 | 1  |

| Ι        | $V_{\rm DD} < 0.4 ~V$          | 4 stages  | 1 | 0  | 0 | 1  | 0 | 1  |

| -        | -                              | -         | 1 | 0  | 1 | 0  | х | х  |

FIGURE 6. Proposed reconfigurable CP (a) scenario I, 4 stages (b) scenario II, 3 stages (c) scenario III, 2 stages.

**FIGURE 7.** Proposed oscillator's voltage controller unit's (a) schematic diagram and (b) equivalent resistant model.

voltage range as it only provides a constant 1MHz clocking frequency in the design throughout the input voltage range.

Another method of changing the VCR is by controlling the clock amplitude of the CP. Reference [7] implemented a clock amplitude reducer to reduce the VCR by half in addition to a reconfigurable CCCP capable of switching between 2 and 4 stages. Reference [21] introduces a novel self-oscillating CP where a different level of source voltages is supplied to the CP to achieve an adaptive VCR. Although the self-oscillating CP does not necessitate the use of an oscillator, this frequency of the self-oscillating charge pump cannot be independently adjusted, so an external frequency modulation block is needed.

FIGURE 8. Block diagram of a non-overlap clock generator. The size of inverters in the buffer represents the transistors' width.

Frequency modulation is important in wide input reconfigurable CP as the high switching loss caused by high oscillating frequency will deteriorate the CP performance. However, it is often overlooked in the past reconfigurable CP works. Reference [28] proposed a subtraction-mode CP that can tolerate high switching frequency loss with frequency in the range of 60 MHz and 100 MHz, but the frequency range is too small in wide input energy harvesting applications. This can be seen in Fig. 4, where the frequency of an oscillator can rise by 100 MHz from a 0.4 V input increment. Reference [20] implemented frequency modulation to his 9 stages CP at which each stage can be deactivated using a stage control block. The frequency modulation is achieved using variable delay cell configuration which will induce high power consumption. The details of power consumption in the frequency modulation technique will be discussed in Section V.

#### III. RECONFIGURABLE CP DESIGN METHODOLOGY

The first step of designing a reconfigurable CP is to individually design the CP for each voltage range. The performance of each CP topology is identified and optimized individually in a way that each CP has a peak performance at a separate input voltage range as depicted in Fig. 2. The determination of the target voltage, at which the CP reconfigures, is based on the intersection of the CPs' PCE curve as illustrated in Fig. 2(c) [29], [30], and [31]. Similarly, to design a reconfigurable CP with an adaptive VCR that limits a bounded output voltage [25], each CP is first individually designed to identify the correlation between VCR and output voltage (V<sub>OUT</sub>). The target voltage for the reconfiguration to occur is determined when the V<sub>OUT</sub> of the CP with higher VCR exceeds the boundary voltage as depicted in Fig. 3. The boundary voltage is selected based on the application, depending on the load breakdown voltage and the transistor's operating point. Next is to develop the control algorithm for the reconfigurable CP. A comparison of the structure of each CP is carried out to determine the number of switches needed for the reconfiguration process. Subsequently, the state of each switch in the various configurations is identified. The third step of the reconfigurable CP design process involves developing a control circuit to implement the algorithm designed in the previous step. The control circuit is composed of a series of logic gates that generate the necessary control signals to activate the switches for the CP reconfiguration process.

The voltage detector is implemented to detect the target voltage where the reconfiguration occurs. There are a few approaches to implementing the voltage detector. A closed-loop system detects the output voltage level to achieve CP reconfiguration [24], [32] whereas an open-loop system detects the input voltage [26]. The closed-loop system offers the benefit of high stability and precise control, whereas the open-loop circuit is simpler to design and has lower power consumption due to its less complex circuitry. The selection of a closed-loop or open-loop system for reconfigurable charge pump design is dependent on the specific application requirements.

Finally, the performance of the reconfigurable CP is tested and compared with the individual CP. Further optimization will be carried out to improve the reconfigurable CP performance.

#### **IV. PROPOSED RECONFIGURABLE CP**

#### A. PROPOSED SERIES-PARALLEL RECONFIGURABLE CP

The proposed CP scheme is shown in Fig. 5. The CCCP's VCR changes by reconfiguring the number of stages in series or parallel, respective to the input voltage ( $V_{DD}$ ). Three main circuit blocks define the scheme. First, the clock generation unit is used to provide two non-overlap clock signals with modulated frequency. The logic control unit provides the

control signals for the CP. Finally, the reconfigurable CP is responsible for output voltage boosting.

The reconfigurable CP consists of 6 individual CCCP which are capable of configuring into 4 stages, 3 stages, or 2 stages based on the detected input voltage. The CP configuration is achieved by controlling the transmission gates, SCP,1-10 which act as the control switches for the reconfigurable CP. The main advantage of using series-parallel reconfigurable CP is that each CP cell is fully in operation under all different input voltage scenarios. Moreover, parallel CP has a lower conduction loss due to its lower equivalent circuit resistance, contributing to a much lower power loss during the charge-transferring phase [33].

As shown in Fig. 6, the proposed CP has three operation modes. When the input voltage V<sub>DD</sub> from the EH source is below 0.4 V (VDD < 0.4 V), SCP,3,4,7,9,10 are turned ON while the remaining gates are turned OFF. Thus, the CP reconfigures to a 4-stage CP with a VCR of 5. In this configuration, CP1, CP3, and CP5 are connected in parallel in the first stage, boosting the voltage from  $V_{DD}$  to  $2V_{DD}$ ; followed by CP2 in the second stage, boosting voltage to 3V<sub>DD</sub>, CP4 in the third stage, and CP6 in the fourth stage as shown in Fig. 6(a). For V<sub>DD</sub> between 0.4V and 0.5V, SCP,2,3,5,8 are turned ON while the rest are turned OFF. The CP is then reconfigured into 3 stages with 2 parallel paths where CP1, CP2, and CP4 form the first CP path, and CP3, CP5, and CP6 form the second pumping path. Where CP1,3 boosts voltage from V<sub>DD</sub> to 2V<sub>DD</sub>; CP2,5 boosts 2V<sub>DD</sub> to  $3V_{DD}$  and CP4,6 boosts  $3V_{DD}$  to  $4V_{DD}$ . When  $V_{DD}$  is scenario above 0.5V ( $V_{DD} > 0.5$  V), SCP,1,2,6,7,8 are turned ON while the rest is OFF. The CP is reconfigured into 2 stages with 3 parallel paths. The first path is made of CP1 and CP2, the second is made of CP3 and CP4 and the last is made of CP5 and CP6. In this configuration, CP1,3,5 is the first CP stage; boosting V<sub>DD</sub> to 2V<sub>DD</sub> whereas CP2,4,6 is the second stage responsible for boosting  $2V_{DD}$  to  $3V_{DD}$ .

#### **B. LOGIC CONTROL UNIT**

The logic control unit is responsible for providing the control signals for controlling the CP configuration. Table 1 shows the breakdown of the control signal for each transmission gate where logic 1 represents the transmission gate being turned ON and logic 0 represents the switch turned OFF. From the table, it is evident that the circuit requires three distinct control signals (A, B, C) and their respective complementary signals (Ab, Bb, Cb) for the topology reconfiguration. For example, SCP,4,9,10 share the same logic signal of 0, 0, and 1 when CP is configured into 2, 3, and 4 stages, respectively. On the other hand, SCP,2,8 share the logic of 1, 1, and 0, which is the direct complement of the control signal A.

To provide the necessary control signals, a voltage detection unit of two Op-amp-based comparators is implemented to detect three voltage levels, below 0.4 V, between 0.4 V and 0.5 V, and beyond 0.5 V. This work adopted the comparator from [34] for voltage detection. Two reference voltages ( $V_{REF1}$ ,  $V_{REF2}$ ) are extracted from an external source

FIGURE 9. Photomicrograph of the proposed reconfigurable CP.

$(V_{REF})$  using diode-connected transistors which act as a voltage divider. The  $V_{REF}$  can be provided by a battery in a battery-assisted energy harvesting system. These reference voltages are then fed into the comparator in the voltage detection unit for voltage comparison.

The first comparator will compare  $V_{DD}$  with  $V_{REF2}$  of 0.4 V and return A = 1 if  $V_{DD}$  is smaller than the VREF2 and return A = 0 otherwise. As long as signal A is high,  $S_{VD,1}$  and  $S_{VD,2}$  will turn OFF to deactivate the second comparator to prevent unnecessary power consumption, this will also force signal B to remain low. When  $V_{DD}$  is larger than 0.4 V, signal A will be LOW, and the second comparator will be activated. It will compare  $V_{DD}$  with  $V_{REF1}$  of 0.5 V and return B = 1 if  $V_{DD}$  is less than  $V_{REF1}$  and return B = 0 if  $V_{DD}$  is larger than  $V_{REF1}$ .

The circuit can identify the three different input voltage ranges (below 0.4V, between 0.4 and 0.5V, and beyond 0.5V) by only using the two control signals generated from the comparators (signals A and B). However, signal A and signal B alone are not sufficient to control the CP configuration, as shown in Table 1. Therefore, an extra signal (C and Cb) is generated from signal A and signal B using an AND logic gate. The truth table of AND logic for signal C and Cb generation is described in Table 2. Using two comparators and an AND logic gate, six control signals covering all possible logic combinations can be generated.

This opens the possibility for future reconfigurable CP work which configure into a different number of stages.

#### **V. CLOCK GENERATION**

#### A. VOLTAGE-CONTROLLED RING OSCILLATOR

A ring voltage-controlled oscillator (RVCO) is a key block in the clock generation unit in the CP scheme to generate an oscillating clock signal [35], [36], [37], [38]. The generated oscillating frequency is dependent on the number of inverter cells and the delay time, as shown in the equation below [39] and [40]:

$$f_{OSC} = \frac{1}{2 \cdot N \cdot t_d} \tag{1}$$

where N represents the number of delay cell stages and  $t_d$  represents the delay time for each stage. The delay time depends

FIGURE 10. Measured performance of (a) PCE versus VIN (b) VCE versus V IN (c) V OUT versus V IN at various output load condition.

on the input voltage of the oscillator and the transistor size [6]. Since the input voltage of an oscillator varies according to

**FIGURE 11.** (a) Graph of PCE versus input current and (b) Graph of output voltage versus input current at various input voltage under 100k  $\Omega$  condition.

FIGURE 12. Post-layout PVT simulation of V  $_{OUT}$  at different input voltage at 100  $k \Omega.$

the circuit's input voltage ( $V_{DD}$ ), the output clock frequency range of the RVCO varies with  $V_{DD}$ . This effect is severe in EH applications where a wide input voltage range is common. In addition, high frequency increases switching losses in the charge pump. As the switching loss is inversely proportional to the conduction loss [41], it is important to regulate an optimal frequency for a balance point between the switching loss and the conduction loss for optimal CP performance.

The oscillating frequency can be reduced by increasing the number of delay cell stages or by reducing the oscillator's input voltage ( $V_{OSC}$ ). However, increasing the number of delay cell stages is not a suitable method for frequency regulation as it will increase the oscillator's power consumption, which can be discernible from the equation below [39]:

$$P_C = N \cdot f_{OSC} \cdot C_L \cdot V_{OSC}^2 \tag{2}$$

Although reducing  $V_{OSC}$  seems like a good approach to satisfy the reduction in the oscillating frequency and the power consumption at the same time, reducing  $V_{OSC}$  will also reduce the oscillating signal's output amplitude swing, which reduces the conduction of the CP. Generally, the amplitude of the CP's clock signals is the same as the oscillating signal's amplitude. Having a lower amplitude will greatly reduce the CP performance and its CR, due to the increase in the onresistance (R<sub>on</sub>) of the charge transfer transistors as described in the equation below [41], [42]:

$$R_{on} = \frac{1}{\mu C_{ox} \frac{W}{L} (V_{GS} - V_{TH})} \tag{3}$$

where  $\mu$  is the mobility of the electron/holes;  $C_{ox}$  is the oxide capacitance; W/L is the ratio of width to length of the transistor, and V<sub>GS</sub> is the gate-to-source voltage of the transistor which is equivalent to the clock amplitude.

As a countermeasure, a dynamic source-fed oscillator as a clock generation unit is proposed where a dynamic input voltage independent from the source voltage of the non-overlap clock is supplied for the oscillator. This is to achieve frequency regulation by changing  $V_{OSC}$  without affecting the output clock amplitude,  $V_{\Phi}$  which is discussed next.

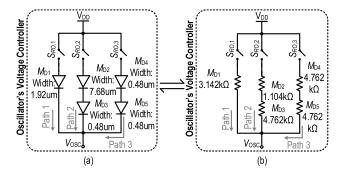

#### B. OSCILLATOR'S VOLTAGE CONTROLLER

The proposed clock generation unit consists of an oscillator's voltage controller (OVC), an RVCO, and a non-overlap clock (NOC) generator. The OVC is used to extract a lower voltage from  $V_{DD}$ , providing a dynamic input voltage for the RVCO. As depicted in Fig. 7, the OVC has three voltage divider paths with different effective resistances which can be activated using transmission gates SRO,1, SRO,2, and SRO,3 that are controlled through signals A, B, and C, respectively. In this work, the gate voltage for all transmission gates is derived from the V<sub>REF</sub> with an amplitude of 1.5 V.

Path 1 consists of a single large-size diode-connected NMOS with an effective resistance of 3.142 k $\Omega$ . Path 2 consists of two diode-connected transistors with a width of 7.68  $\mu$ m and 0.48  $\mu$ m, yielding a total effective resistance of 5.806 k $\Omega$ . Path 3 has the highest total effective resistance of 9.524 k $\Omega$  from the two small-sized transistors with a width of 0.48  $\mu$ m each.

The working principle is explained through 3 operational scenarios similar to Section II-B. In scenario I, as  $V_{DD}$  is low ( $V_{DD} < 0.4$  V), SRO,1 will be turned on to activate the first voltage divider path, which has a relatively lower effective resistance. The resistance in path 1 will reduce the  $V_{DD}$  from 0.26 V ~ 0.4 V to 269 mV ~ 240 mV, providing a lower VOSC for the oscillator. In scenario II, the second path will be activated with SRO,2 turned on. The 5.806 k $\Omega$

| Parameters                                | This work                           | [20]                         | [51]                         | [22]                                | [21]                             | [52]                                     | [7]                                                           |

|-------------------------------------------|-------------------------------------|------------------------------|------------------------------|-------------------------------------|----------------------------------|------------------------------------------|---------------------------------------------------------------|

| CMOS                                      | 65nm                                | 180nm                        | 130nm                        | 180nm                               | 180nm                            | 180nm                                    | 65nm*                                                         |

| No. of Stage                              | 2,3,4                               | 1~9                          | 4                            | 4~6                                 | 4                                | 4                                        | 2~4                                                           |

| Output Voltage<br>Regulation<br>Technique | Series-<br>Parallel CP              | Variable stage<br>selection  | Resistive voltage<br>divider | Variable stage selection            | Variable<br>cascaded<br>stage    | Fast-transient<br>dynamic<br>reconfigure | Variable stage<br>selection + clock<br>amplitude<br>reduction |

| Frequency<br>Modulation<br>Technique      | Dynamic<br>source-fed<br>oscillator | Variable delay<br>cell stage | Test register                | Dynamic voltage<br>for delay blocks | Dynamic voltage for delay blocks | TFM                                      | -                                                             |

| Input Voltage (V)                         | 0.26~<br>0.64                       | 0.25~<br>1.1                 | 0.27~<br>1.4                 | 1                                   | 1.2                              | 2                                        | 0.45 ~<br>0.7                                                 |

| Regulated<br>Voltage (V)                  | 1.8                                 | 1.8                          | 1.4                          | 3~6                                 | 2.2                              | 6~10                                     | 1.2 ~ 3                                                       |

| Frequency<br>(MHz)                        | 4.3~<br>24                          | 0.75~7.5                     | 0.6~1                        | 0.01~20                             | 70x10 <sup>-6</sup> ~<br>19      | -                                        | 10                                                            |

| Peak PCE (%)                              | 62                                  | 57                           | 58                           | 58                                  | 75                               | 69.8                                     | 73*                                                           |

| Area (mm <sup>2</sup> )                   | 0.346                               | -                            | 0.42                         | 0.5                                 | 0.069                            | 0.66                                     | 0.023**                                                       |

TABLE 3. Performance summary and the state-of-art comparison of the proposed circuit.

\*simulation result

\*\* oscillator not included

resistance from path 2 will decrease the VOSC to 180.5 mV  $\sim$  201 mV from V<sub>DD</sub> of 0.4 V  $\sim$  0.5 mV as depicted in Fig. 5. In scenario III, SRO,3 will turn on to activate the highest resistance path 3 (e.g., 9.524 k $\Omega$ ) to produce a V<sub>OSC</sub> of  $207 \text{ mV} \sim 257 \text{ mV}$ . By using the three voltage dividing paths, a stable  $V_{OSC}$  can be regulated for the RVCO to generate a modulated frequency.

This work adopted an RVCO from [43] for clock frequency generation which has a better performance compared to the conventional oscillator in subthreshold operation. However, instead of utilizing the supply at node V<sub>DD</sub>, this work uses V<sub>OSC</sub> generated from OVC earlier as the voltage supply node. V<sub>OSC</sub> is bounded from 169 mV to 257 mV using the control signals, A, B, and C. Thus, the frequency generated from the oscillator will also be maintained in the range of 4.3 MHz to 24 MHz, as depicted in Fig. 5. It is worth heeding that the unbounded VOSC would rise from 168 mV to 384 mV, causing the unmodulated frequency to surge from 4 MHz to 148 MHz as delineated in the same figure.

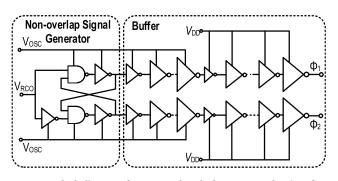

### C. NON-OVERLAP CLOCK GENERATOR

The non-overlap clock generator is an integration of two parts as shown in Fig. 8. The early part consists of two cross-connected NAND gates which are responsible for creating two non-overlapping signals for the CP pumping operation. The later part consists of a series of cascading inverters, forming a series of buffer that shapes the sinusoidal wave from RVCO into a square wave. The last few stages of inverters in the series of buffer takes V<sub>DD</sub> as the supply voltage instead of V<sub>OSC</sub>. This ensures the final output clock amplitude remains as V<sub>DD</sub>, independent from the lower amplitude VOSC of the RVCO.

**VI. MEASUREMENT RESULT**

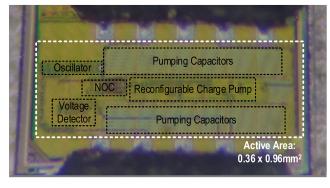

We implemented the proposed CP in 65-nm CMOS, adopting on-wafer probing for the chip with an active area of  $0.36 \times 0.96$  mm<sup>2</sup>, shown in the photomicrograph in Fig. 9. To optimize the performance in subthreshold operation [44], this work adopted low-voltage threshold (LVT) devices in all charge transfer transistors to elevate the forward conduction loss. Other circuit blocks, such as OVC and the comparator, utilize standard threshold (SVT) transistors. Each CP stage in the circuit utilizes two 20 pF metal-insulator-metal (MIM) capacitors for the charge pumping operation. Additionally, a 120 pF MIM capacitor is employed as the load capacitor to reduce the output voltage ripple and provide a smoother output voltage.

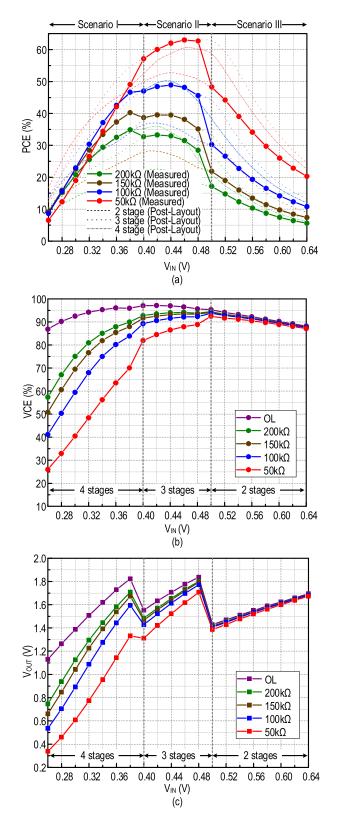

To evaluate the proposed system's performance, we measure the PCE and the system's voltage conversion efficiency (VCE) at different load conditions as portrayed in Fig. 10 (a) and (b). PCE is a metric used to measure the effectiveness of a power conversion system in converting input power to usable output power while VCE is a measure of how effectively a voltage conversion system converts input voltage to output voltage. The formula for PCE and VCE is given below:

$$PCE = \frac{P_{OUT}}{P_{IN}} \times 100\% \tag{4}$$

$$VCE = \frac{V_{OUT(measured)}}{V_{OUT(ideal)}} \times 100\%$$

(5)

In scenario I where  $V_{DD}$  < 0.4 V, the LVT device and the switch-connection parallel CP configuration allow the reconfigurable CP to achieve a high PCE in subthreshold operation. In scenario II, the CP is configured into 3 stages with 2 parallel paths which lowers its effective resistance to

allow a high PCE. The performance of the CP in scenario II is observed to be superior compared to scenario I as the transistors are not operating in the subthreshold region owing to the higher input voltage. The peak PCE is recorded in scenario II with 62 % at 0.48 V when driving 50 k $\Omega$  loads. In scenario III, the CP performance drops despite having three parallel pumping paths. This is because the CP is optimized for low input voltage operation. The CP suffers high reverse current leakage across the LVT transistors in high-voltage operations. Moreover, the utilization of a 2-stage CP leads to a circuit mismatch that results in an ineffective transfer of power to the output load. To limit the output voltage under 1.8 V for safeguarding the system, the CP performance is sacrificed in scenario III.

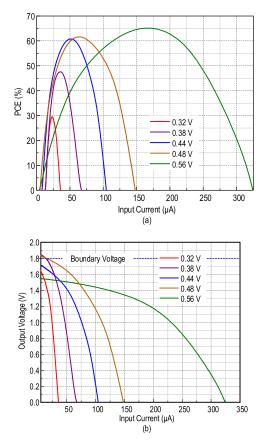

Fig. 10 (b) depicts the VCE of the proposed reconfigurable CP. It exhibits over 80% VCE at all voltage ranges, with a peak VCE of 97% recorded at open load conditions with 0.4 V input voltage. The proposed circuit successfully limits the output voltage under 1.8 V in all load conditions for an input voltage of 0.26 V to 0.64 V as shown in Fig.10(c). As the input voltage rises from 0.26 V to 0.4 V, the circuit is reconfigured into 3 stages, lowers its CR to 4, and decreases the V<sub>OUT</sub> under 1.8 V. The same phenomenon repeats itself at 0.5 V with the circuit configured into 2 stages, as illustrated in Fig. 10(c). This can prevent voltage overstress on the LVT devices used in the reconfigurable CCCP. The measured performance of the CP is provided in Fig. 11(a) as a function of the input current. From the figure, it can be observed that the peak PCE is shifted towards the right at a higher input voltage. In other words, lower stage configuration performs better with higher input current. The proposed CP is tested with various input currents up to a range of 325  $\mu$ A. Fig. 11(b) illustrates the relationship between the input current and output voltage of the proposed circuit. The figure demonstrates that the proposed circuit effectively maintains the output voltage within the boundary level for most input current levels, except when the input voltage is near the configuration switching points (0.48V and 0.38V). Nevertheless, the circuit is capable of maintaining the boundary voltage at the input current level as low as 15  $\mu$ A.

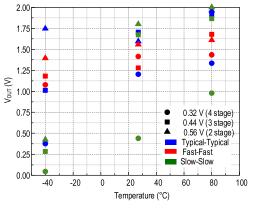

As depicted in Figure 12, the proposed circuit shows process variations of 17.66% (FF) and 63.4% (SS) for the 4-stage configuration at an input voltage of 0.32V. For the 3-stage and 2-stage configurations, the process variations are 24.88% (FF), 1.739% (SS), and 2.31% (FF), 12.86% (SS) respectively. Additionally, the circuit exhibits temperature variations of 68.7% (-40 °C) and 11% (80 °C) for the 4-stage configuration. The 3-stage configuration has temperature variations of 40.56% (-40 °C) and 12.3% (80 °C), while the 2-stage configuration has variations of 36.5% (-40 °C) and 19.9% (80 °C).

While the proposed circuit is effective in limiting the output voltage under 1.8V, it cannot regulate and maintain the output voltage level across the wide input voltage range. However, an auxiliary closed-loop regulation mechanism [19], [45], [46], [47], [48], [49], [50] can be implemented in conjunction

with the proposed circuit to maintain a consistent output voltage. In this configuration, the proposed circuit caps the output voltage, while the auxiliary closed-loop circuit finetunes and maintains the desired output voltage level.

Table 3 summarizes and compares the proposed system with the state-of-the-art reconfigurable CP. Reference [51] limits the output voltage under 1.4 V using an output feedback mechanism with a resistive voltage divider. This technique compares the output voltage with a bandgap reference voltage to adapt the division ratio of the resistive voltage divider for voltage regulation. As a consequence, the output will suffer in power losses for the voltage absorbed by the resistive voltage divider. The works in [20], [21], and [22] regulated the output voltage by varying the number of CP stages in operation in a way similar to the proposed work. However, the work deactivates the CP to reduce its pumping stage instead of connecting them in parallel. This technique fails to utilize the advantage of the low equivalent circuit resistance that is obtained by connecting multiple CPs in parallel, resulting in a potential loss of harvesting efficiency.

Concerning using the approach of frequency regulation, [20] used a variable delay cell configuration for frequency modulation. Such configuration comprises different stages of delay cells to generate the desired frequency. However, as described in equation (2), the high number of delay stages will increase the power consumption in the clock generation circuit. The works in [21] and [22] perform frequency modulation by varying the voltage source of the delay cell, similar to the proposed work. The difference is, that the work utilizes the output from the CP as the dynamic source for the delay stages. Nevertheless, the high boosted voltage from the CP output will result in a high-power loss in the delay cells.

Table 3 demonstrates that the proposed reconfigurable CP exhibits the highest PCE among other state-of-the-art reconfigurable CPs for low-voltage energy harvesting applications [20], [22], [51] which achieved a peak PCE of approximately 58%. Although [21] and [52] achieved a slightly higher PCE, it was at a higher input voltage. Additionally, [7] achieved a 73% PCE, but it was based on simulation results and did not consider the power consumption of the oscillator. Furthermore, the proposed work recorded the lowest circuit complexity, occupying a silicon area of only 0.346 mm2.

#### **VII. CONCLUSION**

This work proposed a series-parallel CP architecture, consisting of a novel dynamic source-fed oscillator, a logic control unit, and a reconfigurable CCCP for low voltage energy harvesting application. By arranging the CCCP into 4, 3, or 2 stages in series and parallel, the proposed CP modified its VCR to maintain the output voltage under 1.8 V. It leveraged the advantage of low effective resistance in a parallel CP topology to enhance the CP performance. Additionally, this work devised a novel dynamic source-fed oscillator for frequency regulation using a dynamic input voltage for the RVCO that enabled frequency modulation without affecting the clock's amplitude. Validated on 65-nm CMOS, the proposed architecture attained a 62% peak PCE and a 97% VCE performance with the lowest circuit complexity when compared with state-of-the-art reported designs.

#### REFERENCES

- B. Nowacki, N. Paulino, and J. Goes, "A simple 1 GHz non-overlapping two-phase clock generators for SC circuits," in *Proc. 20th Int. Conf. Mixed Design Integr. Circuits Syst. MIXDES*, Jun. 2013, pp. 174–178.

- [2] M.-K. Law, Y. Jiang, P.-I. Mak, and R. P. Martins, "Miniaturized energy harvesting systems using switched-capacitor DC–DC converters," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 6, pp. 2629–2634, Jun. 2022, doi: 10.1109/TCSII.2022.3168307.

- [3] A. Ballo, A. D. Grasso, and G. Palumbo, "A subthreshold crosscoupled hybrid charge pump for 50-mV cold-start," *IEEE Access*, vol. 8, pp. 188959–188969, 2020, doi: 10.1109/ACCESS.2020.3032452.

- [4] J. K. Yong, H. Ramiah, K. K. P. Churchill, G. Chong, S. Mekhilef, Y. Chen, P.-I. Mak, and R. P. Martins, "A 0.1-V VIN subthreshold 3-stage dual-branch charge pump with 43.4% peak power conversion efficiency using advanced dynamic gate-bias," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 9, pp. 3929–3933, Sep. 2022, doi: 10.1109/TCSII.2022.3182344.

- [5] A. Ballo, A. D. Grasso, and G. Palumbo, "Charge pump improvement for energy harvesting applications by node pre-charging," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 12, pp. 3312–3316, Dec. 2020, doi: 10.1109/TCSII.2020.2991241.

- [6] K. K. Pakkirisami Churchill, H. Ramiah, G. Chong, M. Y. Ahmad, J. Yin, P.-I. Mak, and R. P. Martins, "A 0.15-V, 44.73% PCE charge pump with CMOS differential ring-VCO for energy harvesting systems," *Anal. Integr. Circuits Signal Process.*, vol. 111, no. 1, pp. 35–43, Apr. 2022, doi: 10.1007/s10470-021-01980-2.

- [7] A. Ballo, A. D. Grasso, and G. Palumbo, "A memory-targeted dynamic reconfigurable charge pump to achieve a power consumption reduction in IoT nodes," *IEEE Access*, vol. 9, pp. 41958–41964, 2021, doi: 10.1109/ACCESS.2021.3065821.

- [8] J. K. Yong, H. Ramiah, P. C. K. Kumar, and G. Chong, "A 0.1 V input energy harvesting charge pump with dynamic gate biasing and capacitance scaling," in *Proc. IEEE Asia Pacific Conf. Circuit Syst. (APCCAS)*, Nov. 2021, pp. 129–132, doi: 10.1109/APCCAS51387.2021.9687765.

- [9] J. F. Dickson, "On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique," *IEEE J. Solid-State Circuits*, vol. SSC-11, no. 3, pp. 374–378, Jun. 1976, doi: 10.1109/JSSC.1976.1050739.

- [10] W. X. Lian, H. Ramiah, G. Chong, K. K. P. Churchill, N. S. Lai, S. Mekhilef, Y. Chen, P.-I. Mak, and R. P. Martins, "A fully-integrated CMOS dual-band RF energy harvesting front-end employing adaptive frequency selection," *IEEE Access*, vol. 11, pp. 74121–74135, 2023, doi: 10.1109/ACCESS.2023.3296145.

- [11] J.-T. Wu and K.-L. Chang, "MOS charge pumps for low-voltage operation," *IEEE J. Solid-State Circuits*, vol. 33, no. 4, pp. 592–597, Apr. 1998, doi: 10.1109/4.663564.

- [12] X. Jiang, X. Yu, K. Moez, D. G. Elliott, and J. Chen, "High-efficiency charge pumps for low-power on-chip applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 3, pp. 1143–1153, Mar. 2018, doi: 10.1109/TCSI.2017.2759767.

- [13] A. Ballo, A. D. Grasso, G. Palumbo, and T. Tanzawa, "A charge loss aware advanced model of Dickson voltage multipliers," *IEEE Access*, vol. 10, pp. 118082–118092, 2022, doi: 10.1109/ACCESS.2022.3218901.

- [14] S. S. Chouhan, M. Nurmi, and K. Halonen, "Efficiency enhanced voltage multiplier circuit for RF energy harvesting," *Microelectron. J.*, vol. 48, pp. 95–102, Feb. 2016, doi: 10.1016/j.mejo.2015.11.012.

- [15] S. S. Chouhan and K. Halonen, "A novel cascading scheme to improve the performance of voltage multiplier circuits," *Anal. Integr. Circuits Signal Process.*, vol. 84, no. 3, pp. 373–381, Sep. 2015, doi: 10.1007/s10470-015-0595-y.

- [16] M. M. Mnif, H. Mnif, and M. Loulou, "A dual frequency RF-DC rectifier circuit with a low input power for radio frequency energy harvesting," *J. Circuits, Syst. Comput.*, vol. 28, no. 3, Mar. 2019, Art. no. 1950048, doi: 10.1142/S0218126619500488.

- [17] P.-L. Peng, L.-W. Chu, M.-F. Tsai, Y.-T. Su, J.-W. Lee, K.-J. Chen, and M.-H. Song, "Low-capacitance SCR for on-chip ESD protection with high CDM tolerance in 7 nm bulk FinFET technology," in *Proc. 41st Annu. EOS/ESD Symp. (EOS/ESD)*, Sep. 2019, pp. 1–5, doi: 10.23919/EOS/ESD.2019.8869982.

- [18] C. H. Aw, "A low-power circuit architecture for transistor electrical overstress (EOS) protection," in *Proc. 5th Asia Symp. Quality Electron. Design* (ASQED), Aug. 2013, pp. 282–286, doi: 10.1109/ASQED.2013.6643601.

- [19] A. Ballo, A. D. Grasso, and G. Palumbo, "A bulk current regulation technique for dual-branch cross-coupled charge pumps," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 10, pp. 4128–4132, Oct. 2022, doi: 10.1109/TCSII.2022.3185525.

- [20] S. Carreon-Bautista, L. Huang, and E. Sanchez-Sinencio, "An autonomous energy harvesting power management unit with digital regulation for IoT applications," *IEEE J. Solid-State Circuits*, vol. 51, no. 6, pp. 1457–1474, Jun. 2016, doi: 10.1109/JSSC.2016.2545709.

- [21] W. Jung, S. Oh, S. Bang, Y. Lee, Z. Foo, G. Kim, Y. Zhang, D. Sylvester, and D. Blaauw, "An ultra-low power fully integrated energy harvester based on self-oscillating switched-capacitor voltage doubler," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 2800–2811, Dec. 2014, doi: 10.1109/JSSC.2014.2346788.

- [22] J.-H. Tsai, S.-A. Ko, H.-H. Wang, C.-W. Wang, H. Chen, and P.-C. Huang, "A 1 V input, 3-to-6 V output, integrated 58%-efficient charge-pump with hybrid topology and parasitic energy collection for 66% area reduction and 11% efficiency improvement," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2014, pp. 233–236, doi: 10.1109/ASSCC.2014.7008903.

- [23] A. K. Gupta, A. Joshi, V. Gajare, H. S. Ghanshyam, and A. Dutta, "Power efficient reconfigurable charge pump for micro scale energy harvesting," in *Proc. IEEE Asia Pacific Conf. Postgraduate Res. Microelectron. Electron. (PrimeAsia)*, Dec. 2013, pp. 73–76, doi: 10.1109/PrimeAsia.2013.6731181.

- [24] G. Palumbo, D. Pappalardo, and M. Gaibotti, "Charge pump with adaptive stages for non-volatile memories," *IEE Proc., Circuits, Devices Syst.*, vol. 153, no. 2, pp. 136–142, Apr. 2006, doi: 10.1049/ip-cds:20041235.

- [25] Y. Jiang, M.-K. Law, P.-I. Mak, and R. P. Martins, "Arithmetic progression switched-capacitor DC–DC converter topology with soft VCR transitions and quasi-symmetric two-phase charge delivery," *IEEE J. Solid-State Circuits*, vol. 57, no. 10, pp. 2919–2933, Oct. 2022, doi: 10.1109/JSSC.2022.3167704.

- [26] X. Zhang and H. Lee, "An efficiency-enhanced auto-reconfigurable 2×/3× SC charge pump for transcutaneous power transmission," *IEEE J. Solid-State Circuits*, vol. 45, no. 9, pp. 1906–1922, Sep. 2010, doi: 10.1109/JSSC.2010.2055370.

- [27] Z. Luo, L.-C. Yu, and M.-D. Ker, "An efficient, wide-output, high-voltage charge pump with a stage selection circuit realized in a low-voltage CMOS process," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 9, pp. 3437–3444, Sep. 2019, doi: 10.1109/TCSI.2019.2924581.

- [28] J. Jiang, X. Liu, C. Huang, W.-H. Ki, P. K. T. Mok, and Y. Lu, "Subtractionmode switched-capacitor converters with parasitic loss reduction," *IEEE Trans. Power Electron.*, vol. 35, no. 2, pp. 1200–1204, Feb. 2020, doi: 10.1109/TPEL.2019.2933623.

- [29] A. Choo, Y. C. Lee, H. Ramiah, Y. Chen, P.-I. Mak, and R. P. Martins, "A high-PCE range-extension CMOS rectifier employing advanced topology amalgamation technique for ambient RF energy harvesting," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, early access, Jun. 14, 2023, doi: 10.1109/TCSII.2023.3285977.

- [30] A. Choo, H. Ramiah, K. K. P. Churchill, Y. Chen, S. Mekhilef, P.-I. Mak, and R. P. Martins, "A high-performance dual-topology CMOS rectifier with 19.5-dB power dynamic range for RF-based hybrid energy harvesting," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 31, no. 8, pp. 1253–1257, Aug. 2023, doi: 10.1109/TVLSI.2023.3261263.

- [31] A. Choo, H. Ramiah, K. K. P. Churchill, Y. Chen, S. Mekhilef, P.-I. Mak, and R. P. Martins, "A reconfigurable CMOS rectifier with 14-dB power dynamic range achieving >36-dB/mm<sup>2</sup> FoM for RF-based hybrid energy harvesting," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 30, no. 10, pp. 1533–1537, Oct. 2022, doi: 10.1109/TVLSI.2022.3189697.

- [32] H.-C. Cheng, P.-H. Chen, Y.-T. Su, and P.-H. Chen, "A reconfigurable capacitive power converter with capacitance redistribution for indoor light-powered batteryless Internet-of-Things devices," *IEEE J. Solid-State Circuits*, vol. 56, no. 10, pp. 2934–2942, Oct. 2021, doi: 10.1109/JSSC.2021.3075217.

- [33] Q. R. R. Flores and F-V. G. Espinosa, "Efficiency comparison of charge pump DC/DC configurations for energy harvesting," in *Proc. 7th Int. Conf. Modern Circuits Syst. Technol. (MOCAST)*, May 2018, pp. 1–4, doi: 10.1109/MOCAST.2018.8376635.

- [34] P. W. Yuen, G. Chong, and H. Ramiah, "A high efficient dual-output rectifier for piezoelectric energy harvesting," *AEU, Int. J. Electron. Commun.*, vol. 111, Nov. 2019, Art. no. 152922, doi: 10.1016/j.aeue.2019.152922.

- [35] P. Shasidharan, H. Ramiah, and J. Rajendran, "A 2.2 to 2.9 GHz complementary class-C VCO with PMOS tail-current source feedback achieving—120 dBc/Hz phase noise at 1 MHz offset," *IEEE Access*, vol. 7, pp. 91325–91336, 2019, doi: 10.1109/ACCESS.2019.2927031.

- [36] C. C. Lim, H. Ramiah, J. Yin, N. Kumar, P.-I. Mak, and R. P. Martins, "A 5.1-to-7.3 mW, 2.4-to-5 GHz class-C mode-switching single-endedcomplementary VCO achieving >190 dBc/Hz FoM," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 2, pp. 237–241, Feb. 2019, doi: 10.1109/TCSII.2018.2848301.

- [37] C. C. Lim, H. Ramiah, J. Yin, P.-I. Mak, and R. P. Martins, "An inverseclass-F CMOS oscillator with intrinsic-high-Q first harmonic and second harmonic resonances," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3528–3539, Dec. 2018, doi: 10.1109/JSSC.2018.2875099.

- [38] Y. Chen, P.-I. Mak, and R. P. Martins, "High-performance harmonicrich single-core VCO with multi-LC tank: A tutorial," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 7, pp. 3115–3121, Jul. 2022, doi: 10.1109/TCSII.2022.3180351.

- [39] K. K. Pakkirisami Churchill, H. Ramiah, G. Chong, Y. Chen, P.-I. Mak, and R. P. Martins, "A fully-integrated ambient RF energy harvesting system with 423-μW output power," *Sensors*, vol. 22, no. 12, p. 4415, Jun. 2022, doi: 10.3390/s22124415.

- [40] T. S. Ho, H. Ramiah, K. K. P. Churchill, Y. Chen, C. C. Lim, N. S. Lai, P.-I. Mak, and R. P. Martins, "Low voltage switched-capacitivebased reconfigurable charge pumps for energy harvesting systems: An overview," *IEEE Access*, vol. 10, pp. 126910–126930, 2022, doi: 10.1109/ACCESS.2022.3226783.

- [41] K. K. Pakkirisami Churchill, G. Chong, H. Ramiah, M. Y. Ahmad, and J. Rajendran, "Low-voltage capacitive-based step-up DC–DC converters for RF energy harvesting system: A review," *IEEE Access*, vol. 8, pp. 186393–186407, 2020, doi: 10.1109/ACCESS.2020.3028856.

- [42] T. S. Chang, H. Ramiah, Y. Jiang, C. C. Lim, N. S. Lai, P.-I. Mak, and R. P. Martins, "Design and implementation of hybrid DC–DC converter: A review," *IEEE Access*, vol. 11, pp. 30498–30514, 2023, doi: 10.1109/ACCESS.2023.3261337.

- [43] S. Bose, T. Anand, and M. L. Johnston, "Integrated cold start of a boost converter at 57 mV using cross-coupled complementary charge pumps and ultra-low-voltage ring oscillator," *IEEE J. Solid-State Circuits*, vol. 54, no. 10, pp. 2867–2878, Oct. 2019, doi: 10.1109/JSSC.2019.2930911.

- [44] G. Chong, H. Ramiah, J. Yin, J. Rajendran, W. R. Wong, P.-I. Mak, and R. P. Martins, "CMOS cross-coupled differential-drive rectifier in subthreshold operation for ambient RF energy harvesting—Model and analysis," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 12, pp. 1942–1946, Dec. 2019, doi: 10.1109/TCSII.2019.2895659.

- [45] H.-C. Cheng, W.-Y. Tsai, P.-H. Chen, and P.-H. Chen, "Fully-integrated reconfigurable charge pump with two-dimensional frequency modulation for self-powered Internet-of-Things applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 11, pp. 4132–4141, Nov. 2020, doi: 10.1109/TCSI.2020.3012504.

- [46] X. Liu, L. Huang, K. Ravichandran, and E. Sánchez-Sinencio, "A highly efficient reconfigurable charge pump energy harvester with wide harvesting range and two-dimensional MPPT for Internet of Things," *IEEE J. Solid-State Circuits*, vol. 51, no. 5, pp. 1302–1312, May 2016, doi: 10.1109/JSSC.2016.2525822.

- [47] X. Liu and E. Sánchez-Sinencio, "An 86% efficiency 12 μW selfsustaining PV energy harvesting system with hysteresis regulation and time-domain MPPT for IoT smart nodes," *IEEE J. Solid-State Circuits*, vol. 50, no. 6, pp. 1424–1437, Jun. 2015, doi: 10.1109/JSSC.2015.2418712.

- [48] O.-Y. Wong and P.-H. Chen, "Fully integrated voltage doubler with dualmode three-dimensional load regulation for on-chip photovoltaic-powered applications," *IEEE Trans. Power Electron.*, vol. 34, no. 2, pp. 1481–1491, Feb. 2019, doi: 10.1109/TPEL.2018.2833881.

- [49] T. Y. Chyan, H. Ramiah, S. F. W. M. Hatta, N. S. Lai, C.-C. Lim, Y. Chen, P.-I. Mak, and R. P. Martins, "Evaluation and perspective of analog low-dropout voltage regulators: A review," *IEEE Access*, vol. 10, pp. 114469–114489, 2022, doi: 10.1109/ACCESS.2022.3217919.

- [50] M. H. Loo, H. Ramiah, K.-M. Lei, C. C. Lim, N. S. Lai, P.-I. Mak, and R. P. Martins, "Fully-integrated timers for ultra-low-power Internetof-Things nodes—Fundamentals and design techniques," *IEEE Access*, vol. 10, pp. 65936–65950, 2022, doi: 10.1109/ACCESS.2022.3183995.

- [51] Y.-C. Shih and B. P. Otis, "An inductorless DC–DC converter for energy harvesting with a 1.2-μW bandgap-referenced output controller," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 58, no. 12, pp. 832–836, Dec. 2011, doi: 10.1109/TCSII.2011.2173967.

[52] M. W. Kim and J. J. Kim, "Energy-efficient fast-transient dynamic reconfigurable charge pump for multi-channel electrical stimulation," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 70, no. 6, pp. 2146–2150, Jun. 2023, doi: 10.1109/TCSII.2022.3228871.

**YONG JACK KEE** (Student Member, IEEE) was born in Selangor, Malaysia. He received the B.E. degree (Hons.) in electronic and computer engineering from Universiti Teknikal Malaysia Melaka, in 2020. He is currently pursuing the Ph.D. degree with the Department of Electrical Engineering, University of Malaya, Kuala Lumpur, Malaysia. His main research interests include the design of energy harvesting circuits in CMOS silicon technology for the Internet of

Things (IoT), analog/RF integrated circuit design, power management ICs, and WSN.

**HARIKRISHNAN RAMIAH** (Senior Member, IEEE) received the B.Eng. (Hons.), M.Sc., and Ph.D. degrees in electrical and electronic engineering (analog and digital IC design) from Universiti Sains Malaysia, Penang, Malaysia, in 2000, 2003, and 2008, respectively.

In 2002, he was with Intel Technology Sdn. Bhd., Penang, where he performed high-frequency signal integrity analysis. In 2003, he was with Sires Labs Sdn. Bhd., Cyberjaya. He is currently a Pro-

fessor with the Department of Electrical Engineering, University of Malaya, Kuala Lumpur, Malaysia, involved in the area of RF integrated circuit (RFIC) and RF energy harvesting circuit design. He is also the Director of the Center of Research Industry 4.0 (CRI 4.0), University of Malaya. He has authored or coauthored several articles in technical publications. His main research interests include analog-integrated circuit design, RFIC design, VLSI system design, and radio frequency energy harvesting power management module design.

Prof. Ramiah is a member of the Institute of Electronics, Information, and Communication Engineers. He was a recipient of the Intel Fellowship Grant Award, from 2000 to 2008. He has received continuous international research funding in recognition of his work, from 2014 to 2021, such as the Motorola Foundation Grant. He is a Chartered Engineer of the Institute of Electrical Technology and a Professional Engineer registered under the Board of Engineers Malaysia.

#### **KISHORE KUMAR PAKKIRISAMI CHURCHILL**

(Member, IEEE) was born in Thanjavur, India. He received the B.E. degree in electronics and communication engineering and the M.E. degree in VLSI design from Anna University, Chennai, in 2010 and 2012, respectively. He is currently pursuing the Ph.D. degree with the Department of Electrical Engineering, University of Malaya, Kuala Lumpur, Malaysia. His research interests include micro energy harvesting, analog/RF

integrated circuit design, VLSI system design, power management ICs, and WSN.

**GABRIEL CHONG** (Member, IEEE) received the B.Eng. degree (Hons.) in electrical and electronics engineering from the Asia Pacific University of Technology and Innovation, Kuala Lumpur, Malaysia, in 2016, and the Ph.D. degree from the University of Malaya, Malaysia. He joined Nexperia in 2020. He is currently with Nexperia Research and Development Penang, Bayan Lepas, Malaysia, as an Analog IC Designer. His research interests include the design of energy harvesting circuits in

CMOS silicon technology for the Internet of Things (IoT) and the Internet of Everything (IoE) application.

**YONG CHEN** (Senior Member, IEEE) received the B.Eng. degree in electronic and information engineering from the Communication University of China (CUC), Beijing, China, in 2005, and the Ph.D. (Eng.) degree in microelectronics and solid-state electronics from the Institute of Microelectronics, Chinese Academy of Sciences (IMECAS), Beijing, in 2010.

From 2010 to 2013, he was a Postdoctoral Researcher with the Institute of Microelectronics,

Tsinghua University, Beijing. From 2013 to 2016, he was a Research Fellow at VIRTUS/EEE, Nanyang Technological University, Singapore. In 2016, he joined the State Key Laboratory of Analog and Mixed-Signal VLSI (AMSV), University of Macau, Macau, China, where he is currently an Associate Professor. His research interests include integrated circuit designs involving analog/mixed-signal/RF/mm-wave/sub-THz/wireline. He was a recipient of the second prize in "Haixi" (three places across the Straits) Postgraduate Integrated Circuit Design Competition, in 2009. He was a co-recipient of the Best Paper Award from the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), in 2019; the Best Student Paper Award (Third Place) from the IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, in 2021; the Macao Science and Technology Invention Award (First Prize), in 2020; and the Macao Science and Technology Invention Award (Second Prize) in 2022. He was recognized as the top five associate editors, in 2020, the five highest-performing associate editors, in 2021, one of the three best associate editors, in 2022, and one of the three best reviewers, in 2022, of IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS. He has been serving as an Associate Editor for IEEE TVLSI Systems, since 2019, a Subject Editor for Circuits and Systems, since 2022, an Associate Editor for IET Electronics Letters (EL), since 2020, and an Editor for International Journal of Circuit Theory and Applications (IJCTA), since 2020. He has served as a Guest Editor for IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: REGULAR PAPERS, in 2022, and IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS, in 2021, and an Associate Editor for IEEE Access, from 2019 to 2021. He served as the Vice-Chair (from 2019 to 2021) and the Chair (from 2021 to 2023) for the IEEE Macau Circuit and System (CAS) Chapter, the Tutorial Chair for the International Conference on Circuits and Systems (ICCS), in 2020, the Special Session Co-Chair for APCCAS, in 2022, and a conference local organization committee of Asian Solid-State Circuits Conference (A-SSCC), in 2019. He has been serving as a member of the IEEE Circuits and Systems Society, Circuits and Systems for Communications (CASCOM) Technical Committee, since 2020, the Technical Program Committee (TPC) of A-SSCC, since 2021, APCCAS, from 2019 to 2022, the International Conference on Integrated Circuits, Technologies and Applications (ICTA), since 2020, Nordic Circuits and Systems Conference (NorCAS), since 2020, IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), since 2022, International Conference on Electronics Circuits and Systems (ICECS), since 2021, and International Conference on Solid-State and Integrated Circuit Technology (ICSICT), in 2020 and 2022; a Review Committee Member for International Symposium on Circuits and Systems (ISCAS), since 2021; and the TPC Co-Chair for ICCS, from 2021 to 2022.

**SAAD MEKHILEF** (Fellow, IEEE) is currently a Distinguished Professor with the School of Science, Computing and Engineering Technologies, Swinburne University of Technology, Melbourne, VIC, Australia, and an Honorary Professor with the Department of Electrical Engineering, University of Malaya. He is actively involved in industrial consultancy for major corporations in the power electronics and renewable energy projects. He has authored or coauthored more than 500 publications

in academic journals and proceedings, five books with more than 33,000 citations, and more than 70 Ph.D. students graduated under the supervision. His current research interests include power converter topologies, the control of power converters, maximum power point tracking (MPPT), renewable energy, and energy efficiency.

He has been listed by Thomson Reuters (Clarivate Analytics) as one of the Highly Cited (Hi.Ci) Engineering Researchers in the world, in 2018, 2019, 2020, and 2021. He is serving as an Editorial Board Member for many top journals, such as IEEE TRANSACTIONS ON POWER ELECTRONICS, IEEE OPEN JOURNAL OF THE INDUSTRIAL ELECTRONICS SOCIETY, *IET Renewable Power Generation, Journal of Power Electronics*, and *International Journal of Circuit Theory and Applications*.

**NAI SHYAN LAI** received the B.Eng. degree (Hons.) in electrical engineering and the Ph.D. degree in silicon-based nanoelectronics and radiation detectors from the University of New South Wales, in 2007 and 2012, respectively. He is currently an Associate Professor with the School of Engineering, Asia Pacific University of Technology and Innovation, involved in the area of micro- and nano-electronics. Since 2009, he has been publishing most of the research work in

the IEEE TRANSACTIONS, the American Institute of Physics, the American Physical Society, and Nature Group journals. His research interests include semiconductor micro- and nano-fabrication, quantum dot devices, cryogenic temperature measurements, single electron transistors, quantum computation, and silicon microdosimeters.

**PUI-IN MAK** (Fellow, IEEE) received the Ph.D. degree from the University of Macau (UM), Macao, China, in 2006.

He is currently a Professor with the UM Faculty of Science and Technology–ECE, the Interim Director of the UM State Key Laboratory of Analog and Mixed-Signal VLSI, and the Deputy Director (Research) of the Institute of Microelectronics. His research interests include analog and radio frequency (RF) circuits and systems for wire-

less and multidisciplinary innovations.

Prof. Mak is a fellow of the Institution of Engineering and Technology (IET) and the U.K. Royal Society of Chemistry (RSC). He is/was the TPC Vice Co-Chair of ASP-DAC, in 2016, a TPC Member of A-SSCC, from 2013 to 2016, ESSCIRC, from 2016 to 2017, and ISSCC, from 2017 to 2019. He (co)-received the 2021 RFIC Best Student Paper Award, the 2005 DAC/ISSCC Student Paper Award, the 2010 CASS Outstanding Young Author Award, the 2011 National Scientific and Technological Progress Award, the Best Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS, from 2012 to 2013, the 2015 A-SSCC Distinguished Design Award, and the 2016 ISSCC Silkroad Award. In 2005, he was decorated with the Honorary Title of Value by the Macau Government. He was the Chairperson of the Distinguished Lecturer Program of IEEE Circuits and Systems Society, from 2018 to 2019. Since 2018, he has been inducted as an Overseas Expert of the Chinese Academy of Sciences. His involvements with IEEE are: an Editorial Board Member of IEEE Press, from 2014 to 2016; a Member of Board-of-Governors of IEEE Circuits and Systems Society, from 2009 to 2011; a Senior Editor of IEEE JOURNAL ON EMERGING AND SELECTED TOPICS IN CIRCUITS AND SYSTEMS. from 2014 to 2015; an Associate Editor of IEEE JOURNAL OF SOLID-STATE CIRCUITS in 2018, the IEEE SOLID-STATE CIRCUITS LETTERS in 2017, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: REGULAR PAPERS, from 2010 to 2011 and from 2014 to 2015, and IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS, from 2010 to 2013. He is/was a Distinguished Lecturer of IEEE Circuits and Systems Society, from 2014 to 2015, and the IEEE Solid-State Circuits Society, from 2017 to 2018.

**RUI P. MARTINS** (Life Fellow, IEEE) was born in April 1957. He received the bachelor's, master's, and Ph.D. degrees, as well as the Habilitation to Full Professor in electrical engineering and computers from the Department of Electrical Engineering and Computers, Instituto Superior Técnico (IST), University of Lisbon, Portugal, in 1980, 1985, 1992, and 2001, respectively.

He has been with the DECE/IST, University of Lisbon since October 1980. Since October 1992,

he has been on leave with the University of Lisbon and the Department of Electrical and Computer Engineering, Faculty of Science and Technology (FST), University of Macau (UM), Macau, China, where he has been the Chair Professor, since August 2013. In FST, he was the Dean, from 1994 to 1997, and has been UM's Vice-Rector, since September 1997. From September 2008 to August 2018, he was a Vice-Rector (Research). From September 2018 to August 2023, he was a Vice-Rector (Global Affairs). Within the scope of the teaching and research activities he has taught 21 bachelor's and master's courses in UM, he has supervised or co-supervised 47 theses, Ph.D. (26), and master's (21). He has authored or coauthored a total of 896 publications: nine books and 12 book chapters; 50 Patents, USA (39), China (eight), and Taiwan (three); 745 papers, in scientific journals (331), and conference proceedings (414); as well as other 80 academic works (H-index = 46/citations = 10,000+, Google Scholar). He created in 2003 the Analog and Mixed-Signal VLSI Research Laboratory, UM, elevated, in January 2011, the State Key Laboratory (SKLAB) of China (the 1st in engineering in Macau), being its Founding Director.

Prof. Martins was the Founding Chair of the IEEE Macau Section, from 2003 to 2005, and IEEE Macau Joint-Chapter on Circuits And Systems (CAS)/Communications (COM), from 2005 to 2008 [2009 World Chapter of the Year of IEEE CAS Society (CASS)], the General Chair IEEE Asia-Pacific Conference on CAS-APCCAS'2008, the Vice-President (VP) Region 10 (Asia, Australia, and Pacific), from 2009 to 2011, and the VP-World Regional Activities and Membership of IEEE CASS, from 2012 to 2013, an Associate-Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS, from 2010 to 2013, nominated Best Associate Editor, from 2012 to 2013. He was the Chair of UMTEC (UM Company), from January 2009 to March 2019, supporting the incubation and creation, in 2018, Digifluidic, the first UM Spin-Off, whose CEO is a SKLAB Ph.D. graduate. He was also the Co-Founder of Chipidea Microelectronics (Macau) [later Synopsys-Macao, and Akrostar, where the CEO was the Ph.D. Student, with double-degree FST-UM/IST-UTL], in 2001/2002. He has been a member of the Advisory Board of the Journal of Semiconductors of the Chinese Institute of Electronics (CIE), Institute of Semiconductors, Chinese Academy of Sciences, since January 2021, and a fellow of the Asia-Pacific Artificial Intelligent Association, since October 2021. He was also a member of: IEEE CASS Fellow Evaluation Committee (Member: 2013, 2014, and 2019; Chair: 2018; Vice-Chair: 2021 and 2022); the IEEE Nominating Committee of Division I Director (CASS/EDS/SSCS), in 2014; and the IEEE CASS Nominations Committee, from 2016 to 2017. In addition, he was the General Chair of the ACM/IEEE Asia South Pacific Design Automation Conference-ASP-DAC'2016, receiving the IEEE Council on Electronic Design Automation (CEDA) Outstanding Service Award, in 2016, and the IEEE Asian Solid-State Circuits Conference-A-SSCC 2019. He was the Vice-President, from 2005 to 2014, the President, from 2014 to 2017, and the Vice-President, from 2021 to 2024, of the Association of Portuguese Speaking Universities (AULP). In September 2021, he was nominated Honorary Member of AULP (honor only bestowed on five people in the world). He also received three Macao Government decorations: the Medal of Professional Merit (Portuguese-1999); the Honorary Title of Value (Chinese-2001), and the Medal of Merit in Education (Chinese 2021). He has been a member of the Advisory Board of the Journal of Semiconductors of the Chinese Institute of Electronics (CIE), Institute of Semiconductors, Chinese Academy of Sciences, since January 2021, and a fellow of the Asia-Pacific Artificial Intelligent Association, since October 2021. Since July 2010, he has been elected, unanimously, to the Lisbon Academy of Sciences, as a Corresponding (from 2010 to 2022) and an Effective Member (since 2022), being the only Portuguese Academician working and living in Asia.

...