Received 12 June 2023, accepted 29 June 2023, date of publication 5 July 2023, date of current version 17 July 2023. Digital Object Identifier 10.1109/ACCESS.2023.3292346

## Accurate Layout-Dependent Effect Model in 10 nm-Class DRAM Process Using Area-Efficient Array Test Circuits

# SEYOUNG KIM<sup>®1,2</sup>, SEUNGHO YANG<sup>®2</sup>, HYEIN LIM<sup>2</sup>, HYEIN LEE<sup>2</sup>, JONGWOOK JEON<sup>®3</sup>, JUNG YUN CHOI<sup>2</sup>, AND JAEHA KIM<sup>®1</sup>, (Senior Member, IEEE)

<sup>1</sup>Department of Electrical and Computer Engineering, Inter-University Semiconductor Research Center, Seoul National University, Seoul 08826, South Korea <sup>2</sup>Memory Business Division, Samsung Electronics, Hwaseong 18448, South Korea

<sup>3</sup>Department of Electrical and Electronics Engineering, Konkuk University, Seoul 05029, South Korea

Corresponding author: Jaeha Kim (jaeha@snu.ac.kr)

This work was supported in part by the National Research Foundation of Korea (NRF) Grant funded by the Korean Government [Ministry of Science and ICT (MSIT)] under Grant 2020R1A4A4079177.

**ABSTRACT** This study presents an accurate model for non-monotonic layout-dependent effects (LDEs) measured using 10nm-class dynamic random access memory technology. To collect the LDE measurement data, a test module with an individually addressable array of 240 transistors has been developed. The proposed test module occupies a small area of 0.1 square millimeters with a density 15 times higher than that of typical scribe-line circuits. The proposed model employs a novel empirical function to precisely describe the non-monotonic dependence on each pair of geometrical parameters, such as the diffusion lengths, lateral/vertical spacings to the adjacent shallow trench isolations, and gate-to-contact distances. Additionally, this model can be easily realized as a sub-circuit model in standard circuit simulators, requiring only two additional tuning parameters for the core transistor. The fitted model demonstrates excellent agreement with the measured values obtained from test modules (802 transistors in total), achieving mean absolute errors of 0.7% for the drain current in the saturation region and 4.7 mV for the threshold voltage.

**INDEX TERMS** Addressable array circuit, layout-dependent effects, dynamic random-access memory, scribe lines, shallow trench isolation.

## **I. INTRODUCTION**

Layout-dependent effects (LDEs) refer to the change in the electrical performance of a transistor caused by the layout of the surrounding structures in an integrated circuit (IC) [1]. LDEs result in unintended failures in ICs unless they are properly accounted for during circuit simulations [2], [3]. Thus, it is crucial to characterize their behavior depending on technologies to achieve the desired power and performance of ICs [4]. For example, one primary cause of LDEs is the stress on the transistor channel imposed by the shallow trench isolation (STI) [5], which can lead up to a 20% variation in the transistor drain current in deep submicron CMOS

The associate editor coordinating the review of this manuscript and approving it for publication was Norbert Herencsar<sup>10</sup>.

processes [6]. Although there exist layout techniques such as dummy fill insertion that can mitigate LDEs to some degree [7], layout optimization for logic gates [8], [9], [10], [11], [12] and placement techniques [13], obtaining an accurate model that can predict LDEs is crucial for optimizing circuit performance and avoiding design respins.

The studies for LDE models for circuit simulation [3], [14], [15], [16] were largely initiated by Pelgrom's seminal work on matching transistors [17], highlighting the significance of acknowledging LDEs in analog/mixed-signal circuits [18] and SRAM circuits [19] designed in deep-submicron technologies. In the early stages, the LDE research was devoted to analyzing the physical causes of these effects, such as mechanically-induced stress caused by the isolation dielectrics such as STIs [5], [6] and inter-layer

dielectrics (ILD) [20]. Other contributors including well proximity [21] were subsequently discovered to be critical. The BSIM4(-CMG) model, which accounts for these LDEs [6], [16], [22], [23], [24], has been used as the golden reference in many integrated device manufacturers (IDMs) and electronic design automation (EDA) industry. Recently, attention has been turned to novel LDEs in advanced deep submicron CMOS technologies, such as high-k metal gate (HKMG) [10], [25] and FinFET [26], [27] processes, raising the concerns on LDEs as the technology scales further [9], [28], [29], [30], [31]. The physical mechanisms underlying these effects are complex with high degrees of interdependencies, and it is particularly challenging to maintain high accuracy of the physics-based models across multiple process generations [1]. Especially, the LDEs beyond 10-nm DRAM technologies have not been well studied and a majority of IDMs rely on their own proprietary models, which tend to be relatively simplistic, describing only the monotonic and symmetric changes with respect to the layout parameters.

However, in deeply-scaled IC technologies such as the current 10nm-class DRAM technologies, LDEs may not be a monotonic function of the geometrical parameters, such as the diffusion lengths, spacings to the adjacent STIs, and gate-to-contact distances [28]. The currently-available LDE models [6], [22], [24], [28] cannot accurately express their non-monotonic dependencies as they only use monotonic functions such as the inverse of a first-order polynomial. Characterizing the non-monotonic dependencies in experimental measurements also presents a challenge because it requires a large number of test transistors spanning the multi-dimensional space of the geometry parameters.

To address these challenges, this study presents an area-efficient test module for measuring the LDEs in 10nm-class DRAM technology and proposes a novel, empirical model that can accurately capture the non-monotonic characteristics of the LDEs. The proposed test module uses an SRAM-like addressable array to contain as many as 240 transistors within a small area of the scribe line [32], [33]. The proposed LDE model uses a simple basis function that adds an exponential factor to the previously used monotonic function, and it can fit the measured LDE data with a mean absolute error (MAE) of 0.7% for the drain current in the saturation region (Idsat) and 4.7 mV for the threshold voltage (Vth). This LDE model can be easily incorporated into current industry-standard models and provide accurate predictions on the LDEs for the layouts of various analog and digital peripheral circuits in DRAMs.

#### II. PROPOSED MODEL AND TEST STRUCTURE

### A. DEFINITION OF LAYOUT PARAMETERS

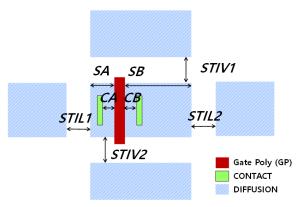

As illustrated in Fig. 1, we define the layout shape of a transistor including the surrounding geometry using eight parameters: i) *SA* and *SB* denote the diffusion lengths in the left and right directions, respectively; ii) *STIL*1 and *STIL*2 denote the lateral spaces between STIs; iii) *STIV*1 and

FIGURE 1. Schematic of a transistor device-under-test (DUT) structure and definition of the surrounding layout parameters used in the proposed model.

STIV2 denote the vertical spaces between STIs; iv) CA and CB denote the left and right gate-to-contact distances, respectively. We characterize the performance variation caused by these eight geometrical parameters considering the transistor performance based on the threshold voltage shift  $\Delta Vth$  and drain current shift  $\Delta I dsat$ .

## B. PROPOSED NON-MONOTONIC LDE MODEL

This study aims to obtain an empirical model for a pair of layout parameters for each pair of side directions. This model should also account for both symmetric and asymmetric layouts; therefore, we utilize two empirical functions for the symmetric and asymmetric cases. To smoothly approximate non-monotonic behaviors, we introduce a novel basis function that multiplies an exponential term  $e^{-1/x}$ , which rapidly varies while the parameter *x* is small and becomes constant elsewhere, to the conventional reciprocal function 1/x. For the symmetric case in which a pair of layout parameters (i.e.,  $x_1$  and  $x_2$ ) vary together, the contributions of the symmetric variation are defined by the function:

$$S(x_1, x_2) = e^{-1/(a(x_1 + x_2 + b))} \times \frac{d}{(x_1 + x_2 + c)}, \qquad (1)$$

where *a*, *b*, *c*, and *d* are the fitting parameters used to accurately fit the measured data.

For the asymmetric case, the function describing only the asymmetric variation in the layout is

$$A(x_1, x_2) = 2\beta (n^2 - \frac{1}{4}) (\frac{n(x_1 + x_2)}{n(x_1 + x_2) + x_1 - x_2} + \frac{n(x_1 + x_2)}{n(x_1 + x_2) - (x_1 - x_2)} - 2),$$

(2)

where  $\beta$  and *n* are fitting parameters. Notably, this equation is empirically derived such that  $A(x_1, x_2) = 0$  when  $x_1 = x_2$  and  $A(x_1, x_2) = 1$  when  $x_1 = 0$  or  $x_2 = 0$ . Therefore,  $A(x_1, x_2)$  is non-zero only for an asymmetric layout. By combining (1) and (2), we can model LDEs for the layout shown in Fig. 1 as follows:

$$F(x_1, x_2) = S(x_1, x_2) + S(x_1, x_2) \times A(x_1, x_2).$$

(3)

We use (3) to represent *Vth* and *Idsat* variations as follows:

$$\Delta Vth(x_1, x_2) = F^{Vth}(x_1, x_2) - F^{Vth}(x_1', x_2'), \qquad (4)$$

$$\Delta Idsat(x_1, x_2) = F^{Idsat}(x_1, x_2) - F^{Idsat}(x_1', x_2').$$

(5)

Here,  $x'_1$  and  $x'_2$  denote the reference layout parameters used in core model extraction, and the functions in (4) and (5) become zero when  $x_1 = x'_1$  and  $x_2 = x'_2$ . Each  $\Delta Vth(x_1, x_2)$  value in (4) and each  $\Delta I dsat(x_1, x_2)$  value in (5) have six fitting parameters: *a*, *b*, *c*, *d*,  $\beta$ , and *n*.

The proposed non-monotonic LDE model considers the variations in channel length *L* and width *W* by employing a binning method similar to that used in the BSIM model [34]. For example, for the upper and lower values of  $L_1$  and  $L_2$  in a bin range of  $L_1 < L < L_2$ ,  $\Delta Vth(x_1, x_2)$  can be obtained for each parameter of the sets  $[a, b, c, d, \beta, n]_{L=L_1}$  and  $[a, b, c, d, \beta, n]_{L=L_2}$ . For clarity, we denote these values as  $\Delta Vth_{L_1}(x_1, x_2)$  and  $\Delta Vth_{L_2}(x_1, x_2)$ . Then, the intermediate variation for  $\Delta Vth$  within the range  $L_1 < L < L_2$  can be represented as follows:

$$\Delta Vth_{final}(x_1, x_2, L) = \Delta Vth_0(x_1, x_2) + \frac{\Delta Vth_l}{L}, \qquad (6)$$

$$\Delta Idsat_{final}(x_1, x_2, L) = \Delta Idsat_0(x_1, x_2) + \frac{\Delta Idsat_l}{L}, \quad (7)$$

where the function introduced in (6) and (7) is expressed as follows:

$$\Delta Vth_0(x_1, x_2) = \frac{\Delta Vth_{L_2}(x_1, x_2)/L_1 - \Delta Vth_{L_1}/L_2}{(L_1^{-1} - L_2^{-1})^{-1}}, \quad (8)$$

$$\Delta Vth_l(x_1, x_2) = \frac{\Delta Vth_{L_2}(x_1, x_2) - \Delta Vth_{L_1}(x_1, x_2)}{L^{-1} - L^{-1}}, \quad (9)$$

$$\Delta Idsat_0(x_1, x_2) = \frac{\Delta Idsat_{L_2}(x_1, x_2)/L_1^2 - \Delta Idsat_{L_1}/L_2}{(L_1^{-1} - L_2^{-1})^{-1}},$$

(10)

$$\Delta Idsat_l(x_1, x_2) = \frac{\Delta Idsat_{L_2}(x_1, x_2) - \Delta Idsat_{L_1}(x_1, x_2)}{L_1^{-1} - L_2^{-1}}.$$

(10)

The width W variation can be represented similarly by applying the same binning method and formula that is adjusted for W instead of L.

#### C. ADDRESSABLE ARRAY TEST CIRCUIT

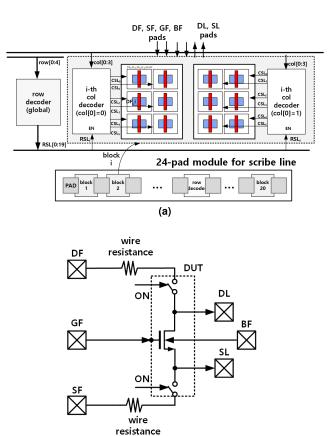

The test devices were located in an addressable array circuit, as shown in Fig. 2. The transistors to be measured can be chosen by their row and column addresses. The voltages were applied to the four terminals of the transistor (i.e., the gate, drain, source, and bulk). DUT cells were placed in the space between each pair of probe pads along the row, and the switching circuits were placed under the probe pads. A unit module with 24 pads is generally used in the DRAM

FIGURE 2. Schematic of a part of the addressable array test structures in the scribe lines. (a) Addressable array circuit concept in the scribe-line pad module. (b) Ohmic IR drop compensation technique in each DUT cell.

(b)

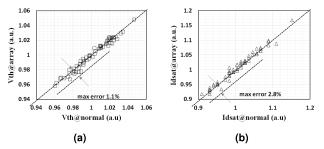

FIGURE 3. Comparison between measurements obtained by the addressable array test and ordinary measurements for the normal threshold voltage n-type MOSFETs (63 data points). The threshold voltages (left) and drive currents (right) were measured using both testing methods.

process; however, only 17 pads were utilized for the proposed array circuit, including five pads for row address, four pads for column address, four pads to force voltage to the gate, drain, source, and bulk nodes, two pads to sense the voltage of the drain and source nodes, and power and ground pads of the address circuits (VDDA, VSSA). In this study, we set the supply voltage at the VDDA pad to 2.0V during the measurements. The remaining pads are utilized by directly connecting to drain and source ports of DUTs in the array circuits for comparing the measurement accuracy. As shown in Fig. 2, the unit array circuit has 20 blocks of circuits with

| TABLE 1. Description of the LDE parameters. L and W denote the length       |

|-----------------------------------------------------------------------------|

| and width of the transistor, respectively. # of points indicates the number |

| of sweep points required to measure each parameter.                         |

| Parameter | Description              | # of L | # of W | # of points |

|-----------|--------------------------|--------|--------|-------------|

| SA(B)     | Diffusion length         | 3      | 2      | 12-18       |

| STIL1(2)  | Lateral space            | 3      | 2      | 12-18       |

| STIV1(2)  | Vertical space           | 3      | 2      | 12-18       |

| CA(B)     | Gate-to-contact distance | 3      | 2      | 6           |

a pair of column decoder circuits and a single-unit DUT cell containing 12 transistors between a pair of switching circuits at both sides.

We measured *Vth* and *Idsat* for the test devices using a test algorithm that can compensate for the voltage drop and leakage current. The switching circuit used for compensating the ohmic IR voltage drop is shown in Fig. 2. The voltage drop occurs owing to the wire resistance depending on the distance from the probe pad to the selected DUT cell. This can be compensated for by iterating the force voltage at the DF node (i.e., V(DF)), as shown in Fig. 2 (b). While iteratively increasing the value of V(DF) until the voltage reaches the desired value (e.g., VDD), the test program measures the voltage near the drain port of the transistor V(DL) and if it equals the desired drain supply voltage, then it stops the current iteration and repeats the same procedure by selecting another transistor located at the next address.

Since a large number of transistors share the same pad, it is necessary to cancel the leakage contributions from the off-state transistors when measuring the current of one specific transistor. To do so, the test algorithm makes two measurements on the drain current and computes the difference. The first measurement is made with V(DF), V(DL), and V(GF) set to the desired voltages, and the second measurement is made with V(GF) forced to 0. This can effectively cancel the leakage contributions from the off-state transistors.

The accuracy of the addressable array test was validated through comparisons with ordinary pad structures, as shown in Fig. 3. The linear relationship between the *Vth* and *Idsat* data measured using ordinary and array-type test circuits validated the accuracy of the addressable array technique. The maximum observed errors were only 1.1% for *Vth* and 2.8% for *Idsat*.

## D. PARAMETER EXTRACTION

We extracted the LDE from  $\Delta Vth$  and  $\Delta Idsat$  independently. The entire sequence used to extract the LDE model parameters is summarized in the following four steps:

- Step 1: Extract *a*, *b*, *c*, and *d* in (1) from  $\Delta Vth$  data of the symmetric layout.

- Step 2: Extract  $\beta$  and *n* in (2) from  $\Delta Vth$  data of the asymmetric layout.

- Step 3: Extract a, b, c, and d in (1) from  $\Delta I dsat$  data of the symmetric layout.

- Step 4: Extract  $\beta$  and *n* in (2) from  $\Delta I dsat$  data of the asymmetric layout.

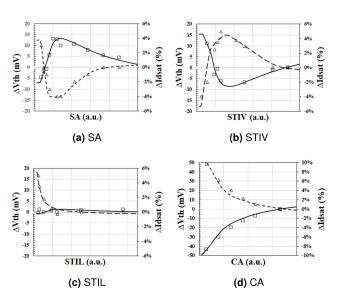

**FIGURE 4.** Comparisons between the experimental data and proposed models for four symmetric cases (squares:  $\Delta Vth$  data; triangles:  $\Delta Idsat$  data; lines: model).

## **III. EXPERIMENTAL RESULTS**

We experimentally demonstrated the proposed LDE model by implementing an array test circuit in a 10nm-class DRAM process. Thirteen modules were fabricated, each containing 240 DUTs. All 3120 transistors with different device types and geometries were implemented in scribe lines in the form of an addressable array circuit and 802 transistors were fitted for characterizing STI-related LDEs. The combinations of each parameter tested in the circuits are summarized in Table 1. The supply voltages for the row and column address pads were set to 3 V to ignore the voltage drop in the NMOS switch connected to the DUTs. The drain voltages were swept in the range of 0 to 1.2 V. Before fabrication, all pad module designs were validated using circuit simulations for IR drop compensation. The proposed LDE model accounting for  $\Delta I dsat$  and  $\Delta V th$  is realized as a sub-circuit model in the HSPICE<sup>™</sup>circuit simulator [35]. The sub-circuit model contains a core model parameter as an instance of BSIM4, and the variations of Vth and Idsat can be easily added using the built-in current scaling parameter mulid0 and threshold voltage shifting parameter delvtho.  $\Delta I dsat$  is converted by the ratio  $(\Delta I dsat + I dsat0)/Id0$  to the original drain current value Idsat0 extracted from the corresponding circuit simulation.

Fig. 4 shows a comparison between the measurement and proposed models for the sample case of symmetric layouts (e.g., SA = SB) for three cases of LDEs: SA(SB),  $STIL1(\cdot 2)$ ,  $STIV1(\cdot 2)$ , and CA(CB). It should be noted that each transistor used in Fig. 4 is different because the scope of this study is not to discuss the physical aspects of LDEs but to show the accuracy of the proposed model for capturing the non-monotonic nature including the asymmetric variation of the LDE parameters. For the other cases not shown in

Error (%)

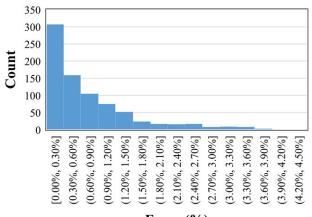

**FIGURE 5.** Error histogram of  $\triangle I dsat$  for 802 transistors.

**FIGURE 6.** Comparisons of *Idsat* between the measurements and proposed model for *SA*(*B*), *STIV*1(2), and *STIL*1(2) (green symbols: data for symmetric cases; triangular symbols:  $\triangle Idsat$  data for symmetric cases; surface: model).

this paper, the proposed model can fit the data with small errors owing to the use of six additional fitting parameters. Our proposed model accurately matched the measured data by capturing the inflection points that originate from the non-monotonic nature of the measurement data. The MAEs were 0.7% for *Idsat* and 4.7 mV for *Vth*. The error histogram for *Idsat* is shown in Fig. 5. Note that errors for *Vth* are not included because most  $\Delta Vth$  data (over 700 points) do not sufficiently show clear trends for parameter extraction.

As shown in Fig. 5, our model describes the LDEs for the asymmetric parameter variations for (*SA*,*SB*), (*STIL*1,*STIL*2), and (*STIV*1,*STIV*2). The surface shows the proposed model, and the green symbols indicate the measured data for the asymmetric cases, which agree with each other. The accuracy

of this modeling methodology should be investigated in future studies using circuit simulations because most transistors in practical chip implementations are surrounded by asymmetrically shaped STIs rather than symmetrically shaped STIs.

## **IV. CONCLUSION**

This study developed a model that can describe the nonmonotonic, asymmetric dependences of LDEs on layout parameters, which are pronounced in 10nm-class DRAM processes. This was achieved by proposing a general yet sophisticated formula to describe the non-monotonic LDE characteristics obtained by simultaneously observing various physical factors influencing the LDE by implementing large-scale test structures in the form of addressable arrays. Moreover, the proposed model accounted for the asymmetric layout parameter variations. The proposed model can provide accurate predictions on the changes in transistor characteristics owing to the layout shapes, yet it is simple enough to be included in the industry-standard compact models, such as BSIM. The presented LDE model and characterization methodology can help optimize the circuit layout designs for 10nm-class DRAM processes and beyond. Although this work demonstrated the effectiveness of the proposed model only with describing the STI-dependent effects, we believe it can be further extended to other LDEs such as well-proximity effects and metal-gate proximity effects, while covering the wider range of layout geometries as well.

## ACKNOWLEDGMENT

The EDA tool was supported by the IC Design Education Center (IDEC), South Korea.

#### REFERENCES

- C. C. McAndrew, "Compact models for MOS transistors: Successes and challenges," *IEEE Trans. Electron Devices*, vol. 66, no. 1, pp. 12–18, Jan. 2019.

- [2] S. Borkar, "Designing reliable systems from unreliable components: The challenges of transistor variability and degradation," *IEEE Micro*, vol. 25, no. 6, pp. 10–16, Nov. 2005.

- [3] P. G. Drennan, M. L. Kniffin, and D. R. Locascio, "Implications of proximity effects for analog design," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2006, pp. 169–176.

- [4] M. Horowitz, E. Alon, D. Patil, S. Naffziger, R. Kumar, and K. Bernstein, "Scaling, power, and the future of CMOS," in *IEDM Tech. Dig.*, Dec. 2005, pp. 9–15.

- [5] G. Scott, J. Lutze, M. Rubin, F. Nouri, and M. Manley, "NMOS drive current reduction caused by transistor layout and trench isolation induced stress," in *IEDM Tech. Dig.*, Dec. 1999, pp. 827–830.

- [6] R. A. Bianchi, G. Bouche, and O. Roux-dit-Buisson, "Accurate modeling of trench isolation induced mechanical stress effects on MOSFET electrical performance," in *IEDM Tech. Dig.*, Dec. 2002, pp. 117–120.

- [7] A. B. Kahng, P. Sharma, and R. O. Topaloglu, "Chip optimization through STI-stress-aware placement perturbations and fill insertion," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 27, no. 7, pp. 1241–1252, Jul. 2008.

- [8] Y. Xiao, M. A. Trefzer, S. Roy, J. A. Walker, S. J. Bale, and A. M. Tyrrell, "Circuit optimization using device layout motifs," in *Proc. 5th Eur. Work-shop CMOS Variability (VARI)*, Sep. 2014, pp. 1–6.

- [9] Y. Gu, H. Lu, X. Zhang, M. Lin, X. Zou, and W. Wong, "A study of LDE on stdcell device performance in advance FinFET technology," in *Proc. 14th IEEE Int. Conf. Solid-State Integr. Circuit Technol. (ICSICT)*, Oct. 2018, pp. 1–3.

- [10] X. Zhang, J. Li, M. Grubbs, M. Deal, B. Magyari-Köpe, B. M. Clemens, and Y. Nishi, "Physical model of the impact of metal grain work function variability on emerging dual metal gate MOSFETs and its implication for SRAM reliability," in *IEDM Tech. Dig.*, Dec. 2009, pp. 1–4.

- [11] H. Aikawa, E. Morifuji, T. Sanuki, T. Sawada, S. Kyoh, A. Sakata, M. Ohta, H. Yoshimura, T. Nakayama, M. Iwai, and F. Matsuoka, "Variability aware modeling and characterization in standard cell in 45 nm CMOS with stress enhancement technique," in *Proc. Symp. VLSI Technol.*, Jun. 2008, pp. 90–91.

- [12] X. Dong and L. Zhang, "EA-based LDE-aware fast analog layout retargeting with device abstraction," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 27, no. 4, pp. 854–863, Apr. 2019.

- [13] H. Ou, K. Tseng, J. Liu, I. Wu, and Y. Chang, "Layout-dependent effectsaware analytical analog placement," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 35, no. 8, pp. 1243–1254, Aug. 2016.

- [14] M. Conti, P. Crippa, S. Orcioni, and C. Turchetti, "Layout-based statistical modeling for the prediction of the matching properties of MOS transistors," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 49, no. 5, pp. 680–685, May 2002.

- [15] C.-C. Wang, W. Zhao, F. Liu, M. Chen, and Y. Cao, "Modeling of layout-dependent stress effect in CMOS design," in *IEEE/ACM Int. Conf. Comput.-Aided Design-Dig. Tech. Papers*, Nov. 2009, pp. 513–520.

- [16] B. Peddenpohl, M. Otrokov, and J. Wells, "Validation of the BSIM4 irregular LOD SPICE model by characterization of various irregular LOD test structures," in *Proc. IEEE Int. Conf. Microelectron. Test Struct. (ICMTS)*, Mar. 2018, pp. 31–34.

- [17] M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers, "Matching properties of MOS transistors," *IEEE J. Solid-State Circuits*, vol. 24, no. 5, pp. 1433–1439, Oct. 1989.

- [18] A. L. S. Loke, D. Yang, T. T. Wee, J. L. Holland, P. Isakanian, K. Rim, S. Yang, J. S. Schneider, G. Nallapati, S. Dundigal, H. Lakdawala, B. Amelifard, C. Lee, B. McGovern, P. S. Holdaway, X. Kong, and B. M. Leary, "Analog/mixed-signal design challenges in 7-nm CMOS and beyond," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2018, pp. 1–8.

- [19] R. W. Mann, T. B. Hook, P. T. Nguyen, and B. H. Calhoun, "Nonrandom device mismatch considerations in nanoscale SRAM," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 20, no. 7, pp. 1211–1220, Jul. 2012.

- [20] T.-K. Yu, S. Chheda, J. Ko, M. Roberton, A. Dengi, and E. Travis, "A two-dimensional low pass filter model for die-level topography variation resulting from chemical mechanical polishing of ILD films," in *IEDM Tech. Dig.*, Dec. 1999, pp. 909–912.

- [21] Y.-M. Sheu, K.-W. Su, S.-J. Yang, H.-T. Chen, C.-C. Wang, M.-J. Chen, and S. Liu, "Modeling well edge proximity effect on highly-scaled MOSFETs," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2005, pp. 826–829.

- [22] K.-W. Su, Y.-M. Sheu, C.-K. Lin, S.-J. Yang, W.-J. Liang, X. Xi, C.-S. Chiang, J.-K. Her, Y.-T. Chia, C. H. Diaz, and C. Hu, "A scaleable model for STI mechanical stress effect on layout dependence of MOS electrical characteristics," in *Proc. IEEE Custom Integr. Circuits Conf.* (CICC), Sep. 2003, pp. 245–248.

- [23] M. V. Dunga and X. Xi, "A holistic model for mobility enhancement through process-induced stress," in *Proc. IEEE Conf. Electron Devices Solid-State Circuits (EDSSC)*, Jun. 2005, pp. 43–46.

- [24] M. V. Dunga, C.-H. Lin, X. Xi, D. D. Lu, A. M. Niknejad, and C. Hu, "Modeling advanced FET technology in a compact model," *IEEE Trans. Electron Devices*, vol. 53, no. 9, pp. 1971–1978, Sep. 2006.

- [25] M. Hamaguchi et al., "New layout dependency in high-k/metal gate MOSFETs," in *IEDM Tech. Dig.*, Dec. 2011, pp. 25.6.1–25.6.4.

- [26] M. G. Bardon, V. Moroz, G. Eneman, P. Schuddinck, M. Dehan, D. Yakimets, D. Jang, G. Van der Plas, A. Mercha, A. Thean, D. Verkest, and A. Steegen, "Layout-induced stress effects in 14 nm & 10 nm FinFETs and their impact on performance," in *Proc. Symp. VLSI Technol.*, Jun. 2013, pp. T114–T115.

- [27] G. Angelov, D. Nikolov, M. Spasova, and R. Rusev, "Study of process variability-sensitive local device parameters for 14-nm bulk FinFETs," in *Proc. 43rd Int. Spring Seminar Electron. Technol. (ISSE)*, May 2020, pp. 1–4.

- [28] D. C. Chen, G. S. Lin, T. H. Lee, R. Lee, Y. C. Liu, M. F. Wang, Y. C. Cheng, and D. Y. Wu, "Compact modeling solution of layout dependent effect for FinFET technology," in *Proc. Int. Conf. Microelectron. Test Struct.* (*ICMTS*), Mar. 2015, pp. 110–115.

- [29] P. Zhao, S. M. Pandey, E. Banghart, X. He, R. Asra, V. Mahajan, H. Zhang, B. Zhu, K. Yamada, L. Cao, P. Balasubramaniam, M. Joshi, M. Eller, F. Benistant, and S. Samavedam, "Influence of stress induced CT local layout effect (LLE) on 14nm FinFET," in *Proc. Symp. VLSI Technol.*, Jun. 2017, pp. T228–T229.

- [30] Z. Wang, L. Chen, and M. Yin, "Analysis and characterization of layout dependent effect for advance FinFET circuit design," *Microelectron. J.*, vol. 125, Jul. 2022, Art. no. 105449.

- [31] H. Xu, J. Wang, H. Xu, Y. Gu, H. Zhu, Q. Sun, and D. W. Zhang, "Impact study of layout-dependent effects toward FinFET combinational standard cell optimization," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 70, no. 2, pp. 731–735, Feb. 2023.

- [32] B. Smith, A. Arriordaz, V. Kolagunta, J. Schmidt, and M. Shroff, "A novel biasing technique for addressable parametric arrays," *IEEE Trans. Semicond. Manuf.*, vol. 22, no. 1, pp. 134–145, Feb. 2009.

- [33] W. Pan, J. Ren, Y. Zheng, Z. Shi, and X. Yan, "Using NMOS transistors as switches for accuracy and area-efficiency in large-scale addressable test array," in *Proc. 12th Int. Symp. Quality Electron. Design (ISQED)*, Mar. 2011, pp. 1–6.

- [34] M. Dunga, "BSIM4.6.1 MOSFET model-user's manual," Univ. California, Berkeley, Berkeley, CA, USA, 2006.

- [35] HSPICE, Synopsys, Mountain View, CA, USA, 2022.

**SEYOUNG KIM** received the B.S. and M.S. degrees in electrical engineering from Seoul National University, Seoul, South Korea, where he is currently pursuing the Ph.D. degree in electrical engineering, with a research focus on design and verification methodologies for memory and analog/mixed-signal circuits. In 2005, he joined Samsung Electronics and performed research on memory design methodologies and computer-aided engineering. He also holds the position of

a Principal Engineer and the Project Leader with the Design for Reliability (DFR) Group, Design Technology Team.

**SEUNGHO YANG** received the B.S. degree in physics from the Pohang University of Science and Technology, Pohang, South Korea, and the Ph.D. degree in physics from Seoul National University. He is currently a Principal Engineer with Samsung Electronics Company, Ltd. He is interested in characterizing electronic devices and compact modeling for circuit simulation and the underlying fundamental physics.

**HYEIN LIM** received the B.S. and M.S. degrees in electronics engineering and the Ph.D. degree from Ewha Womans University, Seoul, South Korea, in 2010, 2012, and 2016, respectively. Her current research interest includes the modeling of magnetic tunnel junction characteristics for spin-transfer torque magneto-resistive random-access memory.

**HYEIN LEE** received the B.S. degree in electronics engineering from Ewha Womans University, Seoul, South Korea, in 2013, and the M.S. degree in electronics engineering from the Korea Advanced Institute of Science and Technology, Daejeon, South Korea, in 2015. Since 2015, she has been with Samsung Electronics Company Ltd., Suwon, South Korea. Her current research interests include device modeling and circuit simulation.

He was a Corporate VP with Samsung Foundry, leading the Design Technology Team and responsible for the design methodology and tool flow for all process technologies and semiconductor products manufactured by the Samsung Foundry for two years, from 2018 to 2019. He is currently a Corporate VP with Samsung Memory, responsible for all design tools and methodologies for memory products while leading the Design Technology Team. Since he joined Samsung, he has contributed to the development of low-power design methodologies, especially for mobile devices, and has developed RTL-to-GDS implementation and sign-off methodologies for semiconductor products. He is currently interested in all aspects of design technologies and environments impacting semiconductor product values (power, performance, area, yield, and cost) considering new process/package technologies, new applications (e.g., mobile, high-performance computing, and automotive), and new working environments (e.g., cloud).

**JONGWOOK JEON** received the B.S. degree in electrical engineering from Sungkyunkwan University, Seoul, South Korea, in 2004, and the Ph.D. degree in electrical engineering from Seoul National University, Seoul, in 2009. From 2009 to 2017, he was a Senior Engineer and a Principal Engineer with the Samsung Research and Development Center, South Korea. Since 2017, he has been an Assistant Professor and an Associate Professor with the Department of Elec-

trical Engineering, Konkuk University, Seoul. His research interest includes design-technology co-optimization (DTCO) for next generation technology in semiconductor devices.

**JUNG YUN CHOI** received the B.S. degree in electronics engineering from Kyungpook National University, Daegu, South Korea, in 1997, and the M.S. and Ph.D. degrees in electrical engineering from the Pohang University of Science and Technology, Pohang, South Korea, in 1999 and 2003, respectively. Since 2003, he has been with Samsung Electronics Company Ltd., Suwon, South Korea. In 2012, he was a Visiting Scholar with Stanford University, Stanford, CA, USA.

**JAEHA KIM** (Senior Member, IEEE) received the B.S. degree in electrical engineering from Seoul National University, Seoul, South Korea, in 1997, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, USA, in 1999 and 2003, respectively. From 2001 to 2003, he was a Circuit Designer with True Circuits Inc., Los Altos, CA, USA. From 2003 to 2006, he was a Postdoctoral Researcher with the Inter-University Semiconduc-

tor Research Center (ISRC), Seoul National University. From 2006 to 2009, he was a Principal Engineer with Rambus Inc. From 2009 to 2010, he was an Acting Assistant Professor with Stanford University. In 2010, he joined Seoul National University, where he is currently a Professor. In 2015, he founded Scientific Analog Inc., an EDA Company focusing on analog/mixed-signal verification. His research interests include low-power mixed-signal systems and their design methodologies. He served in the Technical Program Committees of the International Solid-State Circuits Conference (ISSCC), the Custom Integrated Circuits Conference (CICC), the Design Automation Conference (DAC), the International Conference on Computer-Aided Design (ICCAD), and the Asian Solid-State Circuit Conference (ASSCC). He was a recipient of the Takuo Sugano Award for Outstanding Far-East Paper from the 2005 ISSCC. He was cited as the Top 100 Technology Leader of Korea by the National Academy of Engineering of Korea (NAEK), in 2020.

...