Received 18 April 2023, accepted 4 May 2023, date of publication 12 May 2023, date of current version 24 May 2023. Digital Object Identifier 10.1109/ACCESS.2023.3275757

# **SURVEY**

# Microarchitectural Side-Channel Threats, Weaknesses and Mitigations: A Systematic Mapping Study

ARSALAN JAVEED<sup>®</sup>, CEMAL YILMAZ<sup>®</sup>, (Member, IEEE), AND ERKAY SAVAS, (Member, IEEE)

Faculty of Engineering and Natural Sciences, Sabanci University, 34956 Istanbul, Turkey Corresponding author: Arsalan Javeed (ajaveed@sabanciuniv.edu)

**ABSTRACT** Over the course of recent years, microarchitectural side-channel attacks emerged as one of the most novel and thought-provoking attacks to exfiltrate information from computing hardware. These attacks leverage the unintended artefacts produced as side-effects to certain architectural design choices and proved difficult to be effectively mitigated without incurring significant performance penalties. In this work, we undertake a systematic mapping study of the academic literature related to the aforementioned attacks. We, in particular, pose four research questions and study 104 primary works to answer those questions. We inquire about the origins of artefacts leading up to exploitable settings of microarchitectural side-channel attacks; the effectiveness of the proposed countermeasures; and the lessons to be learned that would help build secure systems for the future. Furthermore, we propose a classification scheme that would also serve in the future for systematic mapping efforts in this scope.

**INDEX TERMS** Cybersecurity, microarchitecture, side-channel, systematic-mapping.

### I. INTRODUCTION

The manifestation of computer architecture roots into microarchitecture and instruction set architecture (ISA). Microarchitecture refers to the ways, in which an ISA is implemented for a specific microprocessor. For reasons, such as design, cost, and optimization, a given ISA can be implemented under different microarchitectures, which typically distinguish among each other in the way constituent components of the processors are interconnected and interoperated. With all these aforementioned complex entanglements in play, exploitable security vulnerabilities may arise, which can be abused by a malicious adversary to affect the confidentiality and integrity of a computing system, potentially resulting in serious loss.

In recent years, among some of the many reported sidechannel attacks exploiting the microarchitectural vulnerabilities, Meltdown [1] and Spectre [2] are few of the notable and widely talked-about examples, as these attacks

The associate editor coordinating the review of this manuscript and approving it for publication was Ali Kashif Bashir<sup>(D)</sup>.

particularly abuse the transient state of the microprocessors during speculative execution. The mechanics of these attacks are although complex, yet they are practical and have successfully demonstrated exfiltration of sensitive private data and cryptographic secrets.

Furthermore, the findings about the microarchitecture attacks have sparked the interest of the security research community and accelerated the research efforts in this relatively recent area of software and cyber security. In this regard, research efforts are being carried out both on the axis of uncovering newer vulnerabilities and to prevent, mitigate, and lessons to build secure systems of the future.

The literature on microarchitecture security research has, therefore, been growing at a relatively fast pace. Typically a microarchitecture side-channel attack is discovered and reported at first, followed by research efforts into its potential attack variations, mitigations, and security-oriented lessons to be learned. However, efforts that over-arch the individual works to systematically gather and to assemble various aspects of microarchitecture security research in a broader context, are yet limited and somewhat outdated, and thus are still desired. The purpose of our presented work as a systematic mapping study is a step in this direction. To the best of our knowledge, this work is the first systematic mapping study carried out on this subject.

A systematic mapping study provides an overview of the existing research through systematic classification of the published literature on the topic, guided by the posed research questions under the constraints of a mapping protocol [3]. A prime finding from such studies are the research spots, which have gained considerable attention, as well as the emerging research trends, which can launch newer investigations and guide the direction for further research. In contrast, a literature survey aims to comprehensively index and, thus report the existing state of affairs on a topic of interest. Consequently, systematic mapping studies and surveys differ from each other in terms of their end goals and the research process they follow.

To guide our investigation, we have raised four research questions (RQs)(Section IV-A) to address the security concerns about microarchitectures, such as the aspects leading up to leakage, the ways in which exploitable corridors are created, the effectiveness of the existing countermeasures as well as their applicability to zero-day attacks, and the lessons to build more secure systems.

The main contributions of our mapping study are: i) a broad overview of the research efforts in the area of microarchitecture security; ii) a classification scheme that can be used to classify newer research in this area; iii) a decent yet diverse coverage of the published research on the topic, particularly from the last five years; and iv) the identification of hot and cold research spots to date.

The target audience of this work is the researchers and practitioners, who aim to establish a better overarching understanding of the research efforts being carried out in this area.

The remainder of the paper is organized as follows: Section II discusses related work; Section III presents the necessary background information; Section IV presents the methodology followed, detailing the search, inclusion, and the exclusion criteria together with the study selection process used; Section V introduces the classification scheme employed, followed by the mapping results; Section VI details the answers to our research questions; Section VII presents potential threats to validity in the study; and Section VIII concludes the paper and presents possible directions for future work.

#### **II. RELATED WORK**

To the best of our knowledge, our study is the first systematic mapping study in the area of microarchitectural side-channel threats, weaknesses, and mitigations. However, there exist a few surveys in the literature [4], [5], [6] as well as some individual works [7], [8], [9], each addressing a specific aspect. Albeit, some of these works are either being somewhat dated or generally lacked wider scope. Table 1 presents a highlevel glimpse on existing related work together with its strengths and limitations.

| TABLE 1. Publication year, Strengths(S) and Limitations(L) of notable | 1 |

|-----------------------------------------------------------------------|---|

| related work.                                                         |   |

|                                                                       |   |

| Article | Year     | Standing |                                                                                                         |                         |

|---------|----------|----------|---------------------------------------------------------------------------------------------------------|-------------------------|

| [4]     | [4] 2012 |          | covers a range of attacks circa. 2012                                                                   |                         |

| [+]     |          |          | somewhat outdated and exclusive fo-<br>cus on embedded micro-processors                                 |                         |

| [5]     | 2018     | S        | variety of microarchitecture attacks<br>and defenses presented with emphasis<br>on role of cache memory |                         |

|         |          | L        | devoid of attacks involving prefetchers                                                                 |                         |

| [6]     | 2019     | 2018     | S                                                                                                       | focus on timing attacks |

|         |          | L        | lacking attacks employing other vec-<br>tors                                                            |                         |

Kanuparthi et al. present a survey [4] dating till 2012. The scope of the survey is bound to embedded microprocessor security only. As the proliferation of embedded systems was on the rise, so as emerging challenges to secure their vulnerable nature due to their limited onboard resources. The authors reported some of the prominent attacks plaguing that arena during those times. Furthermore, the authors compared the trade-offs among sought-after countermeasure approaches, such as levering integrity checks, data encryption, and microarchitecture revisions.

Szefer et al. present a survey [5] on microarchitectural side- and covert-channels with their defense proposals dated until 2018. The prime emphasis of the aforementioned work is on timing-based and (to some degree) access-based exploitations. In a distinct regard, the authors did foresee the role of the prefetchers in microarchitectural exploitations and did theoretically present a setting for such an attack, yet were unable to provide a citation to any known published literature, since the research into prefetcher exploitations was still in its infancy during the time of the work.

Another survey [6], which Ge et al. authored around the same year of 2018, exclusively focused on the timingbased microarchitectural attacks and their countermeasures. The main motivation behind this survey was to taxonomize the aforementioned efforts. These attacks established their reputation as prime vectors for remote exploitation in cloud computing. Furthermore, the authors emphasize the need to secure cloud systems against such class of attacks, as our ever-increasing adoption and growing reliance on cloud computing would continue to grow with the passage of time.

Note that a direct comparison with these works wouldn't be straightforward because of the different sought after research objectives as well as the methodology being employed. Last but not least, we believe the constituent studies employed in our work are fairly recent in the sense that half of them have been published in the last five years (since 2018).

As we and other researchers [5], [6] have observed that microarchitecture security is a fast-growing field and even the entire playground may change quickly. So we believe, in this time frame, our systematic gathering of literature, especially from the last five years is going to be an important effort and would serve as a valuable scientific resource.

#### **III. BACKGROUND INFORMATION**

To assist the understanding of the reader for the remainder of this article, we, in this section, introduce essential terms/concepts and provide some relevant definitions for the material ahead. Furthermore, for clarity, we also provide Table 6 in Appendix B to list out all the abbreviations and their expansions in one place, which will be used throughout this article.

The usual intention behind a microarchitectural sidechannel attack undertaken by a malicious actor is to exfiltrate some secret information or to perform acts of sabotage on a system. In literature, malicious actors are also often referred to as adversaries. This secret information is usually wellprotected and is not meant to be revealed to any adversaries. In the case of cryptography, this secret information could be a secret key, the content of a file containing sensitive business information, the content of a buffer, or the latent parameters of a machine learning algorithm. In contrast, an act of sabotage would intend to disrupt the services provided by a system, such as a ransomware attack. Regardless of the intention of the malicious actor, an affected system or a process is generally referred to as a victim. If the malicious actor's main intention is to exfiltrate some information then it is referred to as a *spy* in contrast to a *saboteur* carrying out a sabotage. Both the spy and saboteur could be a single process, a group of processes, a compromised system component, or another involved remote actor.

A *side-channel* is a communication channel established between a sender party and one or more receiver parties, such that sensitive information is unintentionally leaked as a result of side-effects to computations being carried out on the underlying hardware. In contrast, a *covert channel* is a sidechannel that is intentionally established between a malicious sender and receiver, upon which exfiltrated secret information is being transmitted.

A CPU (central processing unit) also referred to as processor or microprocessor, executes the machine instructions. A CPU is realized on a silicon die through an electronic design and automation (EDA) process and usually comprises billions of interconnected transistors. A CPU provides a programmable interface in the form of instruction set architecture (ISA). The ISA could be implemented in several ways dictated by the underlying microarchitectural design, i.e. microarchitecture. Generally, a microarchitecture comprises some specialized processing elements, which are referred to as functional units, and some intermediate temporary storage elements, which are referred to as registers and buffers. A register is a small, but fast temporary storage area within the processor to hold some data, such as an argument to an instruction. A buffer, on the other hand, is a temporary storage area allocated in the main memory to hold data inbetween transfers. In recent microarchitectures, however, few specialized buffers exist in the CPU to assist the operations of various onboard functional units, such as pipeline buffers. Furthermore, a CPU or GPU (graphics processing unit) could be equipped with performance counters, which are special onboard registers counting the low levels occurring in the CPU, such as the number of cache misses or hits. A GPU is a specialized processor meant to process computer graphics.

Instructions of a program execute in a pipeline and typically go through instruction-*fetch*, *decode*, *execute*, *memory*, and *writeback* steps. During each stage of this pipelined execution, the intermediate results are stored in the pipeline buffers where the arguments and the operational configuration are provided through intermediate registers.

The microarchitecture itself is a specific instance of the number of valid ways, in which the underlying *functional units* of the CPU should be interconnected to fulfill the design and performance goals intended by the designers. On modern CPUs, the ISA is mapped onto a sequence of small microcode operations established by the underlying microarchitecture. Instructions are executed in one or more clock ticks, which are referred to as *clock cycles*.

A multicore processor is a single processor containing multiple execution cores in a single package. Each core has some core-private resources, such as cache and pipeline stages, in addition to having some resources shared with other cores. Multicore processors deliver significant performance improvements as the workload can be distributed among available cores to be executed concurrently.

Out-of-order and speculative execution are other performance enhancement mechanisms, leveraged to optimize the execution of instruction stream on modern processors. Outof-order execution refers to executing instructions independently from each other in their order of execution to increase overall throughput. Those instructions that do not have pending data dependencies are executed immediately whereas instructions with pending dependencies are scheduled for a later time when those dependencies are met. However, out-of-order execution remains hidden from the application point of view and everything appears as it has been executed sequentially. In a distinct regard, speculative execution refers to executing branches speculatively ahead of time by guessing the most probable branch. If the guesswork is correct then results are already available from the executed branch. Otherwise, the executed branch is discarded and the correct branch is taken.

Caches are small memories that bridge the data-access latency between slow but large physical memory and fast CPU(s) by buffering frequently accessed data. Modern systems typically have multiple cache levels (L1, L2, and often L3) arranged in a hierarchy comprising the cachesubsystem. L1 cache is split as instruction and data cache, followed by a larger L2 cache. L1 and L2 caches are coreprivate, i.e., each core gets its own dedicated set of these caches. On some systems, L3 cache, also called the last-level cache (LLC), is shared between all the CPU cores. On modern Intel microarchitectures, LLC is inclusive in nature [10], which contains all the data within L1 and L2 caches. Given a memory address to be accessed, the CPU first looks it up in the L1 cache, if the respective data is found in the cache, its called a cache hit, otherwise a cache miss. Upon a cache miss, the CPU next looks for the address in next level

cache and keeps on traversing the cache hierarchy until either the respective data is located in the cache or it reaches all the way to the main memory. A cache is organized into *cache lines* and *cache sets*, each of which contains the same number of cache lines. A given memory address is decoded into *tag*, *index*, and *offset* fields in order to look up the respective data in the cache hierarchy.

The memory controller handles the memory accesses to DRAM when data requested by the CPU is not available in the cache. *Memory controller* serves a data request by translating the given physical address into an internally maintained DRAM map of channel, bank, row, and column information. Furthermore, the memory controller arbitrates internally among the concurrent memory accesses through scheduling and buffering policies. *Memory deduplication* is a mechanism to save the physical memory space by keeping one copy for each duplicated memory pages as long as the pages are unmodified. The modified page is isolated and kept as a separate independent page.

Prefetching is among the few employed methods besides speculative execution to enhance performance in modern CPUs. Hardware prefetchers are those microarchitectural units that perform the task of prefetching and handling associated aspects. In a nutshell, prefetchers increase the cache hit rate through speculatively prefetching the data that would potentially be requested in the near future during a computation. To this end, patterns of memory access requests are observed and speculative data fetching is issued accordingly. Prefetchers exist in a hierarchy among all the levels of cache-to-memory, such as L3-L2 and L2-L1. The implementation details of the prefetchers are usually proprietary and subject to change as the underlying microarchitecture evolves. Broadly speaking, prefetchers are categorized into next line prefetchers and stride prefetchers. The former simply prefetches the next line for the current cache-line in use, whereas the latter learns and utilizes the patterns in memory accesses.

In recent years, a paradigm in secure computing has emerged themed around its reliance upon hardware-based *Trusted Execution Environments* (TEE), realized in software through enclave programming [11]. CPU vendors provided TEE environments through microarchitectural extensions. For instance, ARM provides ARM-TrustZone [12] and Intel provides TPM+TXT [13] and later Software Guard Extensions (SGX) [14].

Last but not least, *Peripheral Component Interconnect* (PCI) and its modern high-speed variant PCIe (PCI *express*) is the de-facto protocol with supporting hardware, through which CPU and high-speed peripheral devices, such as GPU and NIC, are connected.

#### **IV. METHODOLOGY**

In this work, we followed the widely-accepted guidelines for carrying out systematic mapping studies [15], [16], which had also been adopted by some of the relevant mapping studies in the literature [17], [18], [19]. To this end, we first carried

out a planning phase, primarily for laying out the research questions, choosing the method to locate and appraise primary studies, crafting a search strategy, and carrying out the curation of the primary studies. In this context, a primary study is a chosen, peer-reviewed, and published scientific article that went through the usual phases of searching, screening, and classification, which are performed as a part of the typical workflow in a systematic mapping process. Each primary study is meant to contribute to the systematic data synthesis by answering one or more research questions.

We, in particular, decided to follow a mapping process comprised of the following steps [15]: *defining research questions, conducting search, screening of papers, keywording of abstracts, classification,* and *data extraction and mapping.* Although all of these steps are sequential in nature and performed one after another, oftentimes the individual steps are performed iteratively more than once to refine their outcomes and improve the overall end result of the whole mapping process. Next, we discuss how we actually carried out each of these steps in this study.

#### A. DEFINING RESEARCH QUESTIONS

We put together the following research questions as a basis for this study:

- RQ1: What are the aspects of microarchitectural artefacts, which contribute to the sensitive information leakage to compromise security and privacy?

- RQ2: How some of the recent microarchitectural surfaces were crafted and turned into feasible attack corridors?

- RQ3: How effective are the proposed countermeasures of microarchitecture side-channel attacks and whether these countermeasures are generalizable? Can these generalized countermeasures predict/prevent zero-day attacks?

- RQ4: Given the published countermeasures, how secure a system we can build against microarchitecture sidechannel attacks and what lessons we can incorporate in this system-design process?

#### **B. CONDUCTING THE SEARCH**

Guided by our research questions, we defined an initial set of keywords as seeds to locate relevant papers in Google Scholar [20]. We read these papers and utilized *snowballing technique* [21] to find additional papers that we find relevant to our RQs. Snowballing refers to locating additional papers based on the reference lists or citations of a given paper [18]. To aid the snowballing process, we used an online tool, called Connected Papers [22]. In particular, we came up with 11 core papers as a result of the initial search, these papers were used to put together a set of keywords (listed in Table 2), which were then used as the basis for defining search strings. The validity of these keywords was tested by rediscovering the core papers they were driven from. We also eliminated some keywords that we found to be redundant, superfluous, **TABLE 2.** Keywords used to form search strings. To avoid redundancy, we are adopting regex format to specify potential variations of a keyword. We used these keywords in *Title, Abstract, Author defined,* and *All metadata* fields for performing database queries.

#### Keyword(s)

| "micro[ -]?architecture", "attack", "vulnerability", |

|------------------------------------------------------|

| "side[ -]?channel", "origin[s]?", "defen[c s]e",     |

| "counter[ -]?measure[s]?", [0 zero]?[ -]?day,        |

| "detect[ion]?","prevent[ion]?",                      |

| "leakage", "predict", "secure", "system"             |

or causing an increased number of irrelevant results in the search.

To carry out the actual search, we utilized three standard databases as sources, namely *IEEExplore* [23], *ACM Digital Library* [24], and *Springer Link* [25]. This decision was primarily influenced by the availability of the database subscriptions that our campus had, the manpower of our team, and the fact that these sources are the de-facto prime venues of scientific literature in computer science. Furthermore, we leveraged the advanced search features of these databases to perform the search queries. The advanced search features enabled us to limit or expand the scope of the queries for decreasing the frequency of the irrelevant results. Based on the keywords given in Table 2, the search strings for each database were created and iteratively experimented with to come up with the most appropriate search results.

We, furthermore, observed that the internal mechanics of these databases were different. That is, a query suitable for one database was not necessarily to be equally effective in another database. For example, we found out that searching for keywords in the abstracts at IEEExplore was more effective than running the same search at ACM Digital Library. Nonetheless, we used the listed set of keywords (Table 2), the database-specific advance search features (e.g., boolean operators), and available filters to tailor the relevance of the search results.

After getting the search results, we sorted them in the order of relevance and picked the top 100 results for ACM Digital Library and Springer Link. For IEEExplore, we chose to stop when 5 irrelevant papers in a row were observed. We used ranking by relevance for ACM and Springer Link databases. For IEEExplore, however, this feature was unavailable. Thus, we opted to use two different aforementioned stopping criteria. Other works [18], [26] have also followed a similar approach.

#### C. SCREENING AND CLASSIFICATION PROCESS

To aid the screening and the study selection process, we tailored the following inclusion and exclusion criteria, which were adopted from [16], [19], and [18].

#### 1) INCLUSION CRITERIA

- a study must answer at least one of the formulated research questions (RQs),

- a study must be dated until the March of 2023,

- priority must be given to the evaluation and validation research studies during the selection process,

- a study must be peer-reviewed and published in English.

#### 2) EXCLUSION CRITERIA

- a study should not be in one of these forms: patents, white papers, reports, thesis, tutorials, and webpages,

- · duplicate studies located by different search engines,

- inaccessible, irretrievable, or irrelevant to the theme of our work,

- any article, the subject matter of which is around quantum computing.

Note that the aforementioned criteria aided us to perform the initial screening and sanitation of the search results.

#### D. OVERVIEW OF THE DATASET

Our initial search effort resulted in 546 articles from the three databases as follows: 192 from IEEExplore, 210 from ACM Digital Library, and 144 from Springer Link. However, after the title and abstract screening, we manually went over the content of the articles, i.e. content scanning, especially for those articles where the abstracts were short enough to be suitably meaningful or lacked ample clarity in general. Furthermore, we also content scanned those articles with abstracts where it was found difficult to pinpoint the investigated problem and/or the main contribution being made. We also performed content scanning of the individual sections for the papers, where we felt that individual clauses of inclusion and exclusion criteria were difficult to apply. In such a case, we relied on team discussion to reach a final consensus. Other mapping studies [18], [27] have also followed a similar practices.

For classification we settled for 104 articles to serve as our primary studies, the list of which is available in Table 5, whereas, the remainder 442 (out of 546) articles were dropped at this step. The classification scheme is described in Section V which guided us toward the final data extraction and mapping of results. Ultimately, the primary studies also served as the basis for answering our RQs, which was, indeed, the main goal of this mapping study.

Regarding further relevant statistics of the primary studies dataset, we notice that 25% (25 out of 104) of articles are published in journals and remainder 75% (79 out of 104) as conference papers. Similarly, page count of primary studies span between 4-27 pages, where 12 is the median count. Lastly, 57% (60 out of 104) of primary studies primarily focused on a countermeasure approach and remainder 43% (44 out of 104) proposed an attack approach. These aforementioned statistics establish a fair degree of confidence about the balance in the dataset for our systematic mapping study.

#### **V. RESULTS**

Systematic mapping studies aim to provide an overview of a research arena through the classification of published literature on the subject topic. To aid discussion and present the results of our study, we first describe the classification scheme, which we used to categorize the primary studies. We then present the mapping results in the light of the aforementioned scheme.

In accordance with the established norm of systematic mapping studies, we first describe the classification scheme, followed by the presentation of aggregate statistics on the individual facets of classification. The main takeaway from the aggregate statistics is the quantitative presentation of the data gathered from primary studies. This data presents an overall picture and helps build ample confidence in the selection and the classification process as well as in the thematic diversity present in the pool of primary studies. The primary studies are then used to answer the main research questions in this study.

# A. CLASSIFICATION SCHEME

Our classification scheme broadly classifies the studies into seven categories: *research type, main contribution, hardware platform, instruction set architecture (ISA), leakage vector,* and *leakage component.* Next, we describe each of these categories.

## 1) RESEARCH TYPE

This category describes the different research approaches as outlined by Wieringa et al. [28]. We chose to use Wieringa's classification scheme as it has also been used in earlier mapping studies [18], [19], [29]. We associated each of our primary studies with one of these research approaches: *evaluation*, *validation*, and *solution proposal*. Based on a typical exclusion criterion of mapping studies [18], [26], we disregarded *philosophical*, *opinion*, and *personal experience* papers, and focused on opting primarily for the *evaluation* and *validation* research. Note that the aforementioned types of research aim to demonstrate the practical usage of a technique backed by real data, relevant experiments, and empirical evaluation.

# 2) MAIN CONTRIBUTION

Categorization based on contribution type in mapping studies has been employed previously by Zein et al. [19] and Shahrokhni et al. [17], which classifies each primary study to one of the following specific types of contribution: *framework, tool, metric, approach,* and *criterion.*

A *framework* paper introduces a detailed method, which has a broad scope and tends to focus on more than one research question or area. Whereas, an *approach* paper has a narrower scope and tends to have a more specific goal addressing a single research question. Similarly, a *tool* paper presents an implementation of at least one approach with the aim of demonstrating the applicability of the proposed approach to the practitioners. Primary studies, where the core emphasis was on tool demonstration, are classified in this category. A *metric* paper, on the other hand, proposes an empirical measure to quantitatively describe a variable of interest. In contrast, a *criterion* paper outlines a strict method, by which a certain quantitative or qualitative attribute of an observatory aspect can be judged upon.

# 3) HARDWARE PLATFORM

This category represents the nature of the physical hardware considered by a primary study, upon which the main subject matter was presented and/or evaluated. This categorization would help establish whether microarchitecture attacks are specific to or prevalent for a certain hardware type. We opted for the following subcategories: commodity, mobile, embedded/IoT, cloud, and any, based upon the explicit mentioning of the platform type discussed. Commodity hardware refers to the general purpose computing platforms, such as workstations for daily usage. Whereas, mobile hardware refers to the handheld portable devices, which are primarily meant for communication and serve the limited computing needs of the users. Smartphones are a prime example of this category. Similarly, embedded/IoT devices refer to the microprocessorequipped hardware with optional networking ability and occasional connections to the internet, which are designed to perform a dedicated function. Similarly, cloud platform refers to a group of server machines that are networked together and connected to the internet, located typically in a datacenter environment. The users are given remote access over the internet to utilize these machines for their application usecases. Last but not least, the any category refers to either an unspecified platform or the specification of the platform does not matter. Those primary studies, which present a generic approach, criteria, or empirical metric, fall under this category as their subject matter is agnostic to a specific hardware type.

#### 4) EVALUATION METHODOLOGY

This category refers to the methods adopted in the primary studies to conduct their experimental evaluations. In this regard, we have observed the following types of methodologies: pure *software* implementation, employment of *simulation* tools, evaluations performed on *real* hardware, evaluations performed on *FPGA*-synthesized hardware, and *other*, referring to the studies where the aforementioned categories do not matter. For instance, studies presenting a criterion or an empirical metric belong to the *other* category. Note that primary studies may follow more than one evaluation methodology, such as a study carrying out the evaluations through simulation followed by hardware implementation and so on.

# 5) INSTRUCTION SET ARCHITECTURE

Instruction set architecture (ISA) refers to the syntactic and semantic realization employed at the machine level, to which the compiled software is assembled for execution. In this regard, we observed that the following types of ISAs were used in the primary studies selected: *Intel*(x86,x86\_64), *ARM*, *RISC*, Nvidia-*CUDA*, *MIPS*, and *other*, referring to the studies where either multiple ISAs or lesser-known ISAs are used. This categorization would help establish whether microarchitecture attacks are agnostic to ISA or not.

#### 6) LEAKAGE VECTOR

Leakage Vector refers to the side-channel, through which the sensitive information leaks or emanates. In this regard, we consider the following leakage vectors: *access patterns*, *contention*, *sharing*, *dependence*, *duplication*, *EM*, *execution*, *fault*, *interruption*, *power*, *speculation*, *state*, and *timing*.

Access patterns refer to the recurrent patterns observed in accessing some hardware resources, through which the high-level behavior of the requesting entities can be inferred. This can later be used as a ladder step to either assist or rely for further malicious exploitation. In contrast, contention refers to at least two entities contending to get access to a shared resource to perform their task. Similarly, sharing refers to a shared resource being granted (according to some agreed-upon policy) to one of the several requesting entities. Whereas, dependence refers to an entity being reliant upon some resources or being controlled by some resources, to perform its assigned function. In contrast, duplication refers to creating a duplicated copy of a requested resource for the requesting entity to fulfill its needs. Moreover, EM refers to the electromagnetic emanations, which can be observed at a distance without physical proximity. These emanations can be utilized to infer the underlying state as well as the ongoing activities of the system radiating from them. Similarly, power refers to the electrical power being consumed in relation to the hardware demand. Whereas, execution refers to the act of executing instructions on a processor. Fault refers to an event or untimely interruption, which disturbs the sanity of the internal state of a processor and the correctness of an ongoing computation. To recover from a faulty state, often the intermediate computation is discarded and the execution is rolled back to some previously known good state. In contrast, interruption refers to an event, which needs to be served immediately, causing temporary suspension of the lower-priority execution happening at the time of the interruption. Speculation refers speculative execution (Section III). Similarly, state refers to an existing internal state of a resource, which would lead to one of the possible future states. Lastly, timing refers to the elapsing of the time between two microarchitectural events of interest.

#### 7) LEAKING COMPONENT

This refers to the microarchitectural functional unit or subsystem, which is the culprit of the side-channel leakage by exposing one or more leak vectors. The constituents for this category that we relied upon organizing the selected primary studies are: *buffers*, *caches*, *instructions*, *interconnects*, *memory*, *microprocessing elements*, *tee* (trusted execution environment), and *timers*. The background information for these components has been presented in Section III

#### **B. MAPPING RESULTS**

In this section, we present the quantitative and qualitative results of our systematic mapping study with respect to the classification scheme introduced in Section V-A.

#### 1) PUBLICATIONS TIMELINE

We curated a total of 104 primary studies by following the steps of the systematic mapping methodology introduced

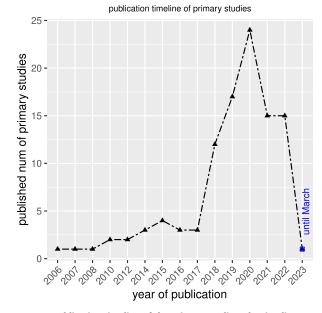

**FIGURE 1.** Publication timeline of the primary studies. The timeline spans from 2006 to 2023. For each year, the number of primary studies is indicated on the vertical axis. The year 2023 is covered only until month of March.

in Section IV. Table 5 lists the title of each study and its associated bibliographic reference. Furthermore, each study is assigned a sequential study ID, such as S1, S2, and S3. We use these study IDs to refer to specific primary studies throughout the remainder of the paper. Note that assigning study ID is an established practice and has widely been followed in other mapping studies [19], [26]. More specifically, study IDs help the reader differentiate between references to bibliographic items versus a primary study.

Figure 1 illustrates the publication timelines for the primary studies over the years from 2006 to 2023. We first observe that the research in microarchitectural side-channel attacks became visible in 2006 and gained gradual attention over the years till 2017. From 2017 onward, the research area gained more and increasing attention, which is evident from the sharp increase in the number of publications. Software and cyber security has been gaining more and more attention over the recent years and this trend has been observed in other studies [18], [26] as well.

Figure 1 also illustrates that the pool of primary studies we assembled for this work is fairly recent. More specifically, 83% (87 out of 104) of the studies were published in the last 6 years (i.e., between 2017 and 2022). Note that, for the year 2023, the studies were included until the end of March, during which we carried out the analysis.

#### 2) RESEARCH SPOTS

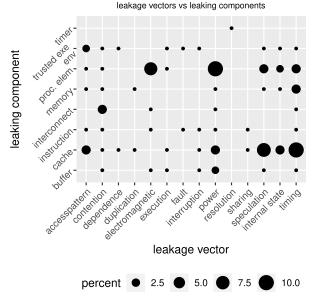

Figure 2 highlights the research spots as a matrix of bubbles where the size of a bubble is proportional to the volume of the studies at the intersection of the respective leakage vector and leaking component categories. As such, the figure reveals the hot and cold spots where the research has focused.

FIGURE 2. Research spots for leakage vector vs. leaking components.

Although some care must be taken when interpreting the research spots in Figure 2 as the pool of primary studies used in the analysis is solely assembled based on a strict selection criterion designed to address our research questions (Section IV-C), the figure illustrates some important research characteristics of the primary studies. Among the notable patterns, we observe that *contention* and *timing* as the leakage vectors have been involved across almost all (7 out of 8) the leaking components. Similarly, *cache* and *trusted execution environment* as the leaking components have been involved across most (11 and 9 out of 14, respectively) of the leakage vectors. The ways, in which the various leaking components leak information through leakage vectors are discussed at length in Section VI.

#### 3) RESEARCH FACET AND CONTRIBUTION TYPE

We classify the primary studies (Table 5) along the axes of research facet and main contribution (Section V-A). Figure 3 illustrates the results we obtained. We observe that most of the primary studies belong to the *validation* category (59 out of 104), followed by the *evaluation* category (37 out of 104), and then the *solution proposal* category (8 out of 104). Note that the *solution proposal* category is customarily [18] excluded from the study selection criteria, because, by nature, they lack considerable evaluation. However, we opted to flex on this practice and, in the final iteration of our study selection proposals. We did this because we found the presented ideas to be interesting and relevant to the scope of our research questions.

Along the same lines, we observe from Figure 3(b) that 75% of the primary studies are actually contributing approaches backed by evaluations. However, the remaining 25% contribute *tools* (4 out of 104), *metrics* (7 out of 104), *frameworks* (15 out of 104), and criteria (1 out of 104). Note

FIGURE 3. Percent-wise share of the primary studies with respect to (a) research facet and (b) main contribution. The length of a bar depicts the percentage value, whereas the integer associated with the bar indicates the actual count.

that the studies occasionally contributed to more than one category.

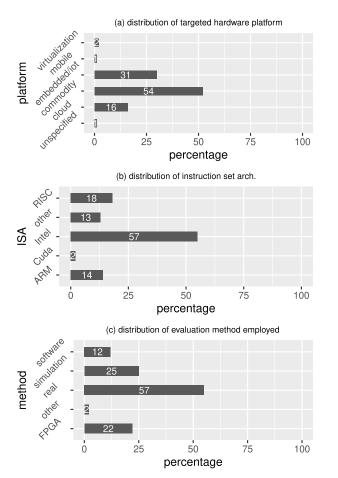

# 4) TARGET PLATFORM AND INSTRUCTION SET ARCHITECTURE

In terms of the target platform hardware and the instruction set architecture (Figures 4a and b, respectively), we observe that all of our primary studies have considered them all, albeit to various degrees as shown through percent-wise proportion in Figure 4. However, we do observe that the commodity hardware platform and the Intel x86 ISA have the largest share overall, which is to be expected due to their proliferation worldwide. Nonetheless, we see contributions from other ISAs and platforms too, which reveals an important fact that microarchitectural exploitations and vulnerabilities are not limited to one specific platform and ISA, but rather threatening the whole spectrum of computing hardware.

### 5) EVALUATION METHODOLOGY

The percent-wise distribution of different types of evaluation methodologies employed by the primary studies is shown in Figure 4(c). Overall, 55% and 22% of the primary studies opted to be evaluated on real hardware and FPGA systems, respectively. In contrast, 25% and 12% of the studies opted for simulation- and software implementation-based evaluations, respectively. And, the meager 2% are grouped under the other category, indicating that the other categories do not apply (e.g., the studies, which propose a criterion).

# VI. DISCUSSION – ADDRESSING THE RESEARCH QUESTIONS

In this section, we address our research questions by using the primary studies in due length and scope. However, the gist of

FIGURE 4. Percent-wise share of primary studies with respect to (a) target hardware platform and (b) instruction set architecture. The bar length indicates the percentage value and the integer value on each bar indicates the actual count.

following sub-sections span along the following lines: i) todate almost all known microarchitectural components have been exploited in quite novel ways; ii) the motivations behind, reverse-engineering skills, knowledge of the microarchitectural intricacies at system-level, and availability of needed resources to research, prove to be sufficient in the hands of exploit developers; iii) upon public disclosure of an exploit, in due time researchers are able to come up with effective mitigations, albeit often at the cost of decrease in system performance; iv) long-term academic research is bearing fruit and has gathered sufficient knowledge that is improving and shaping security-oriented future of microarchitectures.

# A. RQ1: WHAT ARE THE ASPECTS OF MICROARCHITECTURAL ARTEFACTS, WHICH CONTRIBUTE TO THE SENSITIVE INFORMATION LEAKAGE TO COMPROMISE SECURITY AND PRIVACY?

Undesired information leakage from the microarchitectures often originates due to the spatio-physical implementation of the CPU, the design optimizations, the trade-offs, and the temporal resource allocations among various functional units during the program executions. Effective resource allocation and optimal scheduling of the functional units can deliver the

VOLUME 11, 2023

desired performance, but may fail to deliver perfect security. From the existing security research, the diverse aspects of the microarchitectures have been explored to discover the security vulnerabilities, which often involve one or more components being engineered into an information leakage state.

We identified a number of artefacts through our set of primary studies (Table 5) compromising microarchitectural security. Next, we provide a high-level overview, which should serve as a primer for a starter audience. The more focused and technically inclined security-specific account will be covered in Section VI-B.

Concurrent execution of multiple processes has an influence on the contents of shared and private caches in a multicore environment. Furthermore, the hardware scheduling and resource allocation policy determines the assignment of cores to concurrently executing processes. Processes executing on the same core can access the core-private caches as well as the shared ones. However, processes even executing on different cores can indirectly influence the content of the private caches of other cores, through the propagation of the side-effects from the shared LLC cache to all cores [S13], [S18] Thus, code execution and data access, ripple through the cache hierarchy in ways, which an adversary can exploit through timing and access based channels.

The memory controller resolves memory accesses made by CPU onto the internal organization of DRAM, such as into channels, banks, rows, and columns. Furthermore, it also arbitrates and schedules multiple concurrent memory access requests in addition to overseeing the buffering of data for reads and writes according to the predetermined policies. The choice among different internal policies exhibits an effect on the timing variations and on the frequency of conflicts during bank- and row- address resolutions. Certain combinations of these policies give rise to exploitable timing differences, which an adversary can leverage [S21] to build a covert communication channel and utilize patterns in these timing differences to encode bits of secret message. In a recent work [S33], the authors described a feasible exploitation of memory deduplication mechanism to establish a covert channel in a cross-vm (virtual machine) scenario.

The buffer contents and the order of register allocation can significantly impact the internal state of the CPU core and could be exploited to engineer an internal state feasible for security exploitation. One such tactic is to prolong intervals of transient execution for certain processes, which would provide an opportunity to attacks reliant on transient state. It would also assist to increase the overall effectiveness of the similar attacks [S58]. Furthermore, under favorable internal states, potent electromagnetic and power side-channel attacks [S54] can be carried out. The internal state of a CPU has a direct correlation to power consumption and electromagnetic emissions. Analyzing these emissions can help a spy infer the degree of system activity as well as the specifics regarding the current workloads.

Intel SGX creates an isolated execution environment, called *enclave*, which provides a protected, secure, and isolated sandbox to code segments in a user process.

In these code segments, sensitive computations are carried out, which rely on some secret information, such as a cryptographic attestation. The notion here is to protect sensitive user processes from untrusted system software, such as an OS or a hypervisor. However, in recent years various microarchitectural attacks have been demonstrated to break the security provided by SGX, despite the strong isolation guarantees provided by this technology [S78], [S77]. In particular, attackers have been able to compromise authentication during the entry and exit protocol performed while delegating the computations from OS to enclave and vice versa. In another instance, malware has been able to conceal itself inside a secure enclave by abusing the SGX protection features, which enabled the malware to carry out attacks on neighboring enclaves [S77].

Modern microarchitectures enable speculative execution of programs. In a nutshell, processors can speculatively fetch and execute a stream of instructions along a predicted path ahead of time. Later, if the program actually executes along this predicted path, the pre-computed results are already available and ready to use. On the contrary, if the prediction fails, the thus-so-far speculative computation trail is simply discarded. However, research reveals that speculative execution leaves behind trails of temporary microarchitectural state changes, such as the cache lines being touched and/or evicted and the updates in the behavior of the branch predictors or prefetchers. The exploitation of aforementioned state changes led up to many side-channel attacks to exfiltrate sensitive information, which otherwise is not possible to do so [S71], [S8].

Some recent research revealed that prefetchers can be exploited to establish a high-bandwidth covert-channel across processes. A prefetcher has the ability to learn and retain patterns of memory accesses and leverage this knowledge to fetch data ahead of time. However, a malicious process can abuse this ability and selectively make the prefetcher to forget the strides it has learned for another process. This is typically feasible due to the limitation that only a finite number of patterns can be kept. Therefore, to make room for a new pattern, one of the old patterns has to be forgotten. Leveraging the aforementioned limitation, two spy processes can exchange secret messages by placing their stride patterns into the prefetcher and determining whether or not their strides are forgotten at a later time. Demonstrations reveal that attackers can build much more stealthier and high-bandwidth covert channels capable of transmitting information in the order of several tens of KBps with low error-rates [S38].

Modern CPUs are equipped with a range of onboard electronic modules to ensure reliability of the operations despite the changing conditions in the surrounding environment. Among other functionalities, these modules are meant to manage power, regulate voltages, and provide protection against excessive temperature. However, these modules are not devoid of side-channel leakage, through which an adversary can snoop into the inner workings of a CPU core. Typically, in adversarial settings, power and electromagnetic emanations are leveraged either to infer or to affect the inner state of a CPU core [S39].

In the preceding account, we observe that the artefacts leading up to the compromised security and privacy are not limited solely to one specific aspect of the microarchitectures, but typically span across the physical components, such as cache, memory, and registers. Nonetheless, they also span across the executional mechanics of the speculative execution and prefetching. Interestingly enough, the onboard electronics also contribute to the artefact emanations in power consumption and electromagnetic emissions.

# B. RQ2: HOW SOME OF THE RECENT MICROARCHITECTURAL SURFACES WERE CRAFTED AND TURNED INTO FEASIBLE ATTACK CORRIDORS?

In RQ1 (Section VI-A), we presented a high-level overview of the artefacts emanating from the microarchitectural intricacies, which ultimately are leveraged by adversaries to compromise the security and the privacy of the computing systems. In RQ2, we intend to cover the ways, through which the aforementioned artefacts are utilized. To this end, we group the primary studies based on the leaking component and provide a brief account of how the attack corridors are actually created.

#### 1) CACHES

From our set of primary studies (Table 5), microarchitectural cache-attacks compromising security and privacy, appear to be a frequent theme. In the following, we briefly summarize and highlight the aspects, through which this involvement was observed.

Fernando et al. [S70] audit the strength of the cache mapping functions, which map memory addresses to cache sets, through their proposed framework and reveal several vulnerabilities. The study emphasizes that sophisticated mapping functions, which obfuscate the address mapping to cache sets, are needed. The authors pointed out a malicious process can significantly infer the portions of a secret key by indirectly observing the cache sets being accessed during encryptions. However, this approach requires prior knowledge of how the addresses are mapped to the cache sets by the underlying hardware. The cache set mapping is typically performed through specific cache mapping functions, the details of which are often proprietary [30]. Weak cache mapping functions reveal a subset of the address bits that can be inferred by the malicious processes. In this regard, one-to-one mapping functions were found to be the weakest, which can reveal all of the bits of the set index. Moreover, larger memory footprints also leak a significant portion of the cache tag. Thus, information-theoretic security measures for the mapping function are absolutely essential.

Similarly, caches are found to be leaking ongoing data accesses of concurrently executing processes through finegrained timing observations. In such a setting, a malicious process intentionally manipulates the cache contents to either transmit information to a co-collaborating process or to infer

secret data being accessed by a victim process. In such settings, cache access patterns of the spy process happen to conflict with in-cache data being processed by a victim process. Such conflicts lead to data evictions from the cache lines, followed by data loads for the affected process. These events of evictions followed by loads are observable in varying access latency, which can be captured through finegrained time measurements made by a different spy process executing concurrently. To serve the malicious intentions, such time measurements can be leveraged to pinpoint the cache lines being in use by a victim process, which can then be associated with the different portions of the secret data, such as the secret keys. This information leakage through the timing channels is a prevalent threat as caches expose a large attack surface, which is difficult to mitigate. The timing aspect has been of particular focus in few of the primary studies [S67], [S15].

Saeshwar et al. [S36] demonstrate a feasible cache covert channel that, although, works on the principle of flushing a cache-line, does not depend on the native flush instruction (clflush) for this purpose. The authors point out that attacks relying on the flush instruction are known to be some of the fastest ones. However, the reliance on the flush instruction requires the sender and the receiver to be in tight synchronization for maintaining a low error rate. The authors conjuncture that higher data rates could be achieved, if reliable asynchronous coupling between the sender and the receiver could be established. To this end, they observe that sequentially accessing a large-enough address space (comparable to the size of LLC) implicitly triggers cachethrashing operations where previously accessed entries from LLC are automatically evicted to create room for the new requests. Leveraging this property, a covert communication channel between a spy and a receiving process can be created. For this to work, a spy needs to consistently stay ahead and sequentially access the successive addresses in a large array. The receiving process, on the other hand, needs to slightly fall behind and observe the incurred LLC misses. The values of the bits in the communicated messages are inferred from these miss patterns. In reality, speculative execution and prefetchers can cause major disruptions by polluting the cache in the aforementioned scheme. To workaround this limitation, a coarse synchronization, such as once every few thousand accesses, is required between the sender and the receiver.

Thoma et al. [S102] argue on the effectiveness of employing randomization schemes as defences to a variety of cache side-channel attacks. To this end, the authors uncovered a new microarchitectural attack named Write+Write, capable of defeating cache randomization based defences. This attack leverages the Write-after-Write side-effects to establish covert-communication across CPU cores. These side-effects emerge whenever two physical addresses collide in a specific range during memory writes, in a sense when a write request is issued, a subsequent write operation to a nearby address in a specific 10-bit range is notably slower than any other address far out of this range. A predetermined set of addresses within aforementioned range are alternatively read and written such that, when write requests are issued among one of those addresses, a concurrent process reads and measure the time it takes for the rest of these addresses. If a pair of write requests do collide on physical addresses under aforementioned range, notable time difference is observed and vice-versa, this strategy is used to encode and secretly transmit ones and zeros of a covert message. A limitation of presented attack is its practicality stays only over short time periods and its stability is adversely affected by dynamic adjustments made to CPU clock frequency by power management hardware. Nonetheless, the attack demonstrates its usability and effectiveness to circumvent randomization based defense mechanisms.

### 2) MEMORY SUBSYSTEM

Semal et al. [S21] present two novel microarchitectural covert channel attacks, demonstrating a vulnerability surrounding the scheduler of the memory controller. These attacks are particularly potent in the context of cloud-based virtualization environments. The underpinnings of the attack dynamics involve a malicious pair of sender and receiver processes sharing regions of the DRAM banks. The sender process continuously creates some intentional memory-bank conflicts to encode bits of a covert message. These conflicts inadvertently also manifests into observable timing variations as the channel scheduler in memory controller experiences higher latency. The receiver retrieves the covert message through continuously performing uncached memory accesses in a pre-determined memory bank and observes the patterns of latency to infer upon transmitted bits of covert message.

Lindemann et al. [S33] reveal that the memory deduplication mechanism can be exploited by demonstrating that a spy virtual machine can identify the software configurations used by the co-located victim virtual machines sharing the same physical memory. The attacker first establishes the knowledge about the exact subset of the memory pages that would uniquely identify an application as well as its version. Such a subset of the memory pages is referred to as the application signature. The attacker overwrites the signature pages that are believed to be a part of the victim VM. The attacker silently waits for the deduplication to take place, then rewrites the signature pages, and finally measures the time required for these operations. The time measurements serve as an indicator of the pages that have been overwritten during the deduplication. This information is later used to determine whether the application of interest and its corresponding version is present in the victim VM. Similarly, Gulmezoglu et al. [S44] rely on the de-duplication mechanism as a prerequisite step to carry out yet another cross-VM attack on AES implementations.

Semal et al. [S64] describe an inter-process covert channel attack, named memory order buffer (MOB) attack. The attack underpins a side-effect of write-after-read hazard known as 4K-aliasing, which happens whenever the lower 12 bits of a virtual address match during a successive load and store operations. This effect inadvertently re-issues an additional

load operation, which causes the load/store bandwidth to drop momentarily, inducing higher latency. A spy process leverages this effect to encode the ones and zeros of a secret message by allocating a buffer at a page-aligned boundary. A value of one is encoded by filling this buffer. On the other side of the covert channel, a process monitors the trends in observed latency and recovers the encoded message bits accordingly.

Shi et al. [S7] advocate for reliance on general-purpose secure processors in trusted computing environments. Secure processors provide a tamper-proof trusted computing environment and protect information stored in regular memory devices by keeping the data in encrypted form. The authors audit a few contemporary secure processor designs and reveal their proneness to memory-fetch attacks. Although the data remains in an encrypted form inside memory, yet it is decrypted on-the-fly inside the processor during execution. However speculative execution poses a challenge as the instructions and data being fetched ahead of time are being decrypted on-the-fly and lead up to additional fetch requests in plain form on the memory bus. A spy snooping on the system bus can leverage these fetch patterns and selectively corrupt the bits of issued addresses to engineer alternate flows of instruction execution and/or data accesses in effort to disclose sensitive information. The authors propose remedial measures and alternate designs for the speculative pipeline, which incorporate the integrity verification of code and data.

Ravichandran et al. [S100] present a novel yet potent vulnerability, named Pacman. This vulnerability is among first of its class where a pair of individual vulnerabilities are teamed up to break existing security barriers in-place to curate a more potent attack. Interestingly, pacman targets Apple's M1 ARM CPU and defeats an important memory protection mechanism based on pointer authentication. ARM introduced pointer authentication to protect pointer integrity as a security feature, and has been in wide use on variety of systems ever since. A memory pointer is protected through storing a computed hash value alongside its contents. The hash value serves to establish if there has been an unwanted pointer modification performed, presumably by an attacker. Whenever, a pointer is used its integrity is verified by validating aforementioned hash value. An attacker who wants to modify a pointer has to correctly infer the correct hash value after a modification to prevent the system from detecting a pointer tampering. Naive brute force attempts of attacker to infer correct hash value will not work as it would lead to program crash once the system detects a hash mismatch during pointer authentication. However, the attacker synthesizes an oracle which he could utilize during speculative execution phase, alongside an experimental guess of a hash value, and queries the oracle about legitimacy of said value. Upon a correct guess the attacker can proceed with pointer modification and its associated hash value, otherwise the attacker would wait for subsequent speculative phase with a newly guessed hash value. The authors describe a practical and systematic way to craft aforementioned oracle and guess for the hash value. To this end, pacman successfully demonstrated all experimental scenarios of overcoming pointer authentication mechanism and hijacked pointers to execute malicious payloads performing attacks from userspace.

Zang et al. [S103] outline that data-execution prevention, and execute only memory protection are effective security hardening mechanisms to protect critical programs and defend against attacks employing principles of returnoriented programming(ROP) [31]. The study makes an important observation that system call routines lack a subsequent return instruction which is deemed essential for any ROP technique, however, exploiting the signal handler mechanism can circumvent this lack of return instructions. Upon exploitation these system calls can be utilized to assemble a set of ROP gadgets through which a broad range of exploitations can be carried out. However, for presented approach to succeed, syscalls need to be timely interrupted during their execution through signals such as illegal memory access. Carefully crafted illegal memory accesses when carried out, open up an avenue where code segments are stitched together through a set of system calls, to craft a complete microarchitecture attack. The authors demonstrate their approach by successfully carrying out three different scenarios of creating a back-door into a victim system.

#### 3) MICROARCHITECTURAL BUFFERS

Barenghi et al. [S59] investigate the extent of the microarchitectural information leakage attributed to the pipeline buffers. They demonstrate that significant information leakage is observed in the power traces obtained during the computeintensive program executions. The observed leakage turns out to be correlated with the order, in which the registers are allocated for the memory loads and stores, rather than the data dependencies among the instructions. They also observe that minor changes in the order of register allocation can potentially lead to exploitable vulnerabilities. In particular, inter-stage buffers among the issue and execution stage (IS/EX), execution and writeback (EX/WB) stage, ALU output, and memory data registers are the main contributors to the said leakage, which tends to get highly influenced by the order of register allocation. In [S54], the authors also demonstrate the role of the pipeline buffers and the associated functional units in causing power-based information leakage.

Schluter et al. [S71] focus on the role of the short-time buffers in information leakage, which are present on CPU cores. In particular, they investigate the role of the line-fill buffers (LFBs) in harboring microarchitectural data sampling attacks. During speculative execution in the event of page faults, such attacks exfiltrate transient data from concurrent processes executing on the same logical cores. Moreover, the study cites the role of the store buffers, fill buffers, and bus configuration registers, which are prone to leakage.

Kim et al. [S58] present a more potent variant of Meltdown [1] attack by using the return stack buffers (RSBs) to widen the window of transient execution. The proposed exploitation technique enables the establishment of a covert channel without requiring a context switch, providing better tolerance to noise-based countermeasures.

#### 4) TRUSTED EXECUTION ENVIRONMENTS (TEE)

A notable number of primary studies have focused on the vulnerabilities of TEE. Next, we briefly summarize their aspects of exploitation.

Gysenlik et al. [S82] demonstrate, in a novel attack, that legacy features for backward compatibility of x86 instruction set can be leveraged to compromise the security of 32-bit SGX enclave. The attack abuses x86 segmentation unit to reveal enclave memory accesses at the granularity of page level and, in more favorable conditions, even at the byte level. In essence, the proposed attack loads the segmentation unit registers with an engineered configuration, which ultimately causes either a general protection fault or an ordinary page fault. The pattern of page faults reveals the secretinformation-dependent memory accesses inside the enclave. From this information, the structure of the sensitive code doing secret processing is inferred and the control flow can be spied upon. This study is notable in the regard to be the first study to expose avenues for newer attacks exploiting the legacy x86 features, which would remain a part of the Intel CPUs providing backward compatibility in the foreseeable future.

Moghimi et al. [S78] present an attack to retrieve secret information from a SGX enclave. The proposed attack exploits the false dependence of the memory read-after-write operations during serialized accesses of specific 4K-byte memory blocks by a victim process. The victim, which has constant-time code implementation for additional security, performs cryptographic operations inside the enclave and performs frequent enclave-memory operations. The aforementioned serialization causes observable and distinguishable latency patterns, which a spy process ultimately harvests to infer upon the bytes of a secret cryptographic key.

Schwarz et al. [S77] present a practical SGX enclavebased malware, which operates from a compromised enclave. The malicious enclave exploits the SGX enclave protection features to conceal itself from the operating system thus, thwarting the discovery while remaining stealthy. And, the attack can be carried out either against the other co-located enclaves or against the secure docker containers co-located at the same machine. The underpinnings of this attack utilize the Prime+Probe [32] technique to determine the cache-access patterns by observing the memory access latencies, such that an RSA key processed by a victim process can be discovered.

Skarlatos et al. [S32] target the privacy of SGX enclaves through microarchitecture replay attacks. Such attacks rely on hardware support to roll back and re-execute instructions under certain preconditions in a quasi-transient state. The attack details a SGX spy, which exfiltrate secret information from the enclave-private memory of a victim by making it repeatedly replay on page faults. The repeated replays enable the adversary to break the privacy of the enclave and figure out the secret enclave data to the extent possible. The proposed approach positions itself as a potent technique, which can function effectively even in the presence of considerable noise.

Lang et al. [S72] point out the tactics of a malicious adversary having complete control over OS, through which the traffic to and from the outside world to a secure enclave can be influenced. One way is to frequently interrupt and preempt the execution inside an enclave from outside. Such repeated interruptions could potentially cause an enclave to move into some meta states, through which the secret information can be exfiltrated. Moreover, in such a setting, the adversary, being an untrusted OS, can block, delay, replay, and modify all the communications issued from outside the enclave, causing the establishment of a weakened inner state, against which an attack can be carried out.

Han et al. [S23] introduce a covert-channel attack that works across Intel SGX enclaves. The attack exploits a special cache, which is part of the memory encryption engine (MEE) of SGX hardware. The authors observe that the aforementioned cache keeps a portion of the integrity tree storing some enclave-private data. And, it turns out that the number of MEE cache accesses performed during the fetching of this enclave-private data, is directly influenced by the internal state of the tree. The proposed attack follows the footsteps of a typical Prime+Probe attack and systematically forces the integrity tree updates by influencing the MEE cache. The patterns observed through the forced updates are then leveraged to encode and transmit the bits of a secret message across the enclaves.

#### 5) PREFETCHERS

Up until the recent past [5], the microarchitectural attacks targeting the prefetchers in a practical setting were nonexistent. Recently, researchers have exploited the prefetchers after the empirical investigation of their inner workings and leveraged the knowledge gained to craft successful attacks. Next we provide a brief account of these attacks.

Patrick et al. [S38] present a microarchitectural covert channel attack targeting the hardware prefetchers on modern Intel CPUs. The presented attack establishes a bi-directional, high-bandwidth covert channel, which is stealthier and can avoid detection. The attack employs a stride prefetcher to differentiate between accesses to the data blocks with the ultimate goal of figuring out whether the blocks are retrieved from the memory or have been already prefetched into the cache. More specifically, the spy process, which concurrently runs with the victim process, intentionally engineers some sequences of prime and evict operations from the L3 cache to perturb the thus-so-far learned sequences by stride prefetchers. The degree of the perturbation is used to encode the bits of a covert message, which is consequently decoded by the receiving spy process through the monitoring of prefetching behavior.

Note that the prefetchers are used to build a covert channel in the aforementioned study [S38]. Interestingly enough, in the case of cache side-channel attacks, prefetching unintentionally hinders the effectiveness of the attacks. Since the prefetching mechanism speculatively brings data into

the cache, it weakens the attacker's ability to distinguish whether a cache line have been fetched on demand by the victim or have been speculatively brought by the prefetcher for the victim. Wang et al. [S46] point out this shortcoming and present a work-around solution in order to enhance the effectiveness of the cache side-channel attacks, thus making them more potent. The main challenge they address is to understand and reliably model the uncertainty in the prefetching patterns, which originates due to the undisclosed proprietary details of the inner workings of the prefetchers. In the aforementioned work, the authors reverse engineer the inner workings of the Intel CPUs and develop a statistical description of the prefetching mechanism implemented by them. This description is later leveraged to strategically craft and place probes to build the enhanced versions of the cache side-channel attacks. Furthermore, they demonstrate a Flush+Reload [33] attack, which is more potent and equipped with the ability to effectively operate under the disruptive behavior of prefetcher.

Ibrahim et al. [S97] argue that sophisticated interactions among various microarchitecture components give rise to potent and often enable previously undiscovered attacks from userspace. Effective defense and offense often require detailed knowledge of inner-workings of aforementioned components however, such details are usually unpublished for many CPUs. The authors introduce concept of leakage templates, to abstractly describe and identify specific dynamics of known attacks. The presented approach, leverages these abstractions to discover leakage-causing code segments in a binary and once discovered, variants of culprit code segments are synthesized through instruction fuzzing, operand mutation and contextual analysis. Later these synthesized variants are executed on a microarchitecture of interest and changes in the microarchitectural state are observed. Among the observed state space, vulnerable states are identified and the code variant causing it. Equipped with this knowledge, practical exploits for a given microarchitecture are crafted. The approach showcases its strength by uncovering a novel cache eviction and a prefetcher based exploits on an ARM CPU.

#### 6) PCle

Tan et al. [S53] present some attack scenarios by analyzing the patterns in PCIe contention where a spy process can exfiltrate sensitive information spanning from keystroke timings to figuring out the webpages being visited and the machine learning models being used. Note that these attacks are particularly relevant in the settings of cloud computing and data centers where co-resident virtual machines can snoop on each other. The underpinnings of the proposed attack assume a pair of peripheral devices connected to the same PCIe switch, one of which serves under the spy process while the other serves the victim process. The spy is interested in learning the distinguishable patterns in IO latency routed through the PCIe switch. The patterns are later post-processed through a supervised learning approach to infer the victim's state. The spy can intentionally choke the PCIe switch to a degree that causes these patterns to emerge as a side-effect to the intermediate buffering of reliable data transfers.

# 7) PERFORMANCE COUNTERS AND GPUs

Graphical Processing Units (GPUs) became one of the musthave components of modern computer systems, which are meant to provide enhanced capabilities and performance for graphical workloads. However, besides graphics processing on modern systems, they can be employed to process intensive workloads such as scientific computation and machine learning applications. The flexibility of the GPUs for the aforementioned purposes is achieved through leveraging the GPU APIs (application programming interfaces). The internal registers of GPU capable of monitoring and profiling executions, are also made available in these APIs. Although a GPU can serve multiple workloads through time sharing, a workload with malicious intentions can abuse the microarchitectural components of a GPU to establish a sidechannel.