Received 31 March 2023, accepted 2 May 2023, date of publication 8 May 2023, date of current version 16 May 2023. Digital Object Identifier 10.1109/ACCESS.2023.3274487

# **RESEARCH ARTICLE**

# **Open-RAN Fronthaul Transport Security Architecture and Implementation**

# DANIEL DIK<sup>©1,2</sup>, (Graduate Student Member, IEEE), AND MICHAEL STÜBERT BERGER<sup>©2</sup>, (Member, IEEE)

<sup>1</sup>Comcores ApS, 2800 Kongens Lyngby, Denmark

<sup>2</sup>Department of Electrical and Photonics Engineering, Technical University of Denmark, 2800 Kongens Lyngby, Denmark

Corresponding author: Daniel Dik (danro@dtu.dk)

This work was supported in part by Comcores ApS, and in part by Innovationsfonden Denmark under Grant 0153-00126A.

**ABSTRACT** The main innovations for next-generation cellular networks are in the Radio Access Network (RAN). Here, the base station functionalities are split between a Radio Unit (RU) and a Distributed Unit (DU), resulting in a virtualized architecture where functions can be centralized close to the core for performance improvement and function extendibility. The fronthaul is the interface between RUs and DUs. It transports very sensitive data and is constrained by strict performance requirements. The clear-text nature of the fronthaul protocols and its direct encapsulation over Ethernet exposes the fronthaul to Layer 2 threats and vulnerabilities that can significantly threaten the operation of the RAN. This paper presents a detailed analysis of the transport network security in the fronthaul. It describes the threats and vulnerabilities that the fronthaul is exposed to and their overall network impact, thereby, elucidating the urgent need for Layer 2 security mechanisms. This paper introduces MACsec as a potential solution to protect the fronthaul. It outlines MACsec's capabilities and limitations for threats protection, and its implementation challenges in the fronthaul network. Finally, this paper proposes three hardware architectures to fully secure the fronthaul using MACsec and evaluates their feasibility in Field-Programmable Gate Array (FPGA) devices and their impact on the network performance.

**INDEX TERMS** FPGA, Fronthaul, MACsec, open-RAN, security.

#### **I. INTRODUCTION**

The fifth generation (5G) and future cellular network specifications are driven by non-consumer services applications. These include massive Machine-Type Communications (mMTC), such as support for billions of Internet of Things (IoT) devices, and Ultra-Reliable Low Latency Communications (URLLC) applications, for example, industrial automation and autonomous vehicles [1], [2]. 5G also provides a range of improvements for faster mobile broadband services. To support all these new verticals, there is a need for network architecture innovations in the Core Network (CN) and in the Radio Access Network (RAN). This includes Cloud RAN, Virtual RAN, Open RAN, Service-based CN architecture, Software Defined Networking (SDN), Network Function Virtualization (NFV), network slicing, and cloud

The associate editor coordinating the review of this manuscript and approving it for publication was Miguel López-Benítez<sup>(D)</sup>.

and edge computing [3], [4]. The convergence of these and more technologies promises great innovation in the network and in the applications that it can serve. However, it also leads to a larger attack surface where the exploitation of threats and vulnerabilities could cause the network to malfunction [5], [6]. Therefore, there is an urgent need to analyze all the security aspects across the whole 5G system, including threats to the user equipment, air interface, edge network, backhaul connectivity, core network, and external networks.

One of the main innovations for 5G and next-generation networks is in the RAN where the base station functionalities are split [7]. This leaves only a few physical functionalities in the antenna location which results in a new RAN virtualized architecture where functions can be centralized close to the 5G core. Therefore, resource sharing between Radio Units (RUs) is possible. This enables simpler RUs implementation requirements and easier function extendibility, which makes it possible for multiple vendors to provide base station solutions. However, additional specifications are needed to ensure interoperability.

The need for further specifications has given rise to various Open RAN initiatives. The most prominent is the Open-RAN (O-RAN) Alliance [8]. The O-RAN Alliance was established in 2018 and unites mobile network operators, vendors, and research and academic institutions from all around the world to standardize the RAN as an open, intelligent, virtualized, and fully interoperable ecosystem. The O-RAN Alliance defines RAN specifications with an emphasis on interfaces and implementation guidelines. Specifically, those which are not detailed in the 3rd Generation Partnership Project (3GPP) recommendations and are important for interoperability. This will result in the sourcing of network infrastructure components from different suppliers, ensuring interoperability, and driving higher innovation at lower costs.

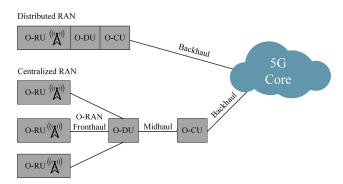

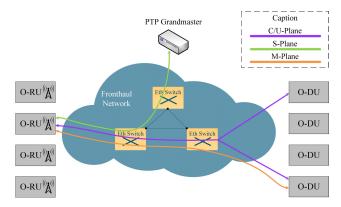

The architecture for the New Radio that the O-RAN Alliance has defined is based on functional split option 7-2x of the baseband station processing chain [9]. This results in a redistribution of lower and higher layer functionalities between new O-RAN components as illustrated in Fig. 1. The base station is divided into two units. The O-RAN Radio Unit (O-RU) implements lower physical functions. The O-RAN Distributed Unit (O-DU) implements higher physical functions. The connectivity in the O-RAN infrastructure between these two units is the O-RAN Fronthaul (O-FH). The O-FH carries very sensitive information between the O-RU and the O-DU. This information is divided into four data planes; Control Plane, User Plane, Synchronization Plane, and a Management Plane. These data planes impose strict highperformance requirements.

**FIGURE 1.** O-RAN transport network architecture. Split of base station functionalities results in new RAN units, O-RU implementing lower physical functions, and O-DU implementing higher physical functions, with the O-FH as the interface between them.

Ethernet is the preferred packet-based technology for the transport of the data planes traffic in the O-FH. This is because of its ubiquitous applications and the ability to mix different types of traffic. Consequently, the Common Public Radio Interface (CPRI) in 4G LTE between the Remote Radio Unit (RRU) and BaseBand Unit (BBU) has been replaced by the Ethernet-based enhanced CPRI (eCPRI) interface for radio control and user data.

The clear-text nature of the data planes and its direct encapsulation over Ethernet exposes the O-FH to Layer 2 threats and vulnerabilities that can significantly risk the operation of the RAN. For example, a Man-in-the-Middle could impersonate a legitimate synchronization message and inject a false clock into the network causing a degradation of the time service. This can result in a complete Denial-of-Service of the network. Hence, there is an urgent need for Data Link Layer security mechanisms to protect the O-FH from any type of threat.

An O-RAN Alliance Security Work Group had been put together to address the security aspects of the O-RAN Architecture. Its core objective is to define security specifications for each component and interface. As recognized in the O-RAN Security Threat Modeling and Remediation Analysis 4.0, the O-FH interface has its own specific threats and vulnerabilities [12]. The most recent specifications from October 2022 have greatly advanced the security needs of the industry. They have defined security requirements that are focused mainly on authentication and less on confidentiality and integrity concerns. However, based on the identified threats and vulnerabilities, confidentiality and integrity are equally important. On the other hand, another Work Group within the O-RAN Alliance defines no requirements for security. They argue that the high requirements for delay, time, and bandwidth in the O-FH do not permit security solutions to be used [10].

Media Access Control Security (MACsec) is a Layer 2 security protocol standardized by the IEEE that operates on Ethernet frames [13]. Its features of authentication, confidentiality, and integrity make it a potential candidate to protect the O-FH. However, the O-FH has multiple requirements that could challenge the use of MACsec. These requirements can be divided into two groups: security and performance. Security requirements are the security features that are indispensable for the O-FH to be protected against potential threats and attacks. Performance requirements are the network aspects of the O-FH for its operation, such as network topologies and data protocols.

The main challenges that are essential for MACsec to address are a) the compatibility of MACsec security functions with all the threats in the O-FH transport network, and b) the impact of MACsec on the performance of the different O-FH topologies and protocols. While MACsec may provide the necessary features to protect the O-FH, it could limit the operation of the protocols under the various possible topologies. Thus, the capability of MACsec to fully secure the O-FH while satisfying its requirements needs to be analyzed [14].

The literature on the security of 5G networks suggests that there are potential threats to the O-FH that may be protected by MACsec because of the suitability of its security features [15], [16]. However, the literature lacks a comprehensive analysis of those threats and their precise impact on the O-FH network. Furthermore, the specific compatibility of MACsec with the O-FH has not been fully investigated. This includes the challenges it faces in respecting the strict performance requirements. White papers exist with commercial MACsec solutions for Ethernet networks [17], [18]. However, these are proprietary solutions without a detailed description of their design, and without a clear analysis of their applicability for the O-FH scenario. Therefore, this work aims to address these gaps by providing the following contributions.

# A. CONTRIBUTIONS

This paper has three main contributions. First, it provides a detailed analysis of the transport network security in the O-FH interface between O-RUs and O-DUs. It identifies a number of threats for the different O-FH protocols and proposes the security features that are indispensable to protect the O-FH. Second, this paper provides a comprehensive study of the applicability of MACsec as a security protocol to protect the O-FH, including the benefits and limitations of MACsec to secure the O-FH while respecting its performance and operation. Finally, this paper proposes a MACsec hardware architecture for the O-FH that meets its security and performance requirements. It evaluates the feasibility of the architecture for its implementation on Field-Programmable Gate Array (FPGA) devices and for its impact on the network performance.

# B. OUTLINE OF THE PAPER

The remaining part of this paper is organized as follows. Section II presents the O-FH including the types of data it transports, the encapsulation protocols that are involved, and their strict performance requirements. Section III analyzes each type of traffic being transported in the O-FH and identifies the different threats and vulnerabilities an attacker can exploit to impact the network. Section IV presents MACsec as a Data Link Layer security solution. Section V makes a thorough analysis of the compatibility of MACsec with the O-FH, including the challenges and limitations that MACsec faces to protect it from all the identified threats, and to respect its strict performance requirements. Section VI proposes three hardware architectures to fully secure the O-FH using MACsec taking into account the identified challenges and limitations. Sections VII and VIII evaluate these architectures under different performance metrics to demonstrate the possibility of O-FH protection while meeting its strict performance requirements. Finally, the conclusions are presented in Section IX.

# II. OPEN-RAN FRONTHAUL

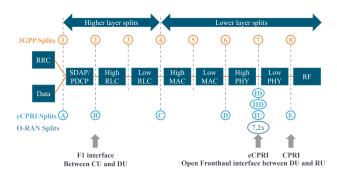

The RAN processing functions can be split at various points as illustrated in Fig. 2 [19]. This enables the functionality to be deployed at various points in the network. Lower layer splits enable simpler, more compact, and lower-cost RU implementations as only the RF and lower physical layer functions need to be supported. Since 5G will require an order of magnitude increase in the number of RUs to be deployed, this can lower deployment costs significantly.

The functional splits also provide flexibility when deploying functionality. This allows specific service performance

FIGURE 2. Split options of RAN processing functions. The O-RAN Alliance has defined split 7.2x based on the eCPRI interface.

requirements to be met. For example, efficient aggregation can be provided by centralizing the virtualized CU and DU functionality as close to the core as possible. On the other hand, if lower latency is required, the CU and DU functionality should be located as close to the RUs as possible.

The F1 interface between the CU and DU is defined in 3GPP specifications. However, the O-FH interface between the DU and RU is not defined. This means it has been proprietary to the vendor in previous mobile network generations. The O-RAN Alliance has defined split 7.2x of base station functionalities with O-FH interface specifications that enable multivendor operation [10]. This is based on the eCPRI interface that replaced the CPRI interface in 4G LTE between the RRU and the BBU.

## A. DATA PLANES

The O-FH carries very sensitive information between O-RU and O-DU. This information is divided into four data planes as illustrated in Fig. 3:

- Control Plane (C-Plane): real-time control information to the O-RU over eCPRI to define how the User Plane traffic should be handled.

- User Plane (U-Plane): real-time uplink and downlink IQ data samples transferred over eCPRI of the traffic that goes over the air.

- Synchronization Plane (S-Plane): periodically timing and synchronization messages over IEEE 1588 Precision Time Protocol (PTP) to synchronize the O-RU to the network.

- Management Plane (M-Plane): non-real-time management and configuration NETCONF/YANG-based operations.

FIGURE 3. O-FH data planes between O-RU and O-DU. CU-Planes are transported over eCPRI, S-Plane over PTP, and M-Plane over NETCONF/YANG-based operations.

# **B. PERFORMANCE REQUIREMENTS**

The full set of performance requirements according to the CUSM-Planes protocols for the transport network has been

| TABLE 1. O-FH transport performance require | rements for the CUSM-Planes. |

|---------------------------------------------|------------------------------|

|---------------------------------------------|------------------------------|

| Latency Transport Delay                    |                                                                                                                                                                           |                                    |                                                                                       |              |                |                 |  |  |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------|--------------|----------------|-----------------|--|--|

| Latency<br>Class                           | Max one-way<br>Frame Delay                                                                                                                                                | Max one-way<br>Frame Loss<br>Ratio | Use case                                                                              |              |                |                 |  |  |

| High25                                     | 25 us                                                                                                                                                                     | 10-7                               | Ultra-low latency performance                                                         |              |                |                 |  |  |

| High75                                     | 75 us                                                                                                                                                                     | <b>10</b> <sup>-7</sup>            | For full NR performance with fiber lengths in 10km range                              |              |                |                 |  |  |

| High100                                    | 100 us                                                                                                                                                                    | 10-7                               | For standard NR performance with fiber<br>lengths in 10km range                       |              |                |                 |  |  |

| High200                                    | 200 us                                                                                                                                                                    | <b>10</b> <sup>-7</sup>            | For installati<br>range                                                               | ons with     | fiber leng     | gths in 30km    |  |  |

| High500                                    | 500 us                                                                                                                                                                    | 10-7                               | Large latency installations > 30 km                                                   |              |                |                 |  |  |

| Medium                                     | 1 ms                                                                                                                                                                      | 10 <sup>-7</sup>                   | U-Plane (slow)<br>C/M-Planes (fast)                                                   |              |                |                 |  |  |

| Low                                        | 100 ms                                                                                                                                                                    | <b>10<sup>-6</sup></b>             | C/M-Plane                                                                             |              |                |                 |  |  |

| Bandwidth Transport Dimension              |                                                                                                                                                                           |                                    |                                                                                       |              |                |                 |  |  |

| Number of<br>sectors                       | Frequency<br>Band                                                                                                                                                         | CBW<br>(MHz)                       | MIMO<br>Layers                                                                        | ABW<br>(MHz) | FH BW<br>(MHz) | FH<br>Interface |  |  |

|                                            | Sub 6<br>C-band                                                                                                                                                           | 100                                | 4                                                                                     | 400          | 7.5            | 1 x 10Gbps      |  |  |

| 1                                          | mmWave<br>39 GHz                                                                                                                                                          | 400                                | 2                                                                                     | 800          | 14.57          | 1 x 25Gbps      |  |  |

|                                            | Sub 6<br>C-band                                                                                                                                                           | 100                                | 4                                                                                     | 1200         | 22.6           | 3 x 10Gbps      |  |  |

| 3                                          |                                                                                                                                                                           |                                    | 16 (massive<br>MIMO)                                                                  | 4800         | 90.4           | 4 x 25Gbps      |  |  |

|                                            | mmWave<br>39 GHz                                                                                                                                                          | 400                                | 4                                                                                     | 4800         | 87.4           | 4 x 25Gbps      |  |  |

|                                            |                                                                                                                                                                           | Time error bud                     | lget allocatio                                                                        | n            |                |                 |  |  |

| Timing<br>Reference                        | Transport<br>network<br>contribution                                                                                                                                      | O-RU                               | Air interface target                                                                  |              |                |                 |  |  |

| At O-DU<br>For LLS-C1:                     | $ \mathbf{TE}  \le 140 \text{ ns}$ Enhanced<br>$ \text{TE}  \le 35 \text{ ns}$ Absolute $ \text{TAE}  \le 1.5 \text{us}$ between ante Category C: for Time Division Duple |                                    |                                                                                       |              |                |                 |  |  |

| TE ≤1.420μs<br>For LLS-C2:<br> TE ≤1.325μs | TE  ≤ 95 ns                                                                                                                                                               | Regular<br> TE  ≤ 80 ns            | Inter-band carrier aggregation or NR Intra<br>band non contiguous carrier aggregation |              |                |                 |  |  |

TE: Time Error, TAE: Air Interface Time Error, LLS-C1: point-to-point fronthaul between O-RU and O-DU, LLS-C2: network of switches fronthaul between O-RU and O-DU.

specified by the O-RAN Alliance in [10]. A summary of these requirements, presented in Table 1, consists of frame loss ratio, frame delay, bandwidth, and synchronization accuracy.

#### C. TRANSPORT ENCAPSULATION

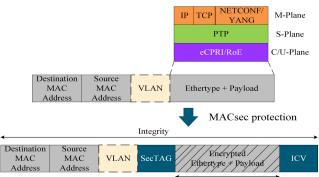

Ethernet is the selected packet-based technology for the O-FH transport network because of its ubiquitous applications and the ability to mix different types of traffic [11]. The encapsulation of CUSM-Planes packets is illustrated in Fig. 4. The CUS-Planes are encapsulated directly over Ethernet, while the M-Plane is transported over TCP and IP. There are some scenarios where the CU-Planes may be transported over UDP and IP [10].

The clear-text nature of the data planes encapsulated directly over Ethernet makes the O-FH vulnerable to Layer 2 threats. Thus, each data plane requires an independent threat analysis based on its type of content.

#### **III. THREAT ANALYSIS**

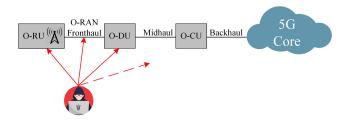

This section analyzes each type of traffic being transported in the O-FH interface and identifies the different threats and vulnerabilities an attacker can exploit to impact the network. Fig. 5 illustrates the threat scenario under analysis. This study

FIGURE 4. O-FH data planes encapsulation over Ethernet. CU-Planes can optionally be transported over UDP and IP for some scenarios. S-Plane PTP messages are directly encapsulated over Ethernet for full-timing support, and the M-Plane messages over TCP and IP.

focuses on the O-FH scenario where the transport of data is encapsulated directly over Ethernet. Hence, the security analysis corresponds to Layer 2 threats on Ethernet ports and frames. This occurs by the premise that an attacker has direct access to the physical port of the O-FH device, with the possibility to add its own device, either to inject its own Ethernet traffic or to perform Man-in-the-Middle attacks. An attacker can either be internal or external. An internal attacker resides within the premises of the O-RU, O-DU, or intermediate switches with access to a trusted segment or with the ability to exploit site vulnerabilities. An external attacker physically intercepts the O-FH interface link from outside the premises. These types of attacks are feasible to occur due to the available physical access to ports in the different components, especially in multi-provider networks where absolute control of the network is limited. Examples of these networks are when the O-RU, O-DU, or intermediate switches are managed by different suppliers, such as Carrier Ethernet service providers.

Layer 2 access gives an attacker the capacity to eavesdrop on all traffic in the O-FH link. This can lead to tampering of the data planes protocols and the appearance of being operational but with intentionally inaccurate information. Without any security mechanism, an attacker can access and identify hosts, types of traffic, and packet contents. This allows him to inject false messages by impersonating a legitimate node, corrupting a legitimate message, and replaying or delaying a legitimate message. All of these threats have different consequences to the RAN depending on the data plane under attack.

#### A. CONTROL AND USER PLANES

The CU-Planes are based on eCPRI messages [20], [21]. The eCPRI payload data contains a C-Plane or U-Plane packet based on the eCPRI message type. There are multiple types of C-Plane messages, named Section Types, each with different message content depending on what information the C-Plane describes. For this threat analysis, C-Plane Section Type 1 is chosen as it is the one used for most data. A C-Plane message contains multiple sections of control information, also named section descriptions. A U-Plane message contains the user data divided into sections, each corresponding to a specific beam or antenna.

FIGURE 5. O-FH attack scenario; an attacker internal or external with legitimate access to the O-FH interface, or exploiting device vulnerabilities.

When an attacker has Layer 2 access in the O-FH, it can inject its own eCPRI messages or corrupt specific fields of legitimate eCPRI packets. Corruption may occur through the eavesdropping of all traffic and identifying eCPRI messages based on their corresponding Ethertype value of 0xAEFE. An attacker can perform these attacks by targeting different message types and packet fields. The manipulation of these fields has a diverse impact on the O-FH network.

A summary of all the identified threats for the CU-Planes eCPRI traffic is detailed on the left side of Table 2. The overall impact of these threats is a possible degradation or Denial-of-Service in the RAN. Therefore, there is a need for Layer 2 security mechanisms to protect the CU-Planes traffic from the aforementioned threats. These mechanisms must include the following four features: authenticity, confidentiality, integrity, and replay protection. Authenticity ensures that only legitimate O-RUs and O-DUs are communicating between them. Confidentiality keeps the eCPRI header and payload hidden. Integrity identifies if any eCPRI message has been corrupted. Finally, replay protection ensures in-order delivery of eCPRI messages.

#### **B. SYNCHRONIZATION PLANE**

The synchronization of O-FH units is based on PTP messages [22], [23]. PTP distributes very precise clock reference to O-DU and O-RU in the O-FH network. There are five types of PTP clock devices:

- Ordinary Clock: device with a single port that acts as a Master or a Slave clock.

- Boundary Clock: device with multiple ports that acts as a Master or a Slave clock.

- End-to-End Transparent Clock: device with multiple ports that acts as a bridge between Master and Slave. It forwards and corrects all PTP messages by adding the bridge residence time into a correction field.

- Peer-to-Peer Transparent Clock: device with multiple ports that acts as a bridge between Master and Slave. It forwards and corrects only Sync and Follow-up messages by adding the bridge residence time plus the peerto-peer link delay into a correction field in the message.

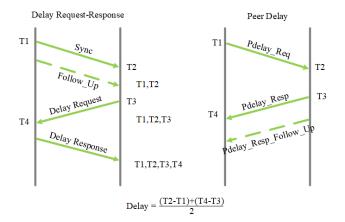

Master and slave devices are kept synchronized by time-stamps generated both at the transmission and reception of PTP messages. The link delay measurement calculation, illustrated in Fig. 6, can be based on the Delay Request-Response mechanism or the Peer Delay mechanism. Ports on Ordinary or Boundary clocks can use either of these mechanisms. Ports on End-to-End Transparent Clocks are independent of these mechanisms, and ports on Peer-to-Peer Transparent Clocks can only use the Peer Delay mechanism.

FIGURE 6. PTP delay calculation options; Delay Request-Response mechanism and Peer Delay mechanism.

The O-FH network can vary from a point-to-point topology to a network of switches as illustrated in Fig. 7. These are necessary to address different deployment market needs. With Full Timing Support the synchronization master is located at the O-DU, all Ethernet Switches function as boundary clock or transparent clock, and the O-RU operates as a slave and/or boundary or transparent clock [10].

FIGURE 7. O-FH topology; it can vary from a point-to-point O-FH interface between O-RU and O-DU, to a network of switches O-FH interface.

Similar to the CU-Planes, when an attacker has Layer 2 access in the O-FH, it can inject its own PTP messages or eavesdrop on all traffic and identify all PTP messages based on its corresponding Ethertype value of  $0 \times 88$ F7. An attacker can perform these attacks by targeting different message types and packet fields. The manipulation of these fields has a diverse impact on the O-FH network.

A summary of all the identified threats for the S-Planes PTP traffic is detailed in Table 2. These threats can result in synchronization mismatching between components of the

| TABLE 2. | Summary of | layer 2 | threats in | the O-RAN | fronthaul. |

|----------|------------|---------|------------|-----------|------------|

|----------|------------|---------|------------|-----------|------------|

|          | Data Plane       | Threat                                     | Packet Field                                                                                                                                                                                                                                                                            | Impact                                                                                                                                                                                                         | C                                | MACsec Security Capabilities |                 |           |                      |

|----------|------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------|-----------------|-----------|----------------------|

| Protocol |                  |                                            |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                | Security<br>Requirement          | Authentication               | Confidentiality | Integrity | Replay<br>Protection |

|          | Control and User | Eavesdropping                              | type                                                                                                                                                                                                                                                                                    | Identification of eCPRI CU-Planes messages for<br>further packet manipulation                                                                                                                                  | Confidentiality                  |                              | ~               |           |                      |

|          |                  |                                            | protocol revision,<br>message type                                                                                                                                                                                                                                                      | Packet discard or cause corrupted processing that<br>leads to later discarding                                                                                                                                 | Confidentiality<br>and Integrity |                              | ~               | ~         |                      |

|          |                  | Packet<br>manipulation                     | payload size                                                                                                                                                                                                                                                                            | Parser error and potential stall or corruption in the O-<br>DU or O-RU                                                                                                                                         |                                  |                              | ~               | ~         |                      |

|          |                  |                                            | dataDirection                                                                                                                                                                                                                                                                           | Packet drop                                                                                                                                                                                                    |                                  |                              | ✓               | ✓         |                      |

|          |                  |                                            | filterIndex                                                                                                                                                                                                                                                                             | Incorrect filter applied causing erroneous processing                                                                                                                                                          |                                  |                              | ✓               | ✓         |                      |

|          |                  |                                            | frameID,<br>subframeID,<br>slotID,<br>startSymbolid                                                                                                                                                                                                                                     | Timing-related content that cause packets to be<br>received outside the reception window and be<br>discarded                                                                                                   |                                  |                              | *               | ~         |                      |

|          |                  | Packet drop,<br>delay or<br>retransmission | All                                                                                                                                                                                                                                                                                     | Packet is received outside reception window and discarded, leading to degradation on the air interface                                                                                                         | Replay and delay protection      |                              |                 |           | Partial              |

|          |                  | Packet injection                           | Section<br>Description fields                                                                                                                                                                                                                                                           | Cell becomes unreliable. O-RU incorrectly allocates<br>or unallocates data on the air interface causing it to<br>glitch out for a particular slot duration or persistenly                                      | Authentication                   | ~                            |                 |           |                      |

| eCPRI    |                  |                                            | udCompHdr                                                                                                                                                                                                                                                                               | Incorrect or unsupported compression applied                                                                                                                                                                   | Confidentiality<br>and Integrity |                              | ✓               | ×         |                      |

|          |                  | Packet<br>manipulation                     | sectionId, rb,<br>symInc, startPrbc,<br>numPrbc, reMask                                                                                                                                                                                                                                 | Control messages will not be applied to the correct<br>U-Plane data causing glitching on the air interface                                                                                                     |                                  |                              | $\checkmark$    | ~         |                      |

|          |                  |                                            | ef                                                                                                                                                                                                                                                                                      | Parsing issue that can corrupt the O-RU                                                                                                                                                                        |                                  |                              | ✓               | ✓         |                      |

|          |                  |                                            | beamId                                                                                                                                                                                                                                                                                  | Incorrect beam is selected leading to poor performance for that particular data allocation                                                                                                                     |                                  |                              | ~               | ~         |                      |

|          | User             | Packet injection                           | Section fields                                                                                                                                                                                                                                                                          | Data become overwritten with the contents of the<br>false packets, causing glitching on the air interface<br>and requiring retransmissions to and from UEs                                                     | Authentication                   | ~                            |                 |           |                      |

|          |                  | Packet<br>manipulation                     | sectionId                                                                                                                                                                                                                                                                               | Mismatch of U-Plane and C-Plane messages in DL<br>causing the message to be dropped entirely                                                                                                                   | Confidentiality<br>and Integrity |                              | ~               | ~         |                      |

|          |                  |                                            | rb, startPrbu,<br>numPrbu                                                                                                                                                                                                                                                               | U-Plane data will not be applied correctly to the air<br>interface causing glitching and drops, or<br>retransmissions at higher layers                                                                         |                                  |                              | ~               | ~         |                      |

|          |                  |                                            | udCompParam                                                                                                                                                                                                                                                                             | Incorrect decompression causing errors on the air<br>interface                                                                                                                                                 |                                  |                              | ~               | ~         |                      |

|          |                  |                                            | iSample, qSample                                                                                                                                                                                                                                                                        | Corruption of the air interface may occur requiring<br>retransmissions at higher layers for recovery                                                                                                           |                                  |                              | ~               | ~         |                      |

| PTP      | Synchronization  | Packet injection                           | Announce message                                                                                                                                                                                                                                                                        | Manipulation of the master election process, causing<br>the switches and O-RU to believe the source is the<br>most eligible candidate to be a clock grandmaster                                                | Authentication                   | ~                            |                 |           |                      |

|          |                  |                                            | et injection<br>Event and General<br>messages<br>Event and General<br>messages<br>Event and General<br>False slave clock i<br>port in a switch ca<br>information to leg<br>switches port and<br>False slave clock i<br>port in a switch ca<br>clock in the O-DU<br>clock that results i | False master clock impersonating an O-DU or a BC<br>port in a switch can distribute false timing<br>information to legitimate slave clocks in BC<br>switches port and O-RU                                     |                                  | V                            |                 |           |                      |

|          |                  |                                            |                                                                                                                                                                                                                                                                                         | False slave clock impersonating an O-RU or a BC<br>port in a switch can respond to a legitimate master<br>clock in the O-DU or BC switches port with a false<br>clock that results in wrong delay computations |                                  | ~                            |                 |           |                      |

|          |                  | Eavesdropping                              | Ethertype                                                                                                                                                                                                                                                                               | Identification of PTP messages for further packet manipulation                                                                                                                                                 | Confidentiality                  |                              | ~               |           |                      |

|          |                  | Packet<br>manipulation                     | Timing fields                                                                                                                                                                                                                                                                           | Incorrect values causing wrong delay computations that impacts the synchronization accuracy                                                                                                                    | Confidentiality<br>and Integrity |                              | ~               | ~         |                      |

|          |                  | Packet drop,<br>delay or<br>retransmission | All                                                                                                                                                                                                                                                                                     | Inaccurate timing information in the fronthaul<br>network impacting the synchronization accuracy                                                                                                               | Replay and delay protection      |                              |                 |           | Partial              |

O-FH network that can lead to a degradation or interruption of the clock service and a complete Denial-of-Service of the RAN. Therefore, Layer 2 security mechanisms are indispensable to protect the S-Plane. Similar to the CU-Planes, the security features of authenticity, confidentiality, integrity, and replay protection are required for the S-Plane. Here, authenticity ensures that only legitimate clock devices are communicating between them. Confidentiality keeps the PTP header and payload hidden. Integrity identifies if any PTP message has been corrupted. Finally, delayreplay protection ensures in-order on-time delivery of PTP messages.

# C. MANAGEMENT PLANE

The M-Plane does not run directly over Ethernet but uses TCP/IP [24]. TLS is, thus, used to secure M-Plane messages. Nevertheless, targeted attacks at the Ethernet layer can still impact the M-Plane in similar ways to the other data planes discussed above. Ethernet frames can be corrupted, delayed, dropped or replayed and thereby disrupt the management and configuration of O-RAN components. Therefore, the same Layer 2 security mechanisms are recommended for the M-plane to complement the protection implemented with TLS. These measures can add an additional layer of protection against potential TLS vulnerabilities.

#### D. O-RAN ALLIANCE SECURITY SPECIFICATIONS

The O-RAN Alliance Security Focus Group (SFG) made its first announcement on October 24, 2020, introducing planned SFG activities and a roadmap [25]. In the announcement, the O-RAN Alliance recognized the need to secure important interfaces including the O-FH interface. The new and updated security specifications from October 2022 greatly progress their mission to address the security concerns of the industry. The O-RAN Security Threat Modeling and Remediation Analysis 4.0 notes that there are specific threats and vulnerabilities associated with the O-FH interface [12]. We expanded upon these threats in detail in the previous sections of this paper. The O-RAN Security Requirements Specification 4.0 defines specific requirements for the O-CU and the O-FH [26]. However, the specifications for O-RUs and O-DUs are yet to be defined. Based on the threats and vulnerabilities they identified, the requirements for the O-FH interface specifically addressed the CS-Planes. For the U-Plane, the document states that the U-Plane user data traffic is protected by higher layer security mechanisms in PDCP implemented in the O-CU protecting both C-Plane and U-Plane traffic between the O-CU and UE. However, the document also states that many of the OEMs have not implemented those security measures because of their impact on the user experience. Security of the M-Plane is addressed in the O-RAN Alliance O-RAN Management Plane Specification 10.0 from October 2022 where it is stated that "An O-RU shall support sFTP based file transfer over SSH and FTPES based file transfer over TLS [24]. For the O-DU, the operator may use SSH, TLS, or both". Therefore, their requirements have generally focused on authentication and less on confidentiality and integrity concerns. However, based on the threats and vulnerabilities we have identified in the preceding sections, confidentiality and integrity are equally important. This is especially true at the Data Link Layer due to the clear-text nature of the CUS-Planes protocols and its direct encapsulation over Ethernet.

A key protection method being considered for O-FH protection by the O-RAN Alliance is MACsec, a standardized Layer 2 security protocol [27]. However, the current discussion hypothesizes that MACsec would not meet split Option 7-2x requirements for stringent bandwidth, tight latency, and hard absolute and relative time error. Additionally, a full analysis of how MACsec can protect the O-FH is still necessary. The following sections of this paper contribute to the O-RAN SWG work by showing that MACsec can address the highlighted threats and vulnerabilities while respecting the strict performance required in the O-FH.

#### **IV. DATA LINK LAYER SECURITY: MACSEC**

MACsec is a Layer 2 security protocol standardized by the IEEE in the 802.1AE standard [13]. It protects communication between components of a Local Area Network (LAN) and, thus, operates on Ethernet frames. Each port of a component that is capable of participating in a MACsec instance

comprises both a control plane Key Agreement Entity (KaY) and a data plane Security Entity (SecY). Each KaY implements the MACsec Key Agreement protocol (MKA) [28]. MKA is a companion protocol that discovers or is made aware of the KaYs presence in the other stations attached to the same LAN. It ensures that those stations are mutually authenticated and authorized. Furthermore, the MKA creates and maintains secure relationships between the stations that are used by the SecYs to transmit and receive frames. The SecY operates on a frame-by-frame basis using Advanced Encryption Standard with Galois Counter Mode (AES-GCM) cryptography according to the configuration parameters set by the KaY. AES-GCM provides authenticated encryption and the ability to check the integrity and authentication of additional authenticated data that is sent in the clear. AES-GCM is specified by the NIST in [29], [30].

#### A. SECURITY RELATIONSHIPS

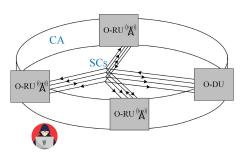

When devices that support MACsec are added to a LAN, they use the MKA protocol to create a Connectivity Association (CA). The MKA protocol is based on the IEEE 802.1X Extensible Authentication Protocol over LAN (EAPoL) that uses Ethernet-based messaging with Ethertype  $0 \times 888E$ . Before the MKA process starts, all MACsec peers' KaYs possess the same Connectivity Association Name (CAN) and Connectivity Association Key (CAK). When the MKA process starts, all MACsec peers are mutually authenticated using the CAN and the CAK, and a CA association is created. A KaY-SecY can be part of only one CA at any time. Peers present to each other their MACsec capabilities and a long-lived Secure Channel (SC) is created for each station SecY providing unidirectional point-to-multipoint communication. Each SC is identified by a Secure Channel Identifier (SCI) comprising a 48-bit MAC address concatenated with a 16-bit Port Identifier. For key rotation during MACsec operation, the SCs persist through the succession of short-lived Secure Associations (SA). A SA, identified by a two-bit Association Number (AN), consists of a unique Secure Association Key (SAK) and a Packet Number (PN) counter. Throughout the MACsec operation, each frame uses a different PN, and once the PN counter reaches its maximum value, the SC swaps to a new SA. As a result, different SAKs are used in the cryptography process. The MACsec security relationships between O-FH components are illustrated in Fig. 8.

#### **B. SECY OPERATION**

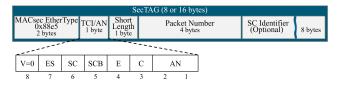

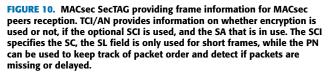

MACsec, through the SecY, provides security features of data confidentiality and integrity to Ethernet frames as illustrated in Fig. 9. It adds a header and tail to each frame. The header consists of a Security Tag (SecTAG) as illustrated in Fig. 10. The SecTAG includes a MACsec Ethertype  $0 \times 88E5$  and frame-specific MACsec parameters, such as the TAG Control Information (TCI). The tail consists of the Integrity Check Value (ICV). When MACsec is enabled, the entire frame is always integrity protected and validated through the ICV,

**FIGURE 8.** O-RAN components secured with MACsec; CA and SCs between O-RUs and O-DU. Each SC persists through the succession of short-lived SAs each with unique SAKs.

while the payload can be optionally encrypted. The ICV, unlike the Cyclic Redundancy Check (CRC) done in the MAC layer, is a cryptographic digest function dependent on the data and the SAK. This forces the attacker to know the key to tamper with the data. VLAN-in-clear is an additional feature that optionally keeps the Virtual LAN (VLAN) field without encryption before the SecTAG. This feature is used in cases that require VLAN information to be exposed to support traffic differentiation and end-to-end bridges.

In transmission, the frame is first assigned to the transmit SC and SA which will be used to protect the frame. The TCI is generated based on the configuration used, together with the SA encoded in the two-bit AN. The SecTAG is created using the MACsec Ethertype, TCI, PN, SCI, and the Short Length (SL), which is the number of octets in the frame following the SecTAG if it is less than 48. The AN is used to identify the SAK and the next PN for that SA. The frame is consequently integrity and confidentiality protected with AES-GCM cryptography using the SAK as the input key, and the SCI and PN as the initialization vector. As a result, the payload is encrypted and ICV generated.

In reception, the TCI, AN, SCI, PN, and SL field (if present) are extracted from the SecTAG. The TCI is used to identify the configuration used in the MACsec frame. The AN and SCI are used to assign the frame to a SA, and hence to identify the SAK. The frame is consequently integrity and confidentiality verified with AES-GCM cryptography using the SAK as the input key, and the SCI and PN as the initialization vector. As a result, the payload is unencrypted and the ICV is verified with the one received in the frame. If the integrity of the frame has been preserved, a valid indication and the octets of the unencrypted payload are returned. MACsec has the feature of replay protection, which allows the replay window to be set and ensures in-order delivery of frames. If the received frame is valid, replay protection (if enabled) is applied by checking that the received PN is not less than the lowest acceptable PN for the SA. If the check succeeds, the frame is presented to the MACsec client, and the lowest acceptable PN is updated. The lowest acceptable PN can lag behind the received PN values, providing a window in which out-of-order is tolerated and allowing the reception of frames that have been misordered by the network.

Confidentiality (optional)

FIGURE 9. MACsec frame format; a SecTAG and an ICV are added to each frame, all frames are integrity protected while confidentiality can be optionally performed to the payload data. The VLAN field, optionally present, can be confidentiality protected as part of the payload, or in-clear before the SecTAG.

#### V. MACSEC TO SECURE THE OPEN-RAN FRONTHAUL

MACsec is a persuasive solution to secure the O-FH as it operates on Ethernet frames and, therefore, can provide protection to the CUSM-Planes encapsulated over Ethernet. However, each data plane needs to be independently analyzed to understand to what extend MACsec can protect each plane from all the identified threats and how MACsec impacts any protocol operation or performance requirements.

#### A. THREAT PROTECTION

When MACsec is enabled on the O-RU and O-DU, both units share the same CAN and CAK, and ports on both ends are initially mutually authenticated by the MKA protocol. A CA with SCs and SAs is created between the O-RU and O-DU with periodical SAKs generations for frame protection and verification. This ensures that only authorized O-RU and O-DU are communicating with each other using the secret keys. As a result, an attacker is not able to inject its own traffic impersonating a node in the network.

Enabling confidentiality to both units keeps all CUSM-Planes encrypted, making each protocol header and payload hidden. As a result, an attacker is not able to identify the type of traffic of the link nor the payload being transported.

Integrity protection is performed over the whole Ethernet frame by the ICV added at the end of the frame using the secret keys. If a CUSM-Plane frame is corrupted while in-motion during the ICV verification there will be an ICV mismatch and the frame will be discarded. As a result, if an attacker changes the values of legitimate CUSM-Plane messages they will be identified and discarded before their delivery to the MACsec client.

Depending on the O-FH network operation, a replay window can be set to 0 or to a very small value in the O-RU and O-DU to ensure in-order delivery of frames. As a result, if an attacker performs a replay attack by recording a legitimate CUSM-Plane message and replaying the same message without modification multiple times at a later time, those frames will be identified and discarded before their delivery to the MACsec client.

With the use of the replay protection feature, MACsec with some limitations could also identify if an attacker has delayed a CUSM-Plane message. This can be done only for the cases where the attacker delays a single frame and lets the rest of the frames pass. In this case, the delayed frame will arrive disordered and the replay window will discard it. MACsec is not able to detect the cases where the attacker delays a desired frame together with the following frames, as they will all appear to arrive in the expected order. Additionally, MACsec is limited if an attacker drops specific frames or all the traffic in the O-FH.

The mapping of MACsec features with the identified threats in the O-FH network is illustrated on the right side of Table 2. As can be seen, the O-RU and O-DU can be protected using MACsec from most of the identified threats, with the exception only of drop and delay attacks that MACsec is partially able to detect. These types of threats can be protected against with network architecture approaches that use redundancy links and protocols such as Parallel Redundancy Protocol (PRP) and High-availability Seamless Redundancy (HSR) [31], [32].

#### **B. IMPLEMENTATION CHALLENGES**

MACsec offers a compelling solution to secure the O-FH. However, implementation challenges exist that need to be addressed.

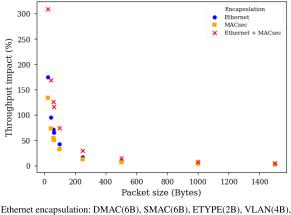

#### 1) O-FH LINE RATE

In terms of bandwidth, MACsec introduces an overhead to each frame due to the added SecTAG of 16 Bytes and ICV of 16 Bytes. Fig. 11 illustrates the impact of Ethernet encapsulation and MACsec overhead for different frame sizes. As can be seen, frame size is inversely proportional to the line rate impact. For smaller payload sizes, there will be a higher impact caused by the overhead, while for bigger sizes the impact is minimal. The MACsec overhead to PTP frames will decrease the line rate by 50.00% - 72.73%, depending on the PTP message size, e.g. sync and follow-up messages are 44 Bytes and announce messages are 64 Bytes. The MACsec overhead to C-Plane frames will decrease the line rate by 2.13% - 133.33%, depending on the C-Plane message size, e.g. type 1 and with 1 section is 24 Bytes while multiple sections can be up to 1500 Bytes that is supported payload in a standard Ethernet frame. The MACsec overhead to U-Plane frames will decrease the line rate by 2.13% - 54.24%, depending on the U-Plane message size, e.g. with 1 section and 1 PRB per section is 59 Bytes, while with multiple sections and PRBs, it can be up to 1500 Bytes that is supported payload in a standard Ethernet frame.

Enemet encapsulation: DMAC(0B), SMAC(0B), ETTPE(2B), VLAN(4B), FCS(4B), PRE(8B), and IPG(12B). MACsee header and tail: SecTAG(16B) and ICV(16B).

## 2) S-PLANE PTP PACKETS PROTECTION

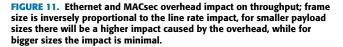

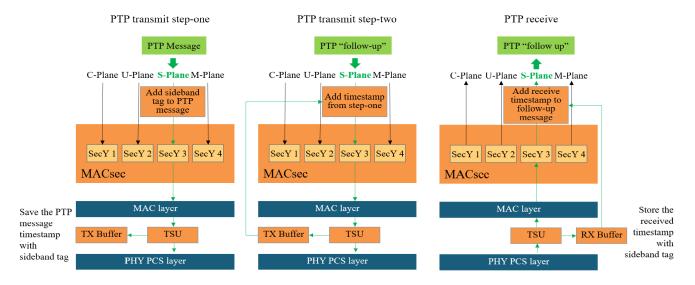

For precise PTP timestamping, the timestamp must occur at the physical layer close to the point where the PTP message is leaving the port. The Time-Stamping Unit (TSU) timestamps PTP messages that are identified by their corresponding Ethertype. When MACsec is used to protect PTP messages, there are timestamping design considerations for transmission and reception that need to be taken into account.

In transmission, for the case of one-step PTP clock implementation, the timestamp would need to be available at the MACsec layer for PTP messages protection using MACsec. This could be possible if the TSU generating the timestamp is placed before the MACsec layer and the latency from that point to the physical layer is added as illustrated in Fig. 12. Therefore, a fixed delay is required between the MACsec layer and the physical layer where PTP timestamping is needed for time precision.

For two-step PTP clock implementation, this consideration is not required as the timestamp is sent in the consecutive follow-up message. Thus, the timestamping can be kept at the physical layer, and the timestamp is available for the MACsec layer. However, this can be possible only for the case when PTP messages are integrity protected without confidentiality because the PTP Ethertype would be visible for the TSU to identify that it is a PTP message and would be able to timestamp it. If the PTP message is confidentiality protected,

separately to different nodes from a single port, as shown

**FIGURE 12.** PTP TSU positioning; ideally closer to the physical layer for time accuracy, however for PTP messages protection using MACsec the TSU needs to be placed before the MACsec layer.

the TSU would not be able to identify the encrypted PTP message nor timestamp it.

In reception, similar considerations occur. If a PTP message is received with integrity protection without confidentiality, the timestamping can be kept at the physical layer with the TSU being able to identify and timestamp the visible PTP message. If a PTP message is received with confidentiality protection, the TSU needs to be placed before the MACsec layer when the PTP message is unencrypted, and, again, a fixed delay would be required between the physical layer and the MACsec layer for time precision.

As a result, with a TSU kept at the physical layer for time accuracy, only a two-step mode would be possible and PTP with messages could be MACsec protected without confidentiality. When a one-step mode or two-step mode with confidentiality is desired, the TSU needs to be placed before MACsec with a fixed delay in the MACsec and following components to the physical layer.

The O-FH can vary from a point-to-point scenario to a network of switches that may act as boundary clock or transparent clock. For the network of switches topology, MACsec can be implemented end-to-end between O-RU and O-DU, or hop-by-hop including each intermediate switch. For the end-to-end option, all Ethernet frames are integrity and confidentiality protected at the O-RU and O-DU, hence, the intermediate switches could only act as forwarding nodes without the capacity to access and make changes to the frame payload. This is a limitation for O-FH switches as they are required to timestamp and correct PTP messages. Therefore, if MACsec is used to protect PTP messages, the hop-byhop option is required with each switch having MACsec capabilities. However, this potentially adds more latency in every hop, and adversary impacts to the end-to-end budget.

## 3) TRAFFIC DIFFERENTIATION

For the network of switches topology at the O-FH interface, traffic from each of the CUSM-Planes may need to be sent

Fig. 13. This results in multiple groups of nodes divided per data plane. For example, a group of nodes can be between an O-RU and two O-DUs based on C-Plane data, and another group between the same O-RU and a PTP grandmaster based on S-Plane data. Each group needs to be secured independently for security robustness including the need for different sets of secret keys. Thus, there is a need to support multiple security domains between a port and different destinations based on the CUSM-Planes type of traffic. If MACsec is used to protect the O-FH, a single port in O-RU, O-DU, and intermediate switches need to support multiple CAs for traffic differentiation, i.e. multiple sets of KaY-SecY per port.

**FIGURE 13.** O-FH network of switches topology; traffic from each of the CUSM-Planes may need to be sent separately to different nodes from a single port. Multiple CAs per port for traffic differentiation are required to protect against threats.

# VI. MACSEC HARDWARE ARCHITECTURE FOR THE OPEN-RAN FRONTHAUL

The O-RAN specifications are still under definition and will offer openness to innovation in the O-FH. This innovation requires O-RAN components to have flexibility in quickly changing or adding features for testing and upgrading functionalities. This becomes a challenge in components that are implemented in hardware (HW) chips for high-performance data operation due to the much longer development time needed compared to software (SW). Application-Specific Integrated Circuit (ASIC) chips, especially, require an extended development time because they are manufactured to execute a specific set of functions [33]. In contrast, FPGAs are pre-produced chips that can be reprogrammed after being manufactured. This offers flexibility to HW implementations that require faster time-to-market [34]. The programmability of FPGAs makes them appealing for the implementation of the continuously changing high-performance functionalities of O-FH components.

As MACsec operates at the Ethernet port level, it is constrained by the strict O-FH transport performance requirements of high throughput, low latency, and accurate time stamping. Because of this, MACsec needs to be implemented in dedicated FPGA or ASIC, contrary to SW implementations running on general purpose Central Processing Units (CPUs) [35].

In this section, we propose a MACsec HW-based architecture for the O-FH that targets FPGA and ASIC implementations. We begin by defining a single SecY fixed-latency pipelined HW architecture compliant with IEEE 802.1AE standard for a point-to-point O-FH topology. We then analyze the requirements to expand this architecture to support multiple SecYs in the same port for traffic differentiation of CUSM-Planes using independent CAs for the network of switches O-FH topology. Following, we propose a multiple SecY architecture with the addition of a Management Domain implementing virtual SecYs. Finally, we propose a PTP buffer system that complements the previous architecture to support full PTP protection and time accuracy.

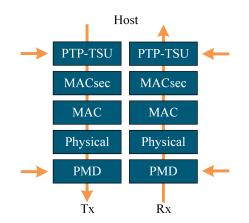

# A. SINGLE SECY ARCHITECTURE

As defined by the MACsec IEEE 802.1AE standard, a SecY is the entity that operates the MACsec data processing on a network port and it can only be part of one CA at any time. The SecY operation is on a frame-by-frame basis and divided into two parts; transmit and receive. The transmit part protects the frame with encryption and integrity using the AES-GCM cryptography functions and creates and appends the SecTAG and the ICV to the frame. The receiving part verifies the frame with decryption and integrity check using the AES-GCM cryptography functions and strips the SecTAG and the ICV from the frame.

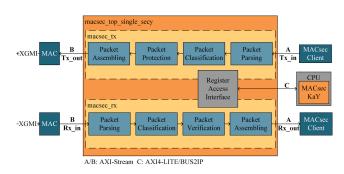

The proposed Single SecY architecture is presented in Fig. 14. It illustrates a highly abstracted hierarchy implementing Single SecY functionalities. The processing flow is divided into transmission (Tx) and reception (Rx), with the top-level architecture partitioned into three functional domains: Register Access Domain, Tx Domain, and Rx Domain.

- Register Access Domain, performing configuration and status register write and read operations.

- Tx Domain, performing MACsec transmission data plane protection functions.

- Rx Domain, performing MACsec reception data plane verification functions.

# 1) REGISTER ACCESS DOMAIN

The Register Access Domain maintains all SecY control information according to the standard, which includes transmitting and receiving SCs and SAs. These are stored in 32 bit configuration and status registers that are fully programmable and accessed through an AXI4-Lite Register Access Interface [36]. It runs under its 100 MHz CPU clock.

## 2) TX DOMAIN

The main purpose of the Tx Domain is to perform data protection of all Ethernet frames that are transmitted from the MACsec Client using input and output AXI-Stream 64 bit data interfaces [37]. It runs under a minimum Tx clock of

156.25 MHz for 10 Gbps and 390.625 MHz for 25 Gbps. At a high level, in Tx every Ethernet frame is processed as follows:

- Packet Parsing: this block extracts header and payload information of each Ethernet frame (MAC address, VLAN, Ethertype, and payload).

- Packet Classification: this block determines how to process each frame, according to the extracted header information and SecY configuration registers, and assigns a class type (bypass, drop, or protect).

- Packet Protection: this block performs frame protection to Ethernet frames with Protect class type using the Tx AES-GCM cipher suite with the corresponding security configuration parameters. The ICV is generated and the payload is encrypted if confidentiality is enabled.

- Packet Assembling: this block assembles Ethernet frames depending on the class type (Bypass, frame without alteration; Drop, the frame is assembled with error flag in Tuser signal at the end of the frame; Protect, the frame is assembled with MACsec SecTAG and ICV added and changed plaintext to ciphertext if confidentiality is enabled).

FIGURE 14. Single SecY top-level architecture partitioned into three functional domains: Register Access Domain, Tx Domain, and Rx Domain.

## 3) RX DOMAIN

The main purpose of the Rx Domain is to perform data verification of all Ethernet frames that are received from the MAC using input and output AXI-Stream 64 bit data interfaces [37]. It runs under a minimum Rx clock of 156.25 MHz for 10 Gbps and 390.625 MHz for 25 Gbps. At a high level, in Rx every Ethernet frame is processed as follows:

- Packet Parsing: this block extracts header and payload information of each Ethernet frame (MAC address, VLAN, Ethertype, SecTAG, payload, and ICV).

- Packet Classification: this block determines how to process each frame according to the extracted header information and SecY configuration registers and assigns a class type (bypass, drop, or verify).

- Packet Verification: this block performs frame verification to Ethernet frames with Verify class type using the Rx AES-GCM cipher suite with the corresponding security configuration parameters. The frame integrity is checked using the ICV and the payload is decrypted if confidentiality is enabled.

• Packet Assembling: this block assembles Ethernet frames depending on the class type (Bypass, frame without alteration; Drop, the frame is assembled with error flag in Tuser signal at the end of the frame; Verify, the frame is assembled with stripped MACsec SecTAG and ICV, and changed ciphertext to plaintext if confidentiality is enabled).

This architecture is, therefore, suitable for a point-to-point scenario as it consists of a single SecY that is required to form a single CA between two O-FH nodes.

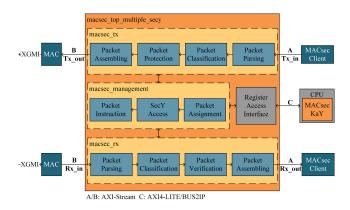

## **B. MULTIPLE SECY ARCHITECTURE**

As was presented in Section V-B, there is a need to support multiple SecYs per port for the network of switches O-FH topology. To support multiple SecYs in the same port for traffic differentiation of CUSM-Planes using independent CAs, one option is to have four instances of the Single SecY architecture, each serving an independent data plane. However, this option is very expensive as it increases by four the whole resource utilization, especially the packet protection and verification blocks implementing the AES-GCM cryptography operations.

We identified that it is possible to have multiple SecYs while keeping a single instance of the Tx and Rx processing flow, including the AES-GCM cryptography operations. This can be done by taking advantage of the frame-byframe transmission and reception operation in the Ethernet port. We propose to abstract the SecY control parameters from Tx and Rx Domains to a new Management Domain and only keep frame data processing operations in Tx and Rx domains. The Management Domain can then store and maintain control information of multiple SecYs and interface with Tx and Rx Domains, instructing them to perform data processing using specific configuration parameters according to a desired SecY. As a result, a configurable number of virtual SecYs can be instantiated in the Management Domain, all sharing the same Tx and Rx data processing flow. The proposed Multiple SecY architecture is presented in Fig. 15.

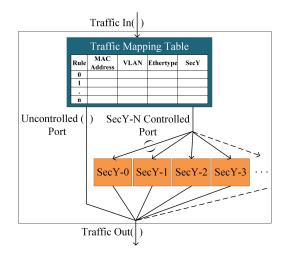

As there is a single physical transmission interface, CUSM-Planes need to be mapped to its corresponding SecY. To achieve this, we introduce in the Management Domain a traffic mapping table at the input interface. Here, rules can be configured to govern which SecY is used for a given transmit frame and to bypass a specific frame if necessary, as illustrated in Fig. 16. The rules can be based on MAC Address, VLAN ID, or Ethertype, offering flexibility depending on the O-FH topology. For example, the rules can be used in the following three O-FH scenarios:

- If a specific type of traffic is sent between concrete physical nodes in the O-FH network, MAC addresses can be used to associate traffic to a specific SecY.

- Different VLAN IDs can be used for each CUSM-Plane to differentiate them, thus, four rules based on VLAN IDs can be used to associate each data plane to a SecY.

- Each CUSM-Plane uses a specific protocol, hence, the corresponding protocol Ethertype can be used as a rule criterion to associate each data plane to a specific SecY. The processing flow of the Management Domain is as follows:

- Packet Assignment: this block uses the parsed header information in Tx and Rx Domains to check a match in the traffic mapping table to either bypass MACsec or to assign the frame to a SecY.

- SecY Access: this block accesses all control information associated with the selected SecY, determines how the frame should be processed, and updates its state.

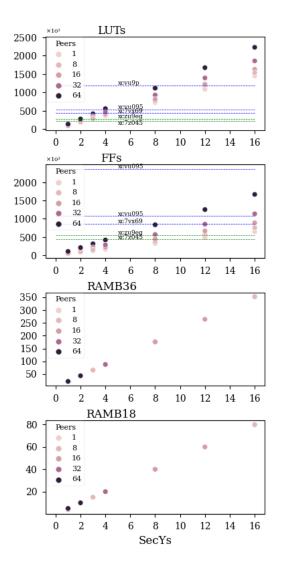

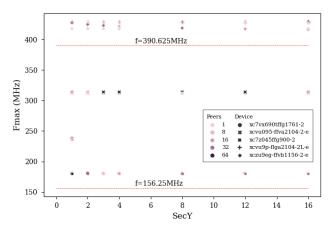

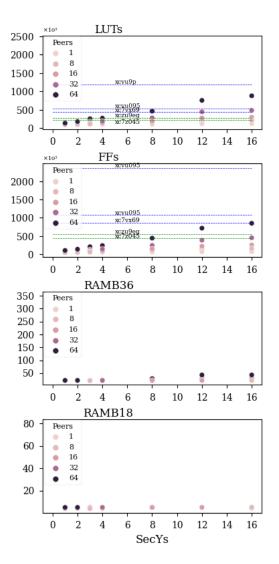

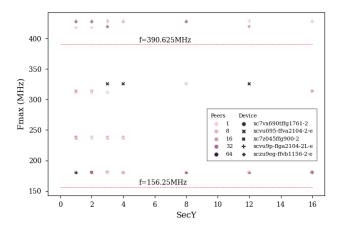

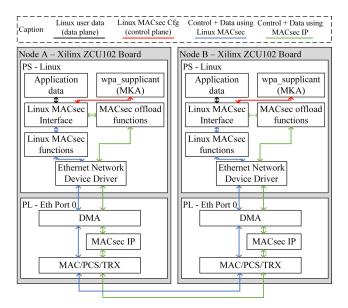

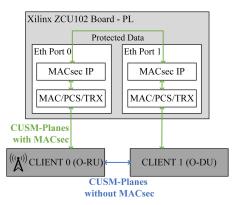

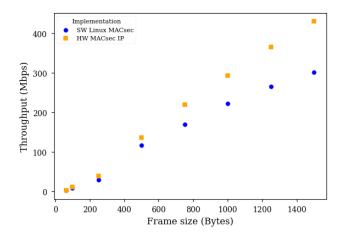

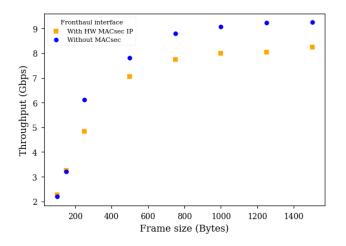

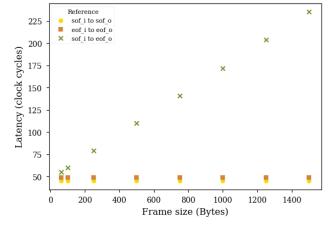

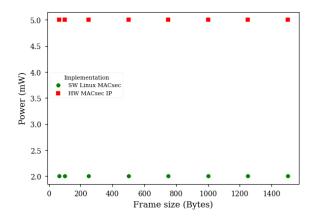

- Packet Instruction: this block instructs Tx and Rx Domains how to continue processing the frame and provides the corresponding configuration parameters.