Received 16 February 2023, accepted 14 March 2023, date of publication 7 April 2023, date of current version 17 May 2023.

Digital Object Identifier 10.1109/ACCESS.2023.3265477

# An Optimized Vertical GaN Parallel Split Gate Trench MOSFET Device Structure for Improved Switching Performance

NILESH KUMAR JAISWAL<sup>®</sup> AND V. N. RAMAKRISHNAN<sup>®</sup>

Department of Micro and Nanoelectronics, Vellore Institute of Technology, Vellore, Tamil Nadu 632014, India

Corresponding author: V. N. Ramakrishnan (vnramakrishnan@vit.ac.in)

This work was financial supported by the Vellore Institute of Technology, Vellore, India, and the authors acknowledge to the Council of Scientific and Industrial Research (CSIR), Government of India, through the project fellowship under Grant 09/844(0085)/2019-EMR-I.

**ABSTRACT** This work proposes a vertical gallium nitride (GaN) parallel split gate trench MOSFET (PSGT-MOSFET) device architecture suitable for power conversion applications. Wherein two parallel gates, and a field plate are introduced vertically on the sidewalls and connected, respectively, to the gate and source. Technology computer-aided design (TCAD) simulator was used in the design process to achieve a specific on-resistance as low as  $0.79~\text{m}\Omega.\text{cm}^2$  for the device, which has the capacity of blocking voltages up to 600 V. The peak electric field of the PSGT-MOSFET could well be lowered to 2.95 MV/cm, which is about 17% lower than that of a conventional trench gate MOSFET (TG-MOSFET) near the trench corner with help of suitable design and optimization of trench depth, drift doping, and field plate thickness. The TCAD simulation shows that the higher drift doping on the device performance of PSGT-MOSFET produces  $\sim 2 \times 10^{-10}$  lower switching losses when compared with a similarly rated conventional TG-MOSFET device.

**INDEX TERMS** Vertical GaN, trench MOSFET, split gate, on-resistance, switching loss, TCAD.

#### I. INTRODUCTION

Power semiconductor switches are the basic components of any power converter circuit to improve the efficiency of modern electronics systems. The automotive semiconductor industry uses high voltage batteries (200 to 300 V) in the hybrid electric vehicles (HEV) [1]. To make HEV conversion efficient, the development of 600 V power MOSFET switches are desired to reduce the power losses [2]. The existing Si-based power device has reached its performance restriction due to the limitation of its material property, and it is difficult to enhance overall performance through the innovation of device principles, the improvement of structure and the progress of the manufacturing process [3], [4]. To achieve better conversion efficiency, the high-performance power devices are needed which have smaller conduction losses and lower switching losses, making them feasible for high-frequency, high-temperature operations. The two most

The associate editor coordinating the review of this manuscript and approving it for publication was Sneh Saurabh .

promising WBG semiconductors are silicon carbide (SiC) and gallium nitride (GaN). SiC switches and diodes have been developed over the past decade to meet certain demanding military and commercial applications and have demonstrated high efficiency and high-temperature operation. GaN switches are projected to have a 100× performance advantage over silicon-based devices, and 10× over SiC, owing to their excellent material properties such as high electron mobility, a high breakdown field, and a high electron velocity. GaN-based power electronics feature both low on-resistance and fast switching, leading to substantial reductions in conduction and switching losses, respectively [5], [6], [7], [8], [9], [10]. The first generation of GaN transistors has been the high electron mobility transistors (GaN HEMTs) that have demonstrated an excellent trade-off between  $R_{on}$  and  $V_{br}$  [11], [12], [13].

However, the GaN HEMT device has a normally-on behaviour, and negative gate bias is required to turn off the transistor [11], [14]. Hence, the use of normally-off GaN lateral transistors has led to the development of cascode devices.

In a cascode device, the depletion-mode GaN lateral transistor and enhancement-mode Si-MOSFET are packed in series to form a normally-off behaviour [15]. The drawback of GaN based cascode devices is that the series connection of the two devices increases packing complexity, resulting in parasitic inductances that might upset the switching performance of the device [16], [17].

On the other hand, vertical GaN transistors show promising characteristics for high power switch applications to benchmark against GaN HEMT [18], [19], [20], [21]. Because of their normally-off behavior, suitability for having the peak electric field (E-field) distant from the surface, and capacity to handle larger power densities. Some of the earlier reports demonstrated that the device performance of 600 V GaN vertical transistors are based on the structure; such as the MOS channel [22], quasi vertical [23], fully vertical [24], regrowth channel types [25], and split gate power MOS-FET [26]. Among these structures, the MOS channel based GaN vertical trench gate MOSFET (TG-MOSFET) design has a significantly smaller on-resistance due to the lack of a junction field effect transistor (JFET) region [27], [28], [29], [30], leading to low switching loss. However, TG-MOSFETs have a significantly higher gate-to-drain capacitance  $(C_{GD})$ and gate-to-drain charge  $(Q_{GD})$  owing to the gate, having been separated from the drain by a thin layer of gate oxide, both of which contribute to a substantial increase in the switching loss and lowers converter efficiency [31]. A critical issue for TG-MOSFET is to lower the E-field which is present in gate oxide around the trench bottom. The split gate technique has been implemented in order to mitigate the issue [32], [33], [34].

The split-gate MOSFET (SGT-MOSFET) is an innovative trench structure, which uses an isolated FP between gate and drain to reduce the gate-to-drain charge and improve the figure of merit while it benefits from low switching loss compared with conventional TG-MOSFET [33]. Another technique for improving the figure of merit and optimizing the electric field distribution is to use an additional charge control electrode (i.e. floating electrode) in the SGT-MOSFET, as known as a floating gate power MOS-FET (FG-MOSFET) [34]. However, in order to realize the SGT-MOSFET and FG-MOSFET, many additional process steps such as deposition and etching were needed due to an interlayer dielectric (ILD) layers used to isolate the gate to field-plate (FP) and field-plate to floating gate (FG). During ILD growth step, thermally grown oxide on top of the FP and FG electrodes become challenging due to the temperature controllability. In this work, a distinct design technique known as the vertical GaN parallel split gate MOSFET (PSGT-MOSFET) structure concept, is proposed with the aim of improving the switching performance. There is no ILD layer in the PSGT-MOSFET, which leads to a reduction in the number of mask steps during patterning. Hence, fabrication costs of PSGT-MOSFET could be reduced when compared to SGT-MOSFET and FG-MOSFET. This methodology was used in the development of Si-based shielded gate MOS-

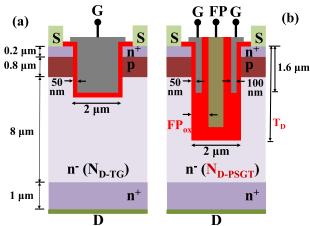

**FIGURE 1.** Cross-sectional representation of (a) TG-MOSFET and (b) PSGT-MOSFET.

FET [38], [39]. The PSGT-MOSFET structure uses a vertical field-plate oxide into a drift layer, which is significantly thicker than the gate oxide. Employing thick oxides at the bottom and trench sidewalls to facilitate field shaping, which involves controlling the location of peak electric fields and preventing an avalanche or significant hot carrier generation in the vicinity of the trench gate oxide. The vertical FP and thick oxide make it possible to use a larger drift doping while maintaining the same breakdown voltage device rating. This indicates that the  $R_{on}$  is lower for a given breakdown. The switching performance of the PSGT-MOSFET is also drastically enhanced due to the reduction in  $C_{GD}$  i.e.  $C_{rss}$ .

The main objective of this study is to benchmark a vertical GaN PSGT-MOSFET for the first time, which will allow for a comparison with TG-MOSGET in terms of switching performance. The TCAD mixed-mode platform has been used in order to perform device and circuit simulations. The paper has been organized in the following manner: in section II, the device designs and simulation methodology are introduced. Section III presents the optimization of the PSGT-MOSFET in order to achieve the desired breakdown voltage of 600 V while simultaneously lowering the maximum GaN E-field at the trench bottom to below 3 MV/cm. The proposed fabrication process steps are highlighted in Section IV. Lastly, section V contrasts the static and dynamic characteristics of proposed a PSGT-MOSFET with those of a conventional device.

# II. DEVICE OPERATIONS, AND SIMULATION METHODOLOGY

The device operation and simulation methodology have been performed using a TCAD simulator. Fig. 1(a) illustrates the cross-sectional representation of TG-MOSFET device structure. The structure has been based on our most recent publication, which includes an 8  $\mu m$  thick Si doped (2  $\times$  10  $^{16}$  cm  $^{-3}$ ) GaN drift layer, a 0.8  $\mu m$  thick Mg doped (1.3  $\times$  10  $^{17}$  cm  $^{-3}$ ) GaN base layer, and a 0.2  $\mu m$  thick Si doped (5  $\times$  10  $^{18}$  cm  $^{-3}$ ) GaN source layer. These layers are built on a Si doped GaN substrate. The doping of the base layer has been optimized

VOLUME 11, 2023 46999

and adjusted to achieve a threshold voltage of  $\sim$ 4.6 V and a breakdown voltage of 600 V. The device has been designed with a trench depth of 2  $\mu$ m and a metal-oxide-semiconductor (MOS) structure has been built into both the sidewall and bottom of the trench.

The device structure parameters of PSGT-MOSFET coincide with those of TG-MOSFET, as shown in Fig. 1(b). Except to complete gate electrode in conventional TG-MOSFET, the middle section of gate electrode in PSGT-MOSFET is changed to thin parallel gate metal lining along gate oxide,  $SiO_2$ . Furthermore, the trench depth in conventional TG-MOSFET is extended to the expected position into the drift layer, and is formed the FP. The FP electrode is connected to source electrode and splits with thicker oxide, thereby substantially reducing the overlapping capacitance, i.e.,  $C_{rss}$  [33]. However, the gate-tosource capacitance  $(C_{GS})$  will increase the input capacitance of PSGT-MOSFET. The thicker FP oxide will create a charge balancing effect by redistributing E-field at the trench bottom. Thanks to FP technology, which leads to the enhancement of the lateral depletion and allows a higher doping concentration in the drift layer, causing a reduction in  $R_{on}$  without impacting on breakdown voltage. As a consequence, it contributes to an increase in the switching speed of the device.

The device characteristics were calibrated amongst the experimental results of a fabricated TG-MOSFET, described by Li et al. [22] using TCAD simulation [40]. The TCAD device simulation methodology and important physics models have been reported in the previous work [26], [34], [35], [36], [37], as shown in Table 1. TCAD Sentaurus provides users with access to a wide variety of physical models, each of which is designed to explain the physical behavior of semiconductor devices as precisely as is technically feasible in relation to the fabricated device. The important physics models have been included in device simulations in order to get accurate forecasts of the fabricated device characteristics. The simulation methodology has been adopted by computing the Poisson's equation, including the electron and hole continuity equations and 2D drift-diffusion carrier transport equations. The recombination phenomenon was taken into account by using three processes, specifically the Radiative, Auger, and Shockley-Read-Hall (SRH) models for a fixed minority-carrier lifetime. In order to take into consideration the effects of velocity saturation, the Caughey Thomas field dependent mobility model and Masetti model for doping dependency were incorporated into the simulation. Simulation models for vertical GaN power transistors were selected with reference to previously published works. According to the report in [26] and [34], the selected simulation models and the experiment [22] have a very good level of agreement with one another. At the gate dielectrics-trench contact, a fixed charge concentration of approximately  $1.5 \times 10^{12}$  $cm^{-2}$  was implemented so that it achieves the desired match of the threshold voltage [42]. Furthermore, the experimentally determined breakdown voltage of 600 V was precisely

TABLE 1. The parameters and models used in this work.

| Parameter                                                  | Value                 |

|------------------------------------------------------------|-----------------------|

| Bandgap (eV)                                               | 3.437                 |

| Dielectric constant                                        | 8.9                   |

| Electron affinity (eV)                                     | 3.95                  |

| Activation energy for donor (meV)                          | 15                    |

| Activation energy for acceptor (meV)                       | 290                   |

| Electron saturation velocity (cm/s)                        | $1.27 \times 10^{7}$  |

| Hole saturation velocity (cm/s)                            | $1.7 \times 10^{7}$   |

| Maximum electron mobilities (cm $^2/V.s$ )                 | 1500                  |

| Maximum hole mobilities (cm $^2/V.s$ )                     | 150                   |

| Impact ionization coefficients for electrons $(A_n)$ (/cm) | $2.9 \times 10^{8}$   |

| Impact ionization coefficients for electrons $(A_p)$ (/cm) | $5.41{\times}10^6$    |

| Impact ionization coefficients for holes $(B_n)$ (V/cm)    | $3.4 \times 10^{7}$   |

| Impact ionization coefficients for holes $(B_p)$ (V/cm)    | $1.96 \times 10^{7}$  |

| Auger recombination model for electrons (cm $^6/s$ )       | $3.0 \times 10^{-31}$ |

| Auger recombination model for electrons/holes (cm $^6/s$ ) | $3.0 \times 10^{-31}$ |

| Direct recombination constant $(cm^3/s)$                   | $2.0 \times 10^{-10}$ |

| Carrier lifetime of electrons/holes (ns)                   | 0.7/2.0               |

| Critical electric field in this work (MV/cm)               | 3.75                  |

**TABLE 2.** Device structure parameters during simulation.

| Parameter                                        | TG-MOSFET            | PSGT-MOSFET          |

|--------------------------------------------------|----------------------|----------------------|

| $n^+$ Source layer depth ( $\mu$ m)              | 0.2                  | 0.2                  |

| p Base layer depth ( $\mu$ m)                    | 0.8                  | 0.8                  |

| $\rm n^-$ Drift layer depth ( $\mu \rm m$ )      | 8.0                  | 8.0                  |

| n <sup>+</sup> Source doping (cm <sup>-3</sup> ) | $5.0 \times 10^{18}$ | $5.0 \times 10^{18}$ |

| p Base doping (cm <sup>-3</sup> )                | $1.3 \times 10^{17}$ | $1.3 \times 10^{17}$ |

| $\rm n^-$ Drift doping (cm $^{-3}$ )             | $2.0 \times 10^{16}$ | $3.5 \times 10^{16}$ |

| Gate width $(\mu m)$                             | 2.0                  | 2.0                  |

| Gate oxide thickness $(G_{ox})$ $(\mu m)$        | 0.05                 | 0.05                 |

| Gate trench depth ( $\mu$ m)                     | 1.6                  | 1.6                  |

| Deep trench depth $(T_D)$ $(\mu \mathrm{m})$     | 1.65                 | 7.0                  |

| Field plate oxide $(FP_{ox})$ $(\mu m)$          | _                    | 0.49                 |

matched by adjusting the effective base layer concentration  $(1.3 \times 10^{17} \text{ cm}^{-3})$ .

# **III. DEVICE OPTIMIZATION**

The main focus of the optimization of PSGT-MOSFET is to obtain lower  $R_{on}$  and  $V_{br}$  of 600 V without modifying the thickness of drift layer and minimizing the electric field distribution at the trench when compared to TG-MOSFET. In order to meet the requirements of this desire, numerous optimizations have been implemented on devices, such as higher drift doping concentration  $(N_{D-PSGT})$ , deep trench depth  $(T_D)$ , and thicker FP oxide  $(FP_{ox})$  of proposed device. A higher  $N_{D-PSGT}$  doped has a low  $R_{on}$  and  $V_{br}$ . However, the incorporated deep  $T_D$  establishes a greater gate-modulated accumulation charge by the drain [41], which is suitable for increasing  $V_{br}$  while maintaining low  $R_{on}$ . Meanwhile, the extended deep of trench depth into the drift layer, the  $C_{GD}$  is enhanced, affecting the switching delays. Therefore,

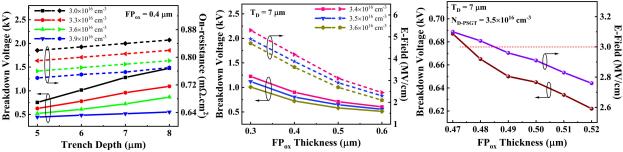

FIGURE 2. (a) Influences of  $V_{br}$  and  $R_{on}$  on  $T_D$  and  $N_{D-PSGT}$ , (b) Influences of  $V_{br}$  and E-Field on  $FP_{ox}$  and  $N_{D-PSGT}$ , and (c) Influences of  $V_{br}$  and E-Field on  $FP_{ox}$ .

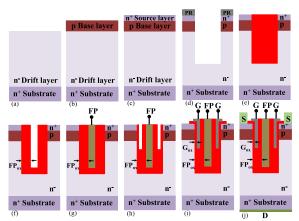

FIGURE 3. Fabrication process steps of PSGT-MOSFET device.

thicker FP oxide is an important parameter that reduces the  $C_{GD}$  by using higher oxide thickness at the trench bottom. Fig. 2 shows the influences of  $N_{D-PSGT}$ ,  $T_D$ , and  $FP_{ox}$  on the  $V_{br}$ , the  $R_{on}$ , and E-field distribution near the trench bottom. During optimization, the pitch of PSGT-MOSFET device structure has been incorporated exactly the same as the TG-MOSFET.

As shown in Fig. 2(a), of the three variables (i.e.  $N_{D-PSGT}$ ,  $T_D$ , and  $FP_{ox}$ ), only two  $(N_{D-PSGT}$ , and  $T_D$ ) are varied at a time, whereas the other one  $(FP_{ox})$  will be set at a fixed value. The  $N_{D-PSGT}$  value is varied from  $3.0 \times 10^{16}$  cm<sup>-3</sup> to  $3.9 \times 10^{16}$  cm<sup>-3</sup>, and the  $T_D$  value is varied from 5  $\mu$ m to 8  $\mu$ m, respectively. As expected, when  $T_D$  increases, both the  $V_{br}$  and  $R_{on}$  increase. To reach the 600 V breakdown voltage target, doping levels need to be below  $3.6 \times 10^{16}$  cm<sup>-3</sup>, and trench depth 7  $\mu$ m. As a result, these parameters have been decided to constitute a beginning step for the simulation.

When considering these parameters, the peak E-field of PSGT-MOSFET device demonstrates a greater than 3.0 MV/cm surrounding the trench bottom. Hence, increasing the thickness of  $FP_{ox}$  can reduce the E-field profile around the trench bottom. The value of  $FP_{ox}$  is varied from 0.3  $\mu$ m to 0.6  $\mu$ m, and  $N_{D-PSGT}$  from 3.4  $\times$  10<sup>16</sup> cm<sup>-3</sup> to 3.6  $\times$  10<sup>16</sup> cm<sup>-3</sup>, whereas the other one ( $T_D = 7 \mu$ m) is fixed. Fig. 2(b) demonstrates the decrement of  $V_{br}$  with respect to the change in the  $FP_{ox}$  thickness with respect to  $N_{D-PSGT}$ . The desired breakdown voltage is achieved between 0.4  $\mu$ m to 0.5  $\mu$ m ( $FP_{ox}$ ), and  $\sim$  3.5  $\times$  10<sup>16</sup> cm<sup>-3</sup> ( $N_{D-PSGT}$ ).

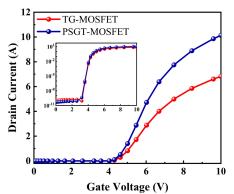

FIGURE 4. Transfer characteristics of devices.

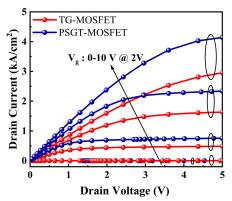

FIGURE 5. Output characteristics of devices.

To achieve high reliability, peak E-field should be maintained at less than 3.0 MV/cm at the bottom of  $FP_{ox}$ . As shown in Fig. 2(c), to obtain the accurate breakdown voltage (about 650 V) and electric field (less than 3.0 MV/cm), the field plate oxide thickness between 0.47  $\mu$ m to 0.52  $\mu$ m have been varied. Finally, it is found that the optimum values for PSGT-MOSFET are obtained as follows:  $N_{D-PSGT}$  of  $\sim$  3.5  $\times$  10<sup>16</sup> cm<sup>-3</sup>, and  $FP_{ox}$  of  $\sim$  0.49  $\mu$ m at  $T_D$  of 7  $\mu$ m. The structural details are given in Table 2.

# IV. PROPOSED FABRICATION PROCEDURE

In regards to the fabrication procedures, the optimized PSGT-MOSFET has been shown to be feasible in Fig. 3. The proposed process steps began with growth of low-doped n<sup>-</sup> GaN (Si doped) drift and p GaN (Mg doped) base layer on a freestanding n<sup>+</sup> GaN wafer [23], [24] (Fig. 3(a)-(b)). On the

VOLUME 11, 2023 47001

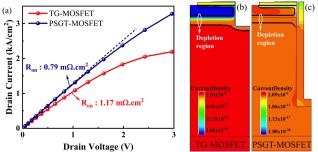

**FIGURE 6.** (a) Specific on-resistance estimation, depletion region at  $V_d = 1$  V keeping  $V_q = 10$  V (b) TG-MOSFET, and (c) PSGT-MOSFET.

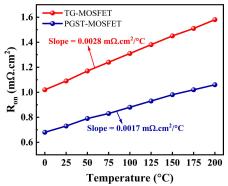

FIGURE 7. Comparison of the  $R_{OR}$ , and temperature dependency of the PSGT-MOSFET to the counterparts of the TG-MOSFET.

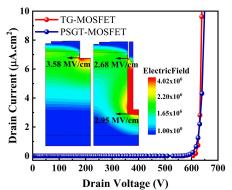

FIGURE 8. Breakdown characteristics of TG-MOSFET, and PSGT-MOSFET (Inset distribution of E-field).

uppermost part of the base layer, a selective area regrowth of an n<sup>+</sup> GaN source layer (Si doped) was performed [43] (Fig. 3(c)). A hard photoresist layer (PR) is used for patterning over the suitable region to remove a selective portion (Fig. 3(d)). An ICP-process was used to etch a gate width of 2  $\mu$ m using the PR to a depth such that the bottom of the trench (7  $\mu$ m) is located within the drift layer [44] (Fig. 3(d)). The wafer was then subjected to wet etching operations in order to clean the surface that had been etched and smooth the surface of the trench sidewall. Following etching, a dielectric layer (i.e.  $FP_{ox}$ ) was deposited (Fig. 3(e)) and etched back to form an oxide sidewall (Fig. 3(f)). Metal was then filled inside the trenches for FP electrode. After that, the metal was isotropically etched and recessed within the trenches (Fig. 3(g)). Sputtering with metal was the technique of choice to provide complete coverage of the shielded FP [45]. The

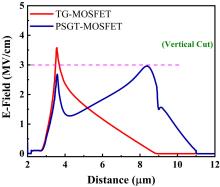

FIGURE 9. E-field profile during vertical cutline of TG-MOSFET, and PSGT-MOSFET.

source and FP electrode will be electrically linked to one another. Following that,  $FP_{ox}$  was etched, revealing a portion of FP metal that forms two troughs on its sides inside the trench (Fig. 3(h)). After this, a dielectric layer of gate oxide  $(G_{ox})$  (0.05  $\mu$ m-thick) was formed across the top of the wafer, trench sidewalls, and troughs inside the trenches (Fig. 3(i)). The removed region is deposited with a suitable metal to form a gate contact. In order to create the source electrodes, a metal stack was first deposited, and then it was patterned. Lastly, the drain electrode was then made by placing a metal stack on the back of the substrate (Fig. 3(j)) [46], [47], [48], [49], [50].

#### **V. RESULTS AND DISCUSSIONS**

The transfer characteristics  $(I_d-V_g)$  of devices are plotted in Fig. 4. The PSGT-MOSFET presents a very similar threshold voltage (4.58 V) to that of the TG-MOSFET (4.6 V). The output characteristics  $(I_d-V_d)$  for both devices under different gate voltages are superimposed as shown in Fig. 5. Clearly, the current carrying capability is higher for PSGT-MOSFET as compared to that of TG-MOSFET device for a  $V_g$  = 10 V. The  $R_{on}$  value of 0.79 m $\Omega$ .cm<sup>2</sup> for PSGT-MOSFET is found to be  $\sim$ 32% lower than that of TG-MOSFET for a drain voltage of 1 V, as indicated in Fig. 6(a). This is because the PSGT has been used with a higher drift doping concentration, which in turn causes an increase in the drive current and results in a lower  $R_{on}$  in the drift layer. As observed from Fig. 6(b)-(c), the depletion regions (the region enclosed by black lines) formed by the p base and trench region reduce to a great extent in the proposed structure as compared to the conventional structure because of the high dopant concentration of the drift region. As the current density increases, the on-resistance decreases (the proposed structure is  $1.09 \times 10^{-6}$  A/cm<sup>2</sup> and conventional structure is  $1.84 \times 10^{-8}$  A/cm<sup>2</sup>), and electron flow occurs primarily in the parallel split gate with deep trench of the added region. The added region for electrons to flow through the drift region provides a low resistivity path, and the electrons spread rapidly to the bottom of the substrate region. Thus, the proposed PSGT-MOSFET achieves a lesser value of the on-resistance as compared to the conventional device. On the other hand, the  $R_{on}$  values of proposed and conventional

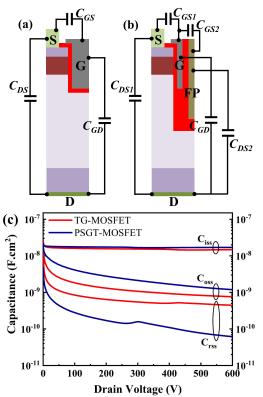

FIGURE 10. Parasitic capacitances of (a) TG-MOSFET, (b) PSGT-MOSFET, and (c) TCAD simulated CV characteristics.

devices are shown as a function of different temperatures in Fig. 7. The temperature coefficient of PSGT-MOSFET is found to be  $0.0017 \text{ m}\Omega.\text{cm}^2/^{\circ}\text{C}$  (average slope), which is ~39% lower than that of TG-MOSFET. It is observed that  $R_{on}$  of the PSGT-MOSFET is less dependent on temperature than that of the TG-MOSFET. Hence, applications requiring operation at high temperatures are a good fit for the PSGT-MOSFET.

The breakdown voltage characteristics are simulated as shown in Fig. 8. The PSGT-MOSFET shows a very comparable breakdown voltage (650 V) to that of the TG-MOSFET (623 V), when  $V_g = 0$  V. The maximum reduction in  $R_{on}$  without compromising blocking voltage is achieved, which is attributed to its heavily doped drift layer and FP region. Later, Baliga's FOM  $(V_{br}^2/R_{on})$  is expressed for indicating the trade-off amongst off-state breakdown voltage and on-state resistance [51], wherein PSGT-MOSFET is calculated to 531 MW/cm<sup>2</sup> which is  $\sim$ 63% better than that of TG-MOSFET.

The distribution and contour line of E-Field at the blocking regime ( $V_d = 600$  V, and  $V_g = 0$  V) for TG-MOSFET and PSGT-MOSFET are shown in inset Fig. 8. In TG-MOSFET, the E-field is overcrowded in the channel region (under the gate). The overcrowding of the E-field leads to a reliability issue for TG-MOSFET. Instead, in the PSGT-MOSFET, the better charge balance phenomenon is observed in the trench corner where the E-field is more uniform across the drift layer, as shown in Fig. 9. This is because

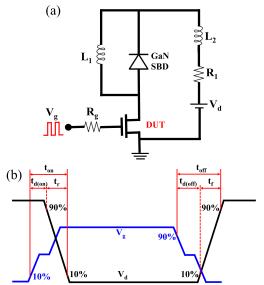

FIGURE 11. (a) Switching test circuit using DUT, and (b) Double pulse based graph definition of switching times.

of the perpendicular splitting effect of the thicker FP region. The E-field of the PSGT-MOSFET is 2.68 MV/cm at the gate oxide. In addition, the peak oxide E-field ( $E_{ox}$ ) of PSGT-MOSFET is observed to 2.95 MV/cm, which is  $\sim$ 17% lower than that of TG-MOSFET around the trench corner, respectively.

In TG-MOSFET, the input capacitance  $[C_{iss} = C_{GS}]$ (gate-source capacitance) +  $C_{GD}$  (gate-drain capacitance)], output capacitance  $[C_{oss} (= C_{GD} + C_{DS})]$  (drain-source capacitance)], and reverse capacitance,  $C_{rss}$  (= $C_{GD}$ ), are shown in Fig. 10(a). Among all,  $C_{rss}$  plays a significant part in analyzing the switching speed of the device as well as preventing false turn-on. Fig. 10(b) shows that in PSGT-MOSFET, there are two capacitances associated with FP (i.e.,  $C_{GS2}$ , and  $C_{DS2}$ ). These capacitors are connected in series, which leads to lowering the  $C_{GD}$  value. However,  $C_{GS1}$  and  $C_{GS2}$ are connected in parallel, which slightly increases the input capacitance. Additionally,  $C_{DS1}$  and  $C_{DS2}$  help to lower the peak overshoot voltage stress on the SGT-MOSFET. This stress comes from circuit parasitic and high dv/dt immunity in switching converter circuits [52]. The terminal capacitance of both devices is shown in Fig. 10(c). The AC signal is established to be 1 MHz to obtain the capacitance by varying the  $V_d$  from 0 to 600 V while keeping  $V_g = 0$  V.  $C_{iss}$  and  $C_{oss}$  of the PSGT-MOSFET are a little higher than that of TG-MOSFET, which has a small effect on switching time and efficiency in high-frequency DC-DC converters. However, the extracted  $C_{rss}$  for PSGT-MOSFET is 61 pF/cm<sup>2</sup>, which is about 7 times lower than that of TG-MOSFET. It means that PSGT-MOSFET exhibits a quick transition during switched on-off. Furthermore, the HF-FOM ( $C_{rss}$  ×  $R_{on}$ ) of PSGT-MOSFET has been calculated [53], and found to be 48 m $\Omega$ .pF, which is 10 times larger than that of TG-MOSFET. The improved HFOM shows a reduction in total power loss.

VOLUME 11, 2023 47003

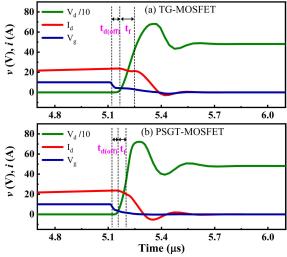

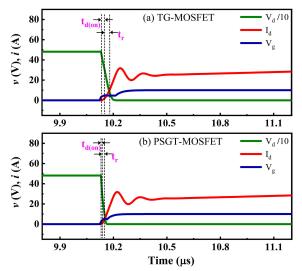

FIGURE 12. Turn-off switching times of TG-MOSFET, and PSGT-MOSFET.

FIGURE 13. Turn-on switching times of TG-MOSFET, and PSGT-MOSFET.

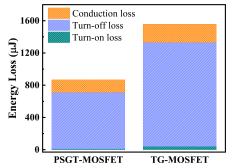

FIGURE 14. Energy loss components of both the devices.

### **VI. SWITCHING ANALYSIS**

In Fig. 11(a), the mixed-mode simulation is incorporated to study the switching performance with the help of a double-pulse test circuit. The switching characteristics of the device under test (DUT), i.e., TG-MOSFET and PSGT-MOSFET, have been studied using an inductive load ( $L_1 = 100 \ \mu\text{H}$ ). This inductive load and the freewheeling GaN schottky barrier diode (SBD) are connected in parallel. The

TABLE 3. An outline of the most important parameter of both devices.

| Parameter                                         | TG-MOSFET | PSGT-MOSFET |

|---------------------------------------------------|-----------|-------------|

| $R_{on} \ (m\Omega.cm^2)$                         | 1.17      | 0.79        |

| $V_{br}(V)$                                       | 623       | 650         |

| BFOM (MW/cm <sup>2</sup> )                        | 331       | 534         |

| $E_{ox}$ (MV/cm)                                  | 3.58      | 2.95        |

| $\mathrm{C}_{rss}~(\mathrm{pF/cm^2})$             | 444       | 61          |

| HF-FOM $(C_{rss} \times R_{on})$ (m $\Omega$ .pF) | 519       | 48          |

| $\mathfrak{t}_f~(\mu \mathfrak{s})$               | 0.08      | 0.04        |

| $\mathfrak{t}_d(off)$ ( $\mu$ s)                  | 0.06      | 0.05        |

| $t_r \; (\mu s)$                                  | 0.05      | 0.02        |

| $t_d(on)$ ( $\mu$ s)                              | 0.02      | 0.01        |

| $E_{on}\ (\muJ)$                                  | 41.9      | 10.9        |

| $E_{off}\left(\muJ\right)$                        | 1290      | 702         |

| $E_{SW}\left(\muJ\right)$                         | 1331.9    | 712.9       |

| $\mathbf{P}_{SW}\left(W\right)$                   | 266       | 144         |

GaN SBD is effective for higher switching speeds and low recovery [8], [54]. The gate pulse voltage  $(V_g)$  of 10 V is applied with an external gate resistance  $(R_g)$  of 1  $\Omega$  and a drain voltage  $(V_d)$  of 480 V [55]. The turn-off time is expressed in terms of turn-off delay time (from  $\sim$ 90% of  $V_g$  to  $\sim$ 10% of  $V_d$ ), and the fall time (from  $\sim$ 10% of  $V_d$  to  $\sim$ 90% of  $V_d$ ). Whereas, the turn-on time is expressed in terms of the turn-on delay time (from  $\sim 10\%$  of  $V_g$  to  $\sim 90\%$  of  $V_d$ ), and the rise time (from  $\sim 90\%$  of  $V_d$  to  $\sim 10\%$  of  $V_d$ ) [56], as given in Fig. 11(b). We have been extracted the turn-off time at the falling edge of the first pulse, and the turn-on time at the rising edge of the second pulse, respectively, as shown in Fig. 12, and Fig. 13. Fig. 12(a) displays the TG-MOSFET switching transitions during the turn-off mode. The obtained turn-off delay time  $[t_d(\text{off})]$  is 0.06  $\mu$ s, and fall time  $(t_f)$ is 0.08  $\mu$ s. Fig. 12(b) displays the PSGT-MOSFET switching transitions during turn-off mode. The obtained  $t_d(\text{off})$  is  $0.05 \mu s$ , and  $t_f$  is  $0.04 \mu s$ . The total turn-off time of PSGT-MOSFET is about  $1.5 \times$  faster compared to the TG-MOSFET. Next, Fig. 13(a) displays the TG-MOSFET switching transitions during turn-on mode. The obtained turn-on delay time  $[t_d(\text{on})]$  is 0.02  $\mu$ s, and rise time  $(t_r)$  is 0.05  $\mu$ s. Fig. 13(b) shows the PSGT-MOSFET switching transitions during turnon mode. The obtained  $t_d$ (on) is 0.01  $\mu$ s, and  $t_r$  is 0.02  $\mu$ s. The total turn-on time of PSGT-MOSFET is about  $2 \times$  faster compared to the TG-MOSFET. The total switching energy loss  $(E_{SW})$  of the DUTs has been calculated by integrating  $V_d$ , and  $I_d$  waveforms over the time interval between turn-off, and turn-on as shown in (1), and (2), respectively [57]. The turn-off  $(E_{off})$ , and turn-on  $(E_{on})$  energy is extracted when the load current reaches at 23 A. Fig. 14 compares the energy loss components of the PSGT-MOSFET and TG-MOSFET counterparts. The extracted energy losses of TG-MOSFET during  $E_{on}$  and  $E_{off}$  transients are 41.9  $\mu$ J, and 1290  $\mu$ J, respectively. The extracted energy losses of PSGT-MOSFET during  $E_{on}$  and  $E_{off}$  transients are 10.9  $\mu$ J, and 702  $\mu$ J, respectively. The total energy loss during turn-on, and turn-off time

of PSGT-MOSFET is around 2× less than TG-MOSFET. Finally, the total power loss  $(P_{SW})$  is calculated as a function of total switching loss, and respective frequency as shown in (3) [45]. The  $P_{SW}$  for PSGT-MOSFET is found to be 144 W, which is  $\sim$ 45% better compared to TG-MOSFET. Because of its low power loss, the PSGT-MOSFET can be employed in power conversion systems with high efficiency. Table 3 contains an outline of the most important parameters.

$$E_{off} = \left[ \int_0^{t_d(off) + t_f} V_d(t) . I_d(t) dt \right]$$

$$E_{on} = \left[ \int_0^{t_d(on) + t_r} V_d(t) . I_d(t) dt \right]$$

(2)

$$E_{on} = \left[ \int_{0}^{t_d(on) + t_r} V_d(t) . I_d(t) dt \right]$$

(2)

$$P_{SW} = (E_{on} + E_{off}).f (3)$$

# **VII. CONCLUSION**

The switching characteristics of a 600 V GaN vertical PSGT-MOSFET have been presented for the first time and compared to a conventional TG-MOSFET using the TCAD simulator. The parallel split gate technology consists of two thin parallel gates that have been aligned with gate oxide. Additionally, a field plate has been introduced vertically in between the gate electrodes, and connected to the source. It has been attributed to the (i) greater drift doping concentration and (ii) reduced surface E-field effect by thick bottom oxide. Hence, it causes a reduction in  $R_{on}$  without impacting on breakdown voltage. The simulation shows that the  $R_{on}$  of PSGT-MOSFET has decreased by nearly  $\sim$ 32% compared to that of a TG-MOSFET. In comparison with similar rated conventional devices, the proposed device shows 10× improvements in the HF-FOM ( $C_{rss} \times R_{on}$ ). Furthermore, when simulated employing in mixed mode, the switching characteristics of PSGT-MOSFET demonstrate decreased switching losses at turn-off as well as turn-on transients. By comparing  $E_{SW}$ , it is found that PSGT-MOSFET shows 1.5× faster switching transient and 2× lower energy loss as compared to TG-MOSFET. The total power loss for PSGT-MOSFET is calculated to be  $\sim$ 45% lower than that of a TG-MOSFET while operating in the same frequency range. However, in the PSGT-MOSFET fabrication process, challenges might exist due to the absence of stop layer where etching should be terminated. The addition of a P<sup>+</sup> shielding pinch structure and/or a P<sup>+</sup> shielding layer at trench bottom can potentially reduce the electric field. The improved performance of the PSGT-MOSFET would be expected to have a significant contribution to high power conversion used in the automotive applications.

#### REFERENCES

- [1] U. Kohler, "Hybrid electric vehicles: Batteries," in Encyclopedia of Electrochemical Power Sources, vol. 1. Amsterdam, The Netherlands: Elsevier, 2009, pp. 269–285, doi: 10.1016/B978-044452745-5.00367-1.

- [2] K. Horiuchi, Y. Arita, and T. Nishimura, "Automotive power MOSFETs," FUJI Electr. Rev., vol. 50, no. 2, pp. 53-57, 2003.

- [3] Q. Zhao-ming, Z. Jun-ming, and S. Kuang, "Status and development of power semiconductor devices and its applications," Proc. CSEE, vol. 34, no. 29, pp. 5149-5151, 2014.

- [4] Eden, "Market forecasts for silicon carbide & gallium nitride power semiconductors," in Proc. World Market Silicon Carbide Gallium Nitride Power Semiconductors, Mar. 2013.

- Y.-F. Wu, R. Coffie, N. Fichtenbaum, Y. Dora, C. S. Suh, L. Shen, P. Parikh, and U. K. Mishra, "Total GaN solution to electrical power conversion," in Proc. 69th Device Res. Conf., Jun. 2011, pp. 217–218, doi: 10.1109/DRC.2011.5994505.

- [6] W. Zhang, Z. Xu, Z. Zhang, F. Wang, L. M. Tolbert, and B. J. Blalock, "Evaluation of 600 V cascode GaN HEMT in device characterization and all-GaN-based LLC resonant converter," in Proc. IEEE Energy Convers. Congr. Expo., Sep. 2013, pp. 3571-3578, doi: 10.1109/ECCE.2013.6647171.

- [7] Z. Xu, W. Zhang, F. Xu, F. Wang, L. M. Tolbert, and B. J. Blalock, "Investigation of 600 V GaN HEMTs for high efficiency and high temperature applications," in Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC), Mar. 2014, pp. 131-136, doi: 10.1109/APEC.2014.6803299.

- [8] R. Mitova, R. Ghosh, U. Mhaskar, D. Klikic, M.-X. Wang, and A. Dentella, "Investigations of 600-V GaN HEMT and GaN diode for power converter applications," IEEE Trans. Power Electron., vol. 29, no. 5, pp. 2441–2452, May 2014, doi: 10.1109/TPEL.2013.2286639.

- [9] J. Millan, P. Godignon, X. Perpina, A. Perez-Tomas, and J. Rebollo, "A survey of wide bandgap power semiconductor devices," IEEE Trans. Power Electron., vol. 29, no. 5, pp. 2155-2163, Jun. 2014, doi: 10.1109/TPEL.2013.2268900.

- [10] X. Ding, Y. Zhou, and J. Cheng, "A review of gallium nitride power device and its applications in motor drive," CES Trans. Electr. Mach. Syst., vol. 3, no. 1, pp. 54-64, Mar. 2019, doi: 10.30941/CESTEMS.2019.00008.

- [11] E. A. Jones, F. Wang, and B. Ozpineci, "Application-based review of GaN HFETs," in Proc. IEEE Workshop Wide Bandgap Power Devices Appl., Oct. 2014, pp. 24-29.

- [12] D. Ueda, T. Fukuda, S. Nagai, H. Sakai, N. Otsuka, T. Morita, N. Negoro, T. Ueda, and T. Tanaka, "Present and future of GaN power devices," in Proc. 8th Int. Conf. Integr. Power Electron. Syst. (CIPS), Feb. 2014, pp. 1-5.

- [13] L. L. Jenkins, C. G. Wilson, J. D. Moses, J. M. Aggas, B. K. Rhea, and R. N. Dean, "The impact of parallel GaN HEMTs on efficiency of a 12-to-1 V buck converter," in Proc. 1st IEEE Workshop Wide Bandgap Power Devices Appl., Oct. 2013, pp. 197-200, doi: 10.1109/WiPDA.2013.6695596.

- [14] Y. Cai, Y. Zhou, K. J. Chen, and K. M. Lau, "High-performance enhancement-mode AlGaN/GaN HEMTs using fluoride-based plasma treatment," IEEE Electron Device Lett., vol. 26, no. 7, pp. 435-437, Jul. 2005, doi: 10.1109/LED.2005.851122

- [15] F. Roccaforte, G. Greco, P. Fiorenza, and F. Iucolano, "An overview of normally-off GaN-based high electron mobility transistors," Materials, vol. 12, no. 10, p. 1599, May 2019, doi: 10.3390/ma12101599.

- [16] X. Huang, T. Liu, B. Li, F. C. Lee, and Q. Li, "Evaluation and applications of 600 V/650 V enhancement-mode GaN devices," in Proc. IEEE 3rd Workshop Wide Bandgap Power Devices Appl. (WiPDA), Nov. 2015, pp. 113-118, doi: 10.1109/WiPDA.2015.7369318.

- [17] E. A. Jones, F. F. Wang, and D. Costinett, "Review of commercial GaN power devices and GaN-based converter design challenges," IEEE J. Emerg. Sel. Topics Power Electron., vol. 4, no. 3, pp. 707-719, Sep. 2016, doi: 10.1109/JESTPE.2016.2582685.

- [18] T. Oka, "Recent development of vertical GaN power devices," Jpn. J. Appl. Phys., vol. 58, no. SB, Apr. 2019, Art. no. SB0805, doi: 10.7567/1347-4065/ab02e7

- [19] Y. Zhang, M. Sun, Z. Liu, D. Piedra, H.-S. Lee, F. Gao, T. Fujishima, and T. Palacios, "Electrothermal simulation and thermal performance study of GaN vertical and lateral power transistors," IEEE Trans. Electron Devices, vol. 60, no. 7, pp. 2224–2230, Jul. 2013, doi: 10.1109/TED.2013.2261072.

- [20] N. K. Jaiswal and V. N. Ramakrishnan, "Vertical GaN reverse trench-gate power MOSFET and DC-DC converter," Trans. Electr. Electron. Mater., vol. 22, no. 3, pp. 363–371, Jun. 2021, doi: 10.1007/s42341-020-00248-2.

- [21] H Amano et al., "The 2018 GaN power electronics roadmap," J. Phys. D, Appl. Phys., vol. 51, Mar. 2018, Art. no. 163001, doi: 10.1088/1361-6463/aaaf9d.

- [22] R. Li, Y. Cao, M. Chen, and R. Chu, "600 V/ 1.7  $\Omega$  normally-off GaN vertical trench metal-oxide-semiconductor field-effect transistor," IEEE Electron Device Lett., vol. 37, no. 11, pp. 1466-1469, Nov. 2016, doi: 10.1109/LED.2016.2614515.

- C. Liu, R. A. Khadar, and E. Matioli, "GaN-on-Si quasi-vertical power MOSFETs," IEEE Electron Device Lett., vol. 39, no. 1, pp. 71-74, Jan. 2018, doi: 10.1109/LED.2017.2779445.

- [24] R. A. Khadar, C. Liu, R. Soleimanzadeh, and E. Matioli, "Fully vertical GaN-on-Si power MOSFETs," *IEEE Electron Device Lett.*, vol. 40, no. 3, pp. 443–446, Mar. 2019, doi: 10.1109/LED.2019.2894177.

- [25] W. Li, H. G. Xing, K. Nomoto, K. Lee, S. M. Islam, Z. Hu, M. Zhu, X. Gao, M. Pilla, and D. Jena, "Development of GaN vertical trench-MOSFET with MBE regrown channel," *IEEE Trans. Electron Devices*, vol. 65, no. 6, pp. 2558–2564, Jun. 2018, doi: 10.1109/TED.2018.2829125.

- [26] N. K. Jaiswal, V. N. Ramakrishnan, and S. D. Roy, "Vertical GaN split gate trench MOSFET with improved high frequency FOM," in *Proc. IEEE 17th India Council Int. Conf. (INDICON)*, Dec. 2020, pp. 1–5, doi: 10.1109/INDICON49873.2020.9342354.

- [27] T. Oka, Y. Ueno, T. Ina, and K. Hasegawa, "Vertical GaN-based trench metal oxide semiconductor field-effect transistors on a free-standing GaN substrate with blocking voltage of 1.6 kV," *Appl. Phys. Exp.*, vol. 7, no. 2, p. 021002, Jan. 2014, doi: 10.7567/APEX.7.021002.

- [28] T. Oka, T. Ina, Y. Ueno, and J. Nishii, "1.8 mΩ·cm² vertical GaN-based trench metal-oxide-semiconductor field-effect transistors on a free-standing GaN substrate for 1.2-kV-class operation," Appl. Phys. Exp., vol. 8, no. 5, Apr. 2015, Art. no. 054101, doi: 10.7567/APEX.8.054101.

- [29] C. Gupta, C. Lund, S. H. Chan, A. Agarwal, J. Liu, Y. Enatsu, S. Keller, and U. K. Mishra, "In Situ oxide, GaN interlayer-based vertical trench MOSFET (OG-FET) on bulk GaN substrates," *IEEE Electron Device Lett.*, vol. 38, no. 3, pp. 353–355, Mar. 2017, doi: 10.1109/LED.2017.2649599.

- [30] S. Chowdhury, J. Kim, C. Gupta, S. Keller, S.-H. Chan, and U. K. Mishra, "Trenched vertical power field-effect transistors with improved on-resistance and breakdown voltage," U.S. Patent 20 170 125 574 A1, May 4, 2017.

- [31] D. Ji, W. Li, and S. Chowdhury, "A study on the impact of channel mobility on switching performance of vertical GaN MOSFETs," *IEEE Trans. Electron Devices*, vol. 65, no. 10, pp. 4271–4275, Oct. 2018, doi: 10.1109/TED.2018.2864260.

- [32] K. Han, B. J. Baliga, and W. Sung, "Split-gate 1.2-kV 4H-SiC MOSFET: Analysis and experimental validation," *IEEE Electron Device Lett.*, vol. 38, no. 10, pp. 1437–1440, Oct. 2017, doi: 10.1109/LED.2017.2738616.

- [33] N. K. Jaiswal, V. N. Ramakrishnan, and S. deb Roy, "Optimization of vertical GaN SGT-MOSFET for low R<sub>on</sub>," in *Proc. IEEE Workshop Wide Bandgap Power Devices Appl. Asia (WiPDA Asia)*, Sep. 2020, pp. 1–5, doi: 10.1109/WiPDAAsia49671.2020.9360257.

- [34] N. K. Jaiswal and V. N. Ramakrishnan, "A comparative analysis and an optimized structure of vertical GaN floating gate trench MOSFET for high-frequency FOM," Semicond. Sci. Technol., vol. 37, no. 7, Jul. 2022, Art. no. 075001.

- [35] J. J. Wierer, J. R. Dickerson, A. A. Allerman, A. M. Armstrong, M. H. Crawford, and R. J. Kaplar, "Simulations of junction termination extensions in vertical GaN power diodes," *IEEE Trans. Electron Devices*, vol. 64, no. 5, pp. 2291–2297, May 2017.

- [36] M. Shurrab, A. Siddiqui, and S. Singh, "Counter-doped multizone junction termination extension structures in vertical GaN diodes," *IEEE J. Electron Devices Soc.*, vol. 7, pp. 287–294, 2019.

- [37] M. Shurrab and S. Singh, "Implantation-free edge termination structures in vertical GaN power diodes," *Semicond. Sci. Technol.*, vol. 35, no. 6, Jun. 2020, Art. no. 065005.

- [38] A. Challa, J. Lee, J. Jung, and H. Jang, "Power semiconductor devices having termination structures and methods of manufacture," U.S. Patent 7 855 415 B2, Dec. 21, 2010.

- [39] Y. Tian, Z. Yang, Z. Xu, S. Liu, W. Sun, L. Shi, Y. Zhu, P. Ye, and J. Zhou, "Novel failure mechanism and improvement for split-gate trench MOSFET with large current under unclamped inductive switch stress," *Superlattices Microstruct.*, vol. 116, pp. 151–163, Apr. 2018.

- [40] TCAD Sentaurus Device Manual, Synopsys, Mountain View, CA, USA, 2020.

- [41] L. Chen, O. J. Guy, M. R. Jennings, P. Igic, S. P. Wilks, and P. A. Mawby, "Study of 4H–SiC trench MOSFET structures," *Solid-State Electron.*, vol. 49, no. 7, pp. 1081–1085, Jul. 2005, doi: 10.1016/j.sse.2005.05.003.

- [42] Z. Renqiang et al., "Enhancing ON- and OFF-state performance of quasivertical GaN trench MOSFETs on sapphire with reduced interface charges and a thick bottom dielectric," *IEEE Electron Device Lett.*, vol. 43, no. 3, pp. 346–349, Mar. 2022.

- [43] Y. Cao, R. Chu, R. Li, M. Chen, R. Chang, and B. Hughes, "High-voltage vertical GaN Schottky diode enabled by low-carbon metal-organic chemical vapor deposition growth," *Appl. Phys. Lett.*, vol. 108, no. 6, Feb. 2016, Art. no. 062103, doi: 10.1063/1.4941814.

- [44] R. Quay, Gallium Nitride Electronics, vol. 96. Berlin, Germany: Springer, 2008

- [45] H. Hahn, G. Lükens, N. Ketteniss, H. Kalisch, and A. Vescan, "Recessed-gate enhancement-mode AlGaN/GaN heterostructure field-effect transistors on Si with record DC performance," Appl. Phys. Exp., vol. 4, no. 11, 2011, Art. no. 114102.

- [46] M. Kodama, M. Sugimoto, E. Hayashi, N. Soejima, O. Ishiguro, M. Kanechika, K. Itoh, H. Ueda, T. Uesugi, and T. Kachi, "GaN-based trench gate metal oxide semiconductor field-effect transistor fabricated with novel wet etching," *Appl. Phys. Exp.*, vol. 1, no. 2, Feb. 2008, Art. no. 021104, doi: 10.1143/APEX.1.021104.

- [47] M. Sugimoto, M. Kanechika, T. Uesugi, and T. Kachi, "Study on leakage current of pn diode on GaN substrate at reverse bias," *Phys. Status Solidi C*, vol. 8, nos. 7–8, pp. 2512–2514, Jul. 2011, doi: 10.1002/pssc.201000935.

- [48] Y. Zhang, M. Sun, D. Piedra, M. Azize, X. Zhang, T. Fujishima, and T. Palacios, "GaN-on-Si vertical Schottky and p-n diodes," *IEEE Electron Device Lett.*, vol. 35, no. 6, pp. 618–620, Jun. 2014, doi: 10.1109/LED.2014.2314637.

- [49] V. Talla, "BOE wet etch of silicon dioxide," M.S. thesis, Dept. Elect. Eng., Univ. Washington, Seattle, WA, USA, May 2011.

- [50] J. Hu, Y. Zhang, M. Sun, D. Piedra, N. Chowdhury, and T. Palacios, "Materials and processing issues in vertical GaN power electronics," *Mater. Sci. Semicond. Process.*, vol. 78, pp. 75–84, May 2018, doi: 10.1016/j.mssp.2017.09.033.

- [51] B. J. Baliga, "Power semiconductor device figure of merit for high-frequency applications," *IEEE Electron Device Lett.*, vol. 10, no. 10, pp. 455–457, Oct. 1989, doi: 10.1109/55.43098.

- [52] T. Sarkar, S. Sapp, and A. Challa, "Enhanced shielded-gate trench MOS-FETs for high-frequency, high-efficiency computing power supply applications," in *Proc. 28th Annu. IEEE Appl. Power Electron. Conf. Expo.* (APEC), Mar. 2013, pp. 507–511, doi: 10.1109/APEC.2013.6520257.

- [53] J. Ejury, "How to compare the figure of merit (FOM) of MOSFETs," Infineon, Neubiberg, Germany, Application Note, 2003.

- [54] L. Efthymiou, G. Camuso, G. Longobardi, F. Udrea, E. Lin, T. Chien, and M. Chen, "Zero reverse recovery in SiC and GaN Schottky diodes: A comparison," in *Proc. 28th Int. Symp. Power Semiconductor Devices ICs (ISPSD)*, Jun. 2016, pp. 71–74, doi: 10.1109/ISPSD.2016.7520780.

- [55] TPH3205WS: 600 V cascade GaN FET in TO-247, Transphorm, Goleta, CA. USA, 2018.

- [56] J. Brown, "Power MOSFET basics: Understanding gate charge and using it to assess switching performance," Vishay Siliconix, Columbus, NE, USA, Appl. Note AN608, 2004.

- [57] "How to select the right CoolMOS and its power handling capability: AN-CoolMOS-03," Infineon, Neubiberg, Germany, Appl. Note, V1.2, 2002.

NILESH KUMAR JAISWAL received the M.Tech. degree in microelectronics and control systems from the Dayanand Sagar College of Engineering, Bengaluru, India, in 2013. He is currently pursuing the Ph.D. degree with the Department of Micro and Nanoelectronics, School of Electronics Engineering, Vellore Institute of Technology, Vellore, India. He has authored or coauthored articles in reputed journals, book chapters, and conference papers. His research interests include designing

and optimizing novel GaN-based power semiconductor devices and also designing converter circuits for automotive applications.

V. N. RAMAKRISHNAN received the M.E. and Ph.D. degrees in electronics engineering from Anna University, India, in 2004 and 2015, respectively. He is currently an Associate Professor with the Department of Micro and Nanoelectronics, School of Electronics Engineering, Vellore Institute of Technology (VIT), Vellore, India. He has published many research articles in reputed journals and presented papers in conferences. His current research interests include nano-scale device

modeling and the design of GaN-based vertical power MOSFETs and ReRAMs.