Received 13 February 2023, accepted 16 March 2023, date of publication 20 March 2023, date of current version 27 March 2023. Digital Object Identifier 10.1109/ACCESS.2023.3259906

## **RESEARCH ARTICLE**

# A Broadband Doherty Power Amplifier for Sub-6 GHz 5G Applications

MOHAMMAD SHAHMORADI<sup>®1</sup>, SAYYED-HOSSEIN JAVID-HOSSEINI<sup>1</sup>, VAHID NAYYERI<sup>®1</sup>, (Senior Member, IEEE), ROCCO GIOFRÈ<sup>®2</sup>, (Senior Member, IEEE), AND PAOLO COLANTONIO<sup>®2</sup>, (Senior Member, IEEE)

<sup>1</sup>School of Advanced Technologies, Iran University of Science and Technology, Tehran 1684613114, Iran <sup>2</sup>Electronics Engineering Department, University of Roma Tor Vergata, 00133 Rome, Italy

Corresponding authors: Vahid Nayyeri (nayyeri@iust.ac.ir) and Paolo Colantonio (paolo.colantonio@uniroma2.it)

**ABSTRACT** This paper presents a novel and accurate procedure for designing a Doherty power amplifier (DPA) for wireless systems. The method is based on a systematic approach to designing the matching networks of both Main and Auxiliary devices, which employs an optimization process to set their input impedance in the corresponding optimal regions obtained from the standard load- and source-pull simulations. To import the optimum regions of each device into the optimization algorithm, mathematical expressions are derived and graphically reported on the Smith chart. Besides this, we have developed an accurate method to account for the loading effect of the Auxiliary amplifier on the Main one at back-off when designing the Main PA. As a proof of concept, a symmetric DPA is designed, fabricated, and tested. The measurements showed a working frequency band of 3.3-3.9 GHz (aimed at n78 band of 5G-NR), a minimum peak output power of 36 W, drain efficiency between 48 % – 53.2 % at peak and 34.6 % – 44.5 % at 6 dB back-off.

**INDEX TERMS** Doherty power amplifier, high-efficiency power amplifier, load-pull, optimization, sourcepull, wideband matching network.

### I. INTRODUCTION

Many modern modulation schemes exhibit significant signal envelope variations, and as long as the push for higher throughput continues, the envelope variation would get more extreme. The envelope variation in a signal causes its average power to be much lower than its peak power. Nowadays, some complex signals have a peak-to-average power ratio (PAPR) of 9 dB or more. In this context, a classic power amplifier (PA) would perform poorly, especially in terms of its average efficiency. On the other hand, the ever-higher demand for green and high-efficiency tech, along with lower OpEx, has drawn significant attention to the efficiency of systems [1].

Several PA topologies have come about to answer the shortcoming of classical PAs when dealing with high PAPR signals, one of which is the Doherty PA (DPA) [2], [3], [4]. The DPA is based on the modulation of the load presented to an active device, namely Main, commonly working in class

The associate editor coordinating the review of this manuscript and approving it for publication was Tae Wook Kim<sup>(D)</sup>.

AB, by using a second active device, namely Auxiliary, which is biased in class C [4]. The DPA is designed in a way that for low input power levels, the Main is on, whereas the Auxiliary is off. By increasing the input power and reaching the Main's saturation, the Auxiliary turns on and modulates the load seen by the Main. By exploiting an impedance inverter network, which can be realized using a simple quarter-wave transmission line, between the two amplifiers, in ideal conditions, it is possible to keep the efficiency of the Main PA constant until the Auxiliary is saturated as well. In such a way, the DPA can provide high efficiency in a wide range of output power back-off (OBO).

On the other hand, the DPA has some shortcomings; one of them is its narrow bandwidth, mainly due to the narrow-band operation of the quarter-wave impedance inverter network [5]. The complexity of designing the matching networks (MNs) is another negative factor. It is worth mentioning that in the design procedure of a classical DPA, the intrinsic output impedance of the device needs to be known. However, for most commercial active devices, manufacturers only provide

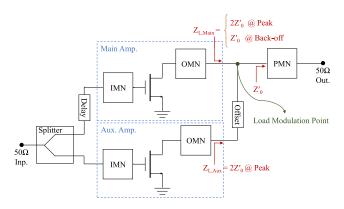

models extracted at the package planes, including both intrinsic and inherent parasitics. In order to address such issues, Akbarpour et al. in [5] proposed a modified architecture of DPA, namely transformer-less load modulated architecture wherein, at first glance, the impedance inverter is eliminated, as shown in FIGURE 1. In this architecture, however, the output MN (OMN) of the Main PA plays the role of an impedance inverter in addition to its primary matching role. In other words, the Main amplifier's OMN transfers the modulated impedance at the load modulation point, which varies dynamically from  $Z'_0$  at 6 dB OBO to  $2 \cdot Z'_0$  at saturation, to proper impedances that the Main device needs to see at the package plane. These impedances can be straightforwardly obtained from load-pull simulations at different input power levels without the need for transistor's model at the intrinsic plane. Furthermore, thanks to the elimination of the quarterwave transformer, a larger bandwidth with respect to the original DPA is achievable. Modifications in inverter-less DPAs were introduced in several recent works to improve the DPA's performance [6], [7], [8], [9], [10], [11], [12], [13].

Usually, DPAs are designed as two separate amplifiers and connected to each other afterward. The underlying assumption in this approach is that the loading effect of one amplifier onto the other does not introduce significant variations with respect to the case of separate amplifiers. However, especially at back-off, i.e., when the Auxiliary PA is off, the reactive loading of the latter onto the Main can significantly degrade the DPA performance. Such aspect, which is usually ignored during the design phase of the Main PA, is then compensated by tuning the length of an offset line, placed at the output of the Auxiliary PA, in order to fulfill the condition in which, at back-off, the Main PA sees an open circuit at the load modulation point, looking towards the Auxiliary PA (see FIGURE 1) [5], [6], [7], [8]. Alternatively, the output-matching network of the Auxiliary PA can be designed so that the output impedance of the Auxiliary PA (when the device is off), seen from the modulation point, becomes close to the open circuit point [14], [15]. However, these techniques themselves would limit the bandwidth as the PA's output impedance cannot be transformed to the open circuit in a wide frequency range. This is where this work differs from previous ones. Instead of ignoring the loading effects of the Auxiliary on the Main PA, we include the Auxiliary, or rather its extracted loading effect, while designing the OMN of the Main PA. This allows a more accurate compensation of the Auxiliary's loading effect onto the Main one.

The developed design method will be presented through the design and implementation of a 40 W DPA targeting the n78 5G band. In particular, the approach is based on a systematic procedure for designing the MNs of both Main and Auxiliary devices, which employs an optimization process to set their input impedance in the corresponding optimal regions. These optimum regions are simply related to the power and efficiency contours levels, which are the result of load- and source-pull simulations. It is worth mentioning that although

FIGURE 1. Block diagram of an inverter-less DPA with a post-MN.

it is traditionally known to consider the optimal regions for MN design, its application in an optimization-based systematic CAD requires expressing the optimal regions using mathematical expressions, which are, in turn, used to define the optimization goal. This has been the subject of some very recent works, however, mainly for a single transistor PA [6], [16], [17], [18], [19].

### **II. DESIGN PROCEDURE**

The proposed design strategy is explained together with the implementation of a DPA with a typical peak power of 40 W for n78 5G frequency band (i.e., 3.3 - 3.8 GHz). However, as a safe margin to account for any frequency shift in the realization, the specified bandwidth is extended to 3.2 - 4 GHz. Both Main and Auxiliary PAs use the same packaged 25 watt GaN HEMTs from Wolfspeed (CG2H40025F). The Main and Auxiliary transistors are biased in classes AB and C, respectively [4]. Moreover, to compensate for the lower gain of a class C, the drain voltage ( $V_{DS}$ ) of the Auxiliary was set to a higher value with respect to the Main one [20]. Specifically,  $V_{DS}$  was set to 28 V and 33 V for the Main and Auxiliary PAs, respectively.

The overall topology uses a transformer-less loadmodulated architecture [5] along with post-matching impedance transformation [6], [7], [8], [9], [10], as shown in FIGURE 1. The transistor's load-pull simulations show that the optimum drain impedances for different bias conditions are in the order of a few ohms. Therefore, to simplify the design of the OMNs, the reference impedance is first set to  $Z'_0 = 5 \Omega$ , and then transformed to  $Z_0 = 50 \Omega$  through the synthesis of a post MN (PMN). The value of  $Z'_0$  is chosen to be close to the real part of the transistor's desired impedance in the frequency band of interest to simplify the design of the OMNs. The DPA implementation starts with the design of the Auxiliary PA, then the Main PA is designed, accounting for the loading effect of the Auxiliary at back-off. In the following, each step of the developed procedure is described in detail. All the simulations were performed using PathWave Advanced Design System (ADS).

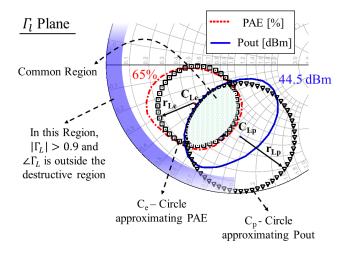

**FIGURE 2.** A sample of load-pull result. The chosen PAE and Pout contours (PAE = 65% and Pout = 44.5 dBm) form a common region which can be approximated with arcs from two circles. A portion of the allowed region for the second harmonic termination is also shown in blue shade.

| f [GHz] | $C_{Lp}$                            |          | $r_{Lp}$              | C <sub>Le</sub>                     |      | $r_{Le}$ |  |  |

|---------|-------------------------------------|----------|-----------------------|-------------------------------------|------|----------|--|--|

| 3.2     | $0.50 \measuredangle - 110^{\circ}$ |          | 0.48                  | $0.364 - 175^{\circ}$               |      | 0.40     |  |  |

| 3.45    | $0.55 \measuredangle - 100^{\circ}$ |          | 0.45                  | $0.38 at - 158^{\circ}$             |      | 0.36     |  |  |

| 3.75    | $0.534-90^{\circ}$                  |          | 0.42                  | $0.42 \cancel{4} - 138^{\circ}$     |      | 0.33     |  |  |

| 4       | $0.55 \measuredangle - 82^{\circ}$  |          | 0.40                  | $0.46 \measuredangle - 125^{\circ}$ |      | 0.30     |  |  |

| (a)     |                                     |          |                       |                                     |      |          |  |  |

|         |                                     | f [GHz]  |                       | Cs                                  |      | rs       |  |  |

|         | 3.2 0.6                             |          | $674 - 110^{\circ}$ 0 |                                     | 0.28 |          |  |  |

|         |                                     | 3.45 0.6 |                       | 59 <b>4 -</b> 102                   | °    | 0.26     |  |  |

|         |                                     | 3.75     | 0.                    | 774 – 92                            | 0    | 0.18     |  |  |

|         |                                     | 4        | 0.                    | 784 – 85                            | 0    | 0.15     |  |  |

| (b)     |                                     |          |                       |                                     |      |          |  |  |

**FIGURE 3.** The centers and radii of the circles defining the optimum regions for the load (a) and source (b) terminations of the auxiliary amplifier. In (a), subscripts p and e stand for Pout and PAE circles, respectively.

### A. DESIGN OF THE AUXILIARY AMPLIFIER

By setting the available power from the source (Pavs) to around 33 dBm, which makes the device saturated, loadand source-pull simulations at several frequencies within the desired bandwidth (i.e., 3.2 - 4 GHz) were performed under a gate-source and a drain-source voltages of  $V_{GS} = -4.6 V$  and  $V_{DS} = 33 V$ , respectively. At each frequency point, multiple contours of power added efficiency (PAE) and output power (Pout) were acquired on the smith chart. For PAE, the contour corresponding to 65 % (around 10 % lower than the maximum efficiency), and for Pout, the contour corresponding to 44.5 dBm (around 1 dB lower than the maximum Pout) were chosen, and the entire common region between these PAE and Pout contours was considered as design goals for the MNs. To synthesize a termination within this common region, we need first to define this region by a mathematical expression; then, it would be possible to consider a MN with

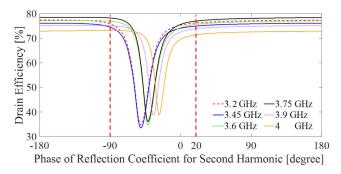

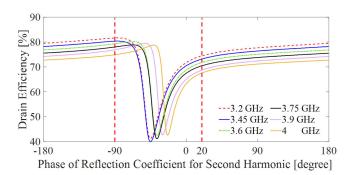

**FIGURE 4.** DE versus the phase of  $\Gamma_L$  at second harmonic (while its magnitude is fixed at 0.9) for the Auxiliary device.

an arbitrary topology having some tunable parameters (for example, a multi-section transmission line where the length and width of the sections can be tuned [21], [22], and apply an optimization algorithm to take the input impedance of the considered MN inside the defined region. To this end, the sections of PAE and Pout contours forming the borders of the common region were approximated by two arcs (of two circles) as shown in FIGURE 2 (black symbols) for the output plane. Then, when designing the MNs, the radius and center of these circles are used to define the design (optimization) goal as,

$$\begin{aligned} \left| \Gamma(f_i) - C_p(f_i) \right| &\leq r_p(f_i) \\ &\& \\ \left| \Gamma(f_i) - C_e(f_i) \right| &\leq r_e(f_i), \end{aligned} \tag{1}$$

where  $f_i$  are the frequency points,  $\Gamma$  is the input reflection coefficient of the MN (seen from the transistor's drain or gait in the case of the OMN and input MN (IMN), respectively),  $C_p$  and  $r_p$  are the radius and center of the circle fitted to the section of the power contour forming a border of the desired region, and  $C_e$  and  $r_e$  are those of the circle fitted to the efficiency contour.

The centers and radii of the circles defining the optimum region for the load and source terminations (in other words, the IMN and OMN design spaces) are given in FIGURE 3 (a) and (b), respectively, for four frequencies. Since the PAE and Pout circles of the source termination almost completely overlap each other, only one circle was considered for defining the optimum region for the IMN synthesis.

Since the transistor's terminations at higher order and specially second harmonic can also impact the PA's performance [23], [24], [25], the MNs are commonly designed in a way that the reflection coefficient at higher frequency with respect to the useful bandwidth is on the border of the Smith chart with a proper phase. To investigate the effect of the second harmonic termination, we performed simulations at several frequencies in which, by keeping the fundamental source and load terminations at the center of the corresponding optimal region, the phase of the load reflection coefficient ( $\Gamma_L$ ) at second harmonic was swept from -180 to 180 degrees, while its magnitude was fixed at 0.9. FIGURE 4

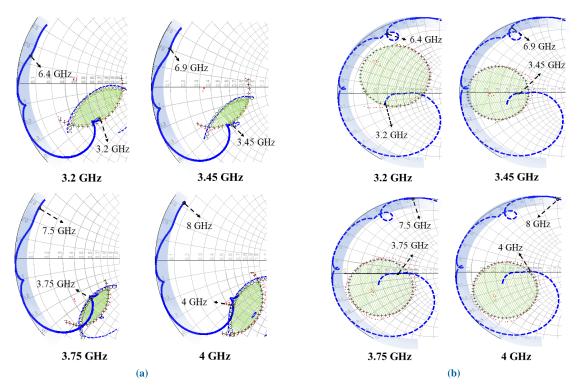

**FIGURE 5.** The impedance trajectory of the optimized OMN of the Auxiliary PA. The optimum regions of the load at fundamental and the suitable region for the second harmonic termination are shown by green and blue shading, respectively. The contours corresponding to Pout = 44.5 dBm and PAE = 65 % are also depicted by blue-dashed and red-dotted lines, respectively.

shows the variation of the drain efficiency (DE) versus the phase of the second harmonic termination, wherein a detrimental effect on efficiency is noted from -90 to 20 degrees for all fundamental frequencies, while elsewhere, the effect is minimal. We concluded that the second harmonic termination does not degrade the PA performance as long as it does not lie in this specific range of phases, which should be avoided in the design procedure. Therefore, when designing the OMN, in addition to (1), the following relations were also considered as a design (optimization) goal,

-----

$$|\Gamma_{\rm L}(2f_i)| \ge 0.9$$

$$\&$$

$$\angle \Gamma_{\rm L}(2f_i) \notin [-90; 20]$$

(2)

The blue ribbon on the periphery of the Smith chart of FIGURE 2 shows the allowed region for the second harmonic termination. The effect of third and higher-order harmonics on performance was observed to be too low to be of any concern.

A network composed of a multi-section transmission line (where the first section is a tapered line) with a high impedance short-circuited stub for biasing the transistor was selected to implement the OMN. Relying upon the positions of the optimum fundamental and second harmonic regions, the width and length of the transmission line sections were obtained through an optimization process setting as a goal the fulfillment of (1) and (2) starting from the impedance  $2Z'_0 =$  $10 \Omega$  (which is the impedance that the OMN of the auxiliary PA sees at the load modulated point at peak condition, as shown in FIGURE 1). FIGURE 5 shows the impedance trajectory of the realized OMN at various frequencies. It is observed that at every frequency, the fundamental falls in the optimum region, as well as the second harmonic. This concludes the design process of the OMN of the Auxiliary PA.

In a similar manner, the IMN was also designed to synthesize a source impedance inside the optimum circles of the source termination. For the source, the effect of the second harmonic termination can be ignored.

### B. DESIGN OF THE MAIN AMPLIFIER

By biasing the transistor in class AB with a  $V_{DS} = 28$  V and a quiescent drain current of  $I_{DQ} = 120 \text{ mA}$ , load-pull simulations were performed in two conditions: peak condition wherein the transistor is saturated, and back-off condition where Pout is expected to be 3 dB lower. To achieve these conditions, in trial and error simulations, Pavs was set around 33 dBm for peak and 27.5 dBm for back-off. At peak power, similar to the Auxiliary PA, the common region between the PAE contour of 65% and Pout contour of 44.5 dBm was considered the optimum one. For having a mathematical expression of this region, the sections of PAE and Pout contours forming the borders of the common region were approximated by arcs of two circles as shown in FIGURE 6(a), where their centers and radii are given in FIGURE 7(a) for four frequencies. At back-off, our sole goal is to maintain high efficiency since the Pout value is fixed by the selected OBO. Therefore only the PAE contour of 50 % was considered as the optimum region, which can be seen in FIGURE 6(b). This figure shows that the PAE contours can be accurately approximated by circles whose centers and radii are given in FIGURE 7(b). Source-pull simulations were performed only in the peak condition and, similar to the Auxiliary amplifier, the contours of PAE and Pout overlapped, hence only one circle is taken into account, as shown in FIGURE 7(c).

For the Main device, the destructive phases for the second harmonic termination ( $\Gamma_L$ ) were also detected to be in the -90 to 20 degrees range, as shown in FIGURE 8.

Once the optimum regions for the transistor's fundamental and second harmonic terminations are defined, the IMN and OMN can be designed to synthesize a termination lies in the optimum regions. While the approach for designing the IMN is identical to that of the Auxiliary PA, the design approach for the OMN is different because a two-state matching is required in the output of the Main PA.

Referring to FIGURE 1, when the auxiliary PA is off, the OMN of the Main PA sees an impedance of  $Z'_0$  at the load modulated point. On the contrary, at peak power, when both PAs are saturated, the OMN of the Main sees a modulated

### **IEEE**Access

FIGURE 6. The impedance trajectory of the optimized OMN of the main PA for (a) Peak and (b) back-off conditions. The optimum regions of the fundamental load termination at four sample frequencies and the allowed region of the second harmonic load termination are also shown in green and blue shading, respectively. In (a), the contours corresponding to Pout = 44.5 dBm and PAE = 65% are depicted by blue-dashed and red-dotted lines, respectively, while in (b), only the contours of PAE = 50% are shown by red dots.

| f [GHz] | $C_{Lp}$             | $r_{Lp}$ | $C_{Le}$                 | $r_{Le}$ |

|---------|----------------------|----------|--------------------------|----------|

| 3.2     | 0.42∡ – 95°          | 0.55     | $0.304 - 185^{\circ}$    | 0.40     |

| 3.45    | 0.37∡ – 95°          | 0.45     | 0.33∡ – 165°             | 0.40     |

| 3.75    | $0.384-88^{\circ}$   | 0.44     | $0.384 - 142^{\circ}$    | 0.35     |

| 4       | $0.434 - 78^{\circ}$ | 0.46     | $0.40 a$ – $130^{\circ}$ | 0.34     |

| f [GHz] | $C_{Le}$                            | $r_{Le}$ |

|---------|-------------------------------------|----------|

| 3.2     | $0.50 \neq -205^{\circ}$            | 0.35     |

| 3.45    | $0.48$ 4 $-188^{\circ}$             | 0.38     |

| 3.75    | $0.50 \neq -158^{\circ}$            | 0.33     |

| 4       | $0.50 \measuredangle - 147^{\circ}$ | 0.29     |

|         |                                     |          |

| f [GHz] | Cs                      | rs   |

|---------|-------------------------|------|

| 3.2     | $0.48$ 4 $-104^{\circ}$ | 0.45 |

| 3.45    | 0.57∡ – 96°             | 0.37 |

| 3.75    | 0.684 – 90              | 0.27 |

| 4       | $0.75 \pm - 82^{\circ}$ | 0.19 |

|         |                         |      |

(c)

FIGURE 7. The centers and radii of the circles defining the optimum regions for the load termination at peak (a) and back-off (b) conditions and the source termination (c) of the Main PA. Subscripts p and e stand for Pout and PAE circles, respectively.

impedance of  $2Z_0'.$  Therefore, the Main PA's OMN must transfer impedances of  $2Z_0'~=~10\Omega$  and  $Z_0'~=~5\Omega$  to the

FIGURE 8. DE versus the phase of  $\Gamma_{\rm L}$  at second harmonic (while its magnitude is fixed at 0.9) for the Main PA.

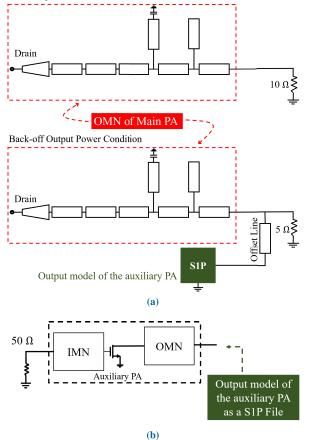

optimum regions obtained for the peak and back-off conditions, respectively. On the other hand, for accurate modeling and design of a DPA, the loading effect of the Auxiliary on the Main PA must also be considered. At peak power and for a symmetric DPA, both amplifiers inject almost the same current into the output load; thus, the loading effects of the amplifiers on each other can be accurately modeled by modulating the load impedance of  $Z'_0$  to  $2Z'_0$ . On the contrary, at back-off, the Auxiliary PA is off and plays the role of a reactive load for the Main. As shown in FIGURE 9 (a), to account for this loading effect, we have included a model of the Auxiliary (wherein the transistor is off) in the design process Peak Output Power Condition

**FIGURE 9.** Procedure used to design the OMN of the Main PA. **FIGURE 9(a)** depicts a two-state matching: at peak power, the amplifier is terminated with a 10  $\Omega$  load. At back-off, the amplifier is connected to 5  $\Omega$  in parallel to an offset line which is terminated with the extracted model of the Auxiliary at back-off. This model was extracted using a simulation setup as depicted in FIGURE 9(b).

of the Main PA. In particular, using small-signal simulations, the output impedance of the Auxiliary PA designed in the previous stage (including its MNs) was extracted in the entire band. This extracted impedance was then used in the design process of the OMN of the Main in the form of a touchstone (S1P) file, as shown in FIGURE 9(b).

A multi-section transmission line network (where the first section is tapered) with a short-circuited and an open-ended stub (as shown in FIGURE 9(a)) was considered for the OMN of the Main PA. The length and width of the transmission line sections, along with the length of the offset line connecting the Auxiliary to the Main, were obtained through an optimization procedure to achieve the two-state matching conditions described previously. Also, in this case, the allowed regions for the second harmonic termination were considered as design goals. The impedance trajectory of the finalized OMN is reported in FIGURE 6. It can be seen that the trace lies in the corresponding optimum regions at both peak (see FIGURE 6(a)) and back-off (see FIGURE 6(b)) conditions. At the same time, the second harmonic in the entire band lies inside the allowed region.

**FIGURE 10.** (a) Optimum load impedance region of the Auxiliary device for gate voltage from -4.6 V to -6 V. (b) Loading effect of the turned-off Auxiliary PA on the Main one at back-off for gate voltage from -4.6 V to -6 V.

### C. DPA INTEGRATION

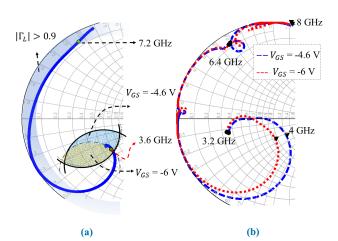

The designed Main and Auxiliary PAs were combined together, and a further investigation was carried out. In particular, being the DPA's performance significantly affected by the bias point of the Auxiliary PA, we evaluated, by performing an additional set of simulations, the effect of changing its  $V_{GS}$  on: 1) its optimum load impedances at its saturation, and 2) its loading on the Main PA when it is turned off. The results are shown in FIGURE 10 for  $V_{GS}$  within -4.6 V to -6 V. FIGURE 10(a) shows the optimum regions of  $\Gamma_{\text{L}}$ (i.e., the regions for Pout > 44.5 dBm and PAE > 65%) at the center frequency (3.6 GHz) for  $V_{GS} = -4.6$  V and -6 V by blue and green shading, respectively, together with the synthesized impedance across the drain of the Auxiliary device by the OMN designed in Section II-A. Notably, even if the variation of the bias point modifies the location of the optimum region, the designed OMN is flexible enough to handle such an eventual need correctly since the realized impedance at 3.6 GHz lies inside the two regions. For the same  $V_{GS}$  values, FIGURE 10(b) reports the behavior of the loading effect of the turned-off Auxiliary PA on the Main one at back-off. Clearly, different  $V_{GS}$  values lead to different touchstone models of the Auxiliary PA (see FIGURE 9(b)), which results in different impedances synthesized at the Main device's output at back-off as observed in FIGURE 10(b). However, it can be seen that this effect is not dramatic, and the impedance trajectories are not far away.

At the input, a Gysel power splitter [26] is adopted to equally split the power between the two PAs. Compared to a Wilkinson power divider, Gysel's grounded resistive terminations help with better power handling, and by keeping parasitic capacitances out of the main signal path, unlike a Wilkinson divider, the parasitics do not play a significant role here. Suitable delay lines were calculated and inserted in the input path of the amplifier branches to ensure zero loss in power combination at the output.

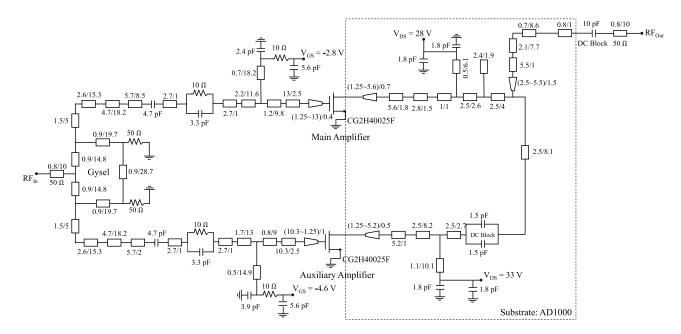

FIGURE 11. Schematic of the designed DPA. Transmission line width and length (W/L) are reported in millimeters.

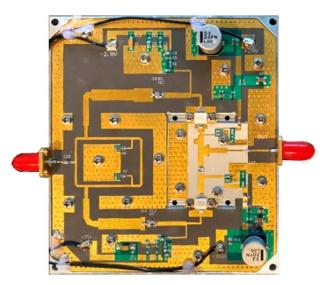

FIGURE 12. Picture of the fabricated DPA.

The DPA was then completed with a three-section postmatching circuit that transforms  $Z'_0 = 5 \Omega$  to the standard load  $Z_0 = 50 \Omega$ .

A schematic of the realized DPA is reported in FIGURE 11, whereas a picture is shown in FIGURE 12. It is worth mentioning that the DPA was designed and fabricated on two different substrates. The input splitter, IMNs, DC source connections, and a small 50  $\Omega$  line at the output were fabricated on a 10-mil RT/duroid 5880 substrate. The OMNs were fabricated on a 10-mil AD1000 substrate. The difference in substrate material is because of size considerations, where the higher dielectric permittivity of AD1000 helps with the miniaturization of the OMNs, which in turn helps with arranging the whole design.

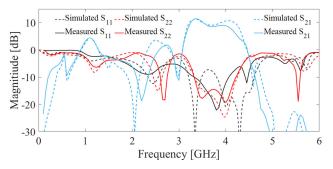

FIGURE 13. Comparison between measured and simulated S-parameters of the DPA.

### **III. RESULTS**

Before performing high-power tests on the fabricated amplifier, its small-signal parameters were measured and compared with the simulation results. The S-parameters measured in the biasing condition  $V_{DD,Main} = 28$  V and  $V_{GS,Main} = -2.6$  V,  $V_{DS,Aux} = 32$  V and  $V_{GS,Aux} = -9$  V, are reported in FIGURE 13, showing a good agreement with the simulated counterpart.

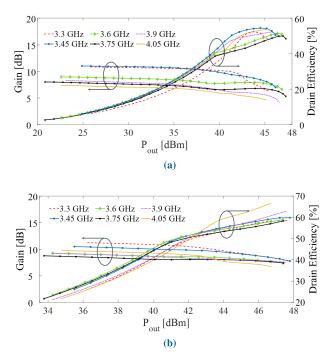

After that, the DPA was tested in continuous wave (CW) conditions. For each frequency in the band, the input power was swept from 20 dBm until the saturation was observed. FIGURE 14(a) shows the registered DE and gain as functions of the output power at various frequency points. Notably, the efficiency traces clearly show the trademark behavior associated with a DPA, signifying the fact that the Auxiliary transistor is tuned on properly and the load pulling is affecting the Main amplifier correctly. FIGURE 14(b) shows the simulation results that are reasonably in agreement with the measurements.

| Ref.      | Operating Freq. | Fractional BW | Minimum saturated $P_{out}$ | DE @ peak | DE @ back-off       |  |

|-----------|-----------------|---------------|-----------------------------|-----------|---------------------|--|

|           | [GHz]           | [%]           | [dBm]                       | [%]       | [%]                 |  |

| [27]      | 3.1 - 3.7       | 18            | 43.1                        | 65 - 72   | 40 - 45 @ 8 dB OBO  |  |

| [28]      | 3.05 - 3.55     | 15            | 42.3                        | 61 - 75   | 51 - 65 @ 6 dB OBO  |  |

| [29]      | 2.8 - 3.55      | 24            | 43                          | 66 - 78   | 50 - 60 @ 6 dB OBO  |  |

| [30]      | 3.4 - 3.6       | 6             | 46.6                        | 63 - 66   | 47 - 49 @ 12 dB OBO |  |

| [31]      | 3.4 - 3.5       | 3             | 49.5                        | 59 - 63   | 46 - 50 @ 6 dB OBO  |  |

| [32]      | 2.8 - 3.6       | 25            | 43                          | 62 - 76.5 | 44 - 56 @ 6 dB OBO  |  |

| This Work | 3.3 - 3.9       | 17            | 45.6                        | 48 - 53.2 | 35 - 45 @ 6 dB OBO  |  |

FIGURE 14. Measurement (a) and simulation (b) results of the fabricated DPA. DE and gain are plotted vs output power.

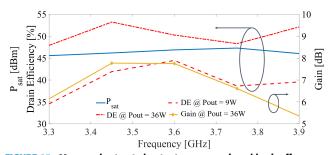

In FIGURE 15, the measured performance of the DPA are reported versus frequency. The amplifier shows a working bandwidth of 600 MHz, from 3.3 to 3.9 GHz (n78 channel of 5G-NR). In this frequency range, it delivers at least 36 W (45.6 dBm) of saturated output power. The power gain and DE at this level of Pout (i.e., 36 W) and the DE at 6 dB of back-off from this level (i.e., 9W) are also reported in the figure. It can be seen that the DE varies between 48-53.2 % (PAE of 36.2 - 44.2 %) at peak (36 W) and between 35 - 45 %(PAE of 30.3-37.7%) at back-off (9W) as reported in TABLE 1. The table also compares the performance of the fabricated DPA with other S-band DPAs reported in the literature. Notice that the two DPAs with a saturated Pout higher than this work have very narrow bandwidths, and the ones with comparable bandwidths have significantly lower Pout.

**FIGURE 15.** Measured saturated output power, peak and back-off efficiency, and power gain of the fabricated DPA in the entire frequency band.

#### **IV. CONCLUSION**

Evolving communication standards require improved methods for designing subsystems, including power amplifiers. This paper presented the design of a quarterwave transformer-less DPA using an improved method. By performing standard load- and source-pull simulations and considering proper target values of Pout and PAE, the optimum regions of the fundamental and second harmonic terminations of the transistor were obtained for the Auxiliary at peak power and for the Main at peak and back-off power conditions. By approximating the Pout and PAE contours by circles, mathematical expressions were derived for the optimum regions, which were then applied as optimization goals in the design process of the MNs. Furthermore, in the design process of the Main PA's OMN, for more accurate modeling of the loading effect of the Auxiliary on the Main PA at the back-off condition and hence a more precise design of the Main, a model of the output impedance of the Auxiliary amplifier (when its transistor is off) was used.

The proof of concept amplifier was designed and built for the n78 band of 5G-NR. In the frequency band from 3.3 to 3.9 GHz, which corresponds to a fractional bandwidth of 16.7%, it achieved a minimum saturated output power of 36 W, while maintaining a DE of around 50% at saturation (36 W) and 40% at 6 dB output back-off.

### REFERENCES

S. Han and S. Bian, "Energy-efficient 5G for a greener future," *Nature Electron.*, vol. 3, no. 4, pp. 182–184, Apr. 2020.

- [2] W. H. Doherty, "A new high efficiency power amplifier for modulated waves," *Proc. IRE*, vol. 24, no. 9, pp. 1163–1182, Nov. 1936.

- [3] M. Iwamoto, A. Williams, P.-F. Chen, A. Metzger, C. Wang, L. E. Larson, and P. M. Asbeck, "An extended Doherty amplifier with high efficiency over a wide power range," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Phoenix, AZ, USA, May 2001, pp. 931–934.

- [4] P. Colantonio, F. Giannini, R. Giofrè, and L. Piazzon, "The AB-C Doherty power amplifier. Part I: Theory," *Int. J. RF Microw. Comput.-Aided Eng.*, vol. 19, no. 3, pp. 293–306, May 2009.

- [5] M. Akbarpour, M. Helaoui, and F. M. Ghannouchi, "A transformer-less load-modulated (TLLM) architecture for efficient wideband power amplifiers," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 9, pp. 2863–2874, Sep. 2012.

- [6] S. Rafati, V. Nayyeri, and M. Soleimani, "A 100-W Doherty power amplifier with super-octave bandwidth," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 6, pp. 1009–1013, Jun. 2020.

- [7] J. Pang, S. He, C. Huang, Z. Dai, J. Peng, and F. You, "A post-matching Doherty power amplifier employing low-order impedance inverters for broadband applications," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 12, pp. 4061–4071, Dec. 2015.

- [8] J. Pang, S. He, Z. Dai, C. Huang, J. Peng, and F. You, "Design of a post-matching asymmetric Doherty power amplifier for broadband applications," *IEEE Microw. Wireless Compon. Lett.*, vol. 26, no. 1, pp. 52–54, Jan. 2016.

- [9] X. Y. Zhou, S. Y. Zheng, W. S. Chan, X. Fang, and D. Ho, "Postmatching Doherty power amplifier with extended back-off range based on self-generated harmonic injection," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 4, pp. 1951–1963, Apr. 2018.

- [10] X. Zhou, S. Y. Zheng, W. S. Chan, S. Chen, and D. Ho, "Broadband efficiency-enhanced mutually coupled harmonic postmatching Doherty power amplifier," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 7, pp. 1758–1771, Jul. 2017.

- [11] H. Kang, H. Lee, W. Lee, H. Oh, W. Lim, H. Koo, C.-S. Park, K. C. Hwang, K.-Y. Lee, and Y. Yang, "Octave bandwidth Doherty power amplifier using multiple resonance circuit for the peaking amplifier," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 2, pp. 583–593, Feb. 2019.

- [12] W. Kong, J. Xia, X. Zhou, T. Zhang, W. Zhang, and X. Bao, "Bandwidth extension of three-way Doherty power amplifier with reactance compensation using parallel peaking amplifiers," *IEEE Access*, vol. 9, pp. 91661–91669, 2021.

- [13] J. X. Sun, F. Lin, X. Y. Zhou, and X. Zhu, "Design of 74% fractional bandwidth continuous-mode Doherty power amplifier using compensation susceptance," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 68, no. 6, pp. 1827–1831, Jun. 2021.

- [14] X. Fang and K.-K.-M. Cheng, "Broadband, wide efficiency range, Doherty amplifier design using frequency-varying complex combining load," in *IEEE MTT-S Int. Microw. Symp. Dig.*, May 2015, pp. 1–4.

- [15] J. Xia, M. Yang, Y. Guo, and A. Zhu, "A broadband high-efficiency Doherty power amplifier with integrated compensating reactance," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 7, pp. 2014–2024, Jul. 2016.

- [16] M. Ghazizadeh and V. Nayyeri, "Design of a 50-W power amplifier with two—Octave bandwidth and high-efficiency using a systematic optimization approach," *IEEE Microw. Wireless Compon. Lett.*, vol. 31, no. 5, pp. 501–504, May 2021.

- [17] M. Ghazizadeh, S.-H. Javid-Hosseini, and V. Nayyeri, "A 90 W 1–3 GHz power amplifier module," in *Proc. 50th Eur. Microw. Conf. (EuMC)*, Jan. 2021, pp. 17–20.

- [18] Y. Zhuang, Z. Fei, A. Chen, Y. Huang, and K. Rabbi, "Design of multioctave high-efficiency power amplifiers using stochastic reduced order models," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 2, pp. 1015–1023, Feb. 2018.

- [19] P. Jia, F. You, S. He, and X. Qian, "A 0.25–1.25-GHz high-efficiency power amplifier with computer-aided design based on optimized impedance solution continuum," *IEEE Microw. Wireless Compon. Lett.*, vol. 28, no. 5, pp. 443–445, May 2018.

- [20] P. Colantonio, F. Giannini, R. Giofre, M. Piacentini, and L. Piazzon, "A design approach to increase gain feature of a Doherty power amplifier," in *Proc. Eur. Microw. Integr. Circuits Conf. (EuMIC)*, 2009, pp. 25–28.

- [21] H. T.-A. Nia and V. Nayyeri, "A 0.85–5.4 GHz 25-W GaN power amplifier," *IEEE Microw. Wireless Compon. Lett.*, vol. 28, no. 3, pp. 251–253, Mar. 2018.

- [22] H. Taleb-Alhagh Nia, S.-H. Javid-Hosseini, and V. Nayyeri, "Design and implementation of a wideband, highly-efficient, high-power amplifier using load-pull and X-parameters models," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 11, pp. 2372–2376, Nov. 2020.

- [23] S. Dudkiewicz, M. S. Tenberge, G. Esposito, and T. Barbieri, "Understanding the relevance of harmonic impedance matching in amplifier design," *Microw. J.*, vol. 58, pp. 112–122, Apr. 2015.

- [24] P. Colantonio, "A C-band high-efficiency second-harmonic-tuned hybrid power amplifier in GaN technology," *IEEE Trans. Microw. Theory Techn.*, vol. 54, no. 6, pp. 2713–2722, Jun. 2006.

- [25] X. Y. Zhou, W. S. Chan, D. Ho, and S. Y. Zheng, "Loading the third harmonic: A linear and efficient post-matching Doherty PA," *IEEE Microw. Mag.*, vol. 19, no. 1, pp. 99–105, Jan. 2018.

- [26] U. H. Gysel, "A new N-way power divider/combiner suitable for highpower applications," in *IEEE MTT-S Int. Microw. Symp. Dig.*, May 1975, pp. 116–118.

- [27] Z. Zhang, Z. Cheng, G. Liu, Z. Zhang, and Y. Cai, "Design of a broadband high-efficiency Doherty power amplifier for 5G communication systems," *IEICE Electron. Exp.*, vol. 16, no. 14, 2019, Art. no. 20190371.

- [28] J. Pang, "Analysis and design of highly efficient wideband RF-input sequential load modulated balanced power amplifier," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 5, pp. 1741–1753, Jan. 2020.

- [29] M. Li, J. Pang, Y. Li, and A. Zhu, "Bandwidth enhancement of Doherty power amplifier using modified load modulation network," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 6, pp. 1824–1834, Jun. 2020.

- [30] J. Xia, T. Zhang, J. Cai, X. Zhou, D. Ding, W. Kong, and X. Bao, "Design of a 12 db back-off asymmetric Doherty power amplifier using reactive output impedance," *IEICE Electron. Exp.*, vol. 17, no. 11, 2020, Art. no. 20200156.

- [31] J. Xia, X. Zhu, L. Zhang, J. Zhai, and Y. Sun, "High-efficiency GaN Doherty power amplifier for 100-MHz LTE-advanced application based on modified load modulation network," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 8, pp. 2911–2921, Aug. 2013.

- [32] A. Nasri, M. Estebsari, S. Toofan, A. Piacibello, M. Pirola, V. Camarchia, and C. Ramella, "Design of a wideband Doherty power amplifier with high efficiency for 5G application," *Electronics*, vol. 10, no. 8, p. 873, Apr. 2021.

**MOHAMMAD SHAHMORADI** was born in Isfahan, Iran. He received the B.Sc. degree in electrical engineering from Shahrekord University, Shahrekord, Iran, in 2018, and the M.Sc. degree in satellite engineering from the Iran University of Science and Technology (IUST), Tehran, Iran, in 2021. His research interests include microwave power amplifiers, filters, and antennas.

**SAYYED-HOSSEIN JAVID-HOSSEINI** was born in Tehran, Iran. He received the B.Sc. degree in electrical engineering from the K. N. Toosi University of Technology, Tehran, in 2014, and the M.Sc. degree in satellite engineering from the Iran University of Science and Technology (IUST), Tehran, in 2018, where he is currently pursuing the Ph.D. degree in satellite engineering.

Since 2015, he has been an Antenna and RF-Circuit Designer with ACECR, Nasir Branch, terrets include antennas and active and pessive

Tehran. His research interests include antennas and active and passive microwave circuits.

**VAHID NAYYERI** (Senior Member, IEEE) received the B.Sc. degree in electrical engineering from the Iran University of Science and Technology (IUST), Tehran, Iran, in 2006, the M.Sc. degree in electrical engineering from the University of Tehran, Tehran, in 2008, and the Ph.D. degree in electrical engineering from IUST, in 2013.

From 2007 to 2013, he was a Research Assistant with IUST and a Visiting Scholar with the Uni-

versity of Waterloo, ON, Canada. In 2013, he joined the Faculty of IUST, where he is currently an Associate Professor, the Director of the Advanced Radio Circuits and Systems Laboratory, and the Head of the Department of Satellite Technology. In 2019, he was a Visiting Professor with the University of Waterloo. He has authored and coauthored one book (in Persian) and more than 100 technical articles. His research interests include applied and computational electromagnetics and microwave active and passive circuits.

Dr. Nayyeri serves as a Member of the Board of Directors for the IEEE Iran Section, the Chair of the Membership Development Committee, and a Steering Committee Member for the Electromagnetics and Photonics Chapter. He received the Best Ph.D. Thesis Award from the IEEE Iran Section, in 2014. He was a Guest Editor of two Special Issues of *Sensors*, in 2019 and 2020. Currently, he serves as an Associate Editor for the IEEE TRANSACTIONS ON MICROWAVES THEORY TECHNIQUES and the *IET Microwaves*, *Antennas and Propagation*.

**PAOLO COLANTONIO** (Senior Member, IEEE) received the Laurea degree in electronics engineering and the Ph.D. degree in microelectronics and telecommunications from the University of Rome Tor Vergata, Rome, Italy, in 1994 and 2000, respectively. He is currently a Full Professor of microwave electronics with the University of Roma Tor Vergata. He is the author or coauthor of more than 300 scientific articles. He has authored the book *High Efficiency RF and Microwave Solid*

*State Power Amplifiers* (Wiley, 2009), three book chapters, four contributions to *Encyclopaedia of RF and Microwave Engineering* (Wiley), and one international patent. His research interests include the field of microwave and millimeter-wave electronics, in particular, the design criteria for nonlinear microwave subsystems and high-efficiency power amplifiers. He was the Chair of EuMIC, in 2022. He is currently an Associate Editor of IEEE MICROWAVE AND WIRELESS LETTERS.

. . .

**ROCCO GIOFRÈ** (Senior Member, IEEE) received the Ph.D. degree in electronics from the University of Rome Tor Vergata, Rome, Italy, in 2008. He joined the Electronics Engineering Department, University of Rome Tor Vergata, in 2009, where he is currently an Associate Professor of electronics. He is involved in many research projects funded by international research agencies, such as the European Space Agency (ESA) and the Research Executive Agency (REA) of the

European Commission. He has published more than 190 peer-reviewed articles, two book chapters, and two contributions for the *Wiley Encyclopedia* of Electrical and Electronics Engineering. His research interests include the microwave- and millimeter-wave electronics area ranging from active device characterization to the design and test of linear and nonlinear circuits and systems. In this wide research area, he is mainly focused on the development of innovative power amplifier schemes and architectures with high efficiency and linearity for both ground and space communication systems, including their integration in multifunctional chips, such as single-chip front ends. He is a member of the IEEE MTT-S Subcommittee 12 on Power Amplifiers. He was a recipient of the 2005 Young Graduated Research Fellowship presented by the GAAS Association and the Best Paper Award at EuMIC, in 2007. He is an Associate Editor of IEEE ACCESS journal and a reviewer of the major journals and conferences of the field.

Open Access funding provided by 'Università degli Studi di Roma "Tor Vergata"' within the CRUI CARE Agreement