Received 16 December 2022, accepted 24 January 2023, date of publication 30 January 2023, date of current version 7 February 2023. Digital Object Identifier 10.1109/ACCESS.2023.3240649

# **RESEARCH ARTICLE**

# New Load Modulation Combiner Having a Capability of Back-Off Control for Doherty Power Amplifiers

YIFEI CHEN<sup>1</sup>, WOOJIN CHOI<sup>®1,2</sup>, JAEKYUNG SHIN<sup>®1,2</sup>, HYEONGJIN JEON<sup>1,2</sup>, SOONCHEOL BAE<sup>®1</sup>, YOUNG CHAN CHOI<sup>®1</sup>, CHEON-SEOK PARK<sup>1</sup>, KANG-YOON LEE<sup>®1</sup>, (Senior Member, IEEE), KEUM CHEOL HWANG<sup>®1,2</sup>, (Senior Member, IEEE), AND YOUNGOO YANG<sup>®1,2</sup>, (Senior Member, IEEE)

<sup>1</sup>Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon 16419, South Korea <sup>2</sup>para-PA Inc., Suwon 16419, South Korea

Corresponding author: Youngoo Yang (yang09@skku.edu)

This work was supported by the National Research Foundation of Korea (NRF) Grant funded by the Korean Government (MSIT) under Grant 2018R1A2B3005479.

**ABSTRACT** A new load modulation combiner (LMC) having the capability of back-off control is proposed for a Doherty power amplifier (DPA). The proposed LMC consists of two transmission lines tied at the combining node, and a shunt element across the other ends of the transmission lines. The shunt element of the LMC becomes virtually open-circuited at the peak power level and allows the carrier amplifier to have an arbitrary load impedance at the low power level. The operating principle and circuit structure of the DPA based on the proposed LMC are presented in detail. The proposed DPA was implemented using GaN-HEMT for the 3.5 - 4.0 GHz band. Using a 5G NR signal with a peak-to-average power ratio (PAPR) of 7.9 dB and signal bandwidth of 100 MHz, the implemented DPA showed drain efficiency (DE) of 49.6 - 54.4% and power gain of 11.1 - 13.0 dB at an average output power of 34.5 dBm. An adjacent channel leakage power ratio (ACLR) was obtained as -50.4 - -45.0 dBc at the average power level with a digital pre-distortion (DPD) technique.

**INDEX TERMS** Load modulation combiner, Doherty power amplifier, extended OBO level, GaN-HEMT.

#### I. INTRODUCTION

Since the modulated signals with high PAPR have been adopted in modern communication systems, many research efforts to improve the efficiency of power amplifiers with large output power back-off (OBO) levels have been initiated [1], [2], [3], [4], [5], [6], [7], [8], [9], [10], [11], [12], [13], [14], [15], [16], [17], [18], [19], [20], [21]. Due to the simple circuit and excellent efficiency improvement characteristics through a wide output power range, DPAs have been widely used for base-transceiver systems. The OBO level for the efficiency peak of the conventional DPA is limited to 6 dB,

The associate editor coordinating the review of this manuscript and approving it for publication was Tae Wook Kim<sup>10</sup>.

while the PAPRs of many modulated signals have become larger than 6 dB.

To extend the OBO level, several well-known methods based on an asymmetric structure, such as asymmetric DPAs [1], [2], [3], multi-way DPAs [4], [5], [6], and multi-stage DPAs [7], [8], [9], have been proposed. These three methods based on a relatively higher power capacity of the peaking amplifier have obvious disadvantages, such as complicated circuits and reduced power gain. As an alternative, LMBAs were proposed to have an extended OBO level [17], [18]. However, LMBAs suffer from complex and bulky structure as well as relatively low power gain. Recently, alternative methods based on a symmetric structure with modified load networks have been reported [10], [11], [12], [13], [14], [15], [16]. For the methods using modified load networks, the carrier amplifier should be simply designed to have the load impedances in complex values at the combining node for either the low power level, the peak power level, or both power levels, which gives increased load impedance modulation of larger than twice for the carrier amplifier at its current source plane of the transistor. The increased load modulation yields an extended OBO level for peak efficiency of the DPA. For these methods, unlike the conventional DPAs using a quarter-wave transmission line and offset lines, it becomes more complex to design the load network, since the load matching networks should match for both the low and peak power levels, considering the load impedance with a complex value.

In this paper, a new LMC with a simple topology having the capability of back-off control is proposed. The proposed LMC is based on two transmission lines tied at the combining node, and a shunt element at the other ends. The load impedance at the low power level can be independently controlled from that at the peak power level, using the shunt element. At the peak power level, the shunt element becomes virtually open-circuited and does not affect the load impedance for both the carrier and peaking amplifiers. By adjusting the load impedance of the carrier amplifier using the shunt element, the OBO level of DPA can be extended, even using a symmetric structure for the carrier and peaking amplifiers. Offset lines for the carrier and peaking amplifiers are required for the proposed LMC, similar to the conventional LMC [20]. Operational principles and the circuit structure of the DPA based on the proposed LMC are presented. To verify the proposed LMC, a symmetric DPA using GaN HEMT for the frequency range of 3.5 - 4.0 GHz was designed, implemented, and evaluated. The simulated and measured results of the proposed DPA are compared to previous state-of-the-art circuits.

#### **II. PRINCIPLE AND ANALYSIS**

## A. LOAD MODULATION ANALYSIS FOR THE PROPOSED LMC

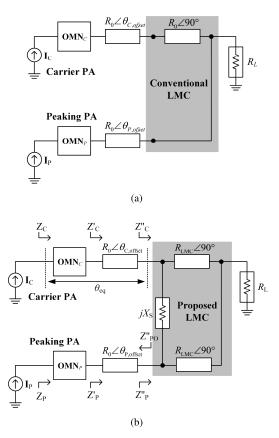

Fig. 1 shows the operational circuit diagrams of the (a) conventional, and (b) proposed LMCs for the symmetrical DPA. Transistors for the carrier and peaking amplifiers are modeled as current sources of  $I_C$  and  $I_P$ , respectively. The output power can be reduced by  $\beta$  times for the low power level compared to the peak output power of the carrier amplifier when operating at the peak power level. The OBO level of the DPA can then be calculated as follows, using the parameter of  $\beta$ .

$$OBO = 10\log(2\beta). \tag{1}$$

For an appropriate operation, the carrier and peaking amplifiers should be fully matched using the matching networks of OMN<sub>C</sub> and OMN<sub>P</sub> for the load impedances of  $Z'_{C,peak}$  and  $Z'_{P,peak}$ , which are real values of  $R_0$  at the peak power level. Two offset lines with a characteristic impedance of  $R_0$ , and with electric lengths of  $\theta_{C,offset}$  and  $\theta_{P,offset}$  are located between the matching networks and the proposed

FIGURE 1. Operational circuit diagrams of the LMCs: (a) conventional, (b) proposed.

LMC for the carrier and peaking amplifiers, as shown. Since the characteristic impedances of the offset lines are the same as the load impedances of the carrier and peaking amplifiers,  $Z'_{C,peak}$  and  $Z'_{P,peak}$  are maintained as  $R_0$  for any electrical lengths of the offset lines at the peak power level. However, at the low power level, the offset lines can tune the output impedance of the peaking amplifier ( $Z'_{PO}$ ) to be infinity, or open-circuited, and can make the load impedance of the carrier amplifier ( $Z'_{C}$ ) to be an optimum value as  $Z'_{C,low}$ . Alternatively,  $Z''_{PO}$  can also be tuned as zero or short-circuited. For this case,  $Z'_{C}$  can become  $Z'_{C,low}$  as well, by tuning the shunt element of  $jX_S$ .

For the conventional LMC, as shown in Fig. 1(a), a quarterwave transmission line is used as an impedance transformer after the carrier amplifier. This quarter-wave line is replaced by the proposed LMC, which includes two quarter-wave transmission lines and a shunt element with a reactance of  $X_S$ , as shown in Fig. 1(b). At the peak power level, since the input power levels at the input ports of the proposed LMC are the same and the load impedances of the carrier and peaking amplifiers after the offset lines ( $Z_{C,peak}^{"}$  and  $Z_{P,peak}^{"}$ ) are the same as well, the voltages at the input ports of the proposed LMC are equal. Then, the shunt element at the LMC is virtually open-circuited with no current through it and does not affect the impedance of the carrier or peaking amplifier

FIGURE 2. Operational diagrams of the LMC: (a) even mode, (b) odd mode.

(b)

at the peak power level. For a load of  $R_L$ , the characteristic impedances of two quarter-wave transmission lines for the proposed LMC can be derived as follows:

$$R_{LMC} = \sqrt{2R_L \mathbf{Z}_{C,peak}''} = \sqrt{2R_L R_0}.$$

(2)

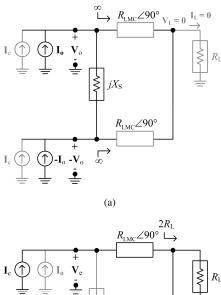

At the low power level, since the output impedance of the peaking amplifier,  $Z_{PO}^{"}$ , can be selected as infinity or zero, the proposed LMC can be simplified with two transmission lines, a shunt element, and the load. Therefore the load impedance after the offset line for the carrier amplifier,  $Z_{C,low}^{"}$ , can be simply derived for two conditions for  $Z_{PO}^{"}$ . As shown in Fig. 2, according to the principle of superposition, the input impedance of the power combiner can be calculated using two independent current sources,  $I_e$  and  $I_o$ , and two input node voltages,  $V_e$  and  $V_o$ . The input impedances of the DPC at the carrier and peaking amplifiers can be derived as follows:

$$\mathbf{Z}_{C}^{\prime\prime} = \frac{\mathbf{V}_{e} + \mathbf{V}_{o}}{\mathbf{I}_{e} + \mathbf{I}_{o}}.$$

(3)

$$\mathbf{Z}_{P}^{\prime\prime} = \frac{\mathbf{V}_{e} - \mathbf{V}_{o}}{\mathbf{I}_{e} - \mathbf{I}_{o}}.$$

(4)

For the even mode condition in Fig. 2(a), the relation between the input current and the node voltage can be simply

calculated as follows:

$$\frac{V_e}{\mathbf{I}_e} = \frac{R_{LMC}^2}{2R_L} = R_0.$$

(5)

For the odd mode condition in Fig. 2(b), the net combined current to the load is zero and the voltage at the load should be zero as well. Then, the relation between the current and voltage at the input of the combiner can be simply derived as follows:

$$\frac{\mathbf{V}_o}{\mathbf{I}_o} = \frac{jX_S}{2}.$$

(6)

Since  $I_o$  should be the same as  $I_e$  for an infinity or open-circuited condition of  $Z''_{PO}$  at the low power level, (3) can be rewritten using (5) and (6) as follows:

$$\mathbf{Z}_{C,low}^{"} = \frac{\mathbf{Z}_{C,peak}^{"}}{2} + \frac{X_S}{4} = \frac{R_0}{2} + \frac{X_S}{4},\tag{7}$$

Similarly, since  $V_o$  should be the same as  $V_e$  for a zero or short-circuited condition of  $Z_{PO}^{"}$ , (2) can be rewritten using (5) and (6) as follows:

$$\mathbf{Z}_{C,low}^{\prime\prime} = (2\mathbf{Z}_{C,peak}^{\prime\prime})||jX_S = (2R_0)||jX_S.$$

(8)

Then,  $Z'_{C,low}$  ( $Z'_C$  in the low power level) can be derived by rotating  $Z''_{C,low}$  clockwise through the constant VSWR circle on the Smith chart normalized by the characteristic impedance of the offset line which is  $R_0$ .

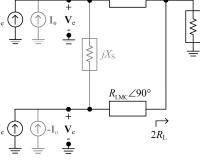

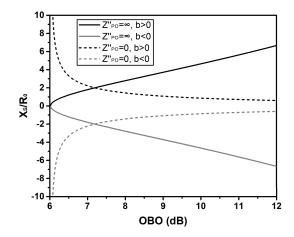

Fig. 3 shows  $Z'_{C,low}$  for the extended OBO levels and the corresponding values of  $X_S$  according to the electrical length of the offset line from 0° to 180° for the symmetric DPA. As the required OBO level increases,  $Z'_{C,low}$  shifts away from the center of the Smith chart as the magnitude of  $X_S$  increases for an infinity or open-circuited condition of  $Z''_{PO}$ , and decreases for a zero or short-circuited condition of  $Z''_{PO}$ . It can then be rotated clockwise through a VSWR circle as the electric length of the offset line ( $\theta_{C,offset}$ ) increases from 0° to 180°. An appropriate impedance point,  $Z'_{C,low}$ , with a length of the offset line can be selected on the circle for the required OBO level to have  $Z_C$  as an optimum load impedance of  $\beta R_{opt}$  at the low power level.

Since the magnitude of the reflection coefficient at each port of the overall load network should be the same for the lossless network, the following relationship can be derived:

$$\left| \frac{\mathbf{Z}_{C,low}^{\prime\prime} - R_0}{\mathbf{Z}_{C,low}^{\prime\prime} + R_0} \right| = \left| \frac{\beta R_{opt} - R_{opt}}{\beta R_{opt} + R_{opt}} \right|.$$

(9)

For various OBO levels, the required reactance of the shunt element for the proposed LMC can be derived using (7)-(9), as follows:

$$X_{S} = \begin{cases} 4abR_{0}, & \text{for } \mathbf{Z}_{PO}^{\prime\prime} \text{ of } \infty \\ \frac{R_{0}}{ab}, & \text{for } \mathbf{Z}_{PO}^{\prime\prime} \text{ of } 0. \end{cases}$$

(10)

**FIGURE 3.**  $Z'_{C,low}$  according to the various values  $\theta_{C,offset}$  for the extended OBO levels and corresponding  $X_S$  values.

where the parameters of a and b are given as

$$a = \sqrt{\beta - \frac{1}{2}},\tag{11}$$

$$b = \pm \sqrt{\frac{1}{2} - \frac{1}{\beta}}.$$

(12)

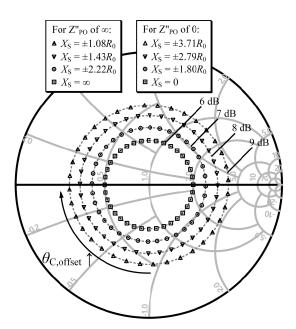

Depending on the sign of *b*, two solution sets can be found for  $X_S$  for each condition of  $Z_{PO}^{"}$ . A positive sign of *b* corresponds to a shunt element with a positive reactance, while the negative sign corresponds to a shunt element with a negative reactance. When *b* equals 0, since the shunt element becomes short-circuited or open-circuited, the proposed LMC functions the same as the conventional LMC with a single quarter-wave transmission line at the carrier amplifier. Since *a* and *b* are functions of  $\beta$ , four sets of  $X_S$  according to the conditions of  $Z_{PO}^{"}$  and the sign of *b* for different OBO levels can be calculated using (1) and (12), and are plotted in Fig. 4.

At the peak power level and the low power level, since the load impedance ( $Z_C$ ) and the input impedance ( $Z_C''$ ) of the LMC are obtained, the load network of the carrier amplifier including the matching network and an offset line can be represented using a 2-port network matrix. For  $Z_{PO}''$  of infinity,

$$\begin{bmatrix} \mathbf{A} & \mathbf{B} \\ \mathbf{C} & \mathbf{D} \end{bmatrix} = \frac{\pm\sqrt{2}}{\sqrt{\beta^2 - 1}} \begin{bmatrix} -\sqrt{\frac{R_{opt}}{R_0}}\beta b & j\sqrt{R_{opt}R_0}a \\ j\sqrt{\frac{1}{R_{opt}R_0}}a & -\sqrt{\frac{R_0}{R_{opt}}}\beta b \end{bmatrix},$$

(13)

**FIGURE 4.** The calculated normalized reactance of the shunt element for various OBO levels.

and for  $Z_{PO}^{\prime\prime}$  of zero,

$$\begin{bmatrix} \mathbf{A} & \mathbf{B} \\ \mathbf{C} & \mathbf{D} \end{bmatrix} = \frac{\pm\sqrt{2}}{\sqrt{\beta^2 - 1}} \begin{bmatrix} \sqrt{\frac{R_{opt}}{R_0}} a & j\sqrt{R_{opt}R_0}\beta b \\ j\sqrt{\frac{1}{R_{opt}R_0}}\beta b & \sqrt{\frac{R_0}{R_{opt}}} a \end{bmatrix}.$$

(14)

The effective electrical length  $(\theta_{eq})$  of the overall load network of the carrier amplifier can be calculated using this 2-port network matrix [22], as follows:

$$\tan(\theta_{eq}) = \begin{cases} -\frac{a}{\beta b}, & \text{for } \mathbf{Z}_{PO}^{\prime\prime} \text{ of } \infty \\ \frac{\beta b}{a}, & \text{for } \mathbf{Z}_{PO}^{\prime\prime} \text{ of } 0. \end{cases}$$

(15)

To match for each solution of  $X_S$ ,  $\theta_{eq}$  should be derived as four different solutions according to the condition of  $Z''_{PO}$ , and the sign of *b* as well. On the other hand, the effective electrical length of the overall peaking amplifier should be the same as an integer multiple of the half-wave transmission line and quarter-wave transmission line for  $Z''_{PO}$  of infinity and zero, respectively. Then, the phase difference of the output currents between the two current sources ( $I_C$  and  $I_P$ ) can be calculated as

$$\tan(\theta_C - \theta_P) = -\frac{a}{\beta b}.$$

(16)

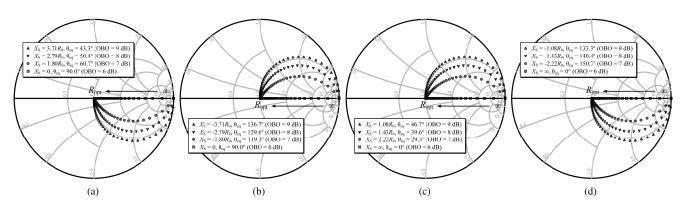

For a fully matched DPA with the proposed LMC, as the input power increases, the load impedance of the carrier amplifier ( $Z_C$ ) is modulated from  $\beta R_{opt}$  to  $R_{opt}$  along the real axis on the Smith chart, while the load impedance of the peaking amplifier ( $Z_P$ ) is modulated from infinity to  $R_{opt}$  through the inductive or capacitive region on the Smith chart. Fig. 5 shows the calculated  $Z_P$ s in the power transition region for various OBO levels according to the four solutions of  $X_S$ . Since a trajectory on a plane with positive imaginary values for the load impedance modulation of the peaking amplifier avoids efficiency degradation at the power

FIGURE 5. The calculated  $Z_P$  according to the input power: (a)  $Z''_{PO} = \infty$  and b > 0, (b)  $Z''_{PO} = \infty$  and b < 0, (c)  $Z''_{PO} = 0$  and b > 0, (d)  $Z''_{PO} = 0$  and b < 0.

FIGURE 6. Modified structure of the LMC with position shifting of the shunt element.

transition region [11], the shunt element having a negative reactance, which comes from a capacitor, is preferable for an open-circuited condition of  $Z_{PO}^{"}$  (see Fig. 5(b)). Conversely, the shunt element should have a positive reactance, which comes from an inductor, for a short-circuited condition of  $Z_{PO}^{"}$  (see Fig. 5(c)).

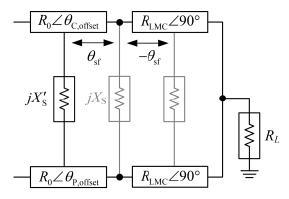

## **B. SHIFTING POSITION OF THE SHUNT ELEMENT**

To make the design more flexible, the position of the shunt element at the LMC can be shifted. As shown in Fig. 6, the position of the shunt element between the offset lines and quarter-wave transmission lines in the LMC can be shifted with a shifting angle of  $\theta_{sf}$ . The positive sign of  $\theta_{sf}$  indicates a shift toward the current source, while the negative sign indicates a shift toward the load. Since the virtual open circuit condition holds for any shifting angle of  $\theta_{sf}$ , the performances can be maintained at the peak power level. However, at the low power level, to keep the electrical characteristics of the circuit the same, a modified reactance value of the shunt element  $(X'_S)$  for each shifting angle should be found as a function of the original value, as follows:

$$X'_{S} = \cos^{2}(\theta_{sf})X_{S} + \frac{1}{2}\sin(2\theta_{sf})R_{sf}.$$

(17)

where, for a positive value of  $\theta_{sf}$ , the value of  $R_{sf}$  is the same as  $R_0$ , while for a negative value of  $\theta_{sf}$ , it is the same

as  $R_{LMC}$ . From (17), it is found that varying the value of the shunt element can be equivalently achieved by simply varying the position of the shunt element. This characteristic of the proposed LMC provides designers with the flexibility to tune the effective value of the shunt element even without changing the value of  $X_S$ .

#### **III. IMPLEMENTATION AND EXPERIMENT RESULTS**

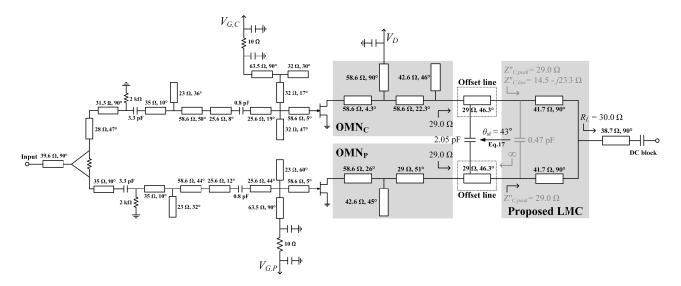

For verification, a symmetric DPA using the proposed LMC was designed to have an OBO level of 8.5 dB with  $\beta$  of 3.54. Fig. 7 shows a circuit schematic of the DPA including the proposed LMC. The optimum load impedances for the carrier and peaking amplifiers at the internal plane and at the peak power level are found from the load–pull simulation as 29  $\Omega$  and 26  $\Omega$ , respectively.

Considering the width of the microstrip transmission line that can be implemented on the PCB, the input impedance,  $R_0$ , of the proposed LMC was selected as 29  $\Omega$  at the peak power level, while the load impedance,  $R_L$ , was selected as 30  $\Omega$ . According to (2), the characteristic impedance of the transmission lines of the LMC becomes 41.7  $\Omega$ . An opencircuited condition for  $Z''_{PO}$  was selected for this design to have a sufficient length of an offset line for the layout. Then, the shunt capacitor of 0.47 pF with a reactance of  $-j94.3 \Omega$ at the center frequency of 3.75 GHz should be used to have a transition through the inductive region with an OBO level of 8.5 dB.

To match the input impedances of the LMC to the optimum load impedances at the peak power level, matching networks of OMN<sub>C</sub> and OMN<sub>P</sub> were designed for the carrier and peaking amplifiers. The additional offset lines with a characteristic impedance of 29  $\Omega$  are deployed after the matching circuits of the carrier and peaking amplifiers for the desired load modulation. The optimum electrical length of the offset line for the peaking amplifier makes the peaking amplifier open-circuited at the LMC, while that of the carrier amplifier increases the load impedance to 102.7  $\Omega$  at the low power level. The optimum electrical length of the overall load network ( $\theta_{eq}$ ) was designed to be 131.4° by tuning the offset line. The second harmonic termination at the load of the carrier

FIGURE 7. Circuit schematic of the DPA including the proposed LMC.

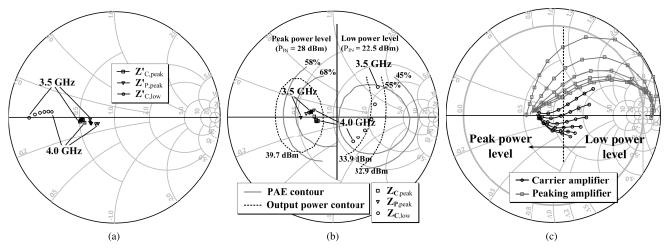

FIGURE 8. Simulated impedances of the carrier and peaking amplifiers for the frequency band of 3.5-4.0 GHz (Smith chart is normalized by 50 Ω): (a) load impedances at the input of the combiner, (b) load impedances at the current source plane, and (c) impedance modulation trajectories according to the input power.

amplifier is achieved using a quarter-wave transmission line at the load of the carrier amplifier, which is used to terminate the second harmonics, and to supply the DC voltage of 28 V. An open stub with an electrical length of 45° is adopted to terminate the second harmonics at the load of the peaking amplifier. According to (13), a shunt capacitor of 2.0 pF was used in the actual circuit by shifting the position with a shifting angle of 43° toward the current source. Fig. 8 shows the simulated load impedances of the carrier and peaking amplifiers for the frequency band of 3.5-4.0 GHz (13%). The load impedances at the input of the combiner are shown in Fig. 8(a), while the load impedances at the current source plane are shown in Fig. 8(b). The impedance modulation trajectories are shown in Fig. 8(c) for the carrier and peaking amplifiers. The load impedances were optimized to have sufficient output power and good efficiency over the band.

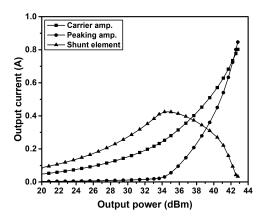

The current through the shunt element gradually decreases and approaches to zero as the peaking amplifier is turned on. When the output current of the peaking amplifier catches that of the carrier amplifier up, it approaches to zero as shown in Fig. 9. Fig. 9 shows the simulated current through the shunt element with the fundamental current levels of the carrier and peaking amplifiers.

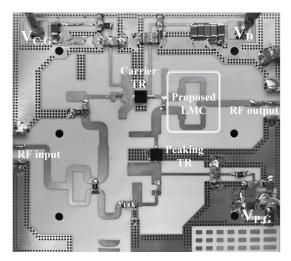

Fig. 10 shows a photograph of the fabricated DPA which has a size of  $60 \times 66.5 \text{ mm}^2$ . A PCB with a dielectric constant of 3.66 and a thickness of 0.508 mm was used to implement the circuit. The carrier and peaking amplifiers have gate bias voltages of -2.85 V for class-AB operation and -7.5 V for class-C operation, respectively. Both amplifiers have a single drain supply voltage of 28 V to have a quiescent current of 19 mA. A photograph of the measurement setup is showed in Fig. 11.

**FIGURE 9.** Simulated current through the shunt element with the fundamental current levels of the carrier and peaking amplifiers at the center frequency of 3.75 GHz.

FIGURE 10. Photograph of the proposed DPA.

FIGURE 11. Photograph of the measurement setup.

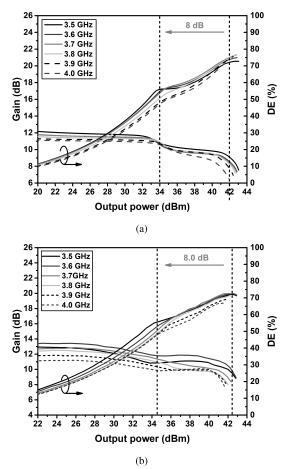

The simulated and measured gain and DE of the proposed DPA, which are very close each other, are shown in Fig. 12. A power gain of 11.1 - 13.0 dB and DE of 67.0 - 71.2% at the saturated output power of 41.7 - 42.7 dBm were

FIGURE 12. Gain and DE of the proposed DPA under CW signal excitation for the frequency band 3.5 - 4.0 GHz: (a) simulation, (b) measurement results.

**FIGURE 13.** Measured saturated output power levels and DEs at the peak power levels and the low power levels with OBO of 8.0 dB.

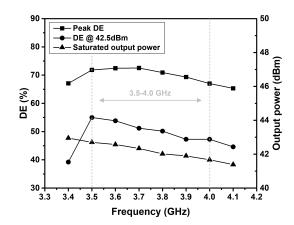

obtained using a CW signal. A measured DE of 47.2 - 55.0% was obtained with a practical OBO level of about 8.0 dB. The measured saturated output power and DEs at the peak and 8 dB back-off power levels for the frequency band of 3.4 - 4.1 GHz are presented in Fig. 13.

TABLE 1. Performance comparison among this work and previous works.

|              | Frequency |                          | Gain              | Psat      | Pava            | $DE_{ava}$                 | ACLR*                  | OBO     | PAPR | Signal BW |        |                          |

|--------------|-----------|--------------------------|-------------------|-----------|-----------------|----------------------------|------------------------|---------|------|-----------|--------|--------------------------|

| Ref.         | (GHz)     | Topology                 | (dB)              | (dBm)     | (dBm)           | (%)                        | (dBc)                  | (dB)    | (dB) | (MHz)     | Signal | Device                   |

| [2]          | 3.4-3.6   | Asymmetric               | 26.2-26.6         | 43.0      | 35.0            | 41.5-43.1                  | -24/-50                | 8.0     | 7.2  | 20        | LTE    | GaN MMIC                 |

| [3]          | 3.3-3.55  | Asymmetric               | 12-15             | 47.5      | 39.0            | 50.6                       | -26/-46.7              | 7.5-8.0 | 7.5  | 20        | LTE    | CGH40025<br>CGH40035     |

| [14]         | 1.4/3.5   | Modified load network    | $12^{\dagger}$    | 42.5/42.1 | 32.5            | 52.1/51.3                  | -25.3/-46.2<br>@3.5GHz | 9       | 9    | 5         | WCDMA  | CGH40006S                |

| [15]         | 3.45-3.75 | Modified load network    | 9.5-11.8          | 41.8-43.5 | 34.6-36.8       | 33.3-54.1                  | -25/-45                | 8.5     | 7.9  | 100       | 5G NR  | CGH40006P<br>CG2H40010F  |

| [16]         | 3.4-3.7   | Modified<br>load network | 11.9-12.7         | 41.7-42.3 | 33.7            | 55.3-60.9                  | -25.5/-42.6            | 8.5     | 7.9  | 100       | 5G NR  | CGH40006S                |

| [17]         | 1.8-3.8   | LMBA                     | 8-10 <sup>†</sup> | 44.0      | 31.0<br>@3.8GHz | $40.0\text{-}50.0^\dagger$ | -30/NA                 | 6       | 9    | 3.84      | WCDMA  | CGH400010F               |

| [18]         | 3.10-4.20 | LMBA                     | 5.5-6.6           | 47.5-48.7 | 37.8            | 39-51                      | -16/-44                | 10      | 10   | 9X100     | 5G NR  | CGHF40010F<br>CGHV27030S |

| This<br>work | 3.5-4.0   | Proposed<br>LMC          | 11.1-13           | 41.7-42.7 | 34.5            | 49.6-54.4                  | -26.5/-49.5            | 8.0     | 7.9  | 100       | 5G NR  | CGH40006S                |

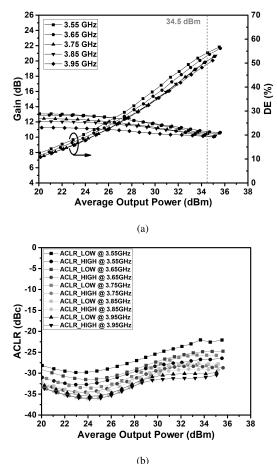

FIGURE 14. Measured performances using the 5G NR signal with a PAPR of 7.86 dB and a signal bandwidth of 100 MHz: (a) gain and DE, (b) ACLR.

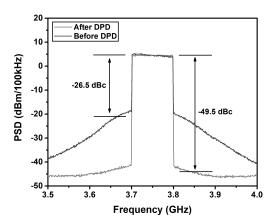

Fig. 14(a) and (b) show the measured performances using the 5G NR modulated signal with a signal bandwidth of 100 MHz and a PAPR of 7.9 dB. A power gain of over 10.5 dB and DE of 49.6 - 54.4% were achieved at an average output power of 34.5 dBm in the 3.5 - 4.0 GHz band. With a DPD method, based on a memory polynomial, the ACLR level was improved by more than 23 dB as shown in \*: Without DPD / With DPD, †: Graphically estimated

FIGURE 15. Measured PSDs using the 5G NR signal before and after DPD at the carrier frequencies of 3.75 GHz.

Fig. 15 which shows the measured power spectral densities (PSDs) using the 5G NR signal at an average output power of 34.1 dBm and the carrier frequency of 3.75 GHz. The performances of the proposed DPA using the 5G NR signal were summarized in comparison to the previously published works in Table 1. The experimental results clearly show superior performances, especially in DE, at an average power level for the wide bandwidth 3.5 - 4.0 GHz of the DPA using the proposed LMC, compared to the previous related works.

#### **IV. CONCLUSION**

A new LMC for a symmetric DPA with the capability of back-off control was proposed. The proposed LMC has a simple structure based on two quarter-wave transmission lines and a shunt element. The proposed LMC allows designers to independently match the load impedance of the carrier amplifier at the low power level, without affecting the impedance at the peak power level. While the conventional LMC gives a fixed OBO level of 6 dB to the symmetric DPA, the proposed LMC has the full capability of extended OBO level even for the symmetric DPA, by selecting the value of the shunt element, or by selecting the placement position (shifting angle) of the shunt element. The proposal has been experimentally verified by implementing a symmetric DPA for the frequency band 3.5 - 4.0 GHz using the proposed LMC to have an OBO level of 8.5 dB in design (about 8.0 dB in measurement). When the 5G NR signal with a signal bandwidth of 100 MHz and PAPR of 7.9 dB is excited, power gain of over 10.5 dB and DE of 49.6 - 54.4% were achieved at an average output power of 34.5 dBm. The proposed LMC can be a very simple and intuitive solution for the DPA to have an extended OBO level, especially for the symmetric DPA.

# REFERENCES

- [1] H. Oh, H. Lee, H. Koo, M. Kim, W. Lee, W. Lim, C. S. Park, K. C. Hwang, K. Y. Lee, and Y. Yang, "Doherty power amplifier based on the fundamental current ratio for asymmetric cells," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 11, pp. 4190–4197, Nov. 2017.

- [2] S. Maroldt and M. Ercoli, "3.5-GHz ultra-compact GaN class-E integrated Doherty MMIC PA for 5G massive-MIMO base station applications," in *Proc. Eur. Microw. Integr. Circuits Conf.*, Oct. 2017, pp. 196–199.

- [3] J. Zhou, W. Chen, L. Chen, and Z. Feng, "3.5-GHz high-efficiency broadband asymmetric Doherty power amplifier for 5G applications," in *Proc. IEEE Int. Conf. Microw. Millim. Wave Technol.*, May 2018, pp. 1–3.

- [4] Y. Yang, J. Cha, B. Shin, and B. Kim, "A fully matched N-way Doherty amplifier with optimized linearity," *IEEE Trans. Microw. Theory Techn.*, vol. 51, no. 3, pp. 986–993, Mar. 2003.

- [5] H. Kang, H. Lee, H. Oh, W. Lee, C. S. Park, K. C. Hwang, K. Y. Lee, and Y. Yang, "Symmetric three-way Doherty power amplifier for high efficiency and linearity," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 64, no. 8, pp. 862–866, Aug. 2017.

- [6] H. Koo, H. Kang, W. Lee, H. Lee, K.-Y. Lee, K. C. Hwang, and Y. Yang, "GaN-HEMT asymmetric three-way Doherty power amplifier using GPD," *IET Microw, Antennas Propag.*, vol. 12, no. 13, pp. 2115–2121, Oct. 2018.

- [7] N. Srirattana, A. Raghavan, D. Heo, P. E. Allen, and J. Laskar, "Analysis and design of a high-efficiency multistage Doherty power amplifier for wireless communications," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 3, pp. 852–860, Mar. 2005.

- [8] M. Seo, M. Song, J. Gu, H. Kim, J. Ham, C. Park, and Y. Yang, "Threestage Doherty amplifier with uneven input splitter," *Microw. Opt. Technol. Lett.*, vol. 55, no. 6, pp. 1405–1409, Jun. 2013.

- [9] A. Barthwal, K. Rawat, and S. K. Koul, "Dual input digitally controlled broadband three-stage Doherty power amplifier with back-off reconfigurability," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 68, no. 4, pp. 1421–1431, Apr. 2021.

- [10] K. Horiguchi, S. Ishizaka, T. Okano, M. Nakayama, H. Ryoji, and Y. Isota, "Efficiency enhancement of 250 W Doherty power amplifier using virtual open stub techniques for UHF-band OFDM applications," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2006, pp. 1356–1359.

- [11] X.-H. Fang, H.-Y. Liu, K.-K.-M. Cheng, and S. Boumaiza, "Two-way Doherty power amplifier efficiency enhancement by incorporating Transistors' nonlinear phase distortion," *IEEE Microw. Wireless Compon. Lett.*, vol. 28, no. 2, pp. 168–170, Feb. 2018.

- [12] W. Choi, H. Kang, H. Oh, K. C. Hwang, K.-Y. Lee, and Y. Yang, "Doherty power amplifier based on asymmetric cells with complex combining load," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 4, pp. 2336–2344, Apr. 2021.

- [13] M. R. Hasin and J. Kitchen, "Exploiting phase for extended efficiency range in symmetrical Doherty power amplifiers," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 8, pp. 3455–3463, Aug. 2019.

- [14] H.-Y. Liu, C. Zhai, and K.-K.-M. Cheng, "Novel dual-band equal-cell Doherty amplifier design with extended power back-off range," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 3, pp. 1012–1021, Mar. 2020.

- [15] Y. C. Choi, W. Choi, H. Oh, Y. Chen, J. Shin, H. Jeon, K. C. Hwang, K.-Y. Lee, and Y. Yang, "Doherty power amplifier with extended highefficiency range based on the utilization of multiple output power backoff parameters," *IEEE Trans. Microw. Theory Techn.*, vol. 70, no. 4, pp. 2258–2270, Apr. 2022.

- [16] Y. Chen, W. Choi, J. Shin, H. Jeon, S. Bae, Y. C. Choi, S. Woo, Y. Y. Woo, H. Oh, K.-Y. Lee, K. C. Hwang, and Y. Yang, "Generalized expression and design method of modified load networks for Doherty power amplifier with extended back-off range," *IEEE Access*, vol. 10, pp. 77487–77497, 2022.

- [17] P. H. Pednekar, E. Berry, and T. W. Barton, "RF-input load modulated balanced amplifier with octave bandwidth," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 12, pp. 5181–5191, Dec. 2017.

- [18] P. Saad and R. Hou, "Symmetrical load modulated balanced power amplifier with asymmetrical output coupling for load modulation continuum," *IEEE Trans. Microw. Theory Techn.*, vol. 70, no. 4, pp. 2315–2327, Apr. 2022.

- [19] H. Kang, H. Lee, W. Lee, H. Oh, W. Lim, H. Koo, C.-S. Park, K. C. Hwang, K.-Y. Lee, and Y. Yang, "Octave bandwidth Doherty power amplifier using multiple resonance circuit for the peaking amplifier," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 2, pp. 583–593, Feb. 2019.

- [20] B. Kim, J. Kim, I. Kim, and J. Cha, "The Doherty power amplifier," *IEEE Microw. Mag.*, vol. 7, no. 5, pp. 42–50, Oct. 2006.

- [21] G. Lv, W. Chen, X. Liu, F. M. Ghannouchi, and Z. Feng, "A fully integrated C-band GaN MMIC Doherty power amplifier with high efficiency and compact size for 5G application," *IEEE Access*, vol. 7, pp. 71665–71674, 2019.

- [22] R. W. Beatty, "Some basic microwave phase shift equations," J. Res. Nat. Bur. Standards, vol. 68, pp. 349–353, Apr. 1964.

**YIFEI CHEN** was born in Hebei, China, in 1994. He received the B.S. degree from the Department of Electronic and Electrical Engineering, Korea University, Seoul, South Korea, in 2018. He is currently pursuing the Ph.D. degree with the Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon, South Korea.

His current research interests include the design of RF/mm-wave power amplifiers, broadband techniques, and mm-wave integration circuits.

**WOOJIN CHOI** was born in Siheung, South Korea, in 1993. He received the B.S. degree from the Department of Electronic and Electrical Engineering, Sungkyunkwan University, Suwon, South Korea, in 2018, where he is currently pursuing the Ph.D. degree with the Department of Electrical and Computer Engineering.

His current research interests include the design of RF power amplifiers for base stations, broadband techniques, and MMICs.

**JAEKYUNG SHIN** was born in Seoul, South Korea, in 1993. He received the B.S. degree from the Department of Electronic and Electrical Engineering, Korea Aerospace University, Goyang, South Korea, in 2018. He is currently pursuing the Ph.D. degree with the Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon, South Korea.

His current research interests include the design of RF/mm-wave power amplifiers, efficiency es, broadband techniques, and microwave power

enhancement techniques, broadband techniques, and microwave power transmission.

**HYEONGJIN JEON** was born in Mokpo, South Korea, in 1994. He received the B.S. degree from the Department of Electronic and Electrical Engineering, Sungkyunkwan University, Suwon, South Korea, in 2020, where he is currently pursuing the Ph.D. degree with the Department of Information and Communication Engineering.

His research interests include the design of RF/mm-wave power amplifiers, RF/analog integrated circuit, efficiency enhancement techniques,

SOONCHEOL BAE was born in Daegu,

South Korea, in 1995. He received the B.S. degree from the Department of Electronic and Electrical Engineering, Sungkyunkwan University, Suwon, South Korea, in 2019, where he is currently pur-

suing the M.S. degree with the Department of

His current research interests include the design

of RF/mm-wave power amplifiers, RF and analog

integrated circuits, and wireless power transfer.

Electrical and Computer Engineering.

linearization techniques, broadband techniques, and wireless power transfer systems.

**KANG-YOON LEE** (Senior Member, IEEE) received the B.S., M.S., and Ph.D. degrees from the School of Electrical Engineering, Seoul National University, Seoul, South Korea, in 1996, 1998, and 2003, respectively. From 2003 to 2005, he was with GCT Semiconductor Inc., San Jose, CA, USA, where he was a Manager of the Analog Division and worked on the design of CMOS frequency synthesizer for CDMA/PCS/PDC and single-chip CMOS RF chip sets for W-CDMA,

WLAN, and PHS. From 2005 to 2011, he was an Associate Professor at the Department of Electronics Engineering, Konkuk University. Since 2012, he has been with the Department of Electrical and Computer Engineering, Sungkyunkwan University, South Korea, where he is currently an Associate Professor. His research interests include implementation of power integrated circuits, CMOS RF transceiver, analog integrated circuits, and analog/digital mixed-mode VLSI system design.

**KEUM CHEOL HWANG** (Senior Member, IEEE) received the B.S. degree in electronics engineering from Pusan National University, Busan, South Korea, in 2001, and M.S. and Ph.D. degrees in electrical and electronic engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 2003 and 2006, respectively. From 2006 to 2008, he was a Senior Research Engineer at Samsung Thales, Yongin, South Korea, where he was involved with

the development of various antennas, including multiband fractal antennas for communication systems and Cassegrain reflector antenna and slotted waveguide arrays for tracking radars. He was an Associate Professor at the Division of Electronics and Electrical Engineering, Dongguk University, Seoul, South Korea, from 2008 to 2014. In 2015, he joined the Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon, Korea, where he is currently an Associate Professor. His research interests include advanced electromagnetic scattering and radiation theory and applications, design of multi-band/broadband antennas and radar antennas, and optimization algorithms for electromagnetic applications. He is a Life Member of KIEES and a member of IEICE.

**YOUNG CHAN CHOI** was born in Seoul, South Korea, in 1996. He received the B.S. degree from the Department of Electronic and Electrical Engineering, Sungkyunkwan University, Suwon, South Korea, in 2020, where he is currently pursuing the Ph.D. degree with the Department of Information and Communication Engineering. His research interests include the design of RF/mmwave power amplifiers, efficiency enhancement techniques, linearization techniques, broadband

techniques, and mm-wave integrated circuits and systems.

**CHEON-SEOK PARK** was born in Seoul, South Korea, in 1960. He received the B.S. degree in electrical engineering from Seoul National University, Seoul, in 1988, and the M.S. and Ph.D. degrees in electrical and electronic engineering from the Korea Advanced Institute of Science and Technology, Daejeon, South Korea, in 1990 and 1995, respectively. He is currently a Professor with the School of Information and Communication Engineering, Sungkyunkwan University, Suwon,

South Korea. His research interests include design of radio-frequency power amplifiers, linearization techniques, and efficiency enhancement techniques.

**YOUNGOO YANG** (Senior Member, IEEE) was born in Hamyang, South Korea, in 1969. He received the Ph.D. degree in electrical and electronic engineering from the Pohang University of Science and Technology, Pohang, South Korea, in 2002. From 2002 to 2005, he was at Skyworks Solutions, Inc., Newbury Park, CA, USA, where he designed power amplifiers for various cellular handsets. Since 2005, he has been with the School of Information and Communication Engi-

neering, Sungkyunkwan University, Suwon, South Korea. His research interest includes RF power amplifiers.

• • •