# Coordinated Online Junction Temperature Estimation of MOSFETs and Antiparallel Diodes in Three-Phase SiC Inverters

Fausto Stella<sup>®</sup>, Member, IEEE, Gianmario Pellegrino<sup>®</sup>, Fellow, IEEE, and Eric Armando<sup>®</sup>, Senior Member, IEEE

Abstract—SiC power MOSFETs guarantee high power density and high efficiency in new-generation power converters. The precise measurement of the device's junction temperature is important in this article for guaranteeing the reliability of the converter and the full exploitation of power semiconductors. While the use of temperature-sensitive electrical parameters (TSEPs) has proven effective and feasible, their application in real-world power converters remains limited. Besides SiC MOSFETs, the temperature of the antiparallel diode is often overlooked and considered noncritical. However, monitoring the temperature of all power electronic devices, diodes included, offers augmented reliability, adaptive adjustment of the converter's peak current at no risk of failure and advanced diagnostics. This article shows that the on-board measurement of the conduction voltage of the SiC MOSFETs and antiparallel diodes can be used for the direct estimate of the respective junction temperatures in a three-phase voltage source inverter. The diode temperatures come with no hardware complication, with respect to what is already in place for SiC MOSFETs characterization and estimate. The proposed methodology is validated on a proof-of-concept two-level three-phase inverter designed for the formula SAE student electric competitions, showing the temperature estimate of the six MOSFETs and diodes at overload current operation.

Index Terms—Conduction voltage, junction temperature estimation, SiC diode, SiC MOSFET, temperature-sensitive electrical parameter (TSEP), voltage source inverters.

#### I. Introduction

RANSPORTATION electrification pushes power electronic systems to improve their power density, partial-load efficiency, cost, and expected failure rate. SiC power devices, combined with innovative packaging and assembly solutions offer such performance advantages [1], [2], [3]. To obtain high levels of reliability avoiding oversizing the costly SiC chips, power converters require advanced thermal management and accurate temperature models [4], [5], [6]. Exceeding the maximum permissible temperature of a power semiconductor even for a short period at best reduces its life expectancy, and at worst brings to its immediate failure. Chip oversize is not acceptable in the cost-critical business of

Manuscript received 6 June 2023; revised 7 September 2023 and 14 October 2023; accepted 18 October 2023. Date of publication 23 October 2023; date of current version 1 December 2023. Recommended for publication by Associate Editor Paolo Magnone. (Corresponding author: Fausto Stella.)

The authors are with the DENERG Department of Energy "Galileo Ferraris," Politecnico di Torino, 10129 Turin, Italy (e-mail: fausto.stella@polito.it).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JESTPE.2023.3326964.

Digital Object Identifier 10.1109/JESTPE.2023.3326964

automotive and neither it is in other industries as aerospace, medical and military, for reasons of power density and reliability beyond cost. Over the years, several techniques have been developed to estimate the junction temperature of power semiconductors, but none of them have reached real industrial maturity. Moreover, the temperature of the antiparallel diodes is not thoroughly investigated in the literature, and it is another useful indicator for the converter's health status. Antiparallel diodes are widely used by power module manufacturers to overcome the downsides of the MOSFET body diode, such as high reverse recovery current and high threshold voltage. In addition, using the body diode under specific conditions can result in premature aging of the device [25], [26].

Multiple techniques have been developed to measure or to estimate the junction temperature of power semiconductors. The direct measurement of junction temperature is possible with optical methods [7], [8], [9], but these are hardly implementable on the board of converters for reasons of cost and reduction of reliability. A thermistor placed in direct contact with the semiconductor die provides a delayed and attenuated image of the junction temperature [10], besides once again deteriorating the converter's reliability (i.e., guaranteeing galvanic insulation with the chip is not trivial). Temperature sensing diodes can be directly integrated into the chip surface to monitor the temperature of the MOSFET or the IGBT [11]; however, semiconductor manufacturers offer a limited number of devices with this capability [12], [13]. This still overlooks the antiparallel diode temperature. State-of-the-art power converters use a temperature sensor placed in the power module or on the heatsink combined with a lumped-parameter thermal network (LPTN) model with calculated power losses [14], [15]. LPTN models have low implementation costs and can be calibrated using datasheet values, finite-element simulation, or measured data. However, the model parameters are usually known only in first approximation and may vary over time (e.g., thermal paste degradation) thus resulting in a rough estimate of the junction temperature.

Indirect techniques relying on temperature-sensitive electrical parameters (TSEPs) use electrical indicators, such as voltages and currents across the semiconductor to estimate temperature. TSEP techniques were mostly developed for IGBT and MOSFETs [16], [17], again overlooking the antiparallel diode

The main TSEPs used for the diode are as follows:

- 1) reverse recovery charge;

- 2) turn-on delay;

- 3) forward voltage at low current;

- 4) forward voltage at high current.

The reverse recovery charge method requires measuring the diode turn-off reverse recovery current [19] or using the commutation voltage as an indirect indicator of the reverse recovery current [21]. However, measuring the device current or voltage at high bandwidth with high precision is hardly applicable to real-world converters. This methodology can be implemented in a laboratory environment, where specialized equipments, such as oscilloscopes and multimeters, are available. Furthermore, the reverse recovery current is influenced not only by the junction temperature but also by the commutation speed, voltage, and current. The turn-on delay of the diode has a correlation with the junction temperature [22], but also in this case the device voltage must be measured on a very short time scale. Forward voltage methods measure the voltage of the diode during conduction, which is a way for less critical to measure. The low-current methods use a calibrated current of a few mA [18]; however, they are hardly viable during operations of a switching converter (i.e., the current in the diode is dependent on the operating point of the converter). Finally, the high-current forward voltage methods [20] consider the conduction voltage of the diode at operating current conditions. This measurement is not time critical and can be performed in converters operating in pulsewidth modulation (PWM) during the conduction time of the diode. Moreover, the same voltage pick-up used for the diode can measure the correspondent MOSFET conduction voltage.

Previous work focused on temperature estimation of the SiC MOSFETs of a two-level, three-phase voltage source inverter [23] on board a switching converter. This work complements previous findings focusing on the junction temperature of the SiC Schottky barrier diodes (SBDs) antiparallel connected with the MOSFETs to enhance their switching performance. The proposed device identification and temperature estimation technique exploits the conduction voltage of the diode at high current as said, and offers a handy solution for real-world PWM commanded converters.

TSEPs calibration is often conducted off-line at the device level using dedicated laboratory equipment such as curve tracers, and calibration data are later used for temperature estimation on board of the power converter, where additional parasitic effects are hard to account for. In this article, the SiC MOSFETs and diodes temperature laws are calibrated directly on the target converter without additional dedicated equipment, using the current and voltage measurement systems already on board of the converter. This means that eventual measurement errors do not affect the temperature estimation, provided that they are consistent over time. This article demonstrates with experimental evidence that the diode temperature estimate does not require additional hardware components or significant computational effort with respect to what is necessary for temperature estimation of the SiC MOSFETs.

This article is organized as follows. Section II reviews previous findings on SiC MOSFET temperature estimation; Section III introduces the new coordinated calibration test; Section IV reports the obtained results, and Section provides V the conclusion.

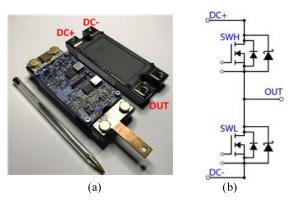

Fig. 1. Overview of the three-phase SiC inverter.

Fig. 2. (a) ROHM BSM180D12P3C007 half-bridge power module with custom driver board embedding the conduction voltage measurement system. (b) Power module schematic.

# TABLE I INVERTER POWER RATINGS

| Nominal DC-link Voltage         | 700 V                      |

|---------------------------------|----------------------------|

| Peak Output Phase Current       | 240 A                      |

| Nominal Switching Frequency     | 20 kHz                     |

| SiC Power Modules (Half Bridge) | 3x ROHM<br>BSM180D12P3C007 |

| DC-link Film Capacitors         | 5x 20 μF                   |

| DC-link Ceramic Capacitors      | 3x220 nF                   |

#### II. PREVIOUS WORK AND PROPOSED IMPROVEMENTS

# A. Three-Phase Inverter and SiC Power Modules

The three-phase SiC inverter for automotive applications capable of estimating the junction temperature of the six power MOSFETs during operations was previously presented in [23]. The converter, shown in Fig. 1 whose power ratings are reported in Table I, was designed to be mounted on a racing car for student competitions. The converter is based on three half-bridge SiC power modules by ROHM semiconductors BSM180D12P3C007. One module with its custom gate driver board is shown in Fig. 2(a), with the power module schematic reported in Fig. 2(b). As shown, two SiC SBDs are antiparallel connected to the SiC MOSFETs.

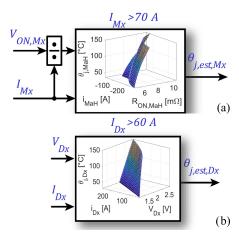

Fig. 3. Temperature estimator working principle. The conduction voltage and the current of the MOSFETs and diodes are measured at each PWM period and entered in a lookup table unique to each device to obtain the estimate of the junction temperature. (a) LUT used for the MOSFETs in the form of  $\theta_{j,Mx}(R_{\text{ON}}, Mx, I_{\text{DS},Mx})$ . (b) LUT used for the antiparallel diode in the form of  $\theta_{j,Dx}(V_{Dx}, I_{Dx})$ .

#### B. Temperature Estimate Based on Conduction Voltage

The proposed temperature estimator exploits the well-known relationship between the junction temperature of the MOSFET and its conduction resistance. Thanks to the online junction temperature estimator the inverter can fully exploit the safe operating area (SOA) of the power MOSFETs with no risk of thermal failure. This article improves the methodology presented for MOSFETs temperature in [23] to include the temperature estimate of the antiparallel diodes with minimum software complication.

The functional diagrams of the junction temperature estimators used for MOSFETs and diodes are shown in Fig. 3. Both estimators require measuring the voltages and the currents across the semiconductors and to enter them in one temperature lookup table so to obtain the junction temperature estimate of the device. These look-up tables which are unique for each device, are preliminarily obtained via a self-calibration test performed directly on the converter as explained later.

# C. Hardware Description

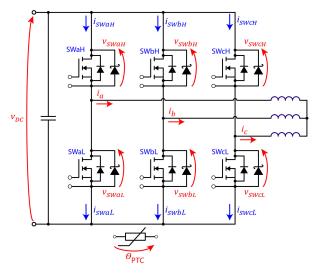

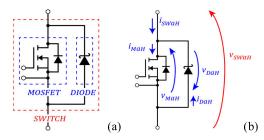

The power converter used for the validation of the proposed methodology embeds all the necessary hardware to be deployed on the racing car. The control board includes a floating point microcontroller unit (MCU) (STM32H7) and a Spartan 6 field-programmable gate array (FPGA) enabling full flexibility on the modulation logic and sampling times. The schematic of the power section of the converter is reported in Fig. 4 with the quantities sampled by the control board shown in red. Compared with a standard three-phase inverter for traction application, the additional measurements are the power semiconductors' conduction voltages  $v_{SWaH}$  and  $v_{SWaL}$ ... The notation used in this article is summarized in Fig. 5(a). The term "switch" is used to refer to the aggregate MOSFET plus diode. The term MOSFET refers to the SiC MOSFET alone, including the body diode, while the term diode refers to the external antiparallel diode. As an example, the notation used for the switch "SWaH" is reported in Fig. 5(b).

Fig. 4. Schematic of the power section of the three-phase inverter. The sampled quantities are indicated in red.

Fig. 5. (a) Notation used in this article: switch, MOSFET, and diode. (b) Voltage and current conventions adopted for the MOSFET and the diode.

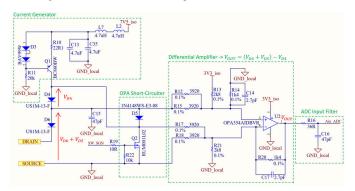

Fig. 6.  $V_{\rm ON}$  measurement system schematic.

The schematic of the  $V_{\rm ON}$  measurement system used to sample the conduction voltage of the power semiconductors during the PWM operations of the converter is shown in Fig. 6. It consists of an operational amplifier in differential configuration that measures the voltage between the drain and the source of the MOSFET (i.e., between cathode and anode of the antiparallel diode) whose output it connected to a local 14bit analog to digital converter (ADC) converter. The diode D6 is used to protect the measurement system when the voltage on the switch rises to the dc-link voltage (i.e., 700 V), per contrary when the switch is in conduction this voltage drops to a few volts and the diode D6 is forward polarized using a current generator shown in the top left of the schematic. The diode D4 connected in series to D6 is employed to counterbalance the conduction voltage of D6, thus enabling to measure only the conduction voltage of the power switch. The "OPA short-

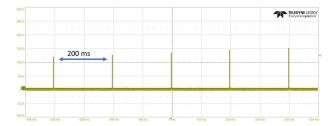

Fig. 7. Current pulses of growing amplitude along the "a+" axis during the calibration test.  $i_a$  (50 A/div) and t = 100 ms/div.

Fig. 8. Current pulses of growing amplitude on each of the six-inverter axes.

circuiter" is optional and can be used to avoid the output saturation of the OPA amplifier when the voltage on the power switch goes high (exiting from a saturation condition requires an additional settling time for the OPA). A detailed description and analysis of this measurement system are not in the scope of this article as they have been previously provided in [23]. Each switch is equipped with its dedicated  $V_{\rm ON}$  measurement system, which communicates ADC measurements to the main MCU through galvanically insulated SPI communication.

#### III. MOSFETS AND DIODES CALIBRATION TEST

The junction temperature characteristics of the MOS-FETs and the antiparallel diodes  $\theta_{j,Mx}(R_{\text{ON},Mx},I_{Mx})$  and  $\theta_{j,Dx}(V_{Dx},I_{Dx})$  must be initially determined via a dedicated calibration test session. The calibration test is performed directly on the converter without dedicated laboratory equipment other than a hotplate and a three-phase 33- $\mu$ H inductor used as a load.

#### A. Calibration Sequence Description

The six MOSFETs and diodes of the converter are individually identified in the current range from 10 to 240 A and the junction temperature range from 35 °C to 145 °C using the following procedure.

- 1) The hotplate is preheated until the positive temperature coefficient (PTC) sensor measuring the heatsink temperature indicates 150 °C and then turned off. The heatsink starts to cool naturally. Due to the slow natural cooling, the junction temperature of all the devices equals the one measured by the PTC thermistor at this stage.

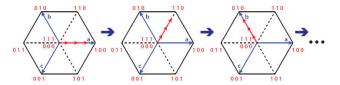

- 2) As the heatsink temperature drops 145 °C the first set of short current pulses (<100  $\mu$ s with 200-ms pause) of growing amplitude from 10 to 240 A is commanded by the inverter in the space direction of phase a (Fig. 7 and first hexagon of Fig. 8). Space direction refers to the space vectors theory [24]. The short duration of the pulses guarantees that the junction temperature is still well represented by the PTC thermistor.

- 3) At the same temperature, another five pulse sequences are repeated for the remaining space directions of the

Fig. 9. Current pulse of 240 A on a+ axis during the commissioning test. Phase current  $i_a$  (50 A/div) and  $t=20 \mu s/\text{div}$ .

inverter, as indicated in Fig. 8 ( $a \rightarrow c$  negative  $\rightarrow b$ ), for a total of 144 pulses. This completes the identification of the six MOSFETs and diodes at around 145 °C. The exact PTC temperature is stored at each pulse during the test.

- 4) After the sequence completion, the heatsink is left cooling to the next temperature level of 140 °C. The current pulse sequences (steps 2 and 3) are repeated and logged at every 5 °C decrease.

- 5) The calibration session terminates at a heatsink temperature of 35 °C in this example.

The assumption of the junction temperature being equal to the heatsink temperature is verified as follows. The single current pulse of duration <100  $\mu$ s causes a junction temperature rise <2 °C for the MOSFET as shown in [23]. The idle time of 200 ms before the next pulse resets the residual temperature perturbation. Therefore, the pulses are considered thermally independent of each other. The total test duration is around 90 min; this time can be consistently reduced by using forced cooling during the test especially when the heatsink is approaching the low temperature range.

#### B. Timing of the Current Pulse and Data Acquisition

This section provides a detailed description of the MOSFET and diode forward voltage sampling strategy during the commissioning stage.

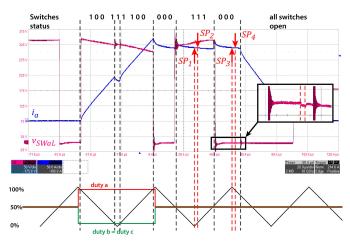

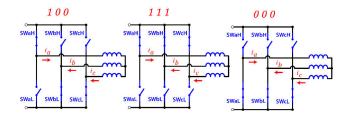

In Fig. 9, the current pulse of the highest magnitude of 240 A is taken as an example, when applied along the phase a positive direction (a+) enables the identification of the MOSFET aH and the diode aL. The 20-kHz PWM carrier and the abc inverter legs duty cycles are reported at the bottom of the figure. The instantaneous states of the inverter legs are indicated on the top of the figure, where "1" indicates that the H switch is closed and "0" that the L switch is closed. Different switch configurations assumed by the invert during the pulse injection along the a+ inverter axis are shown in Fig. 10. Returning to Fig. 9, the inverter state alternates between the active state "100" and the two zero voltage states "000" and "111."

The first PWM period (100–111–100) is used to ramp the current  $i_a$  to the target value of 240 Apk by imposing

Fig. 10. Switches configuration during pulses along the a+ axis.

TABLE II

Data Obtained From the a+ Axis Pulse Sequence

| SP1 | $MaH(i_a)$ | 1 |              | SP3 |              |  | $DaL(i_a)$ |

|-----|------------|---|--------------|-----|--------------|--|------------|

|     | -          |   | $DbH(i_a/2)$ |     | $MbL(i_a/2)$ |  |            |

|     |            |   | $DcH(i_a/2)$ |     | $McL(i_a/2)$ |  |            |

appropriate duty cycles. In the second PWM period (000-111-000) the inverter forces zero voltage to keep the current  $i_a$  constant and the forward voltage and current of the devices along with the heatsink temperature are sampled. The sampling instants are labeled SP1-SP4 in Fig. 9.

SP1: The inverter state is 111, and the current  $i_a$  flows in the MOSFET MaH while equal currents  $-i_a/2$  flow in SWbH and SWcH (SW = MOSFET//diode) as explained in Fig. 10. The conduction voltage and current  $i_a$  of MaH are thus sampled at SP1 together with the heatsink temperature. The negative current values of switches SWbH and SWcH are not sampled at SP1 as the MOSFET and diodes are sharing the current.

SP2: After SP1 is completed, the MOSFETs bH and cH are turned off to access the diode forward voltage alone. Now, the diodes DbH and DcH conduct  $i_a/2$  each and their voltage, current, and temperature values are sampled at SP2. A blank time of 2  $\mu$ s is left between the turn-off command of MbH, McH, and SP2. In this way, any voltage transient due to the commutation of the two MOSFETs is over, and the measurement system is able to measure the actual conduction voltage of the diodes. It must be noted that only the MOSFETs bH and cH are turned off thus avoiding forcing any voltage to the load that would result in high currents slew rates (i.e., if also the MOSFET aH is commanded open the converter would work as a diode bridge rectifier causing a large current slew rate on the load). After SP2 is completed, the bH and cH MOSFETs are commanded on again.

SP3: The next sampling instance is dual to SP1, with the inverter in state 000 (low-side MOSFETs closed). Conduction voltages and currents of MbL and McL together with the heatsink temperature are stored at SP3 for a current of  $i_a/2$ .

SP4: immediately after SP3, MaL is turned off and the DaL quantities are logged for a current  $i_a$  at SP4, with a blank time of 2  $\mu$ s after the turn-off of MaL.

To summarize, the current pulse in the a+ axis populates the map of MaH (SP1) and DaL (SP4) at the corresponding current value (e.g.,  $i_a=240$  A). As by-products, the characteristics of the other MOSFETs MbL, McL (SP3) and diodes DbH and DcH (SP2) are mapped at  $i_a/2$ . The data extracted from the a+ axis pulse is summarized in Table II. The "half-current"

TABLE III Data Obtained From All Current Pulse Sequences

|            | SP1        | SP2        | SP3        | SP4        |

|------------|------------|------------|------------|------------|

| <i>a</i> + | $MaH(i_a)$ |            |            | $DaL(i_a)$ |

| <i>c</i> – |            | $DcL(i_c)$ | $McL(i_c)$ |            |

| <b>b</b> + | $MbH(i_b)$ |            |            | $DbL(i_b)$ |

| <i>a</i> – |            | $DaH(i_a)$ | $MaL(i_a)$ |            |

| <i>c</i> + | $McH(i_c)$ |            |            | $DcL(i_c)$ |

| <b>b</b> – |            | $DbH(i_b)$ | $MbL(i_b)$ |            |

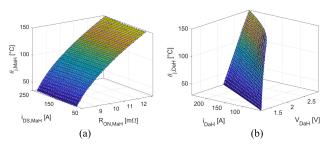

Fig. 11. Lookup table obtained from the current pulse test. (a) MOSFET MaH for  $i_{\rm DS,MaH} > 60$  A and (b) diode DaH for  $i_{\rm DaH} > 60$  A.

measurements at SP2 and SP3 reported in blue are redundant, as the corresponding devices will be characterized at full current during the dedicated pulse sequences (MbL and DbH at phase b- pulse sequence, McL and DcH with phase c-). The current pulse injection is repeated for all the inverter axes as indicated in Table III to map the characteristics of all the MOSFETs and diodes of the bridge. By looking at the current pulse of Fig. 9, it is possible to note the presence of the inactive state "111" between the two active states "100." While not strictly necessary, this state is due to the employed modulation technique, which is consistently utilized even during the power converter's standard operation, whereby the reference duty cycles are updated exclusively at the triangular carrier's positive vertex.

# IV. DIODE TEMPERATURE ESTIMATION

#### A. Use of the Temperature Maps

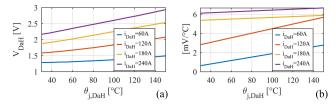

The temperature maps of MaH and DaH are reported in Fig. 11 as examples. Fig. 11(a) shows the data collected for the MOSFET MaH represented as  $\theta_{i,MaH}(R_{ON,MaH}, I_{DS,MaH})$ , and Fig. 11(b) the map of the diode DaH in the form  $\theta_{i,\text{DaH}}(V_{\text{DaH}}, I_{\text{DaH}})$ . Using  $R_{\text{ON}}$  in place of  $V_{\text{ON}}$  for the MOSFET results in an easier to interpolate surface (i.e., a second degree polynomial function). For the diodes, the values obtained for currents below 60 A are discarded while for the MOSFETs are discarded the value below 70 A. Fig. 12(a) shows the measured  $V_{\text{DaH}}(\theta_{i,\text{DaH}})$  for different values of current. The voltage to temperature sensitivity is shown in Fig. 12(b) as a function of the junction temperature. The voltage sensitivity is higher at high currents and temperatures, which is when it is most needed. It is also possible to note how the sensitivity tends to be lower at low current values, in particular, below 60 A, the TSEP sensitivity (mV/°C) is too low to be used by the temperature estimator.

Fig. 12. (a) Diode conduction voltage as a function of  $\theta_j$ . (b) Diode conduction voltage sensitivity as a function of  $\theta_j$ .

Fig. 13. Forward threshold voltage comparison at 1 A between the body diode and the antiparallel diode at various junction temperatures.

The temperature LUTs are used to estimate the junction temperature of the MOSFETs and diodes using the functional block diagram shown in Fig. 3(a) and (b), respectively. In particular, for measuring the conduction voltage of the diode, the corresponding MOSFET must be commanded off for a short amount of time during PWM operations. Only the MOSFETs of the switches conducting a negative current greater than 60 A are commanded open for 2  $\mu$ s so that all the switch current is conducted by the antiparallel diode. This enables to estimate the junction temperature of the diode without significantly affecting the voltage applied to the load. As the voltage drop of the diode is slightly higher (0.5–2 V higher) than the voltage drops of the MOSFET channel, this causes a negligible voltage error on the load given that the inverter is operating with a dc link voltage of 700 V. As this causes a minimal amount of additional conduction losses, diode temperature sampling rate can be reduced with respect to the PWM frequency. In the presented experimental results, the temperature of the diodes is evaluated once every five PWM periods (i.e., 250  $\mu$ s), which can be further relented considering the tenths of milliseconds horizon of the thermal time constants in play. It was observed that monitoring the temperature of the diode once every 10-50 PWM periods would be sufficient.

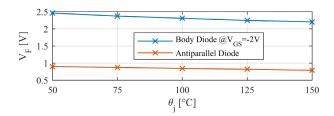

# B. Limitations Related to the Body Diode

A critical assumption behind the proposed technique is that with the negative current in the switch and the MOSFET turned off the current flows entirely in the SiC SBD and not in the body diode. This assumption is met as long as the forward voltage of the external diode is lower than the threshold voltage of the body diode. As the datasheet does not provide the threshold voltage of the body diode, a dedicated identification test was performed.

One power module was disassembled to have access to the MOSFET and the antiparallel diode separately. The conduction voltage of the body diode was measured with the MOSFET off ( $V_{\rm GS}=-2$  V, same as in operation). Comparative results are reported in Fig. 13, for a forward current of 1 A, where

Fig. 14. Conduction voltage characteristic of the diode DaH at different junction temperatures. The operating area of the diode temperature estimator is highlighted in green.

the threshold voltages of both diodes show to depend on the respective junction temperatures.

The body diode threshold voltage spans in the range of 2.2–2.5 V, with a minimum of 2.2 V at the highest MOSFET junction temperature  $\theta_i = 150$  °C. The antiparallel diode threshold voltage spans between 0.85 and 0.90 V. If the conduction voltage of the antiparallel diode exceeds the threshold voltage of the body diode, part of the current is conducted by the latter one and the proposed temperature estimator can no longer be used. During operation, the diode temperature estimate is thus valid when the measured forward voltage does not exceed the body diode threshold. For simplicity, the worst case value of 2.2 V is selected as a fixed threshold, independently of the temperature of the MOSFETs. This is a cautionary value as in reality when the diode is in conduction the temperature of the MOSFET is well below 150 °C; however, this cautionary value enables us to account also for any parameter dispersion between components.

In conclusion, the temperature estimate of the antiparallel diode is valid as long as its conduction voltage is below 2.2 V, as shown in Fig. 14.

A second limitation is caused by the low TSEP sensitivity at low current as previously shown in Fig. 12(b). Therefore, the temperature of the diode is not estimated for currents below 60 A. The operating range of the diode temperature estimator is summarized by the green area of Fig. 14.

#### V. RESULTS AND DISCUSSION

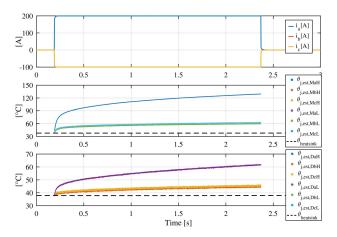

The following results show the real-time estimate of the  $\theta_j$  of the six MOSFETs and diodes during the converter operation. The inverter operates at a PWM switching frequency of 20 kHz, and it is connected to a three-phase 33- $\mu$ H load inductor while imposing different levels of current. The temperatures of the six inverter MOSFETs and the antiparallel diodes are real-time estimated directly by MCU using the functional blocks shown in Fig. 3, and the LUTs are obtained during the calibration test. Therefore, the junction temperatures of the power switches are known to control firmware that can eventually decide to limit the output currents if an over temperature is detected.

### A. Online Temperature Estimation

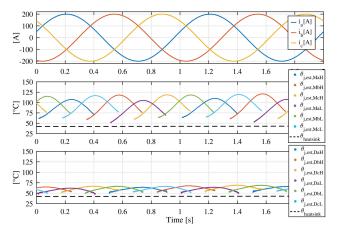

In Fig. 15, a sinusoidal current of magnitude 200 Apk at 1 Hz is commanded by the converter to the inductive load. The top plot shows the phase currents, and the middle one shows  $\theta_{j,\text{est}}$  of the six inverter MOSFETs, while the bottom one shows

Fig. 15. Top: Sinusoidal phase currents, 200 Apk, 1 Hz. Middle:  $\theta_{j,\text{est}}$  of the MOSFETs and measured heatsink temperature. Bottom:  $\theta_{j,\text{est}}$  of the diodes and measured heatsink temperature.

$\theta_{i,\text{est}}$  of the correspondent antiparallel diodes. The measured heatsink temperature is represented by a black dashed line, and it is circa constant during the test. As already explained, the temperatures of the MOSFETs can be estimated only for  $i_{DS} > 70$  A. At low currents the TSEP sensitivity of the MOSFET is too low (this case is not thermally critical) while at negative currents it is not possible to compute the current sharing between the MOSFET (in ON state) and the antiparallel diode. The temperatures of the diodes can be estimated only for  $i_D > 60$  A and  $v_D < 2.2$  V as previously explained. The MOSFETs temperatures are characterized by large thermal swings between 50 °C and 120 °C and follow the phase currents with a certain delay. The peak temperature is around 120 °C and is slightly different for each device. For example, the MOSFETs of phase a, namely, MaH and MaL exhibit a lower junction temperature compared to the ones of the other phases. This is due to parametric dispersion, and the module of phase a shows to have a lower conduction resistance, as further verified offline using dedicated laboratory instrumentation. Both the large temperature swing and the parameter dispersion clearly show how critical temperature monitoring can be for the advanced thermal management of the power converter.

The maximum junction temperature of the antiparallel diodes is significantly lower than that of the MOSFETs, reaching peak values of around 70 °C. In fact, the antiparallel diodes are in conduction for a limited amount of time.

- 1) During the switching dead time (i.e., 400 ns).

- When the MOSFETs are conducting high negative current and their conduction voltages overcome the threshold voltages of the diodes.

- 3) When the MOSFETs are turned off for measuring the forward conduction voltage of the diodes required by the temperature estimator (i.e.,  $2 \mu s$ ). In this case, the temperature of the diodes is estimated once every five PWM periods

An additional aspect to note is that when the current in the diodes lowers the temperature estimation becomes noisy due to the lower TSEP sensitivity.

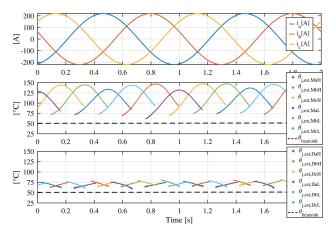

Fig. 16. Top: Sinusoidal phase currents, 220 Apk, 1 Hz. Middle:  $\theta_{j,\text{est}}$  of the MOSFETs and measured heatsink temperature. Bottom:  $\theta_{j,\text{est}}$  of the diodes and measured heatsink temperature.

Fig. 17. Top: Sinusoidal phase currents, 200 Apk, 10 Hz. Middle:  $\theta_{j,\text{est}}$  of the MOSFETs and measured heatsink temperature. Bottom:  $\theta_{j,\text{est}}$  of the diodes and measured heatsink temperature.

In Fig. 16, the test is repeated with a slightly higher peak current of 220 Apk. Please note that the 10% current increase causes a significant temperature rise, as the junction temperature of the MOSFETs swings up to around 150  $^{\circ}$ C. The same is true for the diodes that temperatures above 75  $^{\circ}$ C, although it is not possible to track their temperature at peak current values due to the 2.2-V body-diode limit.

Finally, in Fig. 17, the same 200-Apk currents of Fig. 15 are imposed at 10 Hz thus resulting in lower temperature swings of both the MOSFETs and the diodes due to the thermal capacitance of the devices that helps to distribute the losses among the semiconductors. In this case, the maximum junction temperature is well below 100 °C.

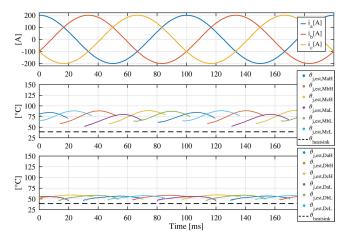

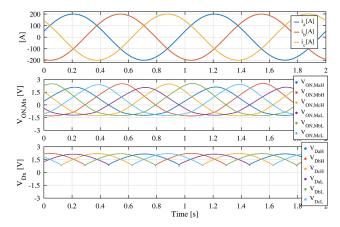

Fig. 18 shows the same test as Fig. 15, but instead of displaying the estimated junction temperatures, it shows the measured voltages across the switches. The central plot shows the measured conduction voltage of the power MOSFETs where the conduction voltage rises to around 1.8 V when the current in the device is positive, while it is only -1.5 V when the current in the switch is negative, this is due to the current sharing between the MOSFET and the antiparallel diode. The bottom plot shows the measured voltage on the antiparallel

Fig. 18. Voltage measurements across power semiconductors during the same test depicted in Fig. 15. Top: Sinusoidal phase currents, 200 Apk, 1 Hz. Middle:  $V_{\rm ON}$  of the MOSFETs. Bottom: Forward conduction voltage of the diodes.

Fig. 19. 200-A step change along the a+ axis. Top: Phase currents. Middle:  $\theta_{j,\text{est}}$  of the MOSFETs and measured heatsink temperature. Bottom:  $\theta_{j,\text{est}}$  of the diodes and measured heatsink temperature.

diode when the switch is conducting a negative current and the corresponding MOSFET is commanded open.

#### B. Temperature Response to a Current Step Change

In Fig. 19, a current step from 0 to 200 A is commanded along the a+ axis of the converter, so that  $i_a=200$  A and  $i_b=i_c=-100$  A. Following the current step, the estimated junction temperature of the MOSFETs and antiparallel diodes start rising from the heatsink temperature. Please note that the starting temperature of all devices coincides with the measured heatsink temperature, which validates the accuracy and consistency of the temperature LUTs in the low-temperature range. The first time constant of the junction temperature response is estimated in the order of 50 ms, and this is in line with the thermal impedance provided in the datasheet.

# C. Aging

The electrical and thermal characteristics of power semiconductors tend to change with the aging of the components due to multiple degradation phenomena such as bonding wire lift-off, die delamination and cracking, oxide degradation, and solder fatigue. Both the MOSFETs and the diodes experience a degradation of their conduction characteristics over a lifetime, reflected in an increase of the ON-state resistance (i.e., conduction voltage) [27], [28].

As the temperature proposed temperature estimator is based on the conduction characteristic of the component obtained during the calibration test performed at the beginning of the life of the converter, the junction temperature accuracy will also deteriorate over the lifetime of the component. Numerous investigations reveal that the conduction resistance of SiC devices remains constant throughout the component's lifetime until the very end, when consistent deterioration of the thermoelectric characteristics occurs [27], [28], [29]. Therefore, the proposed temperature estimator should not be significantly affected until the very end of the life of the component as previously shown in [29]. As a precautionary measure, one approach to maintaining the accuracy of the temperature estimator is to periodically repeat the calibration test after a certain number of working hours. This helps ensuring that the temperature estimator remains highly accurate over time.

It is important to note that while this section serves as a warning about potential issues related to component aging, dedicated studies will be essential to comprehensively investigate this complex phenomenon.

#### D. Strengths and Limitations of the Method

The strengths of the proposed methodology are as follows.

- The TSEP calibration of the SiC MOSFETs and antiparallel diodes can be performed directly on the converter without the need for specialized equipment such as a curve tracer

- 2) The additional circuitry required for the  $v_{\rm ON}$  measurement system is simple and low-cost. In principle, the measurement system can be easily integrated into the gate driver IC chip.

- No complex computation or hard to tune model is involved.

- 4) The nonidealities of the on-board voltage measurement system such as offset and gain errors do not harm the temperature estimator, provided that they are consistent over time.

The limitations of the proposed methodology in its current form are as follows.

- 1) The junction temperature of the MOSFETs cannot be estimated for negative values of  $i_{DS}$ , although this case tends not to be critical temperature wise, as conduction losses are shared with the antiparallel diode. Furthermore, when  $i_{DS} < 0$  the commutation losses in the device are lower if compared to the case  $i_{DS} > 0$ .

- 2) The temperature of the diodes cannot be estimated for currents below 60 A. Also, this case is not critical.

- 3) The temperature of the diodes cannot be estimated when the forward conduction voltage of diodes overcomes 2.2 V. This is a major limitation as it blinds the temperature information in the critical area of high current and high temperature. In Fig. 16, the temperature of the diodes is measured up to 200-A circa and not between

Fig. 20. Thermographic validation previously provided in [30], where the same temperature estimation technique was applied to a SiC MOSFET power module in an H-bridge configuration. On the right side is visible the measured temperature on the semiconductor surface, where the borders of the chip are highlighted by the black dashed line.

200 and 220 A. In this case, additional considerations may be needed to verify that the temperature does not overcome the SOA of the component (i.e., it is possible to use the online temperature estimator conjointly with a thermal model of the component). However, just by looking at Fig. 16, we can realistically assume that in the range 200 to 220 A the temperature of the diode does not overcome 100 °C, also considering that part of the current is conducted by the body diode of the MOSFET.

4) The measurement of the 2.2-V threshold voltage limit requires a dedicated laboratory-type identification test. Future work will deal with the automatic identification of the area of validity of the diode temperature estimate, and its extension in terms of current and temperature range.

#### E. Goodness of the Results

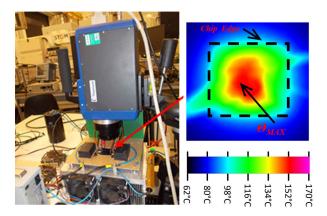

Providing a direct validation of the proposed method, for example via thermography, is not trivial, especially on board of a PWM-operated converter.

Thermography validation necessitates providing visual access to the die by removing the encapsulant gel, which is nontransparent to infrared rays. This removal process can be accomplished either mechanically or by employing specialized solvents such as TP3884. However, the gel removal would lead to a reduction in voltage breakdown capability. Consequently, conducting the validation test under PWM supply at full dc-link voltage becomes impractical in practice. Moreover, due to the compact layout of the converter (designed to be embedded in a racing car), providing visual access to the die is impossible.

Another approach for validation would use less invasive optical fibers that allow only a punctual measurement of temperature to be performed. However, the temperature gradient across the die of a semiconductor during its working operations can reach tens of degrees as shown in [12] and [30].

An indirect form of validation is provided in Fig. 19 where following a step current variation from 0 to 200 A the temperature of the MOSFETs and the diodes starts rising

exactly from the temperature of the heatsink measured with the PTC thermistor.

The same technique was previously validated on a proof-of-concept prototype based on an H-Bridge SiC MOSFET power module where the temperature of one of the switches was estimated using the same temperature estimator shown in this article [30]. The H-bridge validation test rig presented in [30] is shown in Fig. 20. The layout of the H-bridge converter was modified to provide visual access to the die, the encapsulant gel was mechanically removed, the surface of the die was black painted and the converter was operated at reduced voltage. The results from the thermal camera showed that the temperature gradient across the chip surface was tens of degrees; however, the proposed technique was able to estimate the average temperature of the die within an error of 5 °C.

#### VI. CONCLUSION

This article builds on previous work on SiC MOSFETs temperature estimation extending what was previously proposed to the temperature estimate of antiparallel diodes on board of a real-world power converter. The calibration test has been improved to map the antiparallel diodes, and their junction temperature is estimated during PWM under load. As pointed out in Section V-E, the estimated junction temperature is representative of the average temperature of the die surface and does not take into account the presence of hotspots. Although the diodes temperatures are typically overlooked in MOSFET converters for being considered not critical, this might not always be the case, especially in those converters where antiparallel diodes are not designed for continuous operation (e.g., failure condition of an inverter connected to a rotating machine with all MOSFETs commanded open and the inverter operating as a diode bridge rectifier). Despite that, the proposed methodology can provide valuable information enabling to fully exploit the SOA of the components without virtually any risk of thermal failure. The proposed advanced capability of diodes monitoring comes at zero hardware cost and little software complication with respect to the setup used for SiC MOSFET temperature tracking.

# REFERENCES

- [1] A. O. Adan, D. Tanaka, L. Burgyan, and Y. Kakizaki, "The current status and trends of 1,200-V commercial silicon-carbide MOSFETs: Deep physical analysis of power transistors from a Designer's perspective," *IEEE Power Electron. Mag.*, vol. 6, no. 2, pp. 36–47, Jun. 2019, doi: 10.1109/MPEL.2019.2909592.

- [2] A. Ghazanfari, C. Perreault, and K. Zaghib, "EV/HEV industry trends of wide-bandgap power semiconductor devices for power electronics converters," in *Proc. IEEE 28th Int. Symp. Ind. Electron. (ISIE)*, Jun. 2019, pp. 1917–1923, doi: 10.1109/ISIE.2019.8781528.

- [3] R. Rupp, "CoolSiC and major trends in SiC power device development," in *Proc. 47th Eur. Solid-State Device Res. Conf. (ESSDERC)*, Sep. 2017, pp. 118–121, doi: 10.1109/ESSDERC.2017.8066606.

- [4] C. Neeb, L. Boettcher, M. Conrad, and R. W. De Doncker, "Innovative and reliable power modules: A future trend and evolution of technologies," *IEEE Ind. Electron. Mag.*, vol. 8, no. 3, pp. 6–16, Sep. 2014, doi: 10.1109/MIE.2014.2304313.

- [5] H. Wang, M. Liserre, and F. Blaabjerg, "Toward reliable power electronics: Challenges, design tools, and opportunities," *IEEE Ind. Electron. Mag.*, vol. 7, no. 2, pp. 17–26, Jun. 2013, doi: 10.1109/MIE.2013.2252958.

- [6] H. Lee, V. Smet, and R. Tummala, "A review of SiC power module packaging technologies: Challenges, advances, and emerging issues," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 239–255, Mar. 2020, doi: 10.1109/JESTPE.2019.2951801.

- [7] O. Olanrewaju, Z. Yang, N. Evans, A. Fayyaz, T. Lagier, and A. Castellazzi, "Investigation of temperature distribution in SIC power module prototype in transient conditions," in *Proc. 20th Int. Symp. Power Electron.*, Oct. 2019, pp. 1–5.

- [8] C. Fang, T. An, F. Qin, X. Bie, and J. Zhao, "Study on temperature distribution of IGBT module," in *Proc. 18th Int. Conf. Electron. Packag. Technol. (ICEPT)*, Aug. 2017, pp. 1314–1318.

- [9] L. Dupont, Y. Avenas, and P.-O. Jeannin, "Comparison of junction temperature evaluations in a power IGBT module using an IR camera and three thermosensitive electrical parameters," *IEEE Trans. Ind. Appl.*, vol. 49, no. 4, pp. 1599–1608, Jul. 2013, doi: 10.1109/TIA.2013.2255852.

- [10] F. Stella, G. Pellegrino, E. Armando, and D. Dapra, "Online junction temperature estimation of SiC power MOSFETs through on-state voltage mapping," *IEEE Trans. Ind. Appl.*, vol. 54, no. 4, pp. 3453–3462, Jul. 2018, doi: 10.1109/TIA.2018.2812710.

- [11] E. R. Motto and J. F. Donlon, "IGBT module with user accessible on-chip current and temperature sensors," in *Proc. 27th Annu. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Feb. 2012, pp. 176–181, doi: 10.1109/APEC.2012.6165816.

- [12] B.-E.-B. Bidouche, Y. Avenas, M. Essakili, and L. Dupont, "Thermal characterization of an IGBT power module with on-die temperature sensors," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Mar. 2017, pp. 2317–2322, doi: 10.1109/APEC.2017.7931023.

- [13] H. Ichikawam, T. Ichimura, and S. Soyano, "IGBT modules for hybrid vehicle motor driving," *Fuji Electr. Rev.*, vol. 55, no. 2, pp. 46–50, 2009

- [14] P. Liu, X. Zhang, S. Yin, C. Tu, and S. Huang, "Simplified junction temperature estimation using integrated NTC sensor for SiC modules," in *Proc. IEEE Int. Power Electron. Appl. Conf. Expo. (PEAC)*, Nov. 2018, pp. 1–4.

- [15] A. S. Bahman, K. Ma, and F. Blaabjerg, "Thermal impedance model of high power IGBT modules considering heat coupling effects," in *Proc. Int. Power Electron. Appl. Conf. Expo.*, Nov. 2014, pp. 1382–1387.

- [16] S. Kalker et al., "Reviewing thermal-monitoring techniques for smart power modules," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 10, no. 2, pp. 1326–1341, Apr. 2022, doi: 10.1109/JESTPE.2021.3063305.

- [17] N. Baker, M. Liserre, L. Dupont, and Y. Avenas, "Improved reliability of power modules: A review of online junction temperature measurement methods," *IEEE Ind. Electron. Mag.*, vol. 8, no. 3, pp. 17–27, Sep. 2014, doi: 10.1109/MIE.2014.2312427.

- [18] Z. Khatir, L. Dupont, and A. Ibrahim, "Investigations on junction temperature estimation based on junction voltage measurements," *Microelectron. Rel.*, vol. 50, nos. 9–11, pp. 1506–1510, Sep. 2010, doi: 10.1016/j.microrel.2010.07.102.

- [19] H. Luo, Y. Chen, W. Li, and X. He, "Online high-power p-i-n diode junction temperature extraction with reverse recovery fall storage charge," *IEEE Trans. Power Electron.*, vol. 32, no. 4, pp. 2558–2567, Apr. 2017, doi: 10.1109/TPEL.2016.2580618.

- [20] X. Perpiña, J. F. Serviere, J. Saiz, D. Barlini, M. Mermet-Guyennet, and J. Millán, "Temperature measurement on series resistance and devices in power packs based on on-state voltage drop monitoring at high current," *Microelectron. Rel.*, vol. 46, nos. 9–11, pp. 1834–1839, Sep. 2006, doi: 10.1016/j.microrel.2006.07.078.

- [21] X. Zhang, D. Xiang, X. Zhong, and Y. Yuan, "Diode junction temperature measurement from power converter output voltage," in *Proc. IEEE Int. Power Electron. Appl. Conf. Expo. (PEAC)*, Nov. 2018, pp. 1–6, doi: 10.1109/PEAC.2018.8590467.

- [22] X. Wang, S. Feng, J. Li, and B. Shi, "Study on junction temperature measurement of SiC Schottky barrier diode based on turn-on-delay time estimation," in *Proc. 2nd IEEE Int. Conf. Integr. Circuits Microsystems* (ICICM), Nov. 2017, pp. 178–181, doi: 10.1109/ICAM.2017.8242163.

- [23] F. Stella, G. Pellegrino, and E. Armando, "Three-phase SiC inverter with active limitation of all MOSFETs junction temperature," *Microelectron. Rel.*, vol. 110, Jul. 2020, Art. no. 113659, doi: 10.1016/j.microrel.2020.113659.

- [24] P. Vas, Electrical Machines and Drives: A Space-Vector Theory Approach. vol. 1. Oxford, U.K.: Clarendon Press, 1992.

- [25] T. Funaki, "A study on performance degradation of SiC MOSFET for burn-in test of body diode," in *Proc. 4th IEEE Int. Symp. Power Electron. Distrib. Gener. Syst. (PEDG)*, Jul. 2013, pp. 1–5, doi: 10.1109/PEDG.2013.6785593.

- [26] M. Kang et al., "Body diode reliability of commercial SiC power MOSFETs," in Proc. IEEE 7th Workshop Wide Bandgap Power Devices Appl. (WiPDA), Oct. 2019, pp. 416–419.

- [27] S. Dusmez and B. Akin, "An accelerated thermal aging platform to monitor fault precursor on-state resistance," in *Proc. IEEE Int. Electric Mach. Drives Conf. (IEMDC)*, May 2015, pp. 1352–1358.

- [28] H. Luo, F. Iannuzzo, F. Blaabjerg, M. Turnaturi, and E. Mattiuzzo, "Aging precursors and degradation effects of SiC-MOSFET modules under highly accelerated power cycling conditions," in *Proc.* IEEE Energy Convers. Congr. Expo. (ECCE), Cincinnati, OH, USA, Oct. 2017, pp. 2506–2511.

- [29] F. Stella, G. Pellegrino, and E. Armando, "Coordinated on-line junction temperature estimation and prognostic of SiC power modules," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Sep. 2018, pp. 1907–1913, doi: 10.1109/ECCE.2018.8557850.

- [30] F. Stella, O. Olanrewaju, Z. Yang, A. Castellazzi, and G. Pellegrino, "Experimentally validated methodology for real-time temperature cycle tracking in SiC power modules," *Microelectron. Rel.*, vols. 88–90, pp. 615–619, Sep. 2018, doi: 10.1016/j.microrel.2018.07.072.

**Fausto Stella** (Member, IEEE) received the bachelor's and master's degrees in electrical engineering and the Ph.D. degree from the Politecnico di Torino, Turin, Italy, in 2012, 2015, and 2019, respectively.

In 2017, he joined the University of Nottingham, Nottingham, U.K., as a Visiting Ph.D. Student. He is currently an Assistant Professor with the Politecnico di Torino. He is also a Research Fellow with the Politecnico di Torino. His research interests include the design of power electronic converters, focusing on SiC semiconductors and reliability issues, and the control of converters

via embedded systems.

Gianmario Pellegrino (Fellow, IEEE) is currently a Professor of power converters, electrical machines, and drives with the Politecnico di Torino, Turin, Italy. He was a Visiting Fellow with Aalborg University, Aalborg, Denmark; the University of Nottingham, Nottingham, U.K.; and the University of Wisconsin–Madison, Madison, WI, USA. He has authored the open-source platform SyR-e for the design of electrical motors and drives, constantly developed and validated in the context of collaborations with the industry, and widely adopted

worldwide. He has coauthored 60+ IEEE journal articles and eight patents. Dr. Pellegrino is an Associate Editor of IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS and a recipient of the 8th Grand Nagamori Award. He received nine best paper awards. He is a Founding Member of the Power Electronics Interdepartmental Center (PEIC) of Politecnico di Torino, a member of the Advisory Board of PCIM Europe, and currently the Rector's Advisor for Interdepartmental Centers of Politecnico di Torino.

**Eric Armando** (Senior Member, IEEE) received the M.Sc. and Ph.D. degrees in electrical engineering from the Politecnico di Torino, Turin, Italy, in 2002 and 2008, respectively.

He is currently with the Politecnico di Torino, as a Full Professor of power converters, electrical machines, and drives. He has coauthored numerous journal articles and three patents. His fields of interest are power electronics and high-performance ac motor drives.

Dr. Armando received three awards for innovation, one paper award from the Power Electronics Technical Committee of the IEEE Industrial Electronics Society and one paper award from the Industrial Drives Committee of the IEEE Industry Applications Society.