Received 20 June 2022; revised 8 July 2022; accepted 13 July 2022. Date of publication 19 July 2022; date of current version 1 August 2022. The review of this article was arranged by Editor C.-M. Zetterling.

Digital Object Identifier 10.1109/JEDS.2022.3192420

# Low Switching Loss Split-Gate 4H-SiC MOSFET With Integrated Heterojunction Diode

### HAI-YONG XU, YING WANG<sup>10</sup>, MENG-TIAN BAO<sup>10</sup>, AND FEI CAO

School of Electronics and Information, Hangzhou Dianzi University, Hangzhou 310018, China

CORRESPONDING AUTHORS: Y. WANG AND M.-T. BAO (e-mail: wangying7711@yahoo.com; baomengtian@163.com)

This work was supported in part by the National Research and Development Program for Major Research Instruments of China under Grant 62027814; in part by the National Natural Science Foundation of China under Grant 61904045; and in part by the Zhejiang Provincial Natural Science Foundation of China under Grant LQ20F040004.

**ABSTRACT** A 4H-SiC MOSFET with p-type region injection and integrated split gate and heterojunction diode is proposed in this paper. Compared with the conventional MOSFET, the proposed structure has a lower on-resistance and switching loss. And the gate oxide layer has been well protected by the p-type region, which reduces the electric field in gate oxide layer at the off-state. The on-resistance of device can be greatly reduced by increasing the doping concentration of current spreading layer and will not cause a huge electric field in gate oxide layer. The specific on-resistance is decreased by about 27.8% and the static characteristic (BV<sup>2</sup>/R<sub>on,sp</sub>) of the device is improved about 37.3%. SiC material has a high third quadrant turn-on voltage due to its wide band gap characteristics. The use of heterojunction integration can take place of parasitic body diode and reduce its turn-on voltage, avoid the bipolar degradation effect, and improves the reverse recovery characteristics. To evaluate the dynamic performance, the reverse transmission capacitance (C<sub>rss</sub>) and gate-drain charge (Q<sub>gd</sub>) of the proposed structure have been studied in this paper via numerical simulations. Based on the simulation, the HF-FOM (C<sub>rss</sub>×R<sub>on,sp</sub>) and HF-FOM<sup>2</sup> (Q<sub>gd</sub>×R<sub>on,sp</sub>) of the proposed structure are decreased by about 87% and 86%, respectively. Meanwhile, the reverse turn-on voltage and reverse recovery characteristics are also improved, and the total energy loss decreases by about 37.3%.

**INDEX TERMS** Silicon carbide, specific on-resistance, switching energy loss, figure of merit, heterojunction diode.

#### I. INTRODUCTION

Sic has good material properties, such as wide band gap, high electron mobility, high breakdown electric field, and stable physical and chemical properties [1]–[3]. It is widely used in power semiconductor devices and has excellent application prospects. Compared with the silicon insulated gate bipolar transistor (Si IGBT), the SiC metal oxide semiconductor field effect transistor (MOSFET) has a faster switching speed and a lower switching loss [4]–[9], [30].

Planar gate power MOSFET is widely used for high-speed switching applications since it features a lower reverse transfer capacitance ( $C_{rss}$ ) compared with trench MOSFET. The split-gate (SG) MOSFET improves the switching speed and decreases the  $C_{rss}$  by decreasing the overlap area of the gate to the drain electrode [10]. However, the use of SG MOSFET will usually increase the resistance of the device under the same cell size [11]–[13], and make the electric field crowding in the gate oxide under high voltage [26], which will affect the reliability of the device for long-term use. The values of HF-FOM ( $C_{rss} \times R_{on,sp}$ ) and HF-FOM<sup>2</sup> ( $Q_{gd} \times R_{on,sp}$ ) are usually compared to measure the performance of the device under high-frequency operation [14]–[15]. These values are not only related to the  $C_{rss}$  and  $Q_{gd}$ , but also related to the specific on-resistance ( $R_{on,sp}$ ). How to decrease the  $R_{on,sp}$  without degenerating other performance also needs to be studied.

Due to the wide band gap of SiC material, the forward turn-on voltage ( $V_F$ ) of the third quadrant body diode is large, which usually requires an anti-parallel Schottky barrier diode (SBD) as a freewheeling diode (FWD), will increase the chip area, introduce stray inductance and increase energy loss. Some literature studies have demonstrated the

integration of SBD in the structure to reduce the third quadrant conduction voltage drop and improve the reverse recovery characteristics [23], [28]. But, when the SBD structure is close to the gate electrode, it will bring metallization pollution and affect the reliability of the device [25]. And due to the mirror force effect and tunneling effect, it will bring a large leakage current, and degenerate the performance of the device.

Heterojunction diode (HJD) is composed of polysilicon and SiC, which is expected to obtain good performance due to its unipolar effect similar to SBD. Some researches have been reported, Tanaka *et al.* [30] fabricated heterojunction diodes with P+-polysilicon on the n-type 4H-SiC epitaxial layer, showing that HJD has ultra-low V<sub>on</sub> and lower leakage current in 2005. Pérez-Tomás *et al.* [31] first fabricated and analyzed the characteristics of n-n Si/SiC HJDs in 2007. Ni *et al.* [32] first fabricated trench MOS with integrated HJD in 2014. An and Hu [33] simulated a separated gate trench MOS integrated with HJD, indicating that HJD can improve the reverse recovery characteristics, and can inhibit the conduction of the pin body diode in 2019. Therefore, HJD is considered a new option to improve the device's overall performance.

In this paper, we propose a new 1200 V class 4H-SiC MOSFET integrated heterojunction diode with a p-type polysilicon region between split gate (HJD-SG-MOS). The HJD of the proposed structure is composed of P+-polysilicon and N-4H-SiC. The bottom of the P+-polysilicon is at the same height as the bottom of the gate oxide layer, which can effectively reduce the electric field at the gate corner and ensure the reliability of gate oxide layer. In addition, the HJD enables the device to work under the high doping concentration of current spreading layer (CSL), thus the Ron, sp can be effectively reduced without changing chip area. The proposed structure has a higher static performance and lowers dynamic performance compared to the conventional structure. The integrated HJD can reduce the hole injection efficiency, due to the lower barrier height of the electron compared with the hole. The HJD, which turns on before the parasitic pin diode, can reduce the V<sub>F</sub> and improve the reverse recovery characteristics. The gate oxide corner has a low electric field and is effectively protected thanks to the electric field shielding effect of the p-type region and the p-base region, which improves the reliability of the device [16]-[21]. To illustrate the superiority of HJD-SG-MOS, we chose the conventional MOSFET (Con-MOS) as a reference. The static and dynamic characteristics of the HJD-SG-MOS and Con-MOS are verified by simulations using the SILVACO Atlas TCAD [20].

#### **II. DEVICE STRUCTURE AND ENERGY BAND ANALYSIS**

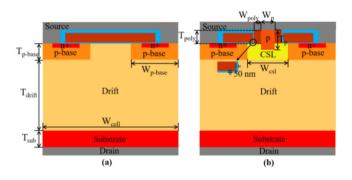

Fig. 1 shows the cross-section of the Con-MOS and HJD-SG-MOS. The two structures have the same cell thickness and width, and the doping concentration of drift is  $8 \times 10^{15}$  cm<sup>-3</sup>. The doping concentration of p-base is  $2 \times 10^{17}$  cm<sup>-3</sup> for both structures, and the depth of p-base is  $1.2 \ \mu$ m. The

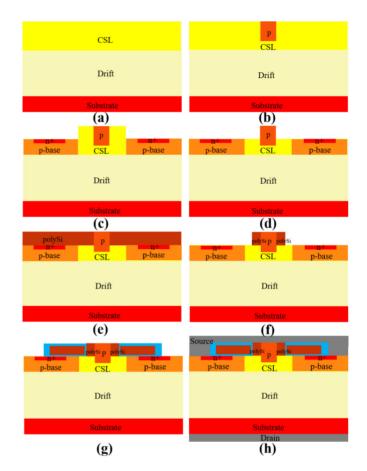

FIGURE 1. Schematic cross sections of (a) Con-MOS, which is used for reference in this article, and (b) HJD-SG-MOS.

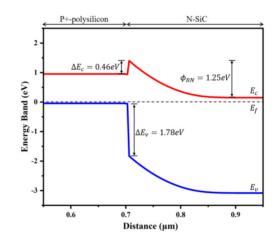

FIGURE 2. Energy-band diagram of P+-polysilicon/N-SiC heterojunction at thermal equilibrium.

thickness of drift layer for the Con-MOS and HJD-SG-MOS is 10  $\mu$ m. The channel oxide layer thickness of HJD-SG-MOS and Con-MOS is 50 nm, and the thickness of oxide layer beside the polysilicon of HJD-SG-MOS is also 50 nm, and the external oxide layer is 0.5  $\mu$ m, which can be formed by thermal oxidation and SiO<sub>2</sub> chemical vapor deposition [22]. The planar channel length is set 0.8  $\mu$ m and channel mobility is about 20 cm<sup>2</sup>/Vs. The doping concentration of the p-type ion-implantation region and P+-polysilicon in the HJD-SG-MOS is  $1 \times 10^{18}$  cm<sup>-3</sup> and  $1 \times 10^{20}$  cm<sup>-3</sup>, respectively. The integration of HJD is composed of p-type polysilicon and n-type 4H-SiC, which is located between the split gate. Meanwhile, due to the JEFT effect formed by ptype region and p-base region, additionally P+-polysilicon is much stronger than that of Con-MOS, therefore it is decided to add CSL to HJD-SG-MOS to reduce the on-resistance. In this structure, the gate corner is the same height as HJD, this greatly reduces the electric field of the gate corner in the off-state of the device. Detailed parameters are shown in Table 1.

Fig. 2 shows the energy band of the P+-polysilicon/N-SiC heterojunction diode at thermal equilibrium. The energy gap of the conduction band is 0.46 eV and the energy band gap of valence bands is 1.78 eV. The simulation result of

| PARAMETER                                             | VALUE                               |

|-------------------------------------------------------|-------------------------------------|

| Thickness N+ source junction, $T_{N^+}$               | 0.2 μm                              |

| Thickness of drift, T <sub>drift</sub>                | 10 µm                               |

| Thickness of substrate, T <sub>sub</sub>              | 1 µm                                |

| Thickness of p-base, T <sub>p-base</sub>              | 1.2 μm                              |

| Thickness of p-type region, T <sub>p</sub>            | 1.2 μm                              |

| Thickness of P+-polysilicon, T <sub>poly</sub>        | 0.7 μm                              |

| Width of cell, $W_{cell}$                             | 10 µm                               |

| Width of p-base, W <sub>p-base</sub>                  | 3.5 µm                              |

| Width of CSL, $W_{CSL}$                               | 3 µm                                |

| Width of P+-polysilicon, W <sub>poly</sub>            | 0.5 μm                              |

| Width of p-type region, W <sub>p</sub>                | 1 µm                                |

| Doping concentration of CSL, N <sub>CSL</sub>         | 6×10 <sup>16</sup> cm <sup>-3</sup> |

| Doping concentration of substrate, $N_{sub}$          | 1×10 <sup>19</sup> cm <sup>-3</sup> |

| Doping concentration of drift, N <sub>drift</sub>     | 8×10 <sup>15</sup> cm <sup>-3</sup> |

| Doping concentration of p-base, N <sub>p-base</sub>   | 2×10 <sup>17</sup> cm <sup>-3</sup> |

| Doping concentration of p-type region, N <sub>p</sub> | 1×10 <sup>18</sup> cm <sup>-3</sup> |

#### TABLE 1. Device parameter in simulation.

the energy band is similar to that of previously reported literature [3]–[33], which shows it's reasonable. The barrier height for electron can be calculated as the peak value of conduction energy minus the Fermi level energy ( $E_f$ ), which is 1.25 eV. The electrons have a much lower barrier height compared with holes, this allows electrons easily flow from N-SiC to P+-polysilicon, but holes can hardly flow from P+-polysilicon to N-SiC. Due to the low barrier height for electrons, the V<sub>F</sub> of HJD can be reduced, improving the reverse recovery characteristics of the device. Meanwhile, the p-type ion-implantation region can reduce the electric field in the polysilicon and gate oxide layer to avoid dynamic degradation.

#### **III. NUMERICAL SIMULATION AND RESULT ANALYSIS**

In this section, we use the SILVACO Atlas to simulate the characteristics of the proposed structure and conventional structure and analyze the result which is based on semiconductor theory. In this simulation, some physical models are added, including the Selberherr impact ionization model (impact Selb), the parallel electric field dependence model (fldmob), the concentration and temperature dependent model (analytic), the Shockley-Read-Hall recombination model (SRH), the auger recombination model (auger), the incomplete ionization model (incomplete), and the bandgap narrowing model (BGN) [19], [24].

## A. EFFECT OF KEY STRUCTURE PARAMETERS OF HJD-SG-MOS

The high doping concentration of CSL can effectively help the diffusion of electrons from the source to the drain.

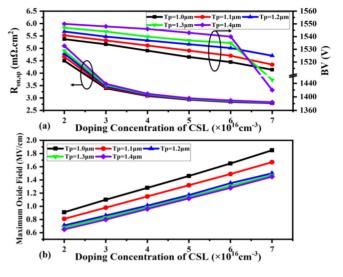

FIGURE 3. The influence of the doping concentration of CSL and the thickness of p-type region on (a)  $R_{on,sp}$ , and (b) maximum electric field in the oxide at  $V_{ds} = 1200$  V and  $V_{gs} = 0$  V.

But will increase the electric field in gate oxide, polysilicon, and the p-type region at off-state. And the excessive concentration of CSL will cause an electric field crowding phenomenon, which may lower the breakdown voltage. To alleviate this phenomenon, and makes a good shielding effect, the parameters of CSL and the added p-type region should be considered.

Fig. 3 shows the influence of the doping concentration of CSL and the thickness of p-type region (Tp) on the  $R_{on,sp}$  and the maximum oxide field ( $E_{ox}$ ) at drain bias of 1200 V. When the low concentration of CSL is low, the larger the Tp, the larger the Ron, sp of the device, as shown in Fig. 3(a). The electric field shielding effect formed by the p-type doping region can be stronger with a larger Tp, as shown in Fig. 3(b). With the concentration of CSL increasing, the higher electron concentration increases the current path between the source to the drain, effectively reducing the JEFT effect, decreasing Ron,sp [29]. But at the same time, Eox is almost linear variation. Tp has little effect on the onresistance of the device under high concentration of CSL, when the doping concentration is lower than  $7 \times 10^{16}$  cm<sup>-3</sup>, the larger Tp can undertake electric field more uniform and improve BV. With a higher doping concentration of CSL, the BV will decrease gradually.

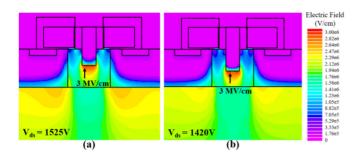

When the doping concentration of CSL is  $7 \times 10^{16}$  cm<sup>-3</sup> and Tp is 1.3  $\mu$ m or 1.4  $\mu$ m, the electric field crowding phenomenon will appear. Fig. 4 shows the electric field distributions of HJD-SG-MOS when (a) Tp is 1.2  $\mu$ m and (b) Tp is 1.4  $\mu$ m at critical voltage. The critical breakdown electric field of SiC material is 3 MV/cm [7]. When Tp is 1.2  $\mu$ m, the drain voltage when SiC reaches the critical electric field is 1525 V. But, while Tp is 1.4  $\mu$ m, due to the p-type region will undertake a larger electric field, the critical electric field will be reached in advance,

**FIGURE 4.** The electric field distribution of HJD-SG-MOS when (a) Tp = 1.2  $\mu$ m and (b) Tp = 1.4  $\mu$ m at critical voltage.

which is 1420 V. It is clear that when the doping concentration of CSL is beyond  $6 \times 10^{16}$  cm<sup>-3</sup>, the reduction of R<sub>on,sp</sub> is not obvious, but BV still decreases. The figure of merit (FOM=BV<sup>2</sup>/R<sub>on,sp</sub>) is usually considered as a trade-off between BV and R<sub>on,sp</sub>. When Tp is 1.2  $\mu$ m and the concentration of CSL is  $6 \times 10^{16}$  cm<sup>-3</sup>, the FOM is 811 MW/cm<sup>2</sup>. Based on the above analysis, Tp is henceforth considered as 1.2  $\mu$ m and the doping concentration of CSL is  $6 \times 10^{16}$  cm<sup>-3</sup>.

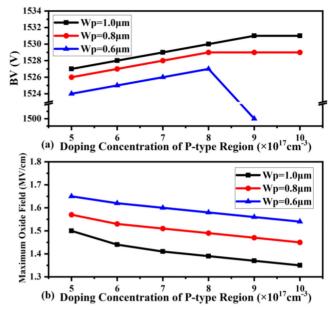

To avoid the reduction of BV caused by electric field crowding, the width of p-type region (W<sub>p</sub>) and the doping concentration of p-type region need further consideration. Fig. 5 shows the doping concentration of p-type region and Wp on the BV and Eox. As expected, increasing the doping concentration of p-type region and Wp could decrease  $E_{ox}$ , the wider and more doping concentration of p-type doping region can form a stronger JEFT effect when the device is off-State, to effectively reduce the electric field at the gate oxide. As Fig. 5(a) shows, BV increases with the increase of doping concentration of p-type region at first, but when it reaches  $9 \times 10^{17}$  cm<sup>-3</sup>, while Wp is 0.6  $\mu$ m, the BV decreases significantly, and the electric field crowding phenomenon at the corner of p-type region degenerate the BV. As mentioned above, 3 MV/cm is considered as SiC critical electric field, when Wp is 0.6  $\mu$ m and the doping concentration of p-type region is  $9 \times 10^{17}$  cm<sup>-3</sup>, the critical electric field will be reached in advance, which is 1500 V. Wp of 1  $\mu$ m and Wp of 0.8  $\mu$ m don't occur electric field crowding phenomenon. The wider the width of the p-type region, the more uniform the electric field can understand, reducing the electric field distribution on the surface of the p-type region. It is worth mentioning that when the CSL doping concentration is  $6 \times 10^{16}$  cm<sup>-3</sup>, the R<sub>on,sp</sub> of the HJD-SG-MOS does not change significantly with the increase of the concentration and the width of the p-type region. Considering the fabrication process of the structure, Wp between 0.8  $\mu$ m and 1  $\mu$ m is acceptable. Meanwhile, to avoid the electric field crowding phenomenon and to keep a good shielding effect, the doping concentration of p-type region is  $1 \times 10^{18}$  cm<sup>-3</sup>. Based on the above analysis, Wp is considered as 1  $\mu$ m and the doping concentration of p-type region is  $1 \times 10^{18}$  cm<sup>-3</sup>.

FIGURE 5. The influence of the doping concentration and the width of p-type region on (a) BV, and (b) maximum electric field in the oxide (E<sub>ox</sub>) at drain bias of 1200 V.

FIGURE 6. On-State output characteristic curves and off-State breakdown voltage output characteristic curves of the HJD-SG-MOS and Con-MOS.

#### **B. COMPARISON BETWEEN TWO STRUCTURES**

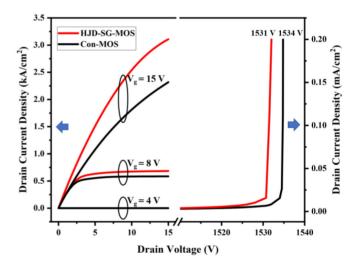

In the following part of this paper, we will focus on comparing the various characteristics of the two structures, such as IV characteristics, breakdown characteristics and various dynamic characteristics. Fig. 6. shows the on-State characteristic and off-State characteristic of the Con-MOS and HJD-SG-MOS, it can be calculated that the R<sub>on,sp</sub> of HJD-SG-MOS and Con-MOS are 2.89 m $\Omega \cdot cm^2$  and 4 m $\Omega \cdot cm^2$ , respectively (V<sub>gs</sub> = 15 V, V<sub>ds</sub> = 1 V). The R<sub>on,sp</sub> decreases by 1.11 m $\Omega \cdot cm^2$ , about 27.8%. Since the high concentration of CSL makes the current path wider at low drain voltages, this assists to disperse current to the drift.

FIGURE 7. Off-State electric field contours of (a) HJD-SG-MOS and (b) Con-MOS at critical voltage.

**FIGURE 8.** Reverse conduction I-V characteristics for the HJD-SG-MOS and Con-MOS. The inserted figures show the hole concentration distribution in the two devices at  $J_D = -200 \text{ A/cm}^2$ .

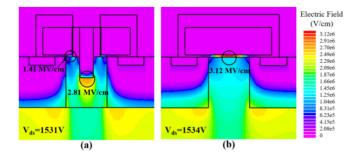

Fig. 7 shows the off-state electric field contours of HJD-SG-MOS and Con-MOS at critical voltage. When the Con-MOS reaches critical breakdown, the huge electric field, which is exceeds 3 MV/cm, is concentrated at the oxide and this reduces the reliability of long-term use. But at HJD-SG-MOS, the bottom of P+-polysilicon and the bottom of gate oxide are at same height, and the p-type ion-implantation region can undertake electric field and decrease the electric field at polysilicon and gate oxide, the electric field in gate oxide layer at critical voltage is 1.41 MV/cm, the gate oxide layer is effectively protected.

The FOM is used to demonstrate the trade-off between BV and  $R_{on,sp}$ , although the HJD-SG-MOS exhibits a similar breakdown voltage (1531 V) to that of Con-MOS (1534 V), due to the reduction of  $R_{on,sp}$ , HJD-SG-MOS shows a better static performance than Con-MOS, and it is calculated to 811 MV/cm<sup>2</sup> and 588 MV/cm<sup>2</sup>, respectively. It means that the FOM has improved by about 37.3%.

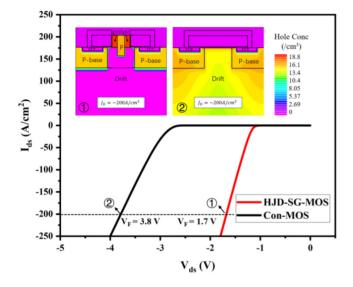

Fig. 8. Shows the reverse conduction IV characteristics of two devices at gate voltage bias -5 V, due to HJD has a low barrier height for electrons so that the HJD-SG-MOS can form an electron current at a low V<sub>F</sub>, which flows from

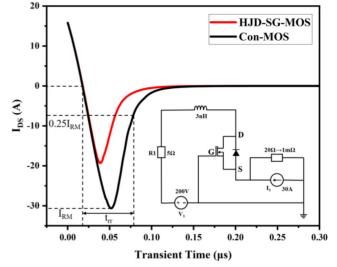

FIGURE 9. Reverse recovery characteristics of the HJD-SG-MOS and the Con-MOS. Inset: test circuit.

polysilicon to the source easily, can be turned on before p-base/n-drift body diode, and the V<sub>F</sub> of HJD-SG-MOS and Con-MOS is 1.7 V and 3.8 V, respectively. The inserted figures show the hole concentration distribution of HJD-SG-MOS and Con-MOS at  $J_d = -200 \text{ A/cm}^2$ . The results show that the HJD-SG-MOS has an extremely low hole concentration at drift compared to Con-MOS, which can suppress the conduction of pin diode and the bipolar degradation effect.

In order to study the reverse recovery characteristics, gate charge characteristics, and switching characteristics of devices, SPISCES and MIXEDMODE are used in the SILVACO Atlas TCAD.

Fig. 9 illustrates the reverse recovery characteristics of the two structures, the test circuit diagram is inserted into it [29]. The HJD-SG-MOS has effectively improved recovery characteristics. Compared with Con-MOS, the reverse recovery time ( $t_{\rm TT}$ ) decreased from 61 ns to 44 ns, it is a decrease of about 27.9%. Meanwhile, the peak reverses current ( $I_{\rm RM}$ ) and reverse recovery charge ( $Q_{\rm TT}$ ) decreased by 36.9% and 54.9%, respectively. As mentioned above, the proposed structure has a low hole concentration distribution at drift, so that the recombination process of minority and majority carriers can be reduced, therefore the reverse recovery characteristics are improved.

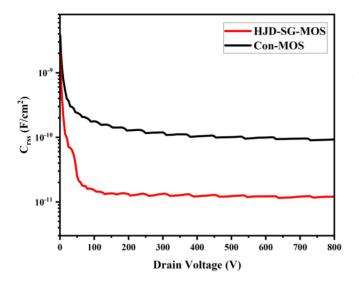

The reverse transmission capacitance ( $C_{rss}$ ) influenced by the drain voltage of two devices is depicted in Fig. 10. Compared with Con-MOS, HJD-SG-MOS shows smaller  $C_{rss}$ . The HJD-SG-MOS reduces the overlapping area of gate and drain to decrease the coupling of the gate and drains, and the p-type region introduces an electric field shielding effect that can also decrease the coupling. The  $C_{rss}$  of HJD-SG-MOS and Con-MOS extracted at drain bias 800 V is 16 pF/cm<sup>2</sup> and 93 pF/cm<sup>2</sup>, respectively. The HJD-SG-MOS shows a superior high-frequency figure of merit (HF-FOM), which is decreased from 372 m $\Omega$ ·pF to 46.2 m $\Omega$ ·pF, it is a

FIGURE 10. The C-V characteristics of the HJD-SG-MOS and Con-MOS at a frequency of 1MHz.

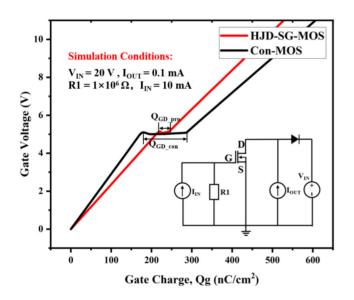

FIGURE 11. Gate charge characteristics of the HJD-SG-MOS and the Con-MOS. Inset: test circuit.

decrease of about 87%. Thus, the HJD-SG-MOS is expected to have a faster switching speed and lower switching loss.

Fig. 11 shows the gate charge  $(Q_g)$  of the two structures evaluated by the test circuit in the inset. Two structures have a similar height of miller plateau, which means they have the same threshold voltage. The gate-drain charge can be calculated by integrating the gate input current and the test time [27]. According to simulation,  $Q_{gd,sp}$  values of the HJD-SG-MOS and Con-MOS are 21 nC/cm<sup>2</sup> and 108 nC/cm<sup>2</sup>, respectively. Meanwhile, the miller platform of HJD-SG-MOS is shorter than that of Con-MOS, and the HF-FOM<sup>2</sup> decreases from 432 m $\Omega$ ·nC to 60.7 m $\Omega$ ·nC, it is a decrease of about 86%.

In 2017, K. Han proposed a buffer-gate region MOSFET with a high doping concentration of JEFT region (BG-MOSFET\_H), which was explained by simulation and experiment [10]. A method is proposed to extend the p-type shielding region to the edge of split-gate MOSFET and add a high doping concentration of n-type region in the central region to reduce the on-resistance. This method is very interesting, BG-MOSFET\_H has greatly improved the device HF-FOM and HF-FOM<sup>2</sup>. After removing the contact resistance, the on-resistance is 6.69 m $\Omega \cdot cm^2$ , and the HF-FOM and HF-FOM<sup>2</sup> are 154 m $\Omega$ ·pF and 401 m $\Omega$ ·nC, respectively. Compared to the conventional MOSFET (also removing the contact resistance), the HF-FOM and HF-FOM<sup>2</sup> have  $3.4 \times$  and  $3.5 \times$  smaller. The HJD-SG-MOS proposed in this paper has a lower on-resistance of 2.89 m $\Omega \cdot cm^2$ , and the HF-FOM and HF-FOM<sup>2</sup> are 46.2 m $\Omega$ ·pF and 60.7 m $\Omega$ ·nC, respectively. The device performance has been further optimized.

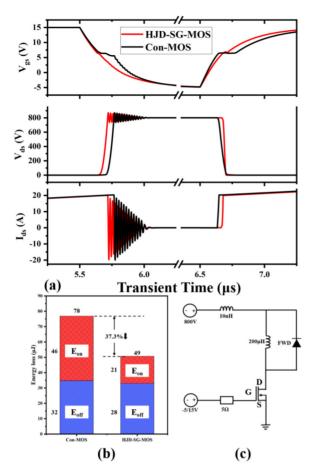

Finally, the switching characteristics of the two structures are also studied. The double-pulse test circuit is used to measure the switching energy loss of two structures. The switching waveforms of the two structures are shown in Fig. 12(a). Fig. 12(c) shows the double-pulse test circuit used for testing switching performances, the gate voltage source is turned on from -5 V to 15 V. From Fig. 12 (a), we can see that HJD-SG-MOS has a shorter miller platform, which is aligned with the results indicated in Fig. 11. And it can also be seen that the switching speed of HJD-SG-MOS is much faster than Con-MOS. The turn-on energy loss and turn-off energy loss can be calculated by the integration of  $I_{ds} \times V_{ds}$  and turn-on delay time or turn-off delay time, respectively [15]. Fig. 12(b) shows the switching energy loss of Con-MOS and HJD-SG-MOS. The energy loss of HJD-SG-MOS has a great improvement compared to Con-MOS, the total energy loss decreased from 78  $\mu$ J to 49  $\mu$ J, decreasing about 37.3%.

In order to show the feasibility of the proposed HJD-SG-MOS, the brief fabrication process is shown in Fig. 13. First, the epitaxial layer and the CSL are grown on the substrate in turn, as Fig. 13(a) shows. Second, the p-type region is formed by ion implantation. Third, as shown in Fig. 13(c), the inductively coupled plasma reactive ion etching (RIE) and ion-implantation are carried out to form p-base region and n+ source junction region, respectively. Fourth, RIE is used to etch both left and right sides of CSL of p-type region, as mentioned above, the width of p-type region is acceptable between 0.8  $\mu$ m and 1  $\mu$ m, which reduces the requirements for etching accuracy, and improves process feasibility. Fifth and sixth, the P+-polysilicon is formed by the refill and re-etch processes, as Figs. 13(e)-(f) shows. Seventh, Fig. 13(g) shows the formation process of the gate electrode, the dry thermal oxidation grows high-quality gate oxide to keep good interface quality of SiC/SiO<sub>2</sub> and gate control ability, then the polysilicon gate is deposited, and thick oxide is filled. Eighth, metal is deposited to form the source electrode and drain electrodes, and the complete structure is shown in Fig. 13(h).

FIGURE 12. (a) Turn-on and turn-off waveforms of two structures with test frequency 1MHz. (b) Switching energy loss of two structures. (c) Double-pulse test circuit used for switching operation.

TABLE 2. Characteristics of the proposed HJD-SG-MOS and Con-MOS.

| Characteristics                                     | Con-MOS | HJD-SG-MOS |

|-----------------------------------------------------|---------|------------|

| $R_{on,sp}^{a}(m\Omega \cdot cm^{2})$               | 4.00    | 2.89       |

| BV (V)                                              | 1534    | 1531       |

| $BV^2/R_{on,sp}$ (MW/cm <sup>2</sup> )              | 588     | 811        |

| E <sub>ox</sub> <sup>b</sup> (MV/cm)                | 2.58    | 1.31       |

| $V_{F}^{c}(V)$                                      | 3.8     | 1.7        |

| $t_{rr}(ns)$                                        | 61      | 44         |

| C <sub>rss</sub> <sup>d</sup> (pF/cm <sup>2</sup> ) | 93      | 16         |

| $C_{rss} \times R_{on,sp}(m\Omega \cdot pF)$        | 372     | 46.2       |

| $Q_{gd} (nC/cm^2)$                                  | 108     | 21         |

| $Q_{gd} \times R_{on,sp}(m\Omega \cdot nC)$         | 432     | 60.7       |

| $E_{total}(\mu J)$                                  | 78      | 49         |

${}^{a}R_{on,sp}$  at  $V_{gs}$ =15 V and  $V_{ds}$ =1 V,  ${}^{b}E_{ox}$  is the maximum electric field in oxide at drain bias 1200 V,  ${}^{c}V_{F}$  is obtained at  $V_{GS}$ =-5 V and  $J_{D}$ =-200 A/cm<sup>2</sup>,  ${}^{d}C_{rss}$  at  $V_{ds}$ = 800 V and frequency 1 MHz.

Table 2 summarizes the static characteristics and dynamic characteristics of the proposed HJD-SG-MOS and Con-MOS, including specific on-resistance (R<sub>on,sp</sub>), breakdown

FIGURE 13. Brief fabrication process of HJD-SG-MOS.

voltage (BV), reverse recovery time ( $t_{rr}$ ), reverse transmission capacitance ( $C_{rss}$ ), gate-drain charge ( $Q_{gd}$ ) and total energy loss ( $E_{total}$ ). To facilitate the comparison of the overall performance of the two structures, FOM ( $BV^2/R_{on,sp}$ ), HF-FOM ( $C_{rss} \times R_{on,sp}$ ), and HF-FOM<sup>2</sup> ( $R_{on,sp} \times Q_{gd}$ ) have also been presented.

#### **IV. CONCLUSION**

In this article, a 4H-SiC MOSFET integrated heterojunction diode with p-type poly-silicon region between split gates is proposed and numerically investigated using the SILVACO Atlas TCAD. The bottom of P+-polysilicon is at the same height as the bottom of the gate oxide layer and the p-type region is formed by ion implantation, which can effectively reduce the electric field in the gate oxide layer under the high concentration of CSL. The CSL can reduce the Ron.sp of the device, which improves the static performance. The P+-polysilicon and N-SiC HJD reduces the electron barrier height and due to the hole collection effect, the reverse recovery characteristics is improved. By relying on the reduction of the overlapping area of gate and drain, it can reduce the coupling of gate and drain, and decrease the gate-drain charge and reverse transmission capacitance. Through the double-pulse circuit test, it is proved that the proposed structure improves the switching characteristics and reduces the switching loss. The enhanced performance makes the HJD-SG-MOS a promising candidate for 1200 V class MOSFET applications.

#### REFERENCES

- A. Elasser and T. P. Chow, "Silicon carbide benefits and advantages for power electronics circuits and systems," *Proc. IEEE*, vol. 90, no. 6, pp. 969–986, Jun. 2002, doi: 10.1109/JPROC.2002.1021562.

- [2] J. Rabkowski, D. Peftitsis, and H.-P. Nee, "Silicon carbide power transistors: A new era in power electronics is initiated," *IEEE Ind. Electron. Mag.*, vol. 6, no. 2, pp. 17–26, Jun. 2012, doi: 10.1109/MIE.2012.2193291.

- [3] Z. Liang, P. Ning, and F. Wang, "Development of advanced all-SiC power modules," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2289–2295, May 2014, doi: 10.1109/TPEL.2013.2289395.

- [4] T. Yang, Y. Wang, and R. Yue, "SiC trench MOSFET with reduced switching loss and increased short-circuit capability," *IEEE Trans. Electron Devices*, vol. 67, no. 9, pp. 3685–3690, Sep. 2020, doi: 10.1109/TED.2020.3005992.

- [5] M. Zhang, J. Wei, H. Jiang, K. J. Chen, and C. H. Cheng, "A new SiC trench MOSFET structure with protruded p-base for low oxide field and enhanced switching performance," *IEEE Trans. Device Mater. Rel.*, vol. 17, no. 2, pp. 432–437, Jun. 2017, doi: 10.1109/TDMR.2017.2694220.

- [6] S. Hazra *et al.*, "High Switching Performance of 1700-V, 50-A SiC power MOSFET over Si IGBT/BiMOSFET for advanced power conversion applications," *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 4742–4754, Jul. 2016, doi: 10.1109/TPEL.2015.2432012.

- [7] X. She, A. Q. Huang, Ó. Lucía, and B. Ozpineci, "Review of silicon carbide power devices and their applications," *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 8193–8205, Oct. 2017, doi: 10.1109/TIE.2017.2652401.

- [8] T. Sakai and N. Murakami, "A new VDMOSFET structure with reduced reverse transfer capacitance," *IEEE Trans. Electron Devices*, vol. 36, no. 7, pp. 1381–1386, Jul. 1989, doi: 10.1109/16.30945.

- [9] J. Fabre, P. Ladoux, and M. Piton, "Characterization and implementation of dual-SiC MOSFET modules for future use in traction converters," *IEEE Trans. Power Electron.*, vol. 30, no. 8, pp. 4079–4090, Aug. 2015, doi: 10.1109/TPEL.2014.2352863.

- [10] K. Han, B. J. Baliga, and W. Sung, "A novel 1.2 kV 4H-SiC buffered-gate (BG) MOSFET: Analysis and experimental results," *IEEE Electron Device Lett.*, vol. 39, no. 2, pp. 248–251, Feb. 2018, doi: 10.1109/LED.2017.2785771.

- [11] K. Han, B. J. Baliga, and W. Sung, "Split-gate 1.2-kV 4H-SiC MOSFET: Analysis and experimental validation," *IEEE Electron Device Lett.*, vol. 38, no. 10, pp. 1437–1440, Oct. 2017, doi: 10.1109/LED.2017.2738616.

- [12] H. Jiang, J. Wei, X. Dai, M. Ke, C. Zheng, and I. Deviny, "Silicon carbide split-gate MOSFET with merged Schottky barrier diode and reduced switching loss," in *Proc. 28th Int. Symp. Power Semicond. Devices ICs (ISPSD)*, 2016, pp. 59–62, doi: 10.1109/ISPSD.2016.7520777.

- [13] K. Cha, J. Yoon, J. Cheon, and K. Kim, "The limitation of the split-gate MOSFET(SG-MOSFET) at 3.3kV," in *Proc. Int. Conf. Electron. Inf. Commun. (ICEIC)*, 2021, pp. 1–4, doi: 10.1109/ICEIC51217.2021.9369734.

- [14] K. Tian *et al.*, "An improved 4H-SiC trench-gate MOSFET with low ON-resistance and switching loss," *IEEE Trans. Electron Devices*, vol. 66, no. 5, pp. 2307–2313, May 2019, doi: 10.1109/TED.2019.2905636.

- [15] J. Zhang, Z. Chen, Y. Tu, X. Deng, and B. Zhang, "A novel SiC asymmetric cell trench MOSFET with split gate and integrated JBS diode," *IEEE J. Electron Devices Soc.*, vol. 9, pp. 713–721, 2021, doi: 10.1109/JEDS.2021.3097390.

- [16] B. J. Baliga, Fundamentals of Power Semiconductor Device. New York, NY, USA: Springer, 2008.

- [17] Y. Wang, K. Tian, Y. Hao, C. Yu, and Y. Liu, "An optimized structure of 4H-SiC U-shaped trench gate MOSFET," *IEEE Trans. Electron Devices*, vol. 62, no. 9, pp. 2774–2778, Sep. 2015, doi: 10.1109/TED.2015.2449972.

- [18] J. Wei, M. Zhang, H. Jiang, C. Cheng, and K. J. Chen, "Low ON-resistance SiC trench/planar MOSFET with reduced OFF-state oxide field and low gate charges," *IEEE Electron Device Lett.*, vol. 37, no. 11, pp. 1458–1461, Nov. 2016, doi: 10.1109/LED.2016.2609599.

- [19] Y. Cheng, Y. Wang, X. Wu, and F. Cao, "4H-SiC UMOSFET with an electric field modulation region below P-body," *IEEE Trans. Electron Devices*, vol. 67, no. 8, pp. 3298–3303, Aug. 2020, doi: 10.1109/TED.2020.3004777.

- [20] ATLAS User's Manual: Device Simulation Software, Version 5.15.32.R, Silvaco Int., Santa Clara, CA, USA, 2015.

- [21] J. A. Schrock *et al.*, "High-mobility stable 1200-V, 150-A 4H-SiC DMOSFET long-term reliability analysis under high current density transient conditions," *IEEE Trans. Power Electron.*, vol. 30, no. 6, pp. 2891–2895, Jun. 2015, doi: 10.1109/TPEL.2014.2357013.

- [22] K. Nakamura, S. Kusunoki, H. Nakamura, and M. Harada, "Advantages of thick CVD gate oxide for trench MOS gate structures," in *Proc. 12th Int. Symp. Power Semicond. Devices (ICs)*, 2000, pp. 83–86, doi: 10.1109/ISPSD.2000.856778.

- [23] W. Sung and B. J. Baliga, "On developing one-chip integration of 1.2 kV SiC MOSFET and JBS diode (JBSFET)," *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 8206–8212, Oct. 2017, doi: 10.1109/TIE.2017.2696515.

- [24] J. Wei, Y. Wang, M. Zhang, H. Jiang, and K. J. Chen, "Highspeed power MOSFET with low reverse transfer capacitance using a trench/planar gate architecture," in *Proc. 29th Int. Symp. Power Semicond. Devices ICs (ISPSD)*, 2017, pp. 331–334, doi: 10.23919/ISPSD.2017.7988956.

- [25] Y. Kobayashi *et al.*, "Evaluation of schottky barrier height on 4H-SiC m-face for Schottky barrier diode wall integrated trench MOSFET," *Jpn. J. Appl. Phys.*, vol. 56, no. 4S, pp. 1–6, 2017.

- [26] K. Li et al., "A new SiC split-gate MOSFET structure with protruded P-base and the mesa above JFET for improving HF-FOM," in Proc. 16th China Int. Forum Solid-State Light. Int. Forum Wide Bandgap Semicond. China (SSLChina: IFWS), 2019, pp. 29–32, doi: 10.1109/SSLChinaIFWS49075.2019.9019759.

- [27] H.-C. Luo *et al.*, "Investigations of SiC VDMOSFET with floating island structure based on TCAD," *IEEE Trans. Electron Devices*, vol. 66, no. 5, pp. 2295–2300, May 2019, doi: 10.1109/TED.2019.2900384.

- [28] F.-J. Hsu *et al.*, "High efficiency high reliability SiC MOSFET with monolithically integrated Schottky rectifier," in *Proc. 29th Int. Symp. Power Semicond. Devices ICs (ISPSD)*, 2017, pp. 45–48, doi: 10.23919/ISPSD.2017.7988889.

- [29] Y. Wang, Y.-C. Ma, Y. Hao, Y. Hu, G. Wang, and F. Cao, "Simulation study of 4H-SiC UMOSFET structure with p+-polySi/SiC shielded region," *IEEE Trans. Electron Devices*, vol. 64, no. 9, pp. 3719–3724, Sep. 2017, doi: 10.1109/TED.2017.2723502.

- [30] H. Tanaka, T. Hayashi, Y. Shimoida, S. Yamagami, S. Tanimoto, and M. Hoshi, "Ultra-low von and high voltage 4H-SiC heterojunction diode," in *Proc. 17th Int. Symp. Power Semicond. Devices ICs (ISPSD)*, 2005, pp. 287–290, doi: 10.1109/ISPSD.2005.1488007.

- [31] A. Pérez-Tomás et al., "Characterization and modeling of n-n Si/SiC heterojunction diodes," J. Appl. Phys., vol. 102, no. 1, Jul. 2007, Art. no. 014505, doi: 10.1063/1.2752148.

- [32] W. Ni et al., "SiC trench MOSFET with an integrated low von unipolar heterojunction diode," *Mater. Sci. Forum*, vols. 778–780, pp. 923–926, Feb. 2014.

- [33] J. An and S. Hu, "Heterojunction diode shielded SiC split-gate trench MOSFET with optimized reverse recovery characteristic and low switching loss," *IEEE Access*, vol. 7, pp. 28592–28596, 2019, doi: 10.1109/ACCESS.2019.2902246.