Received 10 November 2021; revised 15 December 2021; accepted 15 December 2021. Date of publication 19 January 2022; date of current version 16 June 2022. The review of this article was arranged by Editor A. Escobosa.

Digital Object Identifier 10.1109/JEDS.2022.3144500

# Six Decades of Research on 2D Materials: Progress, Dead Ends, and New Horizons

FRANK SCHWIERZ<sup>®</sup> (Senior Member, IEEE), AND MARTIN ZIEGLER<sup>®</sup>

Department of Electrical Engineering and Information Technology, Micro- and Nanoelectronic Systems, Technische Universität Ilmenau, 98693 Ilmenau, Germany CORRESPONDING AUTHOR: F. SCHWIERZ (e-mail: frank.schwierz@tu-ilmenau.de)

This work was supported in part by the Deutsche Forschungsgemeinschaft DFG under Project IDs SCHW 729/26-1 and Project 434434223—SFB 1461; in part by the Carl Zeiss Foundation via the Project MemWerk; and in part by the Federal State of Thuringia under Project ID 2018 FGR 0088 2D-Sens.

ABSTRACT The present paper guides the reader through six decades of research on 2D materials, thereby putting special focus on the use of these materials for electronic devices. It is shown that after a slow start and only little activity over many years, since 2004 the exploration of 2D materials advanced at an enormous pace. While some of the high expectations raised in the so-called golden era of graphene did not fulfil, other electronic applications for 2D materials that originally were not on the agenda gain increasing attention now. One of the main research topics in the field of 2D materials during the early 2000s was high-performance graphene transistors. This effort, however, led to a dead end due the consequences of the missing bandgap in graphene. On the other hand, the semiconducting 2D materials show potential for different device concepts including stacked-channel 2D nanosheet MOSFETs and 2D memristors. The former may become the transistor architecture of choice at the end of the CMOS roadmap and 2D memristors represent a promising device concept for future neuromorphic computing, a type of information processing that shows great potential for artificial intelligence applications where energy efficiency is a key requirement.

**INDEX TERMS** Memristor, nanosheet transistor, two-dimensional materials.

#### I. INTRODUCTION

The well-disposed reader might object that research on 2D (two-dimensional) materials began in 2004, when Novoselov and colleagues reported on the exfoliation of graphene [1], and not 60 years ago as the title of the present paper suggests. In fact, however, already six decades back from now the formation of monolayers with a regular arrangement of carbon atoms in a hexagonal lattice, i.e., the configuration today called graphene, was observed in experiments [2].

Before starting our discourse, a few remarks on the use of the term 2D materials in the present paper are advisable. As suggested by its designation, a 2D material such as graphene represents a 2D system with large extensions in two spatial dimensions and an extremely small extension in the third dimension. The electronic properties of such 2D systems differ from those of the corresponding 3D bulk material. It should be noted that 2D materials are by far not the only 2D systems relevant for electronics. The best known and most important electronic 2D system is

the inversion layer (channel) of the Si MOSFET, the dominating device in today's semiconductor electronics. In a conventional MOSFET, this inversion channel is an electrically induced extremely narrow quantum well at the surface of a thick 3D semiconductor substrate. The work on 2D inversion layers started already in the early 1950s for germanium structures [3] and was later extended to silicon [4] and other semiconductors. Another popular 2D system are the 2D electron gases occurring at III/V semiconductor heterojunctions, e.g., AlGaAs/GaAs or InAlAs/InGaAs, which are used in RF (radio frequency) transistors. Thus, one can distinguish between different types of electronic 2D systems, of which in the reminder of the present paper solely the 2D materials are discussed in detail.

Strictly speaking, 2D materials consist of a single monolayer of the corresponding material, e.g., of a single layer of carbon atoms in the case of graphene, or when considering 2D MoS<sub>2</sub> of one layer of molybdenum atoms sandwiched between two layers of sulfur atoms.

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

It became common practice in the community, however, to designate both monolayers and very thin sheets of a few monolayers as 2D materials, and we follow this convention.

The research on 2D materials passed through different stages, from a modest start through a period of enthusiasm and excitement (we call it the golden era of graphene), followed by a phase of disillusionment and partial frustration, finally leading to the current period of new prospects and cautious optimism. In the present paper, we go through these stages and discuss, from an electronic device engineer's perspective, both major achievements as well as problems encountered by the community and research directions that turned out to be dead ends. The discourse about the latter should not be misunderstood as a know-it-all critique. On the contrary, it should be considered as a constructive discussion in the spirit of Eden who was one of the leading scientists in the field of digital GaAs electronics in the late 1970 and in the 1980s and who, in retrospect, delivered a highly recommendable perspective on the evolution of digital GaAs technology [5]. Since this technology, in spite of some achievements, could not fulfill the early expectations, he stated that it is generally much more useful (for purposes of achieving success in the future) to focus on past mistakes, problems and failures than to bask in the glory of what went *right* [5].

2D materials are currently explored for many different applications and a variety of electronic device types based on 2D materials are under investigation. To keep the length of the discussion within reasonable limits, on the material side we deal most and foremost with graphene since it was the first 2D material investigated in detail and with the 2D TMDCs (transition metal dichalcogenides) which currently enjoy great popularity. Other 2D materials are mentioned briefly but are not discussed extensively. Regarding devices, the present paper focuses on 2D MOSFETs and 2D memristors, while other types of 2D devices are dealt with only in passing.

## **II. THE EARLY YEARS**

60 years ago, in November 1961, researchers from Heidelberg University, Germany, submitted a manuscript to the journal *Zeitschrift für Naturforschung* reporting on the reduction of graphitic oxide and the observation of ultra-thin carbon layers with a thickness down to a single monolayer of atoms.

The paper was published in March 1962 [2], provided evidence for the existence of a monolayer material, and marked the beginning of the research on 2D materials. Nevertheless, neither this paper nor those by May [6] from 1969 and van Bommel *et al.* [7] from 1975 on the formation of graphene on platinum and SiC surfaces attracted much attention, and the 2D materials played only a subordinated role in science for decades.

# III. THE GOLDEN ERA OF GRAPHENE AND THE ADVENT OF 2D MATERIALS BEYOND GRAPHENE

The situation changed abruptly in 2004, when the Geim-Novoselov group from the University of Manchester, U.K., published a seminal paper on the mechanical exfoliation of graphene from a natural graphite crystal. They observed carrier mobilities exceeding 10,000 cm<sup>2</sup>/Vs at 300 K in their samples, discussed the possibility of ballistic carrier transport in graphene over long distances, and concluded that graphene may enable *transistors that could be scaled down to much smaller sizes and would consume less energy and operate at higher frequencies than traditional semiconducting devices* [1]. This paper raised enormous interest and became one of the most frequently cited works in the fields of physics and electronics. The Web of Science database [8] counts 44,719 citations of this paper (as of Nov. 05, 2021).

Likewise in 2004, a second important paper on graphene was published [9]. Here, a group from Georgia Tech, USA, reported the formation of epitaxial graphene on SiC, and again ballistic transport and the potential of graphene for electronics were addressed: . . . the graphite/SiC system could provide a platform for a new breed of seamlessly integrated ballistic carrier devices based on nanopatterned epitaxial graphene. Such an architecture could have many advantages for nanoelectronics, including ... energy efficiency ... Shortly afterwards, an upper limit of 200,000 cm<sup>2</sup>/Vs for the room-temperature carrier mobility in graphene was suggested [10]. These high mobilities moved to the fore in the discussions on the prospects of graphene and set the main direction of graphene research for the next years, ultra-fast high-performance transistors, while other material properties (e.g., the missing bandgap) gained less attention.

Funding agencies worldwide established a magnitude of programs for graphene research. Examples are the CERA program (2008, DARPA, \$30 million) aiming at RF graphene electronics [11], the National Graphene Institute in the U.K. (\$80 million approved in 2012) to foster the commercialization of graphene, most notably for electronic applications [12], and the Roadmap for Graphene Commercialization (South Korea, \$200 million approved in 2012) [13]. Moreover, the Graphene Flagship (> \$1 billion) was implemented by the EU in 2013 [14]. According to the Flagship Research Agenda, graphene devices were expected to break the 1 THz barrier in a matter of a few years [15], and thus a core focus of the Flagship was on ultra-fast graphene-based electronic systems.

On the scientific side, we witnessed fast progress in the field of 2D electronic devices. In 2007, the first graphene MOSFET was demonstrated [16] and only a few years later graphene transistors showing cutoff frequencies  $f_T$  ( $f_T$  is an RF figure of merit and designates the frequency at which the small-signal current gain drops to unity) in excess of 420 GHz [17] and graphene RF ICs have been reported [18]. Moreover, researchers extended their work to 2D materials

beyond graphene. A milestone in this direction was the demonstration of the world's first 2D MoS<sub>2</sub> MOSFETs [19] by A. Kis and colleagues from EPFL Lausanne, Switzerland. This achievement motivated intensive work on MOSFETs with semiconducting 2D channels consisting, e.g., of TMDCs (like MoS2 or WSe2) or phosphorene. Due to the ultimate thinness of the 2D materials, such MOSFETs show excellent electrostatics and strongly suppressed short-channel effects. In addition, several 2D materials offer heavier carrier effective masses than Si. As predicted by theoretical studies [20]-[21], this leads to a very effective suppression of direct source-drain tunneling even at ultra-short gate length levels below 5 nm. The demonstration of a MoS<sub>2</sub> MOSFET with 1 nm gate length (note that this is the MOSFET with shortest gate reported ever) showing excellent switch-off and a subthreshold swing of 65 mV/dec [22] confirmed the predictions.

In 2009, A. Geim was awarded the prestigious annual e750,000 Körber Foundation European Science award and in 2010 the Nobel prize in physics went to A. Geim and K. Novoselov for their achievements in graphene research. In addition to the scientific results mentioned above, these two prizes consolidated the reputation of graphene to be highly promising for future electronics.

#### IV. THE PERIOD OF DISILLUSIONMENT

Despite the excellent results discussed in Section III, the voices warning that the potential of the 2D materials might be overestimated became louder during the 2010s and the prospects of the 2D materials for electronics were assessed less optimistic. Several reasons contributed to this change of mood.

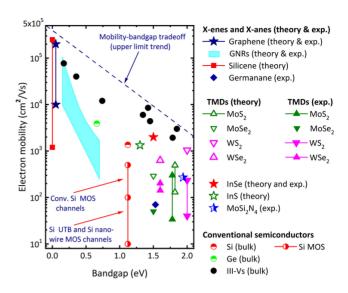

Since graphene is gapless, graphene MOSFETs do not switch off properly and therefore are not suitable for digital logic. We note that digital logic represents the backbone of today's information processing technologies and stands for a multi-billion-dollar market. While a bandgap can be opened in ultra-narrow graphene nanoribbons, this leads to a dramatic reduction of the mobility so that the main advantage of graphene is lost [23]. Graphene as well as all semiconductors including the 2D materials beyond graphene are subject to what we call the mobility-bandgap tradeoff, which is observed at and around room temperature and shown in Fig. 1. It can clearly be seen that by trend for an increasing bandgap the mobility decreases and that only the zero bandgap and narrow bandgap materials show ultra-high mobilities. The hole mobility (not shown in Fig. 1) exhibits a similar, albeit somewhat less pronounced, behavior.

Interestingly, at low temperatures the electron mobility gap between graphene and the conventional semiconductors seems to become smaller or even to disappear. For example, in suspended graphene an electron mobility of  $10^6$  cm<sup>2</sup>/Vs was measured at 4.2 K [25], while at the same temperature electron mobilities exceeding  $3 \times 10^6$  cm<sup>2</sup>/Vs were observed in AlGaAs/GaAs structures [26].

FIGURE 1. Room temperature electron mobility vs bandgap of 2D materials, bulk semiconductors (undoped), and Si MOS channels, together with a trend line indicating the mobility-bandgap tradeoff. UTB: Ultra-thin body. After [23]–[24], updated.

Another important application for transistors is RF electronics. Since in most RF circuits the transistors do not necessarily have to be switched off, a lot of work has been done to exploit the high mobility of graphene for ultrafast RF MOSFETs. It turned out, however, that the zero bandgap of graphene is not only responsible for the missing switch-off, but for a poor saturation of the drain current in the transistors' output characteristics (drain current  $I_D$ as a function of the drain-source voltage  $V_{DS}$ ) as well. It has been shown by both theory [27] and experiments [28] that graphene MOSFETs with long gates show kind of a drain current saturation in a very limited  $V_{DS}$  range only. High-performance RF MOSFETs, however, need to have very short gates and for graphene MOSFETs with such short gates the saturation is poor or even missing at all. The slope of the output characteristics is a measure for the current saturation, appears in the transistor's small-signal equivalent circuit as the differential drain conductance  $g_{ds}$ , and affects the RF performance. It particularly degrades the RF power gain and the maximum frequency of oscillation  $f_{\text{max}}$  ( $f_{\text{max}}$  is the frequency at which the unilateral power gain drops to unity), while its effect on current gain and  $f_{\rm T}$  is much weaker [24], [29]. Recognizing this is important when assessing the suitability of transistors for RF applications since for most of such applications a high power gain and thus a high  $f_{\text{max}}$  are much more important than high current gain and high  $f_{\rm T}$ .

Table 1 comparing the RF performance of the best RF graphene MOSFETs with that of competing RF FET types in terms of  $f_{\rm max}$  and  $f_{\rm T}$  indicates that graphene MOSFETs are capable of RF operation but that their performance falls short to that of other RF FETs. This leads us to the conclusion that graphene MOSFETs are neither suited for digital logic nor for high-performance RF applications.

TABLE 1. RF performance of RF FET types in terms of  $f_{\text{max}}$  and  $f_{\text{T}}$ .

| FET type           | $f_{\text{max}}$ (GHz) | $f_{\rm T}\left({ m GHz}\right)$ |

|--------------------|------------------------|----------------------------------|

| Graphene<br>MOSFET | 200                    | 255                              |

|                    | =                      | 427                              |

| InP HEMT           | 1500                   | 610                              |

|                    | 1000                   | 700                              |

| GaAs mHEMT         | 1100                   | 660                              |

|                    | 800                    | 688                              |

| Si MOSFET          | 420                    | 360                              |

|                    | 410                    | 395                              |

Data taken from [17,30-36]. HEMT: High electron mobility transistor. mHEMT: Metamorphic HEMT. Note that for the second graphene MOSFET in the table only the cutoff frequency but not  $f_{\text{max}}$  is provided in Ref. [17].

When the limitations of graphene MOSFETs became apparent, several groups explored vertical beyond-MOSFET graphene transistor concepts [37]–[38]. While operating vertical graphene transistors could be demonstrated, their performance was by far not good enough to compete successfully with Si transistors. Thus, we cannot help but note that graphene transistors turned out to be a dead end.

On the other hand, MOSFETs using semiconducting 2D materials beyond graphene for the channel stand out due to their excellent switch-off. Moreover, many 2D materials offer heavy carrier effective masses  $m_{\rm eff}$ . For example,  $m_{\rm eff}$  for electrons is around  $0.5 \times m_0$  for the Mo-based 2D TMDCs, compared to about  $0.2 \times m_0$  for Si, where  $m_0$  is the electron rest mass. Strictly speaking, the Si  $m_{\rm eff}$  given above refers to the conductivity electron mass for Si channels on (100) Si surfaces in the <011> direction while for other Si surface orientations and channel directions,  $m_{\rm eff}$  may vary to a certain, but in many cases limited, extent [4], [39]–[40]).

Since a heavy  $m_{\rm eff}$  helps suppressing source-drain tunneling in ultra-short channels, 2D MOSFETs are scalable beyond the limits of Si MOSFETs and therefore show promise for ultimately scaled CMOS logic with sub-5 nm gate transistors. Note, however, that in 2011 the FinFET architecture has been introduced into production [44]. Since FinFET footprint can be decreased without shrinking the gate length, it became consensus in the CMOS community that, in contrast to earlier predictions [45], gate length scaling will level off at around 10 nm [46]. Here, source-drain tunneling is not an issue and a heavy carrier effective mass as offered by 2D materials is not needed. Moreover, the attempts to introduce 2D materials into FinFET technology showed rather modest results [47].

All this caused the optimism of the 2D community to fade away and made way for an atmosphere of gloom. While that is understandable to a certain extent, we recommend to keep a cool head and not to put the 2D materials off the agenda, in particular since inflated expectations, followed by a phase

of disillusionment, are not specific for graphene and the 2D materials but rather part of the evolution of any emerging technology today [48]–[50]. Instead, the strengths and weaknesses of the 2D materials should be carefully analyzed, the question whether fundamental reasons speak against using a certain material for a targeted application (e.g., gapless channels do not switch off) should be posed, and, if there are such fundamental limitations, alternative applications where other materials fail or perform poor should be looked for.

## V. NEW PROSPECTS AND CAUTIOUS OPTIMISM

Currently, research on 2 D materials continues without restraint. An interesting detail is that the search for unexplored 2D materials received support from computational chemistry recently. Taking 3D bulk materials as starting point and investigating their bonding conditions, a plethora of materials potentially existing in stable 2D configurations were identified and their electronic properties were calculated.

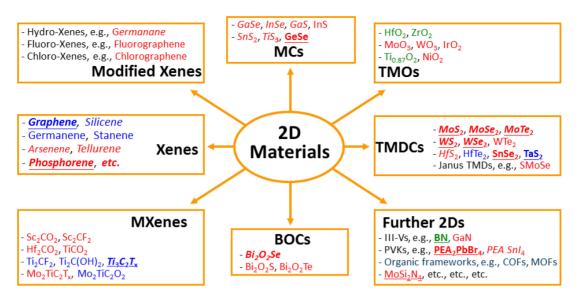

The number of such potentially existing 2D materials rose quickly from 49 in 2013 [51] to 170 in 2014 [52] and finally to over 6000 today [53]. Figure 2 shows our attempt to categorize the 2D materials and provides an impression of the tremendous diversity of this material class. We note, however, that in the foreseeable future only part of these 2D materials will really be prepared and that so far, this is our guess, only less than 5% of the possibly existing 6000 2D materials have been demonstrated experimentally yet.

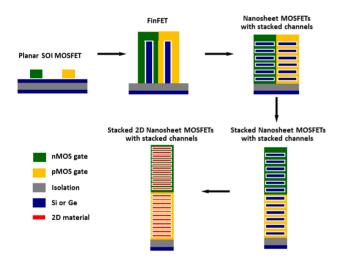

On the device side, we observe a renewed interest in 2D MOSFETs for digital CMOS in both academia and the chip industry. The reason is that FinFET scaling, although still successfully practiced, will come to an end soon and therefore a new MOSFET architecture is needed. A possible beyond-FinFET scaling scenario is shown in Fig. 3. In a first step, the FinFETs are replaced by MOSFETs with multiple vertically stacked Si (or Ge) nanosheet channels [54]. By properly choosing the lateral dimensions of the nanosheet channels, substantial area savings can be achieved. We mention that the concept of stacked-channel nanosheet MOSFETs is already close to mass production. In May 2021 IBM unveiled details of a 2-nm node technology which applies stacked-channel Si nanosheet transistors [55]. Note that the 2 nm in the technology name is neither related to the gate length nor to any other geometrical dimension of the transistors. Instead, the gate length of the MOSFETs in this technology is 12 nm. The plan is to transfer the 2-nm technology to Si foundries and to have it foundryready in 2024. The next step envisaged is vertically stacking not only the channels of a single transistor but rather stacking n-channel and p-channel nanosheet MOSFETs one on top of the other. Such a technology does already exist at the laboratory stage [56]. Finally, replacing the Si nanosheets of stacked-channel transistors by sheets of 2D materials might lead to the ultimate MOSFET architecture [57].

This concept would combine the area saving arising from optimizing the lateral nanosheet dimensions as mentioned

FIGURE 2. Categorization of the 2D materials. BOC: Bismuth oxychalcogenide. TMO: Transition metal oxide. PVK: Perovskite. MC: Metal chalcogenide. PEA: C<sub>6</sub>H<sub>5</sub>C<sub>2</sub>H<sub>4</sub>NH<sub>3</sub>. Ti<sub>3</sub>C<sub>2</sub>T<sub>x</sub>: Ti<sub>3</sub>C<sub>2</sub> terminated with F or OH groups. COF: Covalent-organic framework [41]. MOF: Metal-organic framework [42]. Meaning of the colors: Black – Material classes and subclasses. Red – Semiconducting. Blue – Metallic/semi-metallic/narrow-bandgap. Green – Insulating. Meaning of the styles (regardless of color): Italic – Used for the channel in experimental MOSFETs. Underlined – Used as active layer in experimental memristors. After [43], updated.

FIGURE 3. Scenario for MOSFET evolution from planar MOSFETs (past) via FinFETs (today) to stacked 2D nanosheet MOSFETs at the final stage of CMOS scaling, after [57].

above with the area savings of vertically stacked n- and p-channel MOSFETs (two transistors at the footprint of one) and with the superior electrostatics of 2D MOSFETs.

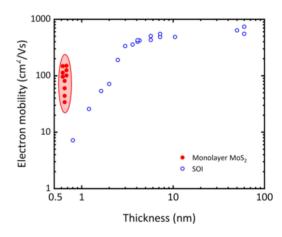

Moreover, the carrier mobilities in semiconducting 2D materials, while being lower than that in bulk Si, are very competitive compared to, and even higher than, the mobilities in ultra-thin Si nanosheets, see Fig. 4.

Another promising application for 2D materials is memristive devices. They can be used as both a memory and a switch and, moreover, show promise for bio-inspired neuromorphic computing which can be extremely beneficial for AI (artificial intelligence) applications. AI is one of the major trends in current information technology and its importance

FIGURE 4. Electron mobility in monolayer MoS<sub>2</sub> and thin SOI (silicon-on insulator) layers versus thickness. Data for SOI taken from [58]–[60].

will grow quickly in the future [61]. Today's computers, which are based on the von Neumann architecture and on Boolean logic operations, are far from ideal for AI applications. A much better solution for many AI problems is information processing in a similar way as done in biologic brains, i.e., neuromorphic computing.

A precondition for such a bio-inspired computing is the ability to emulate the operation of the basic elements of biologic brains, which are synapses and neurons. A first option to achieve this is using neuromorphic CMOS-based systems. Pioneering work in this field was done during the late 1980s [62]–[63] and commercial CMOS-based neuromorphic systems are available on the market today [64]–[65]. An alternative and possibly even more promising approach is to use devices showing resistive switching as basic building block. These devices, in their simplest form, are two-terminal

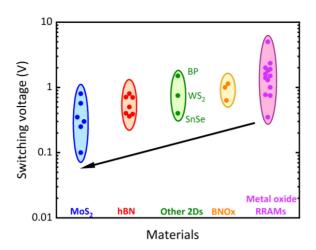

FIGURE 5. Representative ranges of the switching voltages for various memristor types (colored ellipses). The data points represent the lowest switching voltages for the different memristor types and are taken from [71], [77]–[87].

structures able to switch between a high-resistance and a low-resistance state and to retain their resistance state when the voltage is removed. Already in the 1960s the first resistive switching devices were demonstrated [66]–[67] and during the 2000s a true run on such devices could be observed. One direction of the work was focused on exploiting resistive switching for non-volatile memories [68] called RRAM (resistive RAM). Moreover, with resistive switching devices the operation of synapses and neurons can be reproduced in a very elegant and energy-efficient way and in this context they are usually designated as memristors [69]–[70]. Memristors may become the key elements for future neuromorphic computing and may play an important role in AI systems where energy efficiency is a key requirement.

So far, the majority of memristors are vertical MIM (metal-insulator-metal) structures [70]–[72]. Part of them show memristive switching right after fabrication but typically need switching voltage around/above 1 V while others offer lower switching voltages, yet need a cumbersome electroforming process. Recently both vertical [73]–[74] and lateral [75]–[76] memristors made of 2D materials, most notably TMDCs and hBN (hexagonal boron nitride), have been reported. The vertical 2D memristors show several advantages over MIM memristors. First, most of them do not need electroforming and second, by trend they show lower switching voltages than to MIM memristors as can be seen in Fig. 5.

The lowest reported switching voltages of  $100\ldots300$  mV of vertical 2D memristors are already close to the potentials typical for biologic brains. While lateral 2D memristors require higher switching voltages than their vertical counterparts, they offer a higher degree of functionality since lateral structures can be equipped with gates and additional terminals. Thus, 2D memristors may play an important role in future power-efficient neuromorphic computing.

A long term vision is the realization of integrated hybrid 2D CMOS – 2D memristor circuits. The basic idea has been elaborated for a Si CMOS process where one or more MIM memristor layers are fabricated on top of the CMOS circuitry [88] and such hybrid circuits have already been realized [89]. The same concept can be imagined for a 2D nanosheet CMOS process combined with 2D memristors. In addition, 2D memristors are attractive for an application much different from neuromorphic computing. In [90], hBN memristors have been used as RF switches operating properly up to 50 GHz.

Beyond transistors and memristors, much more electronic applications for the 2D materials are currently under consideration. These include, e.g., optoelectronic devices, sensors, the use of 2D materials for transparent electrodes and in batteries, and many more [91]–[92]. There are even the first commercial applications for graphene, albeit not in the heart of high-performance electronics. Instead, graphene is used, e.g., as efficient heat conductor and for flexible touch screens [93].

To get a realistic picture of the current status of the 2D materials, in addition to the promising prospects highlighted above also some of the problems and challenges connected to the 2D materials beyond graphene should be discussed briefly. A first general point to mention is that the 2D material and device technology is still at an embryonic stage and much less mature compared to Si technology. One of the pressing issues is the deposition of homogeneous 2D material films with constant and controllable thickness and crystallographic quality. Different approaches for large-area 2D material growth including chemical vapor deposition, metal-organic chemical vapor deposition, atomic layer deposition, and molecular beam epitaxy, each with specific merits and drawbacks, are followed [94]-[95]. Frequently the development of a growth process enabling the formation of a single-crystalline 2D layer across a whole wafer is defined as the goal. While this is certainly a respectable objective, it is an illusion to believe that such a growth method will become available in the foreseeable future, and this is not necessary at all since a well-defined layer quality is needed in and close to the active device regions only and not across an entire wafer. Recent work on the patterned growth of 2D materials [96]–[97] goes precisely in this direction.

Another issue of the 2D materials is doping. First, for digital CMOS both n-channel and p-channel 2D nanosheet MOSFETs are needed and thus an approach for achieving local n-type and p-type doped regions has to be developed for the 2D materials. Moreover, to achieve optimum transistor performance in Si CMOS technology, well-defined doping profiles with steep doping gradients are used, and the possibility to get such doping profiles for 2D nanosheet MOSFETs is highly desirable. While research on doping of 2D materials is in progress [98], a lot of work in this field is still to be done. Finally, at present it is not clear which insulators are best suited for the gate dielectric of 2D

nanosheet MOSFETs [99]. Also crucial for both 2D transistors and memristors are the contacts between metals and the 2D materials [100]. For transistors, ohmic source/drain contacts with low contact resistance are needed. The contact resistances achieved so far are still too high and need to be reduced. Depending on the memristor type, good ohmic contacts and possibly also well-defined rectifying Schottky contacts are needed.

Finally it should be mentioned that the physics of 2D memristors and the origin of resistive switching in these devices are still not well understood. Thus, apart from solving various problems related to the growth and processing of 2D materials, a lot of theoretical work, in particular on the operation of 2D memristors, is still to be done.

# VI. SUMMARY AND OUTLOOK

Research on 2D materials started slowly 60 years ago, experienced a tremendous boom since 2004, and is an incredibly active field of research still today [101]–[103]. Many of the 2D materials, in particular those having a bandgap, are promising for transistors at the end of the CMOS roadmap, for memristors, and for other types of devices. Gapless 2D materials such as graphene, however, could not fulfill the high expectations. When assessing the potential of new materials and novel device concepts, be they nanosheet MOSFETs, memristors, or others, one should never focus on only a single material property or only on one particular device feature since, as we have seen in the discussion on graphene and the high carrier mobility, this may lead into a dead end. Instead, one should always keep an eye on the big picture.

Graphene is the first 2D material that found its way to commercial applications, though not in devices for highperformance information processing. Moreover, it paved the way for the large variety of other 2D materials currently under investigation. From these, in particular the semiconducting materials are of great interest for electronics. In spite of many open questions and unsolved problems, we expect further rapid progress in the research on 2D materials. On the other hand, certainly not all current expectations will be met. One should always bear in mind that Si has an incredible head start over all other electronic materials in terms of maturity and accumulated investments. This makes it difficult for alternative materials, including the 2D materials, to compete. Notwithstanding we are convinced that 2D materials will enjoy popularity in the future as they do today and that some of them will find their way into real-world electronic applications.

# **REFERENCES**

- [1] K. S. Novoselov *et al.*, "Electric field effect in atomically thin carbon films," *Science*, vol. 306, no. 5696, pp. 666–669, 2004.

- [2] H. P. Boehm, A. Clauss, G. O. Fischer, and U. Hofmann, "Dünnste Kohlenstoff-Folien," *Zeitschrift Naturforschung*, vol. 17, no. 3, pp. 150–153, 1962.

- [3] W. L. Brown, "N-type surface conductivity on p-type germanium," Phys. Rev., vol. 91, pp. 518–527, Aug. 1953.

- [4] F. Stern and W. E. Howard, "Properties of semiconductor surface inversion layers in the electric quantum limit," *Phys. Rev.*, vol. 163, pp. 816–835, Nov. 1967.

- [5] R. C. Eden, "25 Years of digital III-V technology: A perspective," in *Dig. GaAs IC Symp.*, 2003, pp. 7–10.

- [6] J. W. May, "Platinum surface LEED rings," Surface Sci., vol. 17, pp. 267–270, Sep. 1969.

- [7] A. J. van Bommel, J. E. Crombeen, and A. van Tooren, "LEED and Auger electron observations of the SiC(0001) surface," *Surface Sci.*, vol. 48, no. 2, pp. 463–472, 1975.

- [8] "Web of Science." [Online]. Available: https://www.webofscience.com/wos/woscc/basic-search Jan. 24, 2022).

- [9] C. Berger et al., "Ultrathin epitaxial graphite: 2D electron gas properties and a route toward graphene-based nanoelectronics," J. Phys. Chem. B, vol. 108, pp. 19912–19916, Dec. 2004.

- [10] S. V. Morozov et al., "Giant intrinsic carrier mobilities in graphene and its bilayer," Phys. Rev. Lett., vol. 100, Jan. 2008, Art. no. 016602.

- [11] J. Albrecht, "Overview of DARPA carbon electronics for RF applications program (CERA)," in *Dig. DRC*, 2010, pp. 204–205.

- [12] "Global Graphene Research and Funding." 2012. [Online]. Available: https://www.nextbigfuture.com/2012/08/global-graphene-research-and-funding.html

- [13] "South Korea Funds Graphene Commercialization." 2012. [Online]. Available: https://www.nextbigfuture.com/2012/05/south-korea-funds-graphene.html

- [14] "Graphene-Flagship." 2021. [Online]. Available: https://graphene-flagship.eu/research/funding/Flagship

- [15] "Deliverable 3.2 'Research Agenda for the GRAPHENE Flagship." 2012. [Online]. Available: http://cordis.europa.eu/docs/projects/cnect/ 8/284558/080/deliverables/001-DeliverableD32.pdf

- [16] M. C. Lemme, T. J. Echtermeyer, M. Baus, and H. Kurz, "A graphene field-effect device," *IEEE Electron Device Lett.*, vol. 28, no. 4, pp. 282–284, Apr. 2007.

- [17] R. Cheng et al., "High-frequency self-aligned graphene transistors with transferred gate stacks," Proc. Nat. Acad. Sci., vol. 109, pp. 11588–11592, Jul. 2012.

- [18] S.-J. Han et al., "Graphene technology with inverted-T gate and RF passives on 200 mm platform," in Tech. Dig. IEDM, 2011, pp. 19–22.

- [19] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, "Single-layer MoS<sub>2</sub> transistors," *Nat. Nanotechnol.*, vol. 6, pp. 147–150, Jan. 2011.

- [20] K. Alam and R. K. Lake, "Monolayer MoS<sub>2</sub> transistors beyond the technology road map," *IEEE Trans. Electron Devices*, vol. 59, no. 12, pp. 3250–3254, Dec. 2012.

- [21] S. Thiele, W. Kinberger, R. Granzner, G. Fiori, and F. Schwierz, "The prospects of transition metal dichalcogenides for ultimately scaled CMOS," *Solid-State Electron.*, vol. 143, pp. 2–9, May 2018.

- [22] S. B. Desai et al., "MoS<sub>2</sub> transistors with 1-nanometer gate lengths," Science, vol. 354, no. 6308, pp. 99–102, 2016.

- [23] F. Schwierz, "Graphene transistors," Nat. Nanotechnol., vol. 5, pp. 487–496, May 2010.

- [24] F. Schwierz, "Graphene transistors: Status, prospects, and problems," Proc. IEEE, vol. 101, no. 7, pp. 1567–1584, Jul. 2013.

- [25] E. V. Castro et al., "Limits on charge carrier mobility in suspended graphene due to flexural phonons," Phys. Rev. Lett., vol. 105, Dec. 2010, Art. no. 266601.

- [26] C. T. Foxon, J. J. Harris, D. Hilton, J. Hewett, and C. Roberts, "Optimisation of (Al,Ga)As/GaAs two-dimensional electron gas structures for low carrier densities and ultrahigh mobilities at low temperatures," *Semicond. Sci. Technol.*, vol. 4, no. 7, pp. 582–585, 1989.

- [27] S. A. Thiele, J. A. Schaefer, and F. Schwierz, "Modeling of graphene metal-oxide-semiconductor field-effect transistors with gapless largearea graphene channels," *J. Appl. Phys.*, vol. 107, no. 9, 2010, Art. no. 094505.

- [28] I. Meric et al., "Current saturation in zero-bandgap, top-gated graphene field-effect transistors," Nat. Nanotechnol., vol. 3, pp. 654– 659, Sep. 2018.

- [29] F. Schwierz, "Graphene transistors 2011," in *Proc. IEEE VLSI-TSA*, 2011, pp. 16–17.

- [30] Y. Wu et al., "200 GHz maximum oscillation frequency in CVD graphene radio frequency transistors," ACS Appl. Mater. Interfaces, vol. 8, pp. 25645–25649, Sep. 2016.

- [31] I. Post et al., "A 65nm CMOS SOC technology featuring strained silicon transistors for RF applications," in Tech. Dig. IEDM, 2006, pp. 1–3.

- [32] C.-H. Jan *et al.*, "A 45nm low power system-on-chip technology with dual gate (logic and I/O) high-k/metal gate strained silicon transistors," in *Tech. Dig. IEDM*, 2008, pp. 1–3.

- [33] T. Merkle *et al.*, "Backside process free broadband amplifier MMICs at D-band and H-band in 20 nm mHEMT technology," in *Proc. CSIC*, 2014, pp. 1–3.

- [34] D.-H. Kim, B. Brar, and J. A. del Alamo, " $f_T = 688$  GHz and  $f_{max} = 800$  GHz in  $L_g = 40$  nm  $In_{0.7}Ga_{0.3}As$  MHEMTs with  $g_{m\_max} > 2.7$  mS/mum," in Tech. Dig. IEDM, 2011, pp. 319–322.

- [35] X. Mei et al., "First demonstration of amplification at 1 THz using 25-nm InP high electron mobility transistor process," IEEE Electron Device Lett., vol. 36, no. 4, pp. 327–329, Apr. 2015.

- [36] S. Sarkozy et al., "Demonstration of a G-band transceiver for future space crosslinks," *IEEE Trans. Terahertz Sci. Technol.*, vol. 3, no. 5, pp. 675–681, Sep. 2013.

- [37] L. Britnell et al., "Field-effect tunneling transistor based on vertical graphene heterostructures," Science, vol. 335, pp. 947–950, Feb. 2012

- [38] S. Vaziri et al., "A graphene-based hot electron transistor," Nano Lett., vol. 13, pp. 1435–1439, Mar. 2013.

- [39] R. Iijima, L. F. Edge, V. Paruchuri, and M. Takayanagi, "Electron mobility limited by remote charge scattering in thin (100) and (110)oriented silicon body double-gated metal-oxide-semiconductor fieldeffect transistors with high-k gate dielectrics," *Jpn. J. Appl. Phys.*, vol. 51, no. 4R, 2012, Art. no. 044102.

- [40] M. O. Baykan et al., "Physical insights on comparable electron transport in (100) and (110) double-gate fin field-effect transistors," Appl. Phys. Lett., vol. 100, no. 12, 2012, Art. no. 23502.

- [41] F. Yu et al., "Electrochromic two-dimensional covalent organic framework with a reversible dark-to-transparent switch," Nat. Commun., vol. 11, p. 5534, Nov. 2020.

- [42] C. Li, K. Wang, J. Li, and Q. Zhang, "Recent progress in stimulus-responsive two-dimensional metal-organic frameworks," ACS Mater. Lett., vol. 2, pp. 779–797, May 2020.

- [43] F. Schwierz, "Performance of graphene and beyond graphene 2D semiconductor devices," ECS Trans., vol. 69, no. 10, pp. 231–240, 2015

- [44] S. Damaraju et al., "A 22nm IA multi-CPU and GPU system-on-chip," in Proc. Dig. ISSCC, 2012, pp. 56–57.

- [45] "The International Technology Roadmap for Semiconductors 2013 Edition." [Online]. Available: http://www.itrs2.net/ (accessed Jan. 24, 2022).

- [46] "The International Roadmap for Devices and Systems 2020 Edition." [Online]. Available: https://irds.ieee.org/ (accessed Jan. 24, 2022).

- [47] M.-C. Chen et al., "TMD FinFET with 4 nm thin body and back gate control for future low power technology," in *Tech. Dig. IEDM*, 2015, pp. 831–834.

- [48] M. Blosch and J. Fenn. "Understanding Gartner's Hype Cycles." [Online]. Available: https://www.gartner.com/en/documents/3887767/understandinggartner-s-hype-cycles (accessed Jan. 24, 2022).

- [49] "Top Trends in the Gartner Hype Cycle for Emerging Technologies, 2017." [Online]. Available: https://www.gartner. com/smarterwithgartner/top-trends-in-the-gartner-hype-cycle-foremerging-technologies-2017/ (accessed Jan. 24, 2022).

- [50] F. Schwierz, "2D electronics—A promising option or a type C hype cycle?" in *Proc. EDTM*, 2018, pp. 233–235.

- [51] S. Lebegue, T. Bjorkman, M. Klintenberg, R. M. Nieminen, and O. Eriksson, "Two-dimensional materials from data filtering and ab initio calculations," *Phys. Rev X*, vol. 3, Jul. 2013, Art. no. 031002.

- [52] P. Miro, M. Audiffred, and T. Heine, "An atlas of two-dimensional materials," Chem. Soc. Rev., vol. 43, no. 18, pp. 6537–6554, 2014.

- [53] J. Zhou et al., "2DMatPedia, an open computational database of twodimensional materials from topdown and bottom-up approaches," Sci. Data, vol. 6, p. 86, Jun. 2019.

- [54] N. Loubet et al., "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET," in Dig. VLSI Technol., 2017, pp. T230–T231.

- [55] J. Salter. "IBM Creates the World's First 2 nm Chip." [Online]. Available: https://arstechnica.com/gadgets/2021/05/ibm-creates-the-worlds-first-2-nm-chip/ (accessed Jan. 24, 2022).

- [56] C.-Y. Huang et al., "3-D self-aligned stacked nMOS-on-pMOS nanoribbon transistors for continued Moore's Law scaling," in Tech. Dig. IEDM, 2020, pp. 425–428.

- [57] R. Chau, "Process and packaging innovations for Moore's Law continuation and beyond," in *Tech. Dig. IEDM*, 2019, pp. 1–6.

- [58] D. Esseni, M. Mastrapasqua, G. K. Celler, C. Fiegna, L. Selmi, and E. Sangiorgi, "Low field electron and hole mobility of SOI transistors fabricated on ultrathin silicon films for deep submicrometer technology application," *IEEE Trans. Electron Devices*, vol. 48, no. 12, pp. 2842–2850, Dec. 2001.

- [59] K. Uchida, J. Koga, and S. Takagi, "Experimental study on electron mobility in ultrathin-body silicon-on-insulator metal-oxidesemiconductor field-effect transisto," *J. Appl. Phys.*, vol. 102, no. 7, 2007, Art. no. 074510.

- [60] M. Schmidt, M. C. Lemme, H. D. B. Gottlob, F. Driussi, L. Selmi, and H. Kurz, "Mobility extraction in SOI MOSFETs with sub 1 nm body thickness," *Solid-State Electron.*, vol. 53, pp. 1246–1251, Dec. 2009.

- [61] J. Welser et al., "Future computing hardware for AI," in Tech. Dig. IEDM, 2018, pp. 21–26.

- [62] R.O. Grondin et al., "A synthetic neural chip," in Proc. 22nd Asilomar Conf. Signals Syst. Comput., 1988, pp. 640–644.

- [63] C. Mead, "Neuromorphic electronic systems," *Proc. IEEE*, vol. 78, no. 10, pp. 1629–1639, Oct. 1990.

- [64] F. Akopyan et al., "TrueNorth: Design and tool flow of a 65 mW 1 million neuron programmable neurosynaptic chip," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 34, no. 10, pp. 1537–1557, Oct. 2015.

- [65] M. Davis et al., "Loihi: A neuromorphic manycore processor with onchip learning," *IEEE Micro*, vol. 38, no. 1, pp. 82–99, Jan./Feb. 2018.

- [66] T. W. Hickmott, "Low-frequency negative resistance in thin anodic oxide films," J. Appl. Phys., vol. 33, no. 9, pp. 2669–2682, 1962.

- [67] S. R. Ovshinsky, "Reversible electrical switching phenomena in disordered structures," *Phys. Rev. Lett.*, vol. 21, pp. 1450–1453, Nov. 1968.

- [68] R. Waser, R. Dittmann, G. Staikov, and K. Szot, "Redox-based resistive switching memories—Nanoionic mechanisms, prospects, and challenges," *Adv. Mater.*, vol. 21, pp. 2632–2663, Jul. 2009.

- [69] L. O. Chua and S. M. Kang, "Memristive devices and systems," Proc. IEEE, vol. 64, no. 2, pp. 209–223, Feb. 1976.

- [70] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, pp. 80–83, May 2008.

- [71] M. Ziegler, C. Riggert, M. Hansen, T. Bartsch, and H. Kohlstedt, "Memristive Hebbian plasticity model: Device requirements for the emulation of Hebbian plasticity based on memristive devices," *IEEE Trans. Biomed. Circuits Syst.*, vol. 9, no. 2, pp. 197–206, Apr. 2015.

- [72] J. J. Yang, M. D. Pickett, X. Li, D. A. A. Ohlberg, D. R. Stewart, and R. S. Williams, "Memristive switching mechanism for metal/oxide/metal nanodevices," *Nat. Nanotechnol.*, vol. 3, pp. 429–433, Jun. 2008.

- [73] R. Ge et al., "Atomristor: Nonvolatile resistance switching in atomic sheets of transition metal dichalcogenides," Nano Lett., vol. 18, no. 1, pp. 434–441, 2018.

- [74] Y. Shi et al., "Electronic synapses made of layered two-dimensional materials," Nat. Electron., vol. 1, pp. 458–465, Aug. 2018.

- [75] D. Li et al., "MoS<sub>2</sub> memristors exhibiting variable switching characteristics toward biorealistic synaptic emulation," ACS Nano, vol. 12, pp. 9240–9252, Sep. 2018.

- [76] V. K. Sangwan et al., "Multi-terminal memtransistors from polycrystalline monolayer molybdenum disulfide," *Nature*, vol. 554, pp. 500–504, Feb. 2018.

- [77] D. Dev et al., "2D MoS<sub>2</sub>-based threshold switching memristor for artificial neuron," *IEEE Electron Device Lett.*, vol. 41, no. 6, pp. 936–939, Jun. 2020.

- [78] R. Xu et al., "Vertical MoS<sub>2</sub> double-layer memristor with electrochemical metallization as an atomic-scale synapse with switching thresholds approaching 100 mV," Nano Lett., vol. 19, pp. 2411–2417, Mar. 2019.

- [79] P. Cheng, K. Sun, and Y. H. Hu, "Memristive behavior and ideal memristor of 1T phase MoS<sub>2</sub> nanosheets," *Nano Lett.*, vol. 16, no. 1, pp. 572–576, 2016.

- [80] Y. Shi et al., "Coexistence of volatile and non-volatile resistive switching in 2D h-BN based electronic synapses," in Tech. Dig. IEDM, San Francisco, CA, USA, 2017, pp. 119–122.

- [81] C. Pan et al., "Coexistence of grain-boundaries-assisted bipolar and threshold resistive switching in multilayer hexagonal boron nitride," Adv. Funct. Mater., vol. 27, Mar. 2017, Art. no. 1604811.

- [82] Y. Zhou et al., "Black phosphorus based multicolor light-modulated transparent memristor with enhanced resistive switching performance," ACS Appl. Mater. Interfaces, vol. 12, pp. 25108–25114, May 2020.

- [83] X. Yan et al., "Vacancy-induced synaptic behavior in 2D WS<sub>2</sub> nanosheet-based memristor for low-power neuromorphic computing," Small, vol. 15, Jun. 2019, Art. no. 1901423.

- [84] J. Guo et al., "Highly reliable low-voltage memristive switching and artificial synapse enabled by van der Waals integration," Matter, vol. 2, pp. 965–976, Apr. 2020.

- [85] H. Zhao et al., "Atomically thin femtojoule memristive device," Adv. Mater., vol. 29, Dec. 2017, Art. no. 1703232.

- [86] G. Piccolboni et al., "Investigation of the potentialities of vertical resistive RAM (VRRAM) for neuromorphic applications," in Tech. Dig. IEDM, Washington, DC, USA, 2015, pp. 447–450.

- [87] M. Ziegler, K. Ochs, M. Hansen, and H. Kohlstedt, "An electronic implementation of amoeba anticipation," *Appl. Phys. A*, vol. 114, pp. 565–570, Feb. 2014.

- [88] D. B. Strukov and R. S. Williams, "Four-dimensional address topology for circuits with stacked multilayer crossbar arrays," *Proc. Nat. Acad. Sci.*, vol. 106, pp. 20155–20158, Dec. 2009.

- [89] C. Wenger et al., "Inherent stochastic learning in CMOS-integrated HfO<sub>2</sub> arrays for neuromorphic computing," *IEEE Electron Device Lett.*, vol. 40, no. 4, pp. 639–642, Apr. 2019.

- [90] M. Kim et al., "Analogue switches made from boron nitride monolayers for application in 5G and terahertz communication systems," Nat. Electron., vol. 3, pp. 479–485, May 2020.

- [91] W. Cao et al., "2-D layered materials for next-generation electronics: Opportunities and challenges," *IEEE Trans. Electron Devices*, vol. 65, no. 10, pp. 4109–4121, Oct. 2018.

- [92] N. Briggs et al., "A roadmap for electronic grade 2D materials," 2D Mater., vol. 6, no. 2, 2019, Art. no. 022001.

- [93] W. Kong et al., "Path towards graphene commercialization from lab to market," Nat. Nanotechnol., vol. 14, pp. 927–938, Oct. 2019.

- [94] J. Sun et al., "Synthesis methods of two-dimensional MoS<sub>2</sub>: A brief review," Crystals, vol. 7, p. 198, Jul. 2017.

- [95] W. Choi, N. Choudhary, G. H. Han, J. Park, D. Akinwande, Y. H. Lee, "Recent development of two-dimensional transition metal dichalcogenides and their applications," *Mater. Today*, vol. 20, pp. 116–130, Apr. 2017.

- [96] X. Chen, Y. J. Park, T. Das, H. Jang, J.-B. Lee, and J.-H. Ahn, "Lithography-free plasma-induced patterned growth of MoS<sub>2</sub> and its heterojunction with graphene," *Nanoscale*, vol. 8, no. 33, 2016, Art. no. 15181.

- [97] A. Sharma et al., "Large area, patterned growth of 2D MoS<sub>2</sub> and lateral MoS<sub>2</sub>–WS<sub>2</sub> heterostructures for nano and opto-electronic applications," Nanotechnology, vol. 31, Apr. 2020, Art. no. 255603.

- [98] K. Zhang and J. Robinson, "Doping of two-dimensional semiconductors: A rapid review and outlook," MRS Adv., vol. 4, pp. 2743–2757, Oct. 2019.

- [99] Y. Y. Illarionov et al., "Insulators for 2D nanoelectronics: The gap to bridge," Nat. Commun., vol. 11, p. 3385, Jul. 2020.

- [100] A. Allain, J. Kang, K. Banerjee, and A. Kis, "Electrical contacts to two-dimensional semiconductors," *Nat. Mater.*, vol. 14, pp. 1195–1205, Nov. 2015.

- [101] Q. Zhao et al., "Current status and prospects of memristors based on novel 2D materials," Mater. Horiz., vol. 7, no. 6, pp. 1495–1518, 2020.

- [102] C. Chang et al., "Recent progress on two-dimensional materials," Acta Physico-Chimica Sinica, vol. 37, no. 12, 2021, Art. no. 2108017.

- 103] S. Das et al., "Transistors based on two-dimensional materials for future integrated circuits," Nat. Electron., vol. 2, pp. 786–799, Nov. 2021.