Received 4 November 2020; revised 4 February 2021 and 21 May 2021; accepted 5 July 2021. Date of publication 9 July 2021; date of current version 19 July 2021. The review of this article was arranged by Editor E. Sangiorgi.

Digital Object Identifier 10.1109/JEDS.2021.3095389

# Determining the Electrical Charging Speed Limit of ReRAM Devices

M. VON WITZLEBEN<sup>® 1</sup>, S. WALFORT<sup>2</sup>, R. WASER<sup>® 1,3,4</sup> (Member, IEEE), S. MENZEL<sup>® 3</sup> (Member, IEEE), AND U. BÖTTGER<sup>1</sup>

1 Institut für Werkstoffe der Elektrotechnik 2, RWTH Aachen University, 52074 Aachen, Germany 2 Institut für Materialphysik, Westfälische Wilhelms-Universität Münster, 48149 Münster, Germany

3 Peter Grünberg Institut 7, Forschungszentrum Jülich and JARA-FIT, 52428 Jülich, Germany 4 Peter Grünberg Institut 10, Forschungszentrum Jülich and JARA-FIT, 52428 Jülich, Germany

+ Feer Oranoerg institut 10, Forschungszehr um Junen and JARA-111, 52420 Junen, German

CORRESPONDING AUTHOR: M. von WITZLEBEN (e-mail: witzleben@iwe.rwth-aachen.de)

This work was supported in part by the Deutsche Forschungsgemeinschaft under Grant SFB 917, and in part by the Federal Ministry of Education and Research (BMBF), Germany, through the Project NEUROTEC under Grant 16ES1134 and Grant 16ES1133K. It is based on the Jülich Aachen Research Alliance (JARA-Fit).

ABSTRACT Redox-based random-access memory (ReRAM) has the potential to successfully address the technological barriers that today's memory technologies face. One of its promising features is its fast switching speed down to 50 ps. Identifying the limiting process of the switching speed is, however, difficult. At sub-nanosecond timescales three candidates are being discussed: An intrinsic limitation, being the migration of mobile donor ions, e.g., oxygen vacancies, the heating time, and its electrical charging time. Usually, coplanar waveguides (CPW) are used to bring the electrical stimuli to the device. Based on the data of previous publications, we show, that the rise time of the effective electrical stimulus is mainly responsible for limiting the switching speed at the sub-nanosecond timescale. For this purpose, frequency domain measurements up to 40 GHz were conducted on three Pt\TaOx\Ta devices with different sizes. By multiplying the obtained scattering parameters of these devices with the Fourier transform of the incoming signal, and building the inverse Fourier transform of this product, the voltage at the ReRAM device can be determined. Finally, the rise time of the voltage at the ReRAM device is calculated, which is a measure to the electrical charging time. It was shown that this rise time amounts to 2.5 ns for the largest device, which is significantly slower than the pulse generator's rise time. Reducing the device's rise time down to 66 ps is possible, but requires smaller features sizes and other optimizations, which we summarize in this paper.

INDEX TERMS ReRAM, VCM, tantalum oxide, waveguide structures, vector network analysis.

## I. INTRODUCTION

Today's memory technologies inevitably approach the end of Moore's law, which raises the need for new memory technologies [1]. Among other emerging memory technologies, ReRAM has the potential to satisfy this demand [2]–[4]. The information in ReRAM devices is stored in its resistance, which can be programmed between a high resistive state (HRS) and a low resistance (LRS) by applying electrical stimuli. One class of ReRAM devices is the valence change memory (VCM), which is usually realized by a vertical stack of two metallic electrodes and a transition metal oxide (e.g., TaO<sub>x</sub>) sandwiched between the two electrodes [2]. One electrode is inert (e.g., Pt), whereas its counter electrode is oxygen affine (e.g., Ta). This metal-oxide-metal-stack corresponds to a parallel plate capacitor, which has a characteristic electrical charging time.

The change in resistance results from a rearrangement of oxygen vacancies, which forms a conductive filament within the transition metal oxide [2]. This rearrangement occurs at the interface to the inert electrode, which is, therefore, referred to as electronically active electrode. The opposite electrode has ohmic attributes and is, therefore, referred to as ohmic electrode. In the LRS, this conductive filament connects the active electrode with the ohmic electrode and thereby decreases the device's resistance. Applying a positive voltage to the active electrode repels the positively charged oxygen vacancies. This results in a rupture of the conductive filament at the active electrode, bringing the device to the HRS. This process is referred to as RESET. During the opposite process (SET), a negative voltage is applied to the active electrode, which attracts the oxygen vacancies and closes the ruptured region in the conductive filament. The device is now back in the LRS.

The voltages applied during the SET and the RESET operations are significantly higher, than the voltages applied during the readout of the device's resistance. This yields the need for fast switching times at high voltages and a long data retention at low voltages (also referred to as voltage-timedilemma [2]). In consequence, overcoming this dilemma requires a strong non-linear dependence of the switching time on the applied voltage. In our recent publication, we have shown that the SET time of VCM devices depends indeed strongly non-linearly on the applied voltage in the range from 250 ps to  $10^4$  s [5], which is sufficient to address the voltage-time-dilemma.

The strong non-linearity origins from the thermally accelerated drift of oxygen vacancies within the conducting filament occurring due to Joule heating during the SET and the RESET operation [6]-[9]. This increase in temperature was also observed experimentally [10]-[13]. At the beginning of the SET operation the device is in the HRS, which is characterized by a low oxygen vacancy concentration at the active electrode [6]. This region is referred to as disc and the oxygen vacancy rich region at the ohmic electrode as plug. The application of a negative pulse to the active electrode induces an electric current into the filamentary region. Due to the low oxygen vacancy concentration in the disc, most of the voltage drops over this region, which results in Joule heating. The higher temperatures, in turn, facilitate the migration of oxygen vacancies towards the disc, leading to a higher electronic conductivity. This results in a continuously increasing current, which has also been observed for TaO<sub>x</sub>-based devices [14]. This process is self-accelerated and results in a thermal runaway, which brings the device to the LRS.

So far, several studies have investigated the switching time at timescales below 1 ns [5], [15]–[18]. The fastest SET time within 50 ps was observed in TaO<sub>x</sub> and ZrO<sub>x</sub> [19] and the fastest RESET time within 85 ps in AlN [20]. In all of these studies, short electrical pulses were applied to VCM devices. Most studies use coplanar waveguide (CPW) structures to bring the short electrical pulses to the device. Their characteristic impedance is designed for 50 $\Omega$  and, therefore, they provide good impedance matching at the contacts. In addition, CPW structures are used at slower timescales [21]–[23] and for the characterization of radio frequency (RF) switches realized with ReRAM devices [24] and phase change memory (PCM) devices [25]. As the transmission line is interrupted at the device, the incoming pulse is reflected. The incoming and reflected pulses superimpose, doubling the effectively applied voltage at the VCM device. The timescale at which this doubling occurs was so far only estimated by circuit based models [15], [26], [27].

At timescales above 10 ns, the migration of oxygen vacancies within the transition metal oxide limits the switching speed [28]. At timescales below 10 ns also the heating time of the VCM device or the electrical charging time becomes relevant [18]. However, it is unclear which of those processes dominates the switching kinetics. So far only finite element (FEM) simulations of the heating exist. They suffer from several uncertainties, such as the geometry of the filament and the thermal properties of the transition metal oxide, which are the thermal conductivity, the heat capacity, and the mass density. The thermal properties of thin films differ from the bulk values and are, therefore, difficult to estimate. The simulation results so far indicate the possibility of the heating to occur only within few picoseconds [18] or several nanoseconds [6]. The electrical charging time depends strongly on the VCM device's area [27].

In this study, we show that at time-scales below 10 ns the rise time of the electrical stimuli (corresponding to the electrical charging time) at the VCM device limits the switching speed. The rise time originates from the presence of capacitances, inductances and resistances of the leads, which increase the electrical charging time of VCM devices. The rise times were estimated for Pt\TaOx \Ta-devices with three different device sizes. To this end, we conducted frequency domain measurements up to 40 GHz. By building the product of the scattering parameters and the Fourier transform of the applied signal, the reflected and transmitted signal at the VCM device can be calculated in the frequency domain. Inversely Fourier transforming from the frequency domain to the time domain of these results allows the calculation of the effectively applied voltage to the VCM device, including its time dependency. This is explained in detail in Section III. This approach is commonly used for high frequency applications [29]-[32]. As described above the VCM stack of the devices constitutes a parallel plate capacitor with a characteristic charging time. Consequently, it takes some time for the effective voltage to reach the maximum voltage. We determine, therefore, the effective voltage for the used devices, and its rise time (10%-90%), which is a measure of their charging time.

The impact of the circuit on the switching kinetics has already been studied with circuit models, in which also the effective voltage at the device was calculated [27] or simulated [15], [26]. Torrezan *et al.* also conducted frequency domain measurements up to 20 GHz [15]. The simulated scattering parameters of their circuit model matched the experimental ones well. Their results, however, do not include information on the electrical charging time. As our approach transforms the results from the frequency domain to the time domain, circuit modeling becomes unnecessary. Our approach, also does not rely on assumptions about the circuit and also takes the frequency dependency of all involved components into account. Also, Kim *et al.* investigated the frequency response of amorphous  $TaO_x$  layers up to 40 GHz [33], but they did not discuss the impact of their results on ReRAM applications.

We also compare the SET kinetics of the three devices on a sub-nanosecond timescale. Two of them were already published in previous studies [5], [19]. By means of the estimated effectively applied voltage, we show that the SET kinetics of all three devices depend on their feature sizes and are consequently mainly limited by the electrical charging time.

Our findings show that the proper integration of ReRAM device into CPW structure is crucial for fast kinetic measurements. Therefore, we provide suggestions for the optimal integration of ReRAM devices into CPW structures.

#### **II. EXPERIMENTAL**

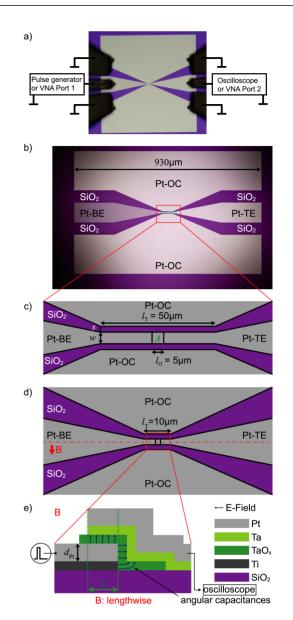

As mentioned in the introduction, CPW are used to bring the high frequency signal to the device. A CPW structure consists of three conductors: two outer and one inner conductor, which are also depicted in Fig. 1a. These lines are connected over an RF probe (in this setup: FormFactor Z-Probes) with three contacts. The two outer connectors are connected to the shield of the cables and the inner conductor to the signal line. The cables are connected to the ports of a VNA (Section II-B) or to a pulse generator and an oscilloscope (Section II-C).

## A. DEVICES

To test the influence of the device's capacitance on the SET kinetics of VCM devices, we chose Pt\TaO<sub>x</sub>\Ta-devices with three different device areas. These devices were incorporated into CPW structures (see Fig. 1). The device's areas are  $15 \times 20 \ \mu\text{m}^2$ ,  $5 \times 5 \ \mu\text{m}^2$ , and  $2 \times 2 \ \mu\text{m}^2$  and are referred to as Ta1, Ta2, and Ta3 device, respectively.

All devices were deposited on a high-resistivity Si substrate ( $\rho > 10 \text{ k}\Omega\text{cm}$ ) with a 430 nm thick SiO<sub>2</sub> layer on top. The inner conductor of the CPW structure has a width of 100  $\mu\text{m}$  and a spacing of 60  $\mu\text{m}$  to the outer conductors. The width of the inner conductor is tapered to the width of the ReRAM device at the center of the CPW structure. Both conductors are shown in Fig. 1b.

Both, the Ta1 and the Ta2 device have the following film thicknesses:  $Pt(25nm)\TaO_x(5nm)\Ta(5nm)\Pt(25nm)$ . More information about their fabrication can be found in [5], in which also the SET kinetics of the Ta1 device were presented. The SET kinetics of the Ta2 device were measured in the framework of this study (see Section II-C). The length of the CPW structure is 930  $\mu$ m. The length of the tapered area is 50  $\mu$ m (see Fig. 1c).

The Ta3 device was fabricated on a different wafer and has the following film thicknesses:  $Pt(30nm)\TaO_x(5nm)\Ta(5nm)\Pt(30nm)$ . Information on the fabrication can be found in [34] and information on the SET kinetics can be found in [19]. To reduce the losses,

FIGURE 1. a) Simplified experimental setup of the SET kinetics measurements (Section II-C) and frequency domain measurements (Section II-B). (b) Optical microscope picture of a CPW structure. The Ta1 device  $(15 \times 20 \ \mu m^2)$  is located at the center (red rectangle). The signal is transmitted through the inner Pt conductor, consisting of a bottom electrode (Pt-BE) and a top electrode (Pt-TE). The Pt outer conductors are labeled as Pt-OC. c) Zoom into the CPW structure's center (mask design), in which the Ta2 device (5  $\times$  5  $\mu m^2) was integrated. The bottom and top$ electrode overlap at the center in the Area A. Here, the VCM device's stack is realized. The length of the overlap Io, the length of the tapered area IT, the width of the inner conductor w and its spacing to the outer conductor s are indicated. The tapered area has a length of  $I_T = 50 \mu m$ . d) Zoom into the CPW structure's center (mask design), in which the Ta3 device  $(2 \times 2 \ \mu m^2)$  was integrated. The width of the tapered area has been reduced to  $I_{T}$  = 10  $\mu$ m. c) and d) are on the same length scale. e) Lengthwise cross-section of the Ta3 device showing the VCM stack (not to scale). The thickness of the Pt electrode  $d_{Pt}$  is indicated. The electrical stimuli are applied to the active Pt bottom electrode (coming from the left). The induced electrical field is indicated with blue arrows. b) and e) are adapted from [18] - Published by The Royal Society of Chemistry.

the length of the CPW structure was reduced from 930  $\mu$ m to 600  $\mu$ m and the length of the tapered area was reduced to 10  $\mu$ m (see Fig. 1d).

| TABLE 1. | Devices. |

|----------|----------|

|----------|----------|

| Identifier |                         |        | Film thicknesses                             |

|------------|-------------------------|--------|----------------------------------------------|

|            | size [µm <sup>2</sup> ] | length |                                              |

| Ta1 [5]    | $15 \times 20$          | 50 µm  | $Pt(25nm)\TaO_x(5nm)\Ta(5nm)\Pt(25nm)$       |

| Ta2 [5]    | $5 \times 5$            | 50 µm  | $Pt(25nm) TaO_x(5nm) Ta(5nm) Pt(25nm)$       |

| Ta3 [19]   | $2 \times 2$            | 10 µm  | $Pt(30nm) \ TaO_x(5nm) \ Ta(5nm) \ Pt(30nm)$ |

The cross section of the VCM stack at the devices' center is sketched in Fig. 1e). The signal is applied to the active bottom electrode at the left side. This electrode consists of a 25 nm thick Pt (light grey) and a 5 nm thick Ti adhesion layer (dark grey). The signal then propagates to the center of the structure and induces an electrical field (indicated by blue arrows) into the 5 nm thick  $TaO_x$  layer (dark green). The current response propagates finally through the top electrode towards the end of the CPW. The top electrode consist of the 5 nm Ta (light green) and 25 nm Pt (light grey). Scanning electron microscope images of this cross section are given in [35].

To calculate the capacitance of a ReRAM device, it is usually approximated as parallel plate capacitor [27]. This assumption, however, neglects the presence of angular capacitances. In [18], we found that these angular capacitances only influence the charging time of ReRAM devices smaller than 100 nm. For larger devices, the contribution of the parallel plate capacitor dominates. All induced electrical fields are illustrated in Fig. 1e as blue arrows. The surface roughness of the electrodes could also lead to a field-enhancement in the oxide. As mentioned in the introduction, the advantage of using scattering parameters is that all components of the measured circuit are considered, including their frequency dependency and geometry.

The used Pt layers have a thickness far below the skin depth of Pt. Using thicker Pt layers resulted unfortunately in short circuits at the device. All voltages indicated in this study were applied to the active Pt bottom electrode. All devices and their attributes are summarized in Table 1.

## **B. FREQUENCY DOMAIN MEASUREMENTS**

Frequency domain measurements of all three devices were conducted with a HP 8722ES vector network analyzer (VNA) measuring the scattering parameter S11 and S21 in the frequency range from 50 MHz to 40 GHz. The experimental setup is sketched in Fig. 1a. All devices were driven to the HRS prior to the frequency domain measurements. The power of the stimuli was chosen to -3 dBm, corresponding to an effective voltage of 0.32 V at the devices, which is below the SET and REST voltages of all devices. If a higher power was chosen, the device could switch to the LRS during these measurements and the subsequent analysis would no longer be valid. The VNA has been calibrated using a Cascade CSR-8 100-250 GSG calibration substrate at the RF probes (Cascade Z probes). During the calibration the losses and reflections due to cables, probes and connectors are determined. In subsequent measurements, these losses and reflections are taken into account and only

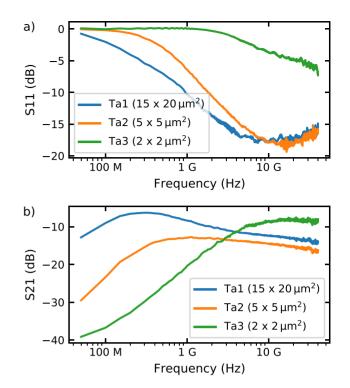

FIGURE 2. a) Forward reflection S11 and b) forward transmission S21 of all used devices. The blue line indicates the Ta1 VCM device, the orange line the Ta2 VCM device and the green line the Ta3 VCM device.

the losses and reflections occurring at the VCM device are recorded. This procedure allows us in Section IV-A to determine the rise time of the VCM devices without the influence of the setup's components. The forward reflection S11 and the forward transmission S21 are shown in Fig. 2a) and b), respectively.

As mentioned above, the stack of the VCM device constitutes a parallel plate capacitor, which scales with the device's size. Higher frequencies can transmit through this capacitor and are consequently not reflected. Therefore, S11 decreases with increasing frequencies, whereas S21 increases up to a certain point, which is explained in the next paragraph. Devices with a large area, and accordingly with a large capacitance, have a worse reflection and a better transmission up to about 3 GHz. All devices are, however, so small that no capacitive resonances occur, which were observed in another study investigating the scattering parameters of amorphous TaO<sub>x</sub> layers [33].

For all three devices, S21 reaches a maximum (e.g., the Ta1 device at about 300 MHz), after which S21 decreases again. This is due to the limitation of the CPW structure. The tapering at the center of the CPW structure decreases its bandwidth. The inner conductor's width of the Ta1 device is tapered to 20  $\mu$ m and, consequently its CPW has a better bandwidth compared to the bandwidth of the Ta2 device ( $w = 5 \mu$ m). As the Ta3 device has been optimized with regards to the length of the CPW structure (600  $\mu$ m, instead of 930  $\mu$ m) and the length of the tapered regime (10  $\mu$ m, instead of 50  $\mu$ m), it is less limited by the bandwidth of

the CPW structure, which explains the crossing of its S21 at about 3 GHz, with the S21 of the other two devices.

# C. SET KINETIC MEASUREMENTS

We have recently published the SET kinetics of the Ta1 device [5] and the ones of the Ta3 device [19]. In these publications, the experimental procedures are explained explicitly. For a better comparison of the device's area influence on the SET kinetics, we conducted a further measurement of SET kinetics on the Ta2 device. The simplified setup is sketched in Fig. 1a. We applied rectangular 10 ns pulses (rise time (10%-90%): 360 ps) with various amplitudes between -1.2 V and -3.2 V to the active Pt electrode of the device. A Picosecond PSPL 2600C pulse generator was used and the current response was measured with a Tektronix DPO73304D real-time oscilloscope (Bandwidth: 33 GHz, Sample rate: 100 GSs<sup>-1</sup>).

The measurement procedure is identical to the one presented in [5]. Prior to the application of the pulses, the Ta2 device was driven to the HRS with a voltage sweep of 2.0 V conducted at a sweep rate of 0.1 Vs<sup>-1</sup> using a Keithley 2634B source measure unit (SMU). The device's resistance was extracted at 0.5 V during this sweep after the switching event. All values for the HRS were in the range from 3 k $\Omega$  to 10 k $\Omega$ . To test the device's functionality and to bring it to a comparable initial state, it is driven to LRS with a voltage sweep of -1.2 V at the end of each cycle. This sweep was also conducted at a sweep rate of  $0.1 \text{ Vs}^{-1}$ . The device's resistance was extracted at -0.5 V prior to the switching event to ensure that the device switched to the LRS during the pulse's application. The values of the LRS were in the range from  $400 \Omega$  to  $600 \Omega$ . Each cycle was repeated at least five times to account for the variance in the SET kinetics of ReRAM devices [36].

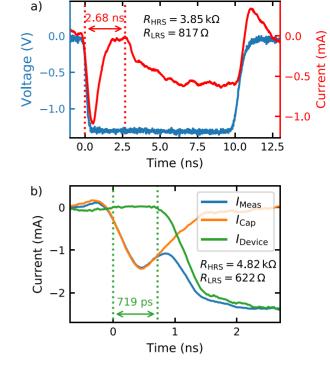

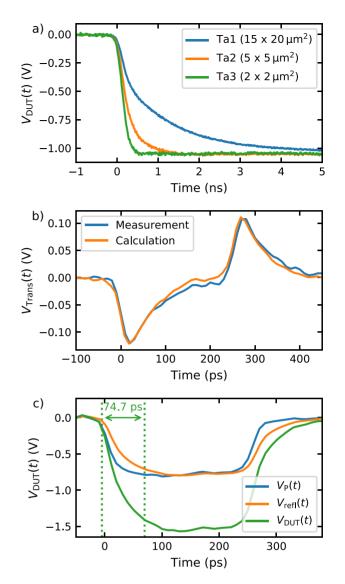

An exemplary 10 ns voltage pulse with an amplitude of -1.2 V is shown in Fig. 3a) in blue. The current response (smoothened with a Savitzky-Golay filter) is shown in red. At the beginning and at the end of the pulse, capacitive currents occur. After the first capacitive peak, the absolute current reduces to almost zero, which indicates that the Ta2 device is still in the HRS at this time. At about 2.68 ns the absolute current increases abruptly, which means that the device's resistance decreases and finally ends in the LRS. During the pulse's application, the resistance decreased from 3.85 k $\Omega$  to 817  $\Omega$ . The time from 20% of the capacitive current to the current increase (in this example 2.68 ns) corresponds to the SET time.

At higher voltage amplitudes the SET time accelerates and occurs during the capacitive charging of the device. The determination of the SET time becomes consequently more difficult, because the capacitive current  $I_{Cap}$  and the current through the device  $I_{Device}$  overlap. Their superposition corresponds to the measured current response  $I_{Meas}$ . To determine the SET time,  $I_{Cap}$  and  $I_{Device}$  need to be separated. This is done by using the same method shown in [19]. To determine the capacitive current at any pulse voltage  $V_P$ , the capacitive

**FIGURE 3.** a) 10 ns voltage pulse with an amplitude of -1.2 V (blue) and its current response (red) from the Ta2 VCM device. b) Zoom into the current response of a 10 ns voltage pulse with an amplitude of -1.8 V. The blue line is the measured current response  $I_{Meas}$ , the orange line the capacitive current  $I_{Cap}$  (calculated with eq. (1)) and the green line the current through the Ta2 VCM device  $I_{Device}$ . The left dotted line marks the beginning of the pulse and the right dotted line the SET event. All current responses were smoothened with a Savitzky-Golay filter.

current  $I_{\text{Cap}}$ , measured at -1.2 V, has been scaled to the corresponding pulse amplitude  $V_{\text{P}}$  by

$$I_{\text{Cap}}(V_{\text{P}}) = I_{\text{Cap}}(V_{\text{P}} = -1.2 \text{ V}) \cdot \frac{V_{\text{P}}}{-1.2 \text{ V}}.$$

(1)

This is illustrated in Fig. 3b), which shows in blue the beginning of  $I_{\text{Meas}}$  of a voltage pulse with an amplitude of  $V_{\rm P} = -1.8$  V. The SET event occurs within the charging of the device and, therefore, becomes difficult to detect. The capacitive current  $I_{\rm Cap}$  was then determined at  $V_{\rm P} = -1.8$  V using eq. (1) and is shown in orange in Fig. 3b). The current through the device is finally determined by subtracting  $I_{\rm Cap}$  from  $I_{\rm Meas}$  and is shown in green. In this example, the SET event occurs after about 719 ps. During the pulse's application, the device switched from 4.82 k $\Omega$  to 622  $\Omega$ . The results of the SET kinetic can be found in Fig. 6 in the results Section IV-B.

# III. DETERMINATION OF THE EFFECTIVE VOLTAGE AT THE DEVICE

As mentioned in the introduction, previous studies investigating the switching kinetics in the sub-nanosecond regime assume that the voltage at the device doubles, because the CPW structures lack a 50  $\Omega$  termination [5], [15], [19], [21], [37]. At faster timescales, however, this assumption no longer holds. As shown in Fig. 2, a significant part of the signal is reflected at the device under test (DUT), but higher frequencies can transmit through the device.

The incoming  $V_P(t)$  and the reflected signal  $V_{refl}(t)$  superimpose at port 1 of the DUT. To determine the effective voltage at the DUT  $V_{DUT}(t)$ , also the transmitted part of the signal  $V_{trans}(t)$  at port 2 needs to be considered:

$$V_{\text{DUT}}(t) = V_{\text{P}}(t) + V_{\text{refl}}(t) - V_{\text{trans}}(t).$$

(2)

A similar approach was also used in [15].

The incoming signal  $V_{\rm P}(t)$  can easily be measured with the oscilloscope and is already shown in Fig. 3a). Also  $V_{\rm trans}(t)$  can be measured. Only  $V_{\rm refl}(t)$  is unknown at this point and cannot be measured with the used setup. To determine  $V_{\rm DUT}(t)$ ,  $V_{\rm refl}(t)$  is calculated using the scattering parameters (shown in Fig. 2) for each device. The derivation is shown in the following and is illustrated with the scattering parameters of the Ta1 device.

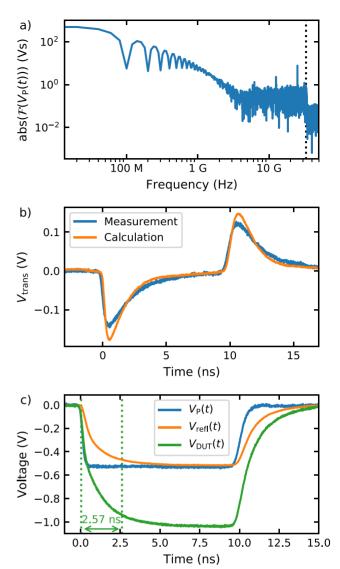

Firstly, the discrete fast Fourier transformation of  $V_P(t)$  of the applied voltage pulse is built. An exemplary Fourier transformation of a 10 ns voltage pulse (see Fig. 4c)) with an amplitude of -0.52 V is shown in Fig. 4a). The Fourier transformation of a square pulse yields a sinc function, which is clearly visible at lower frequencies. As the sampling rate of the oscilloscope is 100 GSs<sup>-1</sup>, the Fourier transformation comprises frequencies up to 50 GHz. The bandwidth of the oscilloscope, however, is limited at 33 GHz (marked as dotted line). The captured signal barely contains frequency components above this bandwidth limit.

Secondly, the Fourier transformation of  $V_{\rm P}(t)$  (referred to as  $\mathcal{F}(V_{\rm P}(t))$  is multiplied with S11 or S21, and subsequently the inverse fast Fourier transformation of this product is built. Using the forward transmission S21 results in  $V_{\rm trans}(t)$ :

$$V_{\text{trans}}(t) = \mathcal{F}^{-1}(\mathcal{F}(V_{\text{P}}(t)) \cdot S21).$$

(3)

More detailed information about this procedure can be found in the appendix Section A. The measured and calculated  $V_{\text{trans}}(t)$  are shown in Fig. 4b) in blue and orange, respectively. Both curves overlap well, which verifies our approach. The low voltage amplitude of -0.52 V was used to avoid a switching event during the application of the 10 ns pulse. Also, the influence of the cables was considered to reproduce the measurement, which is explained in the appendix Section B. Analogously, the reflected voltage can be determined by using the forward reflection S11:

$$V_{\text{refl}}(t) = \mathcal{F}^{-1}(\mathcal{F}(V_{\text{P}}(t)) \cdot \text{S11}), \tag{4}$$

and is shown in Fig. 4c) in orange along with the original signal in blue. Finally,  $V_{\text{DUT}}(t)$  is determined using eq. (2) and shown in green. At long timescales, the voltage effectively doubles as predicted, but it takes several nanoseconds to reach twice the applied pulse's voltage. The measured rise time (10%-90%) amounts to 2.57 ns and is significantly slower than the rise time of the generated pulse (360 ps). The results of the other two devices are shown in the following results Section IV-A.

**FIGURE 4.** a) Discrete fast Fourier transformation of a 10 ns voltage pulse (see Fig. 4c)) with an amplitude of -0.52 V. The dotted line marks the bandwidth of the oscilloscope at 33 GHz. b) Measured transmitted voltage of the Ta1 VCM device with the oscilloscope (blue) and calculated  $V_{trans}(t)$  (orange) using eq. (3). c) Measured original signal  $V_P(t)$  (blue), calculated reflection  $V_{refl}(t)$  of the Ta1 device using eq. (4) (orange) and effective voltage at the DUT  $V_{DUT}(t)$  (green) using eq. (2) to (4).

#### **IV. RESULTS AND DISCUSSION**

## A. RISE TIMES OF THE DIFFERENT DEVICES

Analogously to Section III, the effective electrical stimulation  $V_{\text{DUT}}(t)$  of the devices are calculated for each device using eq. (2) to (4). For this example, the 10 ns voltage pulse with an amplitude of -0.52 V from Fig. 4c) is used as  $V_{\text{P}}(t)$ . For each device, the scattering parameters of Fig. 2 are used. As the rise time of  $V_{\text{DUT}}(t)$  is most crucial for the characterization of ReRAM devices on fast timescales, the rising edges of  $V_{\text{DUT}}(t)$  are shown in Fig. 5a) for all devices.

As expected, the rise times of  $V_{\text{DUT}}(t)$  decrease significantly with smaller device sizes. From these curves the rise time (10%-90%) of each device is determined. The rise times

TABLE 2. Series resistances and rise times (10%-90%).

| Device                       | $R_{\rm S}$  | C       | $T_{\rm PG}$ | $T_{\rm Calc}$ | $T_{\rm DUT}$ |

|------------------------------|--------------|---------|--------------|----------------|---------------|

| Ta1 $(15 \times 20 \mu m^2)$ | $167 \Omega$ | 4.60 pF | 360 ps       | 2.57 ns        | 2.54 ns       |

| Ta2 $(5 \times 5 \mu m^2)$   | $460\Omega$  | 0.37 pF | 360 ps       | 730 ps         | 635 ps        |

| Ta3 $(2 \times 2 \mu m^2)$   | $147\Omega$  | 0.13 pF | 35 ps        | 74.7 ps        | 66.0 ps       |

of the pulse generator  $T_{PG}$  and the one of the DUT  $T_{DUT}$  add up quadratically to the calculated rise time  $T_{Calc}$  [38]:

$$T_{\rm Calc}^2 = T_{\rm PG}^2 + T_{\rm DUT}^2.$$

(5)

Consequently,  $T_{\text{DUT}}$  can be calculated from  $T_{\text{Calc}}$  and  $T_{\text{PG}}$ , which amounts to 360 ps for the PSPL 2600C pulse generator:

$$T_{\rm DUT}^2 = \sqrt{T_{\rm Calc}^2 - T_{\rm PG}^2}.$$

(6)

The rise time of the Ta3 device yielded faster results than  $T_{PG}$  of the PSPL 2600C. We used, therefore, a signal from a faster customized pulse generator from Sympuls Aachen (referred to as PG5) as  $V_{\rm P}(t)$ . The pulse generator provides fast rise times of about  $T_{PG} = 35$  ps. The used 250 ps voltage pulse with an amplitude of -0.79 V is shown in Fig. 5c) in blue. Again, a low amplitude was chosen to avoid a switching event during the application of the pulse. Similar to the procedure in Section III,  $V_{\text{trans}}(t)$  and  $V_{\text{refl}}(t)$ are derived using eq. (3) and (4), respectively. Again, the measured and calculated curve overlap well as shown in Fig. 5b), which indicates that our approach is also suitable at faster timescales. The influence of the cables was also considered, which is explained in the appendix Section B. The result for  $V_{refl}(t)$  is shown in Fig. 5c), along with the result for  $V_{\text{DUT}}(t)$  (derived using eq. (2)). From this curve, the rise time of the Ta3 device is determined and amounts to 74.7 ps.

The rise time of all devices are summarized in Table 2. Only the rise time of the Ta3 device had to be determined with the faster pulse generator as the other two devices have slower rise times than the maximum pulse length of the PG5 pulse generator, which is 250 ps. To take the rise times of the pulse generators into account,  $T_{\text{DUT}}$  in the last column is calculated with eq. (6).

For the following discussion, the devices capacitances C and series resistances  $R_S$  were measured and are listed in Table 2. The capacitances C were measured at a frequency of 1 MHz with a HP4284A LCR metre. The series resistances  $R_S$  were measured on through structures without integrated ReRAM device. These structures are consequently short-circuited at the center of the CPW structure.

The rise time of all devices clearly scales with the devices size, which can be explained by the reduction of the devices' capacitances. Also, the length of the tapered area  $l_T$  (see Fig. 1c)) has an impact on the rise time of the devices. Although, the Ta1 device is about 12 times larger (300  $\mu$ m<sup>2</sup>) than the Ta2 device (25  $\mu$ m<sup>2</sup>), its rise time is only 4 times faster. This is due to its larger series resistance  $R_S$ , which is 3 times larger than the one of the Ta1 device. This increase

**FIGURE 5.** a) Rising edges of  $V_{DUT}(t)$  for all three devices.  $V_{DUT}(t)$  was derived as described in Section III using eq. (2) to (4) with the 10 ns voltage pulse with an amplitude of -0.52 V (shown in Fig. 4c)), and the scattering parameters of Fig. 2. Their rise times clearly scale with the device's size. b) Measured (blue) and calculated (orange) transmission of  $V_P(t)$  through the Ta3 VCM device. c) 250 ps pulse  $V_P(t)$  with an amplitude of -0.79 V, emitted by the pulse generator PG5 (blue), calculated reflection at the Ta3 VCM device  $V_{reff}(t)$  (orange) using eq. (4), and effective voltage at the device  $V_{DUT}(t)$  (green) using eq. (2) to (4).

in resistance can be explained with the tapered width w of the CPW structure, which amounts to 20  $\mu$ m<sup>2</sup> for the Ta1 and to 5  $\mu$ m<sup>2</sup> for the Ta2 device. As  $T_{DUT}$  is proportional the product of the series resistance (3 times larger) and the capacitance (12 times smaller), this explains the observation of the 4 times faster rise times of the Ta2 device.

Although, the tapered width w of the Ta3 device is even smaller (2 µm), it has the lowest series resistance. This is mainly due to the shorter  $l_{\rm T}$ , which amounts to 10 µm for the Ta3 device and to 50 µm for the Ta1 and Ta2 device. Also, the reduction of the overall length of the CPW structure (from 930 µm to 600 µm) and the slight thicker Pt electrodes  $d_{\text{Pt}}$  (from 25 nm to 30 nm) contribute to the lower series resistance  $R_{\text{S}}$ . Both, its capacitance and lower series resistance result in an almost 10 times faster rise time on the Ta3 device compared to the Ta2 device, which demonstrates that it is crucial to minimize  $l_{\text{T}}$  to achieve fast rise times. In Section IV-C, we present more suggestions on how to integrate ReRAM device into CPW structures.

Our results on the Ta3 device show that it is possible to charge ReRAM devices within 74.7 ps. By using a pulse generator with faster rise times, even shorter rise times down to 66.0 ps are reachable. In our previous study, we have shown that faster SET times down to 50 ps are still possible, which is faster than the determined rise time. This does not contradict our previous results, because the devices can also switch during the rising edge of  $V_{\text{DUT}}(t)$ .

# **B. EXTRAPOLATION OF SET KINETICS**

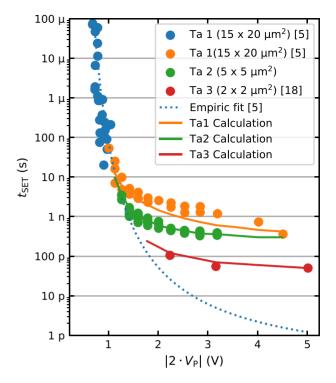

The SET kinetic results of all three devices are summarized in Fig. 6 (see Section II-C). Although, the Ta1 and the Ta2 device were both measured with the same setup (using the PSPL 2600C pulse generator), the Ta2 device achieves significantly faster SET times at the same pulse voltage, which shows that the significantly shorter rise time of the Ta2 device also reflects on the SET kinetics. The Ta3 device was measured with the PG5 pulse generator, realizing SET times down to 50 ps. Although, only three data points are visible for the Ta3 device, the variance of the SET kinetics was taken into account. Each point was derived from a large statistical set comprising at least 30 measurements cycles per measured SET time. More details on this measurement technique can be found in [19].

The blue points in Fig. 6 represent the slow time regime of the Ta3 device's SET kinetics and were measured with a Keithley 4200SCS. Physically, the SET kinetics are limited by the migration of oxygen vacancies in this slow regime [6] and are only very little influenced by the device's electrical charging or heating time. Therefore, this slow regime reflects the intrinsic speed limit of ReRAM devices. In [5], an empiric function was fitted to this regime:

$$t_{\text{SET}}(t) = t_0 \cdot \exp\left(\frac{\kappa}{|V_{\text{DUT}}(t)| - V_0}\right),\tag{7}$$

with  $\kappa = 11.2$  V and  $V_0 = 0.162$  V serving as fitting parameters. The constant  $t_0 = 1.19 \cdot 10^{-13}$  s corresponds to the attempt frequency's reciprocal value of amorphous TaO<sub>x</sub> [39]. Eq. 7 is shown as blue dotted line in Fig. 6. It would also be possible to use a more physically motivated formula, such as the law of Mott-Gurney [6], [40]. However, estimating the device's temperature requires a precise measurement of the electrical current, which is not possible with the speed-optimized setup and, therefore, a phenomenological equation was used. The impact of the temperature on the SET kinetics of TaO<sub>x</sub>-based was already investigated in [8].

The fast regime data from the Ta1 device (orange points in Fig. 6) and from the Ta2 device (green points) were measured as described in Section II-C. The SET kinetics of all three

FIGURE 6. Summary of the SET kinetics of the Ta1 VCM device (blue and orange points, data from [5]), the Ta2 VCM device (green points), and the Ta3 VCM device (red points, taken from [19]). The blue dotted line is an empiric fit to the Ta1 device's slow regime (blue points) using eq. (7). The solid lines mark the calculations described in the main text. The voltage indicated on the abscissa is twice the amplitude of the applied pulse, which corresponds to the voltage at the device at the end of the charging time.

devices are delayed compared to the estimated values using eq. (7) in the fast regime (below 10 ns), because of the rise times of  $V_{\text{DUT}}(t)$ . To prove that this delay originates from these rise times, we calculated the SET times using eq. (7) while considering the rise time of  $V_{\text{DUT}}(t)$ , which is explained in the following.

Firstly,  $V_{\text{DUT}}(t)$  was calculated for every applied pulse in Fig. 6. The first value in time of  $V_{\text{DUT}}(t)$  above 0.162 V (corresponding to  $V_0$  in eq. (7)) is referred to as  $V_1$  and used to calculate  $t_{\text{SET}}(V_1)$  with eq. (7). Subsequently, the quotient  $q_1 = \frac{t_S}{t_{SET}(V_1)}$  is built, in which  $t_S = 10$  ps corresponds to the oscilloscope's sampling time. This quotient  $q_1$  corresponds to a state variable, which describes the current state of the ReRAM devices. At values for  $q_1 < 1$ , the SET time is longer than the considered timeframe and, therefore, the device did not switch during this timeframe. At the beginning of a pulse,  $V_{DUT}(t)$  is still low and, therefore, the value of  $q_1$  is below 1. This procedure is repeated for the next values of  $V_{\text{DUT}}(t)$ . The *i*-th value above 0.162 V is referred to as  $V_i$ . The corresponding quotient  $q_i = \frac{t_{\rm S}}{t_{\rm SET}(V_i)}$  is built for each value of  $V_i$ . The values for  $q_i$  are added up until their sum reaches 1 ( $\sum_{i=1}^n q_i \ge 1$ ). The number of iterations n times  $t_S$  corresponds to the calculated SET time. This procedure is done for all three devices.

The results of the calculations are shown in Fig. 6 as solid lines and match the measured SET time well, which indicates that the SET kinetics are only limited by the electrical charging of the ReRAM devices in these experiments. A similar procedure on a slower timescale was used in one of our previous studies to derive the SET kinetics of SrTiO<sub>3</sub> devices [40].

As mentioned in the introduction, the limitation of the switching kinetics due to the electrical charging time was already demonstrated in other studies [5], [27]. Determining the rise time is required in studies in the sub-nanosecond regime to separate charging effects from physical processes within the investigated materials. The advantage of calculating  $V_{\text{DUT}}(t)$  from the scattering parameters is that it is a purely experimental approach and, consequently, no circuit-based models or calculations are required. Also, the frequency dependency of the components and deviations from bulk values are considered with the presented approach.

This result also indicates that the heating time of the presented ReRAM devices does not yet limit the SET time at 50 ps. Our FEM study on  $50 \times 50 \text{ nm}^2$ -scaled ReRAM devices suggests heating times between 120 ps and tens of picoseconds [18]. Our results confine this interval to a maximum heating time of 50 ps for filamentary TaO<sub>x</sub>-based ReRAM devices. As mentioned in the introduction, the heating time also depends on the device's geometry and, therefore, this conclusion does not hold for other devices.

For VCM devices to become market-ready, fast switching times also need be realizable in nanoscale devices. So far, the fastest measured switching time for nanoscale VCM devices amounts to 5 ns [41]. The switching kinetics were in this study, however, limited by the experimental setup and not by the charging or heating of the tested device. The smallest device investigated on a sub-nanosecond timescale has a size of  $1.2 \times 1.2 \ \mu m^2$  [17]. From our results no conclusion can be drawn on whether the heating time or the electrical charging time will be the limiting factor for devices smaller than  $2 \times 2 \ \mu m^2$ . The electrical charging time scales with device's area and, consequently, can reach values down to picoseconds for nanoscale ReRAM devices [18]. During the SET and the RESET mainly the filamentary region of the ReRAM device is heated. TEM measurements have shown for  $50 \times 50$  nm<sup>2</sup>-scaled HfO<sub>x</sub>-based devices that this region has only a diameter of 1 nm to 3 nm [42]. As this is still much smaller than the device, we do not expect any change in the heating time down to sub- $10 \times 10$  nm<sup>2</sup>-scaled ReRAM devices.

The switching of the devices to the LRS also affects the determination of  $V_{\text{DUT}}(t)$ . Lower device resistances lead to lower reflected signals  $V_{\text{refl}}(t)$  and higher transmitted signals  $V_{\text{trans}}(t)$ . According to eq. (2), this would reduce  $V_{\text{DUT}}(t)$  significantly. The amplitude of  $V_{\text{refl}}(t)$  depends on the reflection coefficient of a transmission line:

$$\Gamma = \frac{Z_{\rm L} - Z_0}{Z_{\rm L} + Z_0},\tag{8}$$

in which  $Z_0$  is the characteristic impedance of the cables and  $Z_L$  the load, which is, for simplicity, approximated as the device's resistance. At  $Z_L = 1 k\Omega$ , still most of the applied signal is reflected  $\Gamma = 0.9$ . Therefore, the presented analysis is only valid up to the point at which device resistance reaches values below 1 k $\Omega$ . This does not affect the calculation of  $t_{\text{SET}}$  in Fig. 6, because only the time until the devices start switching to the LRS is analyzed. The non-linearity of the HRS also only has a minor influence, because the device's resistance remains above 1 k $\Omega$ , up to the switching event.

## C. OPTIMIZATION SUGGESTIONS FOR CPW STRUCTURES

Our results show that to conduct fast kinetics measurement on ReRAM devices, it is crucial to properly implement the ReRAM device into a CPW structure. The rise times at the device observed in this study are slower than the ones of the employed pulse generators. The Ta1 device's rise time of  $V_{\text{DUT}}(t)$ , e.g., amounts to 2.54 ns. Reducing the size of device's VCM stack and reducing the overall and tapered length of the CPW structure (see Fig. 1) resulted in much faster rise times of  $V_{\text{DUT}}(t)$ . The Ta3 device's rise time of  $V_{\text{DUT}}(t)$  is more than one order of magnitude faster and amounts to 66.0 ps, although, an almost identical fabrication process has been used. We, therefore, decided to give some suggestions for the optimal integration of ReRAM devices into CPW structures.

# C.1. SMALLER STRUCTURES

The overall CPW structure should be short to minimize angular capacitances to the outer ground electrodes. To reduce the device's series resistance, the length of the tapered area  $l_{\rm T}$  should also be as short as possible. To reduce the VCM stack's capacitance, also the length of the overlap between the bottom and the top electrode  $l_{\rm O}$  should be short. The width of the inner conductor *w* also scales with the device's size and its capacitance. It also scales inversely with the series resistance  $R_{\rm S}$  and, therefore, its influence on the rise time is lower.

# C.2. THICKER ELECTRODES

As already stated in [15], thicker electrodes could improve the bandwidth of the CPW structures. In this paper, 30 nm and 25 nm thick Pt electrodes were used, which is far below the skin depth of Pt, which would amount to 815 nm for a frequency of 40 GHz. Using thicker Pt electrodes, however, results in short circuits at the edges of the overlapping area between the bottom and top electrode. Avoiding these edges requires a completely different device fabrication as the bottom and top electrode needed to lie in one plane. This requires the use of chemical mechanical polishing if a vertical material stack is desired.

### C.3. LATERAL ReRAM DEVICES

As the VCM stack's capacitance seems to be the main factor contributing to the rise time of  $V_{\text{DUT}}(t)$ , it would be best

to remove the vertical VCM stack. To realize this, the two electrodes could be connected with lateral devices, which would avoid their overlap. Only minor angular capacitances between the two electrodes and between the inner and outer conductors would remain [18]. Also, the tapered area, limiting the bandwidth of the CPW structure, would not be required anymore. It is, however, more difficult to fabricate lateral ReRAM devices than vertical ones. The homogeneous electric field of vertical devices, also, cannot be realized in lateral devices.

## C.4. USING A HIGH RESISTIVE SUBSTRATE

The use of a high resistive substrate is crucial for the realization of a good CPW structure. Otherwise, angular capacitances between the inner and outer conductors of the CPW structures would emerge, which would in turn limit the bandwidth of the CPW structure.

These recommendations are not only valid for the integration of ReRAM devices into CPW structures but can also be applied to other types of memories, which are controlled with electrical stimuli. An example is PCM [43], for which lateral structures are more easily realizable [44].

Electrically measuring the switching time of memory device at timescales faster than 50 ps, however, remains challenging. Pulse generators with rise times between 5 ps and 10 ps are only rarely available. Capturing a switching event from the current response at this timescale also requires an oscilloscope with a sampling rate above 100 GSs<sup>-1</sup>, which exist but are only affordable for very few scientific groups. Therefore, finding new measurement approaches is also necessary. One approach could be optically inducing THz signals into the memory device, which was already successfully demonstrated for PCM devices [45].

### **V. CONCLUSION**

In this study, we determined the electrical charging time of TaO<sub>x</sub>-based ReRAM devices, which were incorporated into CPW structures. We found that smaller feature sizes significantly reduce the charging time. A proper implementation of ReRAM devices into the CPW structure is, consequently, more crucial for fast measurements than the choice of a fast pulse generator. We, therefore, provide suggestions on how to implement ReRAM devices into CPW structures. These suggestions are also transferable to other memory technologies. Extrapolating the SET kinetics in the sub-nanosecond regime and taking the charging time into account resulted in a good agreement to the measured data. This indicates that at time scales in the sub-nanosecond regime the SET time is mainly limited by the electrical charging time and only little by the heating time of the filamentary region or by intrinsic effects, such as the migration of oxygen vacancies.

#### **APPENDIX A**

# **CONVERSION OF FREQUENCY DOMAIN TO TIME DOMAIN**

The scattering parameters shown in Fig. 2 range from 50 MHz to 40 GHz. The Fourier transformation shown in

Fig. 4a), however, ranges from 20 MHz to 50 GHz. To consider also higher frequencies the scattering parameters were extrapolated to 50 GHz by using the values at 40 GHz. This regime has only little influence on the calculations as the bandwidth of the oscilloscope is anyway limited at 33 GHz. Additional scattering parameters between 20 MHz and 50 MHz were measured with a Rhode & Schwarz ZVL3 VNA to also consider lower frequencies. To match the frequency content of both, the scattering parameters and the Fourier transformation of the signal, the scattering parameters were interpolated to the frequency content of the signal using a spline function.

## **APPENDIX B**

## **INFLUENCE OF CABLES ON TRANSMITTED VOLTAGE**

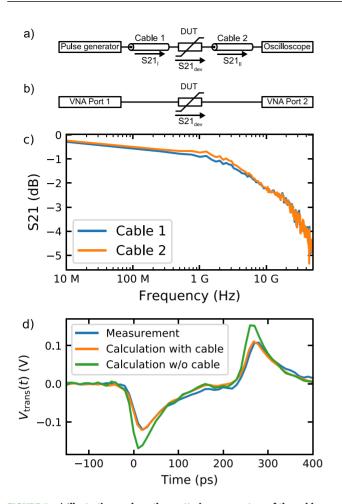

In the pulse measurements of Section II-C, a generated pulse is not only influenced by the ReRAM device, but also by the cables and other components of the experimental setup [5], [19]. All components of the setup have a bandwidth of 40 GHz (except for the oscilloscope with a bandwidth of 33 GHz). Only the insertion loss of the 1.2 m long cables is higher than 0.5 dB at 40 GHz, and, therefore, has a measurable impact on the measured current response. This is illustrated in Fig. 7a): the signal from a pulse generator is firstly slightly attenuated during the propagation through cable 1 (described by S21<sub>I</sub>). At the device, the current response is generated (described by S21<sub>dev</sub>), which is again slightly attenuated by cable 2 (described by S21<sub>II</sub>), before it is measured with the oscilloscope.

As described in Section II-B, the calibration of the VNA was conducted at the ReRAM devices and, consequently, the losses of the experimental setup (cables, adapters, RF probes, bias tee) are not included in the measured scattered parameters (see Fig. 7b)). With this method, S21<sub>dev</sub> could be measured directly. To compare the calculate transients with measured transients, the 1.2 m long cables were also considered in the derivation of  $V_{\text{trans}}(t)$  (shown in Fig. 4b) and Fig. 5b)), which is explained in the following. The forward transmission S21 of both cables are shown in Fig. 7c). The measurement was conducted from 10 MHz to 50 GHz, with an Agilent Technologies N5245A VNA.

To consider cable 1, the transmission through cable 1  $V_{\text{trans,I}}(t)$  is firstly calculated analogously to eq. (3):

$$V_{\text{trans},I}(t) = \mathcal{F}^{-1}(\mathcal{F}(V_{\rm P}(t)) \cdot \text{S21}_{\rm I}).$$

(9)

Then, the transmission through the device  $V_{\text{trans,dev}}(t)$  is calculated analogously only with  $V_{\text{trans,I}}(t)$  instead of  $V_{\rm P}(t)$ , and the forward transmission of the Ta3 device S21<sub>dev</sub> instead of S21<sub>I</sub>:

$$V_{\text{trans,dev}}(t) = \mathcal{F}^{-1} \big( \mathcal{F} \big( V_{\text{trans,I}}(t) \big) \cdot S21_{\text{dev}} \big).$$

(10)

Finally, also the transmission of  $V_{\text{trans,dev}}(t)$  through the cable 2  $V_{\text{trans,II}}(t)$  is calculated, which should correspond to the measured signal, as the signal also propagates through both cables:

$$V_{\text{trans,II}}(t) = \mathcal{F}^{-1} \big( \mathcal{F} \big( V_{\text{trans,dev}}(t) \big) \cdot S21_{\text{II}} \big).$$

(11)

**FIGURE 7.** a) Illustration on how the scattering parameters of the cables affect the measured current responses. b) Simplified sketch of the frequency domain measurements. Due to the calibration of the VNA, all losses of the cables are discarded. c) Measured forward transmission S21 of the used cables. d) Measured (blue) and calculated (orange) transmitted voltage, using eq. (9) to (11), of a 250 ps voltage pulse (emitted by the PG5 pulse generator) with an amplitude of -0.79 V, applied to the Ta3 device. The green curves shows the transmitted voltage without cables influence.

Fig. 7d) shows the measured transmitted voltage of a 250 ps pulse with an amplitude of -0.79 V (identical to Fig. 5c)), emitted with the PG5 pulse generator, which was applied to the Ta3 device. The orange line indicates the calculated transmitted voltage  $V_{\text{trans,II}}(t)$  using eq. (9) to (11). The green curve shows the result without the cables' influence. The amplitude of the capacitive peak at the beginning and at the end of the pulse is higher compared to the capacitive peaks of the measured transmitted voltage. This can be explained with the cables' influence. As shown in Fig. 7c) the cables absorb a part of the higher frequencies, which could transmit through the device and, consequently, contribute to the capacitive current. As the absorbed part of the higher frequencies is missing in the measured current response, the amplitude of the capacitive peaks is lower.

In the main text, we intend to focus on the influence of the device on the rise time without external influences, such as the cables or the pulse generator's rise time. Therefore, the cables influence is only considered to reproduce the measurement of  $V_{\text{trans}}(t)$ .

## ACKNOWLEDGMENT

The authors thank Alvaro M. Mártir and Florian Merget from the Integrated Photonics institute at the RWTH Aachen University for providing the Agilent Technologies N5245A VNA, with which the cables were characterized, and for consulting us with regards to frequency domain measurements.

### REFERENCES

- M. A. Zidan, J. P. Strachan, and W. D. Lu, "The future of electronics based on memristive systems," *Nat. Electron.*, vol. 1, pp. 22–29, Jan. 2018, doi: 10.1038/s41928-017-0006-8.

- [2] R. Waser, R. Dittmann, G. Staikov, and K. Szot, "Redox-based resistive switching memories—Nanoionic mechanisms, prospects, and challenges," *Adv. Mater.*, vol. 21, nos. 25–26, pp. 2632–2663, 2009, doi: 10.1002/adma.200900375

- [3] J. J. Yang, D. B. Strukov, and D. R. Stewart, "Memristive devices for computing," *Nat. Nanotechnol.*, vol. 8, no. 1, pp. 13–24, Dec. 2013, doi: 10.1038/nnano.2012.240.

- [4] S. Yu and P.-Y. Chen, "Emerging memory technologies: Recent trends and prospects," *IEEE Solid-State Circuits Mag.*, vol. 8, no. 2, pp. 43–56, Jun. 2016, doi: 10.1109/MSSC.2016.2546199.

- [5] U. Böttger *et al.*, "Picosecond multilevel resistive switching in tantalum oxide thin films," *Sci. Rep.*, vol. 10, no. 1, 2020, Art. no. 16391, doi: 10.1038/s41598-020-73254-2.

- [6] S. Menzel, M. Waters, A. Marchewka, U. Böttger, R. Dittmann, and R. Waser, "Origin of the ultra-nonlinear switching kinetics in oxide-based resistive switches," *Adv. Funct. Mater.*, vol. 21, no. 23, pp. 4487–4492, 2011, doi: 10.1002/adfm.201101117.

- [7] A. Marchewka *et al.*, "Nanoionic resistive switching memories: On the physical nature of the dynamic reset process," *Adv. Electron. Mater.*, vol. 2, no. 1, pp. 1–13, 2016, doi: 10.1002/aelm.201500233.

- [8] M. Witzleben *et al.*, "Investigation of the impact of high temperatures on the switching kinetics of redox-based resistive switching cells using a highspeed nanoheater," *Adv. Electron. Mater.*, vol. 3, no. 12, 2017, Art. no. 1700294, doi: 10.1002/aelm.201700294.

- [9] J. M. Goodwill, D. K. Gala, J. A. Bain, and M. Skowronski, "Switching dynamics of TaO\_x-based threshold switching devices," *J. Appl. Phys.*, vol. 123, no. 11, 2018, Art. no. 115105, doi: 10.1063/1.5020070.

- [10] E. Yalon, S. Cohen, A. Gavrilov, and D. Ritter, "Evaluation of the local temperature of conductive filaments in resistive switching materials," *Nanotechnology*, vol. 23, no. 46, 2012, Art. no. 465201, doi: 10.1088/0957-4484/23/46/465201.

- [11] E. Yalon, A. A. Sharma, M. Skowronski, J. A. Bain, D. Ritter, and I. V. Karpov, "Thermometry of filamentary RRAM devices," *IEEE Trans. Electron Devices*, vol. 62, no. 9, pp. 2972–2977, Sep. 2015, doi: 10.1109/TED.2015.2450760.

- [12] M. Uenuma, Y. Ishikawa, and Y. Uraoka, "Joule heating effect in nonpolar and bipolar resistive random access memory," *Appl. Phys. Lett.*, vol. 107, no. 7, 2015, Art. no. 073503, doi: 10.1063/1.4928661.

- [13] J. M. Goodwill *et al.*, "Spontaneous current constriction in threshold switching devices," *Nat. Commun.*, vol. 10, p. 1628, Apr. 2019, doi: 10.1038/s41467-019-09679-9.

- [14] K. Fleck et al., "Uniting gradual and abrupt set processes in resistive switching oxides," *Phys. Rev. Appl.*, vol. 6, no. 6, 2016, Art. no. 064015, doi: 10.1103/PhysRevApplied.6.064015.

- [15] A. C. Torrezan, J. P. Strachan, G. Medeiros-Ribeiro, and R. S. Williams, "Sub-nanosecond switching of a tantalum oxide memristor," *Nanotechnology*, vol. 22, no. 48, 2011, Art. no. 485203, doi: 10.1088/0957-4484/22/48/485203.

- [16] B. J. Choi *et al.*, "Electrical performance and scalability of Pt dispersed SiO<sub>2</sub> nanometallic resistance switch," *Nano Lett.*, vol. 13, no. 7, pp. 3213–3217, 2013, doi: 10.1021/nl401283q.

- [17] C. Wang et al., "Ultrafast RESET analysis of HfO<sub>x</sub>-based RRAM by sub-nanosecond pulses," Adv. Electron. Mater., vol. 3, no. 12, 2017, Art. no. 1700263, doi: 10.1002/aelm.201700263.

- [18] S. Menzel, M. von Witzleben, V. Havel, and U. Boettger, "The ultimate switching speed limit of redox-based restive switching devices," *Faraday Discuss.*, vol. 213, pp. 197–213, Aug. 2018, doi: 10.1039/C8FD00117K.

- [19] M. Witzleben, T. Hennen, A. Kindsmüller, S. Menzel, R. Waser, and U. Böttger, "Study of the SET switching event of VCM-based memories on a picosecond timescale," *J. Appl. Phys.*, vol. 127, no. 20, 2020, Art. no. 204501, doi: 10.1063/5.0003840.

- [20] B. J. Choi *et al.*, "High-speed and low-energy nitride memristors," *Adv. Funct. Mater.*, vol. 26, no. 29, pp. 5290–5296, 2016, doi: 10.1002/adfm.201600680.

- [21] A. A. Sharma, M. Noman, M. Skowronski, and J. A. Bain, "Highspeed *in-situ* pulsed thermometry in oxide RRAMs," in *Proc. Int. Symp. VLSI Technol. Syst. Appl. (VLSI-TSA)*, 2014, pp. 1–2, doi: 10.1109/VLSI-TSA.2014.6839687.

- [22] A. A. Sharma, I. V. Karpov, R. Kotlyar, J. Kwon, M. Skowronski, and J. A. Bain, "Dynamics of electroforming in binary metal oxide-based resistive switching memory," *J. Appl. Phys.*, vol. 118, no. 11, 2015, Art. no. 114903, doi: 10.1063/1.4930051.

- [23] J. Kwon *et al.*, "Transient thermometry and HRTEM analysis of filamentary resistive switches," *ACS Appl. Mater. Interfaces*, vol. 8, no. 31, pp. 20176–20184, 2016, doi: 10.1021/acsami.6b05034.

- [24] R. Ge et al., "Atomristor: Nonvolatile resistance switching in atomic sheets of transition metal dichalcogenides," *Nano Lett.*, vol. 18, no. 1, pp. 434–441, 2018, doi: 10.1021/acs.nanolett.7b04342.

- [25] N. El-Hinnawy et al., "A 7.3 THz cut-off frequency, inline, chalcogenide phase-change RF switch using an independent resistive heater for thermal actuation," in Proc. IEEE Compd. Semicond. Integr. Circuit Symp. (CSICS), 2013, pp. 1–4, doi: 10.1109/CSICS.2013.6659195.

- [26] U. Böttger et al. (2019). Picosecond Multilevel Resistive Switching in Tantalum Oxide Thin Films. [Online]. Available: https://arxiv.org/abs/2002.00700.

- [27] Y. Lu, J. H. Lee, and I.-W. Chen, "Nanofilament dynamics in resistance memory: Model and validation," ACS Nano, vol. 9, p. 7649, Jun. 2015, doi: 10.1021/acsnano.5b03032.

- [28] S. Menzel, U. Böttger, M. Wimmer, and M. Salinga, "Physics of the switching kinetics in resistive memories," *Adv. Funct. Mater.*, vol. 25, no. 40, pp. 6306–6325, 2015, doi: 10.1002/adfm.201500825.

- [29] K. Green and R. Sobolewski, "Extending scattering-parameter approach to characterization of linear time-varying microwave devices," *IEEE Trans. Microw. Theory Techn.*, vol. 48, no. 10, pp. 1725–1731, Oct. 2000, doi: 10.1109/22.873902.

- [30] A. Lewandowski, D. F. Williams, P. D. Hale, J. C. M. Wang, and A. Dienstfrey, "Covariance-based vector-network-analyzer uncertainty analysis for time- and frequency-domain measurements," *IEEE Trans. Microw. Theory Techn.*, vol. 58, no. 7, pp. 1877–1886, Jul. 2010, doi: 10.1109/TMTT.2010.2049768.

- [31] T. Zhuang, R. Inum, M. M. Rana, K. N. Shushama, and M. A. Quader, "EBG based microstrip patch antenna for brain tumor detection via scattering parameters in microwave imaging system," *Int. J. Biomed. Imag.*, vol. 2018, Feb. 2018, Art. no. 8241438, doi: 10.1155/2018/8241438. [Online]. Available: https://www.hindawi.com/journals/ijbi/2018/8241438/

- [32] G. H. Weber, H. L. D. Moura, D. R. Pipa, C. Martelli, J. C. C. D. Silva, and M. J. D. Silva, "Cable fault characterization by time-domain analysis from S-parameter measurement and sparse inverse Chirp-Z transform," *IEEE Sensors J.*, vol. 21, no. 2, pp. 1009–1016, Jan. 2021, doi: 10.1109/JSEN.2020.2990929.

- [33] J. Kim, A. Garg, E. J. Rymaszewski, and T. Lu, "High frequency response of amorphous tantalum oxide thin films," *IEEE Trans. Compon. Packag. Manuf. Technol.*, vol. 24, no. 3, pp. 526–533, Sep. 2001, doi: 10.1109/6144.946502.

- [34] A. Schoenhals *et al.*, "Critical ReRAM stack parameters controlling complementary versus bipolar resistive switching," in *Proc. IEEE Int. Memory Workshop (IMW)*, 2015, pp. 73–76, doi: 10.1109/IMW.2015.7150281.

- [35] V. Havel, "Transient processes in resistive switching memory devices at ultimate time scale down to sub-nanosecond range," Ph.D. dissertation, Dept. Mater. Elect. Eng., RWTH Aachen Univ., Aachen, Germany, 2016, doi: 10.18154/RWTH-2016-02755.

- [36] C. Bengel *et al.*, "Variability-aware modeling of filamentary oxide based bipolar resistive switching cells using spice level compact models," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 12, pp. 4618–4630, Dec. 2020, doi: 10.1109/TCSI.2020.3018502.

- [37] J. S. Brockman *et al.*, "Subnanosecond incubation times for electric-field-induced metallization of a correlated electron oxide," *Nat. Nanotechnol.*, vol. 9, pp. 453–458, Apr. 2014, doi: 10.1038/nnano.2014.71.

- [38] H. W. Johnson and M. Grahm, *High Speed Digital Design: A Handbook of Black Magic*, vol. 1. Cairo, Egypt: Olympic Technol. Group, 1993.

- [39] H. Ono and K. I. Koyanagi, "Infrared absorption peak due to Ta = O bonds in Ta<sub>2</sub>O<sub>5</sub> thin films," *Appl. Phys. Lett.*, vol. 77, no. 10, pp. 1431–1433, 2000, doi: 10.1063/1.1290494.

- [40] K. Fleck, U. Böttger, R. Waser, and S. Menzel, "Interrelation of sweep and pulse analysis of the SET process in SrTiO<sub>3</sub> resistive switching memories," *IEEE Electron Device Lett.*, vol. 35, no. 9, pp. 924–926, Sep. 2014, doi: 10.1109/LED.2014.2340016.

- [41] C. Hermes *et al.*, "Analysis of transient currents during ultra fast switching of TiO<sub>2</sub> nanocrossbar devices," *IEEE Electron Device Lett.*, vol. 32, no. 8, pp. 1116–1118, Aug. 2011, doi: 10.1109/LED.2011.2156377.

- [42] S. Privitera, G. Bersuker, S. Lombardo, C. Bongiorno, and D. Gilmer, "Conductive filament structure in HfO<sub>2</sub> resistive switching memory devices," *Solid-State Electronics*, vol. 111, pp. 161–165, Sep. 2015, doi: 10.1016/j.sse.2015.05.044.

- [43] G. W. Burr et al., "Recent progress in phase-change memory technology," *IEEE Trans. Emerg. Sel. Topics Circuits Syst.*, vol. 6, no. 2, pp. 146–162, Jun. 2016, doi: 10.1109/JETCAS.2016.2547718.

- [44] M. Salinga *et al.*, "Monatomic phase change memory," *Nat. Mater.*, vol. 17, pp. 681–685, Jun. 2018, doi: 10.1038/s41563-018-0110-9.

- [45] P. Zalden et al., "Picosecond electric-field-induced threshold switching in phase-change materials," *Phys. Rev. Lett.*, vol. 117, no. 6, 2016, Art. no. 067601, doi: 10.1103/PhysRevLett.117.067601.