Received 13 August 2020; revised 15 October 2020; accepted 17 October 2020. Date of publication 5 November 2020; date of current version 8 December 2020.

The review of this article was arranged by Editor B. Iñiguez.

Digital Object Identifier 10.1109/JEDS.2020.3036135

# THz Characterization and Modeling of SiGe HBTs: Review (Invited)

SEBASTIEN FREGONESE<sup>® 1</sup>, MARINA DENG<sup>® 1</sup> (Member, IEEE), MARCO CABBIA<sup>® 1</sup> (Member, IEEE), CHANDAN YADAV<sup>® 1,2</sup> (Member, IEEE), MAGALI DE MATOS<sup>® 1</sup>, AND THOMAS ZIMMER<sup>® 1</sup> (Senior Member, IEEE)

1 IMS Laboratory, University of Bordeaux, 33400 Talence, France

2 Department of Electronics and Communication Engineering, National Institute of Technology Calicut, Kozhikode 673601, India

CORRESPONDING AUTHOR: S. FREGONESE (e-mail: sebastien.fregonese@ims-bordeaux.fr)

This work was supported in part by the French Nouvelle-Aquitaine Authorities through the FAST project and in part by the EU under Project Taranto 737454, and in part by IPCEI (Important Projects of Common European Interest) under Grant NANO2022.

**ABSTRACT** This article presents a state-of-art review of on-wafer S-parameter characterization of THz silicon transistors for compact modelling purpose. After, a brief review of calibration/de-embedding techniques, the paper focuses on the on-wafer calibration techniques and especially on the design and dimensions of lines built on advanced silicon technologies. Other information such as the pad geometry, the ground plane and the floorplan of the devices under test are also compared. The influence of RF probe geometry on the coupling with the substrate and adjacent structures is also considered to evaluate the accuracy of the measurement, especially using EM simulation methodology. Finally, the importance of measuring above 110 GHz is demonstrated for SiGe HBT parameter extraction. The validation of the compact model is confirmed thanks to an EM-SPICE co-simulation that integrates the whole calibration cum de-embedding procedure.

**INDEX TERMS** THz characterization, mmW, S-parameters, on-wafer, HBT, BiCMOS, HICUM, compact modelling, de-embedding, TRL calibration.

#### I. INTRODUCTION

The recent review of THz silicon-based circuits presented by Wuppertal group [1] evidently shows an unprecedented panel of circuits operating in the lower end of the THz spectrum.

III-V technologies have been leading in the THz field for many years, but these technologies are difficult to use on a large scale for mass applications owing to issues like reliability, scaling, integration etc. In fact, mass applications require economical single-chip solutions that obviate the need for complex microelectronic assembly used to connect the III-V chips to the system. Therefore, Hillger et al. [1] pointed out that advanced CMOS and SiGe BiCMOS technologies could "fulfill this role, at least in the lower end of the THz spectrum". The arguments put forward by the authors are as follows [1]: the Si/SiGe technologies concurrently offers economies of scale, smallform-factors, and unprecedented integration capability at the highest industry

standards. At the lower end of the THz spectrum, the potential mass applications are microsystems for sensing and active imaging components, but also future 6G wireless systems.

To enable engineers to design such Si-THz circuits, unique expertise and knowledge is required. In the development of complex THz circuits, advanced, precise and readable computer-aided-design (CAD) tools are an essential requirement. At THz range, a desirable feature in the CAD tools is to consist of both accurate electromagnetic EM tools and compact models. Moreover, in setting up these tools, have to be fed with accurate measurements in the THz range. In order to obtain accurate measurement data in THz range, techniques must be developed to verify and analyze the measurements with numerical simulation results. Characterization in the THz range is usually performed by small signal S-parameter measurements.

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

In this work, we present a review of S-parameter measurement and simulation methods for Si transistors over the last 15 years. Indeed, many research works have been performed on this topic, but only limited reviews of high frequency measurement above 110 GHz have been presented. In this field, Rumiantsev and Doerner [2] elaborated a detailed review of probe technology; Derrier *et al.* presented a comprehensive analysis of calibration and de-embedding techniques for the on-wafer measurement below 110 GHz in 2012 [3]; Chevalier *et al.* published a review on THz HBT and compact modelling [4]. This article complements the documents cited above by an analysis of the methodology of on-Silicon wafer measurements above 110 GHz.

After a comprehensive overview of the calibration and de-embedding techniques in Section II of this article, in Section III we focus on the design of test structures for the on-wafer calibration with special consideration of line geometry, ground-plane and floorplan. Section IV describes the importance of the measurement setup, especially the influence of the RF probes. Finally, Section V presents a methodology for comparing measurements at very high frequencies, which is essential above 70 GHz for transistor compact modelling.

#### **II. CALIBRATION AND DE-EMBEDDING METHODS**

The characterization of transistors requires precise calibration methods. Below 50 GHz, Short-Open-Load-Thru (SOLT) calibration on aluminum oxide substrate, followed by an open-short de-embedding, is an efficient method widely used in industry. Above 50 GHz, more precautions are required, especially with regard to the de-embedding method, and using sophisticated method such as pad-open/transistor-short/transistor-open method leads to more accurate result [3]. For the off-wafer calibration, methods such as LRRM are also used [5].

Above 70 GHz, the characterization of transistors on Siwafers becomes more challenging [3]. Only very few demonstrations of transistor measurements at higher frequencies have been performed on silicon substrates [3], [5], [6]-[9]. Voinigescu et al. [7] have demonstrated measurements up to 325 GHz of an advanced SiGe HBT (hetero-junction bipolar transistor) and have shown results of parameters S<sub>21</sub> and H<sub>21</sub> along with the maximum available gain MAG. In [7], the calibration has been carried out with impedance standard substrate (ISS) and the calibration methods used were LRRM (line-reflect-reflect-match) and TRL (Thru, Reflect, Line). In [8], Deng et al. have presented an exhaustive set of S-parameter measurements up to 325 GHz on HBTs from an advanced 55nm BiCMOS technology using calibration approach (LRRM on ISS) similar to [7]. Unfortunately, measurements in [7], [8] were not benchmarked with EM simulation. The report presented by Williams et al. in [5] clearly shows the limitations of off-wafer calibration methods by comparing them with the on-wafer TRL method. To compare the off-wafer calibration with the on-wafer TRL [5], the off-wafer calibration need to be followed by additional

de-embedding methods such as open-short, pad-short-open or thru, line, short-open etc.

In [5], measurement results from a silicon-oninsulator (SOI) technology were presented where the characteristics of the line were characterized up to 500 GHz, while the transistor measurement was performed up to 110 GHz.

While previous studies were based on experimental demonstration, Fregonese *et al.* [10] took a different approach, using both experimental data and EM simulation to compare off-wafer SOLT and TRL calibration with onwafer-calibration. The EM-based approach includes a model for the RF probes and models of the off-wafer and the onwafer calibration kit and on-wafer devices-under-test (DUT). The study concludes that with increasing frequency the use of the off-wafer calibration methods lead to higher discrepancies in measurement with respect to the expected results. This discrepancy is more correlated to the fact that off-wafer calibration is performed in a different electrostatic environment between measurement and calibration than with the calibration method itself.

To sum-up the most important points:

- SOLT and LRRM are widely used methods that can be employed from low frequencies up to 50 GHz or more, while TRL calibration at very low frequencies is less convenient due to the line size.

- ii) The SOLT and LRRM methods require input parameters to be defined for each probe topology (note that LRRM does not require input parameter for the load). These parameters are often not well described at very high frequencies.

- iii) Off-wafer calibration uses a reference plane that is defined at the probe tip in an EM environment which is altered during the measurement phase. This is a major drawback resulting in inaccuracies above 110 GHz.

- iv) The on-wafer method has the same EM environment during both the calibration and measurement process.

- v) The TRL method is an efficient method for on-wafer calibration and high frequency measurement because it uses a reference plane in an homogeneous medium (middle of a line) and requires only one set of lines with known lengths and a reflect on the wafer. Note that an impedance correction step using an on-wafer load is required.

Hence, recent studies agree that on-wafer TRL is the most accurate calibration method for high frequency measurement (>70 GHz), but this requires engineering efforts to develop an accurate on-wafer design kit. This calibration must be followed by an impedance correction procedure that can be tricky.

#### **III. DESIGN OF TEST STRUCTURES**

The validity of the TRL procedure and its accuracy is strongly dependent on the choice of the line topology, i.e., microstrip line (MLIN) or coplanar waveguide (CPW)), and on its geometry. Other than line, two other important aspects

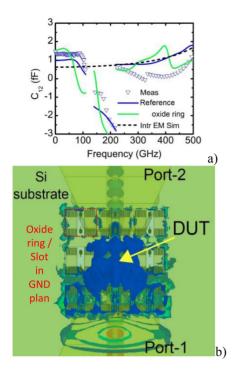

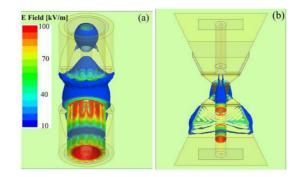

FIGURE 1. Port 1 to port 2 capacitance with and without SiO<sub>2</sub> ring (a) and HFSS-simulated electric field contour (back view) for DUT transistor-open at 500 GHz with aligned neighbors and oxide ring (b).

in on-wafer calibration kit design are the design of RF pad and the ground plane.

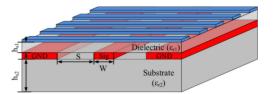

# A. GROUND PLANE

Williams et al. [11] recommend to use a continuous ground plane: "We further suppressed multimode propagation by using a continuous ground plane under the entire calibration kit to eliminate the possibility of slot modes between the grounds of adjacent calibration structures and other resonances." This point was the weakness of the layout presented in [12] and that was clearly identified using EM simulation. The impact of a non-continuous ground plane is shown in the Fig. 1. From Fig. 1a, the effect of the oxide ring is visible. The addition of the oxide ring disturbs the trends of the port capacitances generating a strong ripple on C<sub>12</sub>, to a lesser extent on C<sub>11</sub> and C<sub>22</sub>. This is due to the fact that, when the dielectric ring is present (Fig. 1b), the E-field is heavily affected. The intensity of the field increases around the DUT and below the excitation probe and we can plainly see the field densifying around every adjacent structure. This reinforces our motivation in the use of the boundless ground plane.

#### **B. CONVENTIONAL LINES**

The design of lines for TRL calibration is still a non-standardized procedure as very different geometries are presented in the literature [9], [13], [14], while the corresponding frequency band and the technology are quite similar with respect to the back-end of the line (BEOL). An overview

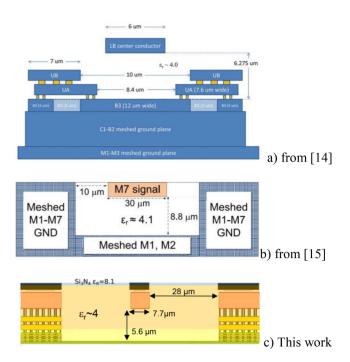

FIGURE 2. Cross-sectional view of different lines used in on-wafer calibration kit: a) line fabricated in 45nm CMOS SOI process[13], b) CPWG line fabricated in a IHP Bipolar process[14], c) microstrip line fabricated in BiCMOS 55nm STMicroelectronics process (copyright to be done).

of different topologies is given in the Table 1 and cross-sections of some lines are shown in Fig. 2. While [5], [13] uses a line comparable to a CPWG structure due to design rule constraints in a SOI CMOS technology, [14] uses CPWG lines with a larger width to minimize the losses within a BiCMOS technology. However, in [11], the authors explain that "the small cross section of the microstrip transmission lines helps to reduce radiation and multiple modes of propagation". In [11], the authors use a microstrip line of 22µm width on a BCB dielectric with very low dielectric losses, a process developed for THz application on III-V technologies.

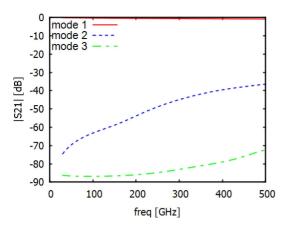

In our approach a MLIN with a width of about 7  $\mu m$  fabricated in a BiCMOS technology is used. This line represents a good trade-off between reduced losses and single mode propagation. Indeed, this line allows the suppression of high order modes at least up to 500 GHz as demonstrated in Fig. 3.

A second important issue in the design of calibration kits is the length of the thru and the distance from pad to pad. The TRL calibration method is in fact an 8-term algorithm that does not correct for crosstalk. If this can be partially corrected by de-embedding, the easiest option to minimize the crosstalk influence is to increase the length between pads together with a reduction of parasitic propagation modes. Williams *et al.* uses upto 400µm in [11] together with microstrip line topology.

Also, Williams *et al.* [15] have proposed crosstalk correction using a 16-term error calibration model, but this is not widely used because of its complexity in terms of need of

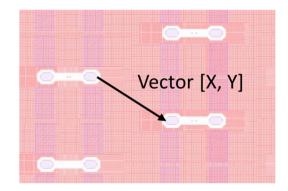

TABLE 1. Review of calibration lines realized for the on-wafer calibration structures to use with TRL method, \* Inter-probe distance is taken from the middle of the pad port 1 to the middle of the pad port 2.<sup>2</sup> Distance is taken from pad (external part) structure 1 to pad structure 2 and is defined thanks to a vector.

|                                            | Comments                                   | Line<br>topology                                   | Thru length /<br>Inter-probe<br>distance [µm] | Line width /<br>dielectric height /<br>horizontal<br>distance to GND<br>[µm] | Pad size<br>: length<br>x width<br>[µm²] | Distance<br>between two<br>adjacent<br>structures—<br>vector [x,y], <sup>2</sup> | Comments                                                                                                              |

|--------------------------------------------|--------------------------------------------|----------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Williams2013<br>[12] NIST                  | InP / BCB<br>Meas up to 1<br>THz           | MLIN                                               | 400μm / NAN                                   | 22 / 8 µm                                                                    | 44 x 22                                  | 150µm                                                                            | BCB dielectric is<br>used up to 750<br>GHz (no high order<br>modes)<br>Gold pad (IIIV<br>techno.)                     |

| Williams2014<br>[5][14]NIST                | Silicon<br>MOSFET<br>Meas up to 110<br>GHz | CPWG<br>(metal<br>density<br>constraint<br>in PDK) | 300µm / ~350<br>µm                            | 6 / 6.275 / (see<br>Fig. 2a) μm                                              | 40 x 30                                  | undisclosed                                                                      | Constraints in line design due to PDK $Z_{\text{C}}=75$ ohm corrected with off wafer load Gold platting of pads       |

| Galatro[15]<br>TU DELFT                    | Silicon<br>BiCMOS<br>Up to 325 GHz<br>IHP  | CPWG                                               | 100 μm / 150 μm                               | 30 / 8.8 / 10 µm                                                             | 50x30                                    | undisclosed                                                                      |                                                                                                                       |

| Galatro[7]<br>TU DELFT                     | Silicon<br>BiCMOS<br>Up to 325 GHz         | CPWG<br>Inverted-<br>CPW                           | 100 µm / 150 µm                               | 30/8/15 μm<br>5/1.07/10 μm                                                   | 50x30                                    | [160, 0] µm<br>(structure are in<br>line)                                        | CPW and Innovative line topology                                                                                      |

| Fregonese IFX<br>[10], [11]<br>U. Bordeaux | BiCMOS<br>Up to 500 GHz<br>Infineon        | MLIN                                               | 50 μm / 90 μm                                 | 4.9 / 3.9 /28 μm                                                             | 38x38                                    | [24, 0] µm<br>(structure are in<br>line)                                         | Too dense floorplan => coupling to adjacent structure - Probable crosstalk                                            |

| Yadav Brava<br>U. Bordeaux<br>[18]         | BiCMOS<br>Up to 500 GHz<br>STMicro         | MLIN                                               | 36.8 / 91 µm                                  | 5.74 / 5.8 / 12.5μm                                                          | 43x27                                    | [123, 0] µm<br>(structure are in<br>line)                                        | Slot in GND plane generates inaccurate results-coupling to adjacent structure is not significant — Probable crosstalk |

| This work U. Bordeaux                      | BiCMOS<br>Up to 500 GHz<br>STMicro         | MLIN                                               | 65µm / 140 µm                                 | 7.7 / 5.6 / 28µm                                                             | 40x25                                    | [207, 133] µm<br>(structure are<br>staggered)                                    | Probable non-<br>negligible crosstalk<br>above 400 GHz                                                                |

Table I: review of calibration lines realized for the on-wafer calibration structures to use with TRL method, \* Inter-probe distance is taken from the middle of the pad port 1 to the middle of the pad port 2.<sup>2</sup> Distance is taken from pad (external part) structure 1 to pad structure 2 and is defined thanks to a vector.

various test structures and its implementation. Nevertheless a crosstalk correction is possible with a simplified approach described in [11] in which the authors mentioned that "having only three such standards, we employed the crosstalk corrections described in [15] and implemented in [16] under the additional assumption of symmetric probes and access lines". The same authors give also the following recommendation to limit probe to probe coupling in the case of the use of CPW lines but that from our point of view can be extended to the MLIN case: minimize probe pitch; keep the distance between crosstalk standards close to the device size.

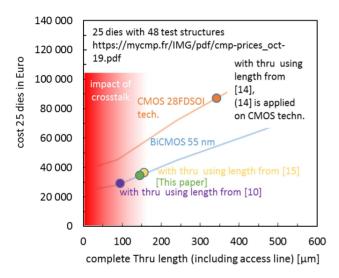

If length extension is a simple option, this procedure is therefore costly, especially for advanced silicon technologies. Therefore, a tradeoff between cost and accuracies need to be found. To illustrate these remarks, we have calculated the cost of 25 dies with 48 test structures. The 48 is a usual

number of test structures necessary for compact modelling purpose. The area required depends on the length of the thru (see Fig. 4). The study is done using two advanced technologies from STMicroelectronics, the 28nm FDSOI and the BiCMOS 55nm technologies. In the same figure, we have indicated the length of the thru chosen in the different on-wafer calibration kits from [13], [14] assuming that we have made a similar choice than these groups to choose the length of the thru. This Fig. 4 undoubtedly demonstrates the enormous cost difference that can be made with this choice: on the one hand a very expensive test structure, on the other hand potentially erroneous measurements.

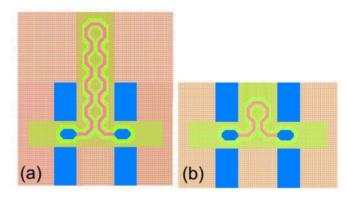

# C. INNOVATIVE APPROACH FOR CALIBRATION LINES

If the on-wafer TRL approach has many advantages and is an accurate method, there are still some measurement

FIGURE 3. Simulation of the first 3 modes of the micro-strip line from Fig. 2c (without pad) highlighting that only the first mode is propagated within the line (Length=583 $\mu$ m).

FIGURE 4. Scenario of estimation of costs versus complete thru length based on the floorplan and on the cost of two advanced STMicroelectronics technologies the 28nm FDSOI CMOS technology and the BiCMOS 55nm technology. The figures highlight the importance in term of cost of the choice of the thru length and access.

difficulties: The on-wafer TRL calibration demonstrated in [9], [13], [14] brings the reference level to the top metal while the transistor itself is at the M1/contact interface. Hence, calibration is usually followed by a de-embedding procedure that requires the measurement of several other test structures. The addition of matrix manipulation together with supplementary measurement amplifies the measurement error, complicates and degrades the overall measurement quality of the transistor especially when probe contact difficulties come into play.

To circumvent or reduce this problem, Galatro *et al.* [6] have proposed the design of low loss lines at the M1 level to define the reference plane exactly at the transistor level. The proposed calibration/de-embedding kit contains capacitively loaded inverted CPW lines, allowing to reduce the losses generated by the conductive (i.e., silicon) substrate, by confining the propagating field in the low-loss dielectric layers (see

**FIGURE 5.** Simplified sketch of a CL-ICPW section. The transmission line consists of a CPW realized on the lossy substrate, which is characterized by a dielectric constant  $\varepsilon_{r2}$  and is capacitively loaded by means of floating bars separated by a dielectric layer, with dielectric constant  $\varepsilon_{r1}$ . Extracted from [6] (copyright to be done).

FIGURE 6. 2D schematic of the meander line used for the on-wafer TRL calibration for the frequency range from 20 to 400 GHz [18], [19].

Fig. 5). The structures were specifically designed for (sub-) mm-wave measurements as a supplement to conventional de-embedding kits used at lower frequencies. The results using this calibration/de-embedding kit, realized in a 130-nm BiCMOS technology, were experimentally obtained in the WR-03 waveguide band.

In the same sense, but with a simpler approach, we attempt to set the reference plane very close to the transistor with a microstrip line at M3 level (0.5µm above M1), while its ground plane is at M1 level. Unfortunately, the small thickness of the M3 line greatly increases the resistive losses and reduces the calibration accuracy.

A second difficulty of the TRL, which is addressed in part V, is the accuracy of the horizontal probe positioning. In fact, the TRL calibration requires the measurement of different line lengths, which forces a horizontal probe displacement that can induce probe error positioning. Moreover, in case of an industrial environment with automatic probe station, manual intervention is required at this stage or it can be replaced by an expensive additional horizontal motorized support installed on the probe holder. To overcome this difficulty, we propose to create a structure based on a repeating pattern to generate lines of different lengths having a scalable behavior with the number of patterns [18], [19] (see Fig. 6).

#### D. FLOORPLAN

When building the calibration kit, the positioning of the individual test structures on the chip (floorplan) should not be

FIGURE 7. Magnitude of the electric field of two identical thru at two positions simulated at 85 GHz extracted from [20], (copyright to be done).

neglected. Williams et 2013 mention: "These three standards were placed 150  $\mu$ m apart to reduce the direct coupling between the calibration standards, and allow the crosstalk between the probes and the access lines to be characterized and at least partially removed from the measurements, as explained in [6]." Also Schmückle *et al.* [20] have evidently underlined the influence of the neighboring structure on the measurement accuracy. To prove this, identical thrus were positioned on a GaAs substrate with different neighbors and different distances. The measurement results evidently demonstrate the influence of the neighbors and the same is confirmed by the EM simulation. Fig. 7 from [20] illustrates the electric field distribution of two similar structures at two different positions on the wafer. Two conclusions can be drawn from this:

i) "the fields are not at all confined to the intended structure but show significant spatial extension involving the neighboring line elements"; ii) "the intensity of the stray fields increases with frequency and that more and more elements are involved in the resulting behavior".

While Schmückle's study [20] highlights an unexpected deviation in the measurement of the magnitude of S21 of a line of about 0.3 dB at 70 GHz on a GaAs substrate, we observed an even higher unexpected deviation in the order of about 1 dB on a line at 450 GHz on a BiCMOS technology. Our observation is consistent with the second point of their analysis, which states that the stray fields increase with frequency. To ensure that this behavior was correlated with neighboring structures, we further investigated this effect through EM-simulation. The EM simulation is performed by reproducing the measurement environment and placing the calibration structures with and without neighbors and including probes. The application of the TRL calibration in both cases, measurement and EM-simulation, plainly reveals the influence of the neighbors with the occurrence of a "oscillating" trend with increasing frequency [9] (see

This effect is enhanced when a very dense floorplan is designed. Measurements shown in Fig. 8 are from our first

FIGURE 8. S<sub>21</sub> parameter measurements of a line up to 500 GHz showing unexpected behavior: impact of adjacent structures confirmed with EM simulation.

FIGURE 9. Typical floorplan using staggered structure[X,Y]=[207,133]  $\mu$ m.

mmW on-wafer calibration kit, where the test-structures were placed very close together. The neighborhood effect does not occur in the new version of the calibration kit where the distance between structures is increased and the structures are staggered (see Fig. 9).

# IV. MODELS OF PROBES IN THE WHOLE FREQUENCY BAND

The design of the mmW calibration kit should not be done without considering the probe used. Of course, the pitch needs to be considered, but other factors such as the probe-to-substrate and probe-to-neighbors coupling or probe-to-probe coupling are generally correlated to the probe topology and geometry. A complete description of probe topology and technology is given in [2].

Andrei *et al.* [21] have highlighted the probe-to-substrate coupling by measuring the same device with and without dicing the die at the pad periphery. Their conclusion obviously discloses that the Cascade's Infinity probes used in the study are affected by the probe-to-substrate coupling despite the microstrip line technology that provides a ground plane between the probe and the wafer.

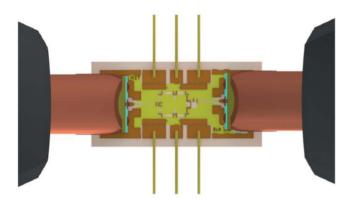

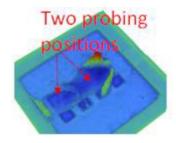

In previous work [9], [10], we have elaborated a methodology for building virtual measurements by introducing the probe into the EM environment and reproducing the complete

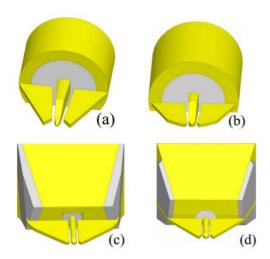

FIGURE 10. EM probe models based on Picoprobe GGB (a) 1 GHz -110 GHz, (b) WR5, (c) WR3 and d) WR2.2. In all models, white=coaxial insulator, gray=solder, yellow=metal.

FIGURE 11. Simulation scenario including RF probes (Infinity Cascade), DC probe, bond-wire and III-V circuit of a digital phase shifter working from 220 to 325 GHz. Extracted from [22], see also [23].

calibration and de-embedding procedure. A similar approach was published in parallel in [22], [23] applied to III-V technologies. In addition, this study is applied to the circuit scale and also covers a large part of the measurement environment with DC probe needle and bond wire (see Fig. 11).

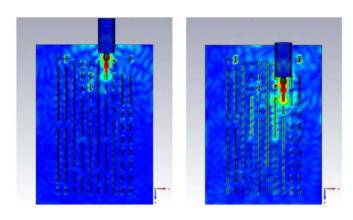

Later it is proposed [24] to study the side effect induced by "the probe construction together with neighboring elements, for the most common planar transmission lines, coplanar waveguides, and thin-film microstrip lines".

To complete this study, [25] developed some accurate EM models of each Picoprobe GGB probe used for measurements from DC to 110 GHz and in the WR5.1, WR3.4 and WR2.2 bands. These models are based on a detailed analysis with microscopic imaging of the probes at various angles. The analysis of the pictures of these four probes undoubtedly revealed that the geometry of the probes was really different and consequently the way the probes confined the EM field towards the pads was also different. The Fig. 13 draw attention about the distribution of the electric field of the WR5.1 probe and the WR3.4 probe for the same test structure in the simulation at 220GHz. This figure

FIGURE 12. Simulation of Electric Field highlighting stray field on a transistor open at 220 GHz using two Picoprobe from GGB at the edge of their frequency band: a) WR5.1: 140-220 GHz, b WR3.4: 220-325 GHz.

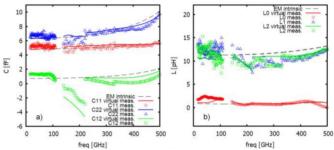

FIGURE 13. (a) Capacitances of the transistor-open; b) Inductors of the transistor-short. In both the panel, measurement (symbols), virtual measurement (EM with probe and calibration represented by solid line) and EM intrinsic simulation (dashed line) are shown up to 500 GHz using an on-wafer TRL calibration kit (thru of 65 $\mu$ m) fabricated using B55 technology- STMicroelectronics.

unmistakably emphasizes the behavior of the probe, which differs dramatically in terms of coupling.

In addition, when measuring the  $C_{12}$  capacitance of a transistor open, we noticed specific signatures and discontinuities that correspond to probe's own frequency band. This was noticed in three generations of on-wafer calibrations kits with different pads, different BEOL and different floorplans[9], [12], [19]. One of this typical signatures is the occurrence of a sudden decrease of the C<sub>12</sub> capacitance calculated from ( $imag(Y_{12}/\omega)$ ) from 70 GHz and up to 220 GHz, as described in Fig. 14. Thanks to the EM simulation including the probe and the application of the complete TRL calibration procedure with EM data, it is possible to reproduce this unexpected behavior, as shown in Fig. 14. In the same way, this effect can be completely suppressed by changing the probe geometry used below 220 GHz by using the front-end geometry of the WR3.4 or WR2.2 probe. Therefore, the two calibration kits developed in [9], [17] and the one from this article are obviously incompatible with the 220 GHz Picoprobe from GGB probe, and the calibration kits deserve to be redesigned taking into account the geometry of this probe. Another solution would be to use better designed probes.

Only limited effort has been made in this direction, with the exception of the University of Virginia, which together with Dominion has proposed new probe architectures based

FIGURE 14. Phase versus frequency (-0.185 Deg/GHz) for the 0.5ps Line extracted from [31].

on silicon MEMS technology and designed for measurements up to 1.1 THz [26]–[29].

#### **V. CONTROL OF EXPERIMENTAL PARAMETERS**

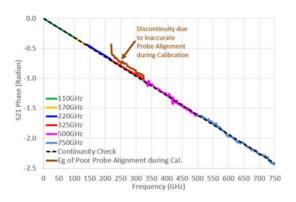

Previous studies have confirmed that probes can be the source of discontinuities from band-to-band. But also the control of experimental setup parameters is of great importance to avoid discontinuities and to obtain realistic measurement results.

Therefore, an important task for these settings is to control the power over a wide frequency range, especially for SiGe HBTs, which can become nonlinear even at a power level of -30 dBm. An exhaustive and well-controlled procedure has been proposed in [30].

Another challenge is the control of DC contacts for each frequency band, which can lead to problems especially on aluminum pads. Of course the probes have to be purchased according to the material of the pads. Another possibility proposed in [13] is to add gold plating on aluminum pads to obtain reliable contacts. In [31], a method is proposed to monitor the DC contact by adding a DC sense probe. In case of DC contact problems, it is sometimes necessary to move the probe to clean the tips or simply make another contact. Unfortunately, moving the probe can cause inaccuracies in the RF calibration. This was investigated in [9], [31] and [32]. The authors from [31] recommend to plot the inductance and the phase (see Fig. 15) of a verification line to assess the accuracy of the calibration. The Fig. 14 shows an example of inaccurate probe alignment during ISS calibration resulting in inaccurate measurement. In the same sense, we proceed to a voluntary inaccurate probe position on the line of our on-wafer calibration kit. This positioning error was measured exactly by optical interferometry (see Fig. 15). This probe position error of about 15µm on the pad leads to an inaccuracy of about 0.4 fF when measuring a transistor open in the WR2.2 band and of about 3° when measuring the phase on a line at 500 GHz. These results were confirmed by the EM simulation.

# **VI. TRANSISTOR CHARACTERIZATION AND MODELLING**

Above 110 GHz, only a few modelling demonstrations have been carried out so far [6], [7]. For example,

FIGURE 15. 3D imaging of the signal pad used in the WR-2 band. Images are taken by optical interferometry. Images show two probe contacts at different positions on the pad where Pad size is  $38x38\mu m^2$ .

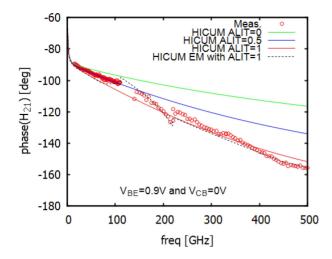

Galatro *et al.* [6] show a comparison of the HICUM model [33], [34] with measurements. Despite precautions regarding the measurement procedure, i.e., calibration and de-embedding, a certain discrepancy between the two data appears which is in the order of about 5dB and about 30-40  $^{\circ}$  on the phase of S<sub>12</sub>. Other parameters show a fairly good agreement considering the frequency range. Unfortunately, the model does not cover the entire frequency range. In [4], the model is shown on the whole frequency range and many bias points up to 325 GHz.

Knowing that most of the transistor parameters are extracted with DC measurement and S-parameter measurement below 40 GHz, even for a technology with a  $f_T/f_{MAX}$  above 300 GHz, the accuracy of the model above 110 GHz is unfortunately not guaranteed.

Some parameters still cannot be extracted at low frequency, such as the NQS parameters of the HICUM model: for example, the phase of the H<sub>21</sub> is very sensitive to the ALIT parameter, which models the delay between the intrinsic base-emitter voltage and the voltage controlled current source. Imagine the following modeling scenario: -i) measurement results are available up to 40 GHz, only. In this case, setting the ALIT parameter equal to zero gives a sufficient accuracy; -ii) measurement results are available up to 110 GHz; now, ALIT=0.5 gives the best fit in this frequency range, while ALIT=1 is too large and overestimates the phase of H<sub>21</sub>. -iii) Measuring at higher frequencies gives a better result, but stopping the measurement at 220 GHz without EM simulation will cause difficulties for compact modelling. First, the measurement shows an unexpected trend compared to the HICUM model. A first guess would lead us to change the parameters to match this unexpected trend or even to modify the HICUM equation. Therefore, the method proposed in [35], which reproduces a virtual measurement by EM modelling including probes and calibration/de-embedding test structures associated with the compact model is a very efficient method to verify the fit of the compact model and the measurements. This is shown in the Fig. 16, where this method is able to reproduce unexpected trends and discontinuities. Finally, we can conclude that very high frequency measurements are mandatory for precise compact model parameter extraction, but cannot be used without a detailed control of the measurements thanks to the above described advanced modelling method.

FIGURE 16. Phase of  $H_{21}$  parameters for peak  $f_{7}$  operating points, Measurement (symbols), virtual measurement (EM-HICUM with probe with calibration-de-embedding shown in dashed line) and HICUM simulation for different set of parameters ALIT (solid line). Data is calibrated using an on-wafer calibration followed bya de-embedding technique. The calibration kit structures and DUT are fabricated using B55 technology-STMicroelectronics.

If the ALIT parameter is an example, other parameters in the HICUM model such as ALQF, which models the vertical NQS effect on the diffusion charge, or the fcrbi parameter, which is required for lateral NQS modelling or substrate related parameters [36], require measurements above 110 GHz.

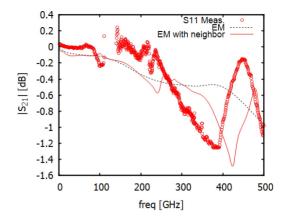

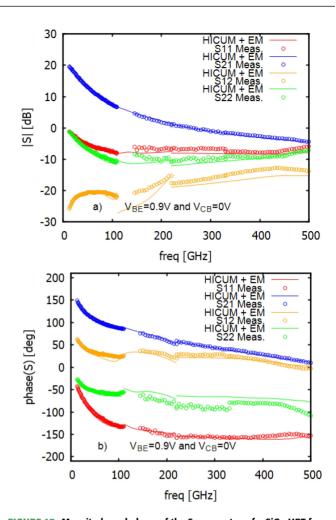

After adjusting all NQS parameters, the HICUM model, on which we have grafted a substrate model [36], gives quite good results, as shown in Fig. 17.

# VII. CONCLUSION

On-wafer characterization of silicon THz transistor is a new challenge that have some peculiarities compared to III-V THz transistors. If the research community in these two fields agree to use on-wafer calibration followed by de-embedding, the implementation of the calibration kit will differ mainly due to the BEOL, which is very different for advanced silicon technologies compared to III-V technologies. On the one hand; III-V technologies have gold plated pads that eliminate many uncertainties associated with the probe contact. On the other hand, their less complex BEOL requires the use of CPW lines, which must be carefully designed to avoid high order modes. Williams et al. [11] use a modified BEOL with BCB, which is not common in III-V technologies. In silicon technologies, the complex BEOL technology with 7 or more metallization layers allows the design of optimized microstrip lines, but the troubles are caused by the probe contact on aluminum pads. Despite the great lead of the III-V community on THz transistor, most transistor measurements are performed below 110 GHz [37]-[39].

We believe that the gap between silicon and III-V technology for THz application will be greatly reduced thanks to the versatility of silicon technology and to the massive efforts of the community on the various topics such as the

FIGURE 17. Magnitude and phase of the S-parametersof a SiGe HBT for  $V_{BE}=0.9$  V  $V_{CB}=0$ V.In the figures, measurement result is shown by symbols, , EM-HICUM with probe with calibration-de-embedding are shown by solid lines. Both actual measurement and virtual measurement data are calibrated using an on-wafer calibration followed by a de-embedding technique where structures are fabricated using B55 technology- STMicroelectronics.

technology process, the characterization and the modelling and the circuit design. Hence, in this review, we aimed to give a feedback on the experience of the research community in characterizing silicon technologies in the THz domain, especially with respect to the design of the calibration kit, the influence of measurement environment, the influence of the probe and the evaluation of the measurement accuracy. A correct design of the lines, the ground plane, the floorplan and a systematic EM simulation procedure including the probes for the measurement analysis are the key points for the THz measurement and transistor modelling.

#### **ACKNOWLEDGMENT**

The authors would like to thank STMicroelectronics for supplying the Silicon wafer.

## **REFERENCES**

P. Hillger, J. Grzyb, R. Jain, and U. R. Pfeiffer, "Terahertz imaging and sensing applications with silicon-based technologies," *IEEE Trans. THz. Sci. Technol.*, vol. 9, no. 1, pp. 1–19, Jan. 2019, doi: 10.1109/TTHZ.2018.2884852.

- [2] A. Rumiantsev and R. Doerner, "RF probe technology: History and selected topics," *IEEE Microw. Mag.*, vol. 14, no. 7, pp. 46–58, Nov./Dec. 2013, doi: 10.1109/MMM.2013.2280241.

- [3] N. Derrier, A. Rumiantsev, and D. Celi, "State-of-the-art and future perspectives in calibration and de-embedding techniques for characterization of advanced SiGe HBTs featuring sub-THz fT/fMAX," in *Proc. IEEE Bipolar/BiCMOS Circuits Technol. Meeting (BCTM)*, Portland, OR, USA, Sep. 2012, pp. 1–8, doi: 10.1109/BCTM.2012.6352639.

- [4] P. Chevalier et al., "Si/SiGe:C and InP/GaAsSb heterojunction bipolar transistors for THz applications," Proc. IEEE, vol. 105, no. 6, pp. 1035–1050, Jun. 2017, doi: 10.1109/JPROC.2017.2669087.

- [5] D. F. Williams et al., "Calibrations for millimeter-wave silicon transistor characterization," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 3, pp. 658–668, Mar. 2014, doi: 10.1109/TMTT.2014.2300839.

- [6] L. Galatro, A. Pawlak, M. Schroter, and M. Spirito, "Capacitively loaded inverted CPWs for distributed TRL-based de-embedding at (Sub) mm-Waves," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 12, pp. 4914–4924, Dec. 2017, doi: 10.1109/TMTT.2017.2727498.

- [7] S. P. Voinigescu et al., "Characterization and modeling of an SiGe HBT technology for transceiver applications in the 100–300-GHz range," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 12, pp. 4024–4034, Dec. 2012, doi: 10.1109/TMTT.2012.2224368.

- [8] M. Deng et al., "Small-signal characterization and modelling of 55 nm SiGe BiCMOS HBT up to 325 GHz," Solid-State Electron., vol. 129, pp. 150–156, Mar. 2017. [Online]. Available: http://www.sciencedirect.com/science/article/pii/S0038110116302805

- [9] S. Fregonese et al., "On-wafer characterization of silicon transistors up to 500 GHz and analysis of measurement discontinuities between the frequency bands," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 7, pp. 3332–3341, Jul. 2018, doi: 10.1109/TMTT.2018.2832067.

- [10] S. Fregonese et al., "Comparison of on-wafer TRL calibration to ISS SOLT calibration with open-short de-embedding up to 500 GHz," IEEE Trans. THz. Sci. Technol., vol. 9, no. 1, pp. 89–97, Jan. 2019, doi: 10.1109/TTHZ.2018.2884612.

- [11] D. F. Williams, A. C. Young, and M. Urteaga, "A prescription for sub-millimeter-wave transistor characterization," *IEEE Trans. THz. Sci. Technol.*, vol. 3, no. 4, pp. 433–439, Jul. 2013, doi: 10.1109/TTHZ.2013.2255332.

- [12] C. Yadav et al., "Analysis of test structure design induced variation in on Si on-wafer TRL calibration in sub-THz," in Proc. IEEE 32nd Int. Conf. Microelectron. Test Struct. (ICMTS), Kita-Kyushu City, Japan, Mar. 2019, pp. 132–136, doi: 10.1109/ICMTS.2019.8730962.

- [13] D. F. Williams et al., "Calibration-kit design for millimeter-wave silicon integrated circuits," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 7, pp. 2685–2694, Jul. 2013, doi: 10.1109/TMTT.2013.2265685.

- [14] L. Galatro and M. Spirito, "Millimeter-wave on-wafer TRL calibration employing 3-D EM simulation-based characteristic impedance extraction," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 4, pp. 1315–1323, Apr. 2017, doi: 10.1109/TMTT.2016.2609413.

- [15] D. F. Williams, F. J. Schmückle, R. Doerner, G. N. Phung, U. Arz, and W. Heinrich, "Crosstalk corrections for coplanar-waveguide scatteringparameter calibrations," *IEEE Trans. Microw. Theory Tech.*, vol. 62, no. 8, pp. 1748–1761, Aug. 2014, doi: 10.1109/TMTT.2014.2331623.

- [16] D. F. Williams and U. Arz. Statistical VNA Calibration Algorithm. Accessed: Jun. 2019. [Online]. Available: https://www.nist.gov/services-resources/software/wafer-calibration-software

- [17] C. Yadav et al., "Importance and requirement of frequency band specific RF probes EM models in sub-THz and THz measurements up to 500 GHz," *IEEE Trans. THz. Sci. Technol.*, vol. 10, no. 5, pp. 558–563, Sep. 2020.

- [18] M. Potéreau et al., "Meander type transmission line design for onwafer TRL calibration," in Proc. 46th Eur. Microw. Conf. (EuMC), London, U.K., 2016, pp. 381–384, doi: 10.1109/EuMC.2016.7824358.

- [19] M. Cabbia et al., "Meander-type transmission line design for on-wafer TRL calibration up to 330 GHz," in Proc. 50th Eur. Microw. Conf., Utrecht, The Netherlands, 2021, p. 4.

- [20] F. J. Schmückle, T. Probst, U. Arz, G. N. Phung, R. Doerner, and W. Heinrich, "Mutual interference in calibration line configurations," in *Proc. 89th ARFTG Microw. Meas. Conf. (ARFTG)*, Honololu, HI, USA, Jun. 2017, pp. 1–4, doi: 10.1109/ARFTG.2017.8000823.

- [21] C. Andrei, D. Gloria, F. Danneville, P. Scheer, and G. Dambrine, "Coupling on-wafer measurement errors and their impact on calibration and de-embedding up to 110 GHz for CMOS millimeter wave characterizations," in *Proc. IEEE Int. Conf. Microelectron. Test Struct.*, Tokyo, Japan, Mar. 2007, pp. 253–256, doi: 10.1109/ICMTS.2007.374494.

- [22] D. Müller. (2018). RF Probe-Induced On-Wafer Measurement Errors in the Millimeter-Wave Frequency Range. doi: 10.5445/KSP/1000084392.

- [23] D. Müller et al., "Electromagnetic field simulation of MMICs including RF probe tips," in Proc. 47th Eur. Microw. Conf. (EuMC), Nuremberg, Germany, Oct. 2017, pp. 900–903, doi: 10.23919/EuMC.2017.8230990.

- [24] G. N. Phung et al., "Influence of microwave probes on calibrated onwafer measurements," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 5, pp. 1892–1900, May 2019, doi: 10.1109/TMTT.2019.2903400.

- [25] C. Yadav, M. Deng, M. De Matos, S. Fregonese, and T. Zimmer, "Importance of complete characterization setup on on-wafer TRL calibration in sub-THz range," in *Proc. IEEE Int. Conf. Microelectron. Test Struct. (ICMTS)*, Austin, TX, USA, Mar. 2018, pp. 197–201, doi: 10.1109/ICMTS.2018.8383798.

- [26] T. J. Reck et al., "Micromachined probes for submillimeter-wave on-wafer measurements—Part I: Mechanical design and characterization," IEEE Trans. THz. Sci. Technol., vol. 1, no. 2, pp. 349–356, Nov. 2011, doi: 10.1109/TTHZ.2011.2165013.

- [27] T. J. Reck et al., "Micromachined on-wafer probes," in Proc. IEEE MTT-S Int. Microw. Symp., Anaheim, CA, USA, May 2010, pp. 65–68, doi: 10.1109/MWSYM.2010.5517580.

- [28] L. Chen et al., "Terahertz micromachined on-wafer probes: Repeatability and reliability," IEEE Trans. Microw. Theory Techn., vol. 60, no. 9, pp. 2894–2902, Sep. 2012, doi: 10.1109/TMTT.2012.2205016.

- [29] T. J. Reck et al., "Micromachined probes for submillimeter-wave on-wafer measurements—Part II: RF design and characterization," IEEE Trans. THz. Sci. Technol., vol. 1, no. 2, pp. 357–363, Nov. 2011, doi: 10.1109/TTHZ.2011.2165020.

- [30] Improving Wafer-Level S-Parameters Measurement Accuracy And Stability With Probe-Tip Power Calibration Up To 110 GHz for 5G Applications, Semicond. Eng., Silicon Valley, CA, USA, Mar. 9, 2020. [Online]. Available: https://semiengineering.com/improving-wafer-level-s-parameters-measurement-accuracy-and-stability-with-probetip-power-calibration-up-to-110-ghz-for-5g-applications

- [31] C. Beng Sia, "Minimizing discontinuities in wafer-level sub-THz measurements up to 750 GHz for device modelling applications," in *Proc. 89th ARFTG Microw. Meas. Conf. (ARFTG)*, Honololu, HI, USA, Jun. 2017, pp. 1–4, doi: 10.1109/ARFTG.2017.8000843.

- [32] R. Sakamaki and M. Horibe, "Uncertainty analysis method including influence of probe alignment on on-wafer calibration process," *IEEE Trans. Instrum. Meas.*, vol. 68, no. 6, pp. 1748–1755, Jun. 2019, doi: 10.1109/TIM.2019.2907733.

- [33] M. Schröter and A. Chakravorty, Compact Hierarchical Bipolar Transistor Modeling With HiCUM. Singapore: World Sci., 2010.

- [34] M. Schroter, A. Pawlak, P. Sakalas, J. Krause, and T. Nardmann, "SiGeC and InP HBT compact modeling for mm-Wave and THz applications," in *Proc. IEEE Comp. Semicond. Integr. Circuit Symp. (CSICS)*, Waikoloa, HI, USA, Oct. 2011, pp. 1–4, doi: 10.1109/CSICS.2011.6062466.

- [35] S. Fregonese et al., "Analysis of high-frequency measurement of transistors along with electromagnetic and SPICE cosimulation," IEEE Trans Electron Devices, vol. 67, no. 11, pp. 4770–4776, Nov. 2020.

- [36] B. Saha, S. Frégonese, S. R. Panda, A. Chakravorty, D. Céli, and T. Zimmer, "Collector-substrate modeling of SiGe HBTs up to THz range," in *Proc. IEEE BiCMOS Comp. Semicond. Integr. Circuits Technol. Symp. (BCICTS)*, Nashville, TN, USA, Nov. 2019, pp. 1–4, doi: 10.1109/BCICTS45179.2019.8972745.

- [37] C. R. Bolognesi, R. Flückiger, M. Alexandrova, W. Quan, R. Lövblom, and O. Ostinelli, "InP/GaAsSb DHBTs for THz applications and improved extraction of their cutoff frequencies," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, Dec. 2016, pp. 1–4, doi: 10.1109/IEDM.2016.7838506.

- [38] V. Teppati, S. Tirelli, R. Lövblom, R. Flückiger, M. Alexandrova, and C. R. Bolognesi, "Accuracy of microwave transistor T and MAX extractions," *IEEE Trans. Electron Devices*, vol. 61, no. 4, pp. 984–990, Apr. 2014, doi: 10.1109/TED.2014.2306573.

- [39] N. Kashio, T. Hoshi, K. Kurishima, M. Ida, and H. Matsuzaki, "Improvement of high-frequency characteristics of InGaAsSb-base double heterojunction bipolar transistors by inserting a highly doped GaAsSb base contact layer," *IEEE Electron Device Lett.*, vol. 36, no. 7, pp. 657–659, Jul. 2015, doi: 10.1109/LED.2015.2429142.