Received 29 April 2020; revised 31 May 2020; accepted 5 June 2020. Date of publication 10 June 2020; date of current version 24 June 2020.

The review of this paper was arranged by Editor K. Shenai.

Digital Object Identifier 10.1109/JEDS.2020.3001211

# SiC Planar MOSFETs With Built-In Reverse MOS-Channel Diode for Enhanced Performance

XINTIAN ZHOU<sup>®</sup>, HAO GONG, YUNPENG JIA, DONGQING HU, YU WU (Member, IEEE), TIAN XIA<sup>®</sup>, HAOYANG PANG, AND YUANFU ZHAO (Senior Member, IEEE)

Faculty of Information Technology, Beijing University of Technology, Beijing 100124, China

CORRESPONDING AUTHOR: Y. JIA (e-mail: jyp@bjut.edu.cn)

This work was supported in part by the China Postdoctoral Science Foundation under Grant 2018M641134, in part by the Beijing Postdoctoral Research Foundation under Grant ZZ2019-64, in part by the Beijing Chaoyang District Postdoctoral Research Foundation under Grant 2019ZZ-36, and in part by the Civil Aerospace Preresearch Plan of China under Project B0202.

**ABSTRACT** In this paper, the SiC planar MOSFET with built-in reverse MOS-channel diode (SiC MCD-MOSFET) is investigated utilizing TCAD simulation tools. When the device is working as a freewheeling diode, the operation of the parasitic body diode is suppressed effectively due to the lower threshold voltage of the MCD. Therefore, the bipolar degradation issue can be completely solved. In addition, the SiC MCD-MOSFET is featuring superior dynamic characteristics. The input capacitance ( $C_{ISS}$ ), reverse transfer capacitance ( $C_{RSS}$ ), gate charge ( $Q_G$ ) and gate-to-drain charge ( $Q_{GD}$ ) are reduced by a factor of  $\sim$ 2,  $\sim$ 7,  $\sim$ 2 and  $\sim$ 10, respectively, as compared to the conventional SiC MOSFET (SiC C-MOSFET). Combined with the slightly increased on-resistance ( $R_{ON}$ ), tremendously enhanced figures of merit ( $R_{ON} \times Q_G$  and  $R_{ON} \times Q_{GD}$  are decreased by a factor of 1.8 and 9, respectively) are obtained in the SiC MCD-MOSFET. The outstanding performance and easy-to-implement feature make the SiC MCD-MOSFET more attractive for further power electronic applications.

**INDEX TERMS** SiC planar MOSFETs, bipolar degradation, dynamic performance.

## I. INTRODUCTION

SiC MOSFETs are generally treated as a replacement of Si counterparts in power electronic applications, owing to the superior material properties [1]-[5]. In many applications, the source-drain diode inherently provided by the MOSFET, also referred to as the body diode, is always utilized as a freewheeling diode, such as in a voltage source inverter [6]. This is attractive since it enables the engineer to cut the number of power semiconductor components to half, thus significantly reducing the cost of the system. However, the parasitic body diode of a conventional SiC MOSFET (SiC C-MOSFET) is not suitable for use because of the following two reasons: one is the large knee voltage (nearly 3 V) due to the wide band gap property of SiC material [7], which would lead to a high conduction loss; the other is the bipolar degradation issue induced by the electron-hole recombination [8]. The basal plane dislocation (BPD) could gain energy from this recombination process. Consequently, the stacking faults grow into the N-drift region, resulting in a higher on-resistance  $(R_{\rm ON}).$

Some approaches have been reported to handle this problem so far. An external SiC Schottky barrier diode (SBD) anti-paralleled with the SiC MOSFET is a popular method [9], whereas the resulting introduction of extra capacitance and inductance is unexpected [10]. A SiC MOSFET with embedded SBD has been put forward to solve this issue [11], [12], which shows a better performance in terms of the switching characteristics and the bipolar degradation suppression. The DioMOS structure [13], [14], which enables the forward and reverse current to flow through the same accumulation channel, is another effective design. Lately, it comes to our attention that a Si-based power MOSFET with built-in channel diode has been proposed to enhance the reverse recovery performance of the device [15]. The channel diode is turned on in competition with the body diode under reverse operation mode, thus reducing the injected minority carriers in the drift region. However, the cut-in voltage of the body diode in Si devices is still small  $(\sim 0.7 \text{ V})$ , so it is difficult to prevent it from operating thoroughly, which may weaken the advantage of this design

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

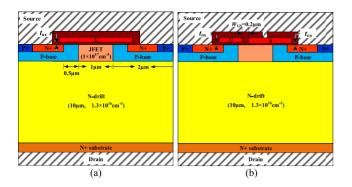

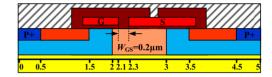

FIGURE 1. Schematic cross-sectional views of (a) SiC C-MOSFET and (b) SiC MCD-MOSFET.

concept. By comparison, this top cell design is more attractive in SiC devices, since the built-in voltage of PN junction is raised to about 3 V due to the wider band gap of SiC material. Our previous work has demonstrated its feasibility based on a double-trench MOSFET structure proposed by Rohm [16]. However, the process implementation of this device architecture is too complex and demanding, making it difficult to be introduced into the market.

In this paper, the easily achievable SiC planar MOSFET with built-in reverse MOS-channel diode (SiC MCD-MOSFET) is studied systematically by TCAD simulations. The dummy gate oxide thickness is thinned for a required turn-on voltage, so as to confine the injection level of the minority carriers from the body diode. As a result, the bipolar degradation can be removed completely when the device acts as a freewheeling diode. The superior performance with remarkably improved figures of merit can be obtained with respect to the SiC MCD-MOSFET, showing a significant advantage in high-frequency applications when compared to the SiC C-MOSFET. What's more, the influence of parameters variation on the device characteristics is addressed as well.

### II. DEVICE STRUCTURES AND SIMULATION RESULTS

The schematic cross sections of the SiC C-MOSFET and MCD-MOSFET are illustrated in Fig. 1, respectively. The doping and dimension parameters used in the simulation refer to the design rules and already published research [17]. The thickness of the epitaxial layer is 10 µm with a doping concentration of 1.3×10<sup>16</sup> cm<sup>-3</sup> to achieve a breakdown voltage (BV) higher than 1200 V. The gate oxide thickness  $(t_{ox})$  is 50 nm and the channel mobility is assumed to be 50 cm<sup>2</sup>/V-s [18]. The doping concentration of the P-base and JFET area are both  $1 \times 10^{17}$  cm<sup>-3</sup>. For the SiC MCD-MOSFET, the dummy gate oxide thickness ( $t_{co}$ ) is thinner than  $t_{ox}$  to modulate the knee voltage of the MCD, and the distance between the true and dummy gate  $(W_{GS})$  is set to be 0.2 µm. The SiC MCD-MOSFET can be realized in a similar fashion as the conventional one, with an additional lithography process to form a stepped oxide profile by dry etch after the oxidation procedure. The true gate and dummy

TABLE 1. Parameters of the impact ionization coefficients of 4H-SiC.

|             | Perpendicular<br>to c-axis <sup>[19]</sup> | Parallel to c-axis <sup>[20]</sup> | Unit             |

|-------------|--------------------------------------------|------------------------------------|------------------|

| $a_{\rm e}$ | 2.1×10 <sup>7</sup>                        | $8.19 \times 10^9$                 | cm <sup>-1</sup> |

| $b_{ m e}$  | $1.7 \times 10^{7}$                        | $3.94 \times 10^{7}$               | V/cm             |

| $a_{ m h}$  | $2.96 \times 10^{7}$                       | $4.48 \times 10^{6}$               | cm <sup>-1</sup> |

| $b_{ m h}$  | $1.6 \times 10^7$                          | $1.28 \times 10^{7}$               | V/cm             |

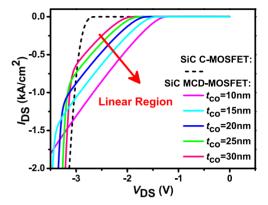

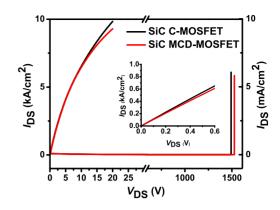

FIGURE 2. Conduction characteristics in the third quadrant for the studied MOSFETs.

gate can be separated incidentally in the subsequent etch process after the polysilicon deposition. Likewise, the contact via hole between the source metal and the dummy gate can be formed along with the formation of the source contact hole.

To simulate SiC-based power devices, the following models are essential: anisotropic avalanche model based on the Chynoweth law [19], [20] used only for breakdown voltage simulations, incomplete ionization of dopants in SiC material, Shockley-Read-Hall (SRH) recombination with doping dependency, bandgap narrowing [21]–[23]. The parameters of the electron- and hole-impact ionization coefficients of 4H-SiC used in the simulations are given in Table 1. The interface charge traps at SiC-SiO<sub>2</sub> interface are not considered in the simulations. It should also be noted that this simulation work is aimed at comparing the performance of two different structures on the same terms instead of revealing their features as physical devices. So the default model parameters for 4H-SiC material given by the simulation tool are employed, and the results are obtained based on rather idealistic assumptions.

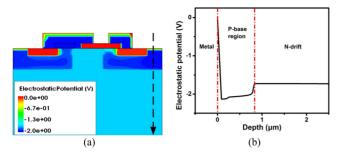

The third quadrant characteristics of SiC C-MOSFET and MCD-MOSFET at  $V_{\rm GS} = -5$  V are plotted in Fig. 2, respectively. A steep on-state curve in the SiC C-MOSFET can be observed, indicating the turn-on of the parasitic body diode, whose knee voltage and voltage drop at  $I_{SD} = 100 \text{ A/cm}^2$ (V<sub>F</sub>) are 2.7 V and 2.82 V, respectively. While in the SiC MCD-MOSFET, although the dummy gate and the P-base region both short-circuit the source metal, the potential of the P-base region is still lower than that of the dummy gate, as shown in Fig. 3 (a). Fig. 3 (b) presents the vertical potential profile along the dotted line. The perpendicular flow of the majority carriers (the holes) results in the abrupt

620 **VOLUME 8, 2020**

FIGURE 3. (a) Potential distribution of SiC MCD-MOSFET with  $t_{\rm co}$  of 15 nm at  $I_{\rm SD}=100~{\rm A/cm^2}$ . (b) Potential profile along the dotted line.

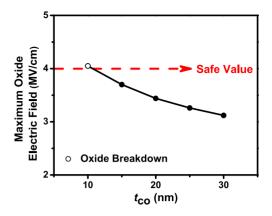

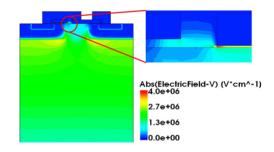

decrease of the potential near the surface of the semiconductor, thus bringing down the potential of the P-base region. Consequently, a strong inversion layer beneath the oxide can be formed to create a path for the current flowing from the source to the drain. In Fig. 2, a linear region can be found in regard to the SiC MCD-MOSFET with an  $I_{SD}$  lower than 500 A/cm<sup>2</sup>, demonstrating the unipolar conduction of the MCD. The characteristic curves with certain values of  $t_{\rm co}$  begin to steepen when  $I_{\rm SD}$  is higher than 500 A/cm<sup>2</sup>. It means that the body diode starts to conduct the reverse current together with the MCD, due to that the on-state voltage drop has already reached the threshold voltage of the body diode at this time. Moreover, it is shown that  $t_{co}$ plays a crucial role in adjusting the cut-in voltage of MCD. A lower cut-in voltage can be obtained with a smaller  $t_{co}$ , thus further restraining the operation of the body diode when carrying high-density current. However, this can also aggravate the electric field crowding in off-state. As shown in Fig. 4, when  $t_{co} = 10$  nm, the maximum electric field in the oxide has already exceeded the safety limit 4 MV/cm at  $V_{\rm DS} = 1200~{\rm V}$  [24]. The corresponding electric field distribution plot can be found in Fig. 5, and the electric field crowing around the bottom corner of the dummy gate is clearly visible. It means that the oxide breakdown occurs, which may influence the long-term reliability of the device. As a result, unless otherwise specified,  $t_{co} = 15$  nm is employed in the following discussions, and thus  $V_{\rm F} = 1.75 \, {\rm V}$ is obtained in the SiC MCD-MOSFET. The smaller  $V_{\rm F}$ with comparison to that of the SiC C-MOSFET enables the device to save much more conduction losses when serving as a freewheeling diode.

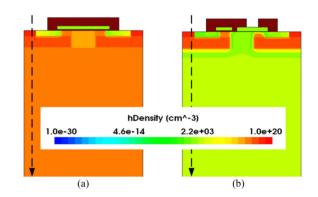

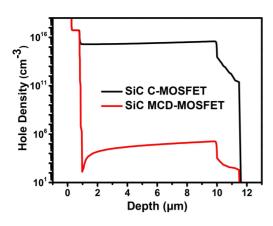

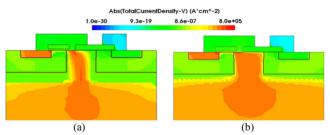

Fig. 6 shows the hole density distributions at  $I_{\rm SD}=100~{\rm A/cm^2}$  for the SiC C-MOSFET and MCD-MOSFET, respectively. The profiles of minority carrier concentration along the dotted lines are exhibited in Fig. 7. The extremely low hole density in the N-drift region of the SiC MCD-MOSFET indicates that the turn-on of the body diode is restrained effectively. Therefore, the bipolar degradation can be completely eliminated when the device is acting as a freewheeling diode.

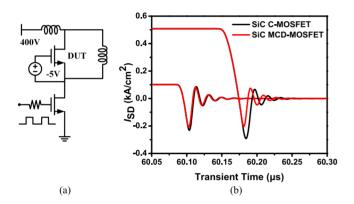

The reverse recovery characteristics of the studied MOSFETs are tested using the circuit in Fig. 8(a), and the reverse recovery performance at different turn-off current is

FIGURE 4. Maximum oxide field versus  $t_{CO}$  at  $V_{DS} = 1200 \text{ V}$ .

FIGURE 5. Electric field distribution at  $t_{\rm co}=10$  nm and  $V_{\rm DS}=1200$  V. The field strength around the left corner of the dummy gate is beyond 4 MV/cm.

FIGURE 6. Hole density distributions at  $I_{SD} = 100 \text{ A/cm}^2$  for the (a) SiC C-MOSFET and (b) SiC MCD-MOSFET, respectively.

reported in Fig. 8(b) for both cases, respectively. The reverse recovery charges  $Q_{\rm RR}$  are nearly the same with respect to the SiC C-MOSFET and MCD-MOSFET at a turn-off current of 100 A/cm<sup>2</sup>, although the bipolar conduction takes place in the former while unipolar conduction in the latter. This is because the injection level of the minority carriers is still not high enough at this moment, which is clearly visible from the hole density profile of the SiC C-MOSFET in Fig. 7. The hole concentration does not even reach the background doping of the N-drift region at  $I_{\rm SD}=100$  A/cm<sup>2</sup>. It seems that the  $Q_{\rm RR}$  could not be reduced so much in the SiC MCD-MOSFET under that circumstance. However, the advantage of this MCD design becomes appreciable at

FIGURE 7. Hole density profiles along the depth of the studied MOSFETs at  $I_{SD} = 100 \text{ A/cm}^2$ .

FIGURE 8. (a) Test circuit used for simulating the reverse recovery characteristics. (b) Reverse recovery performance at different turn-off current.

a high turn-off current, such as at  $I_{\rm SD}=500~{\rm A/cm^2}$  in Fig. 8(b). The epitaxial layer of the SiC C-MOSFET now is flooded with plasma, and more charges need to be removed when it is turned off, resulting in a higher  $Q_{\rm RR}$  [25]. While in the case of SiC MCD-MOSFET, its  $Q_{\rm RR}$  is not changed with that turn-off current, which is a unique feature for the unipolar devices. By calculation, the  $Q_{\rm RR}$  of 3.28  $\mu$ C/cm<sup>2</sup> is obtained in the SiC C-MOSFET, while 1.56  $\mu$ C/cm<sup>2</sup> in the SiC MCD-MOSFET at a turn-off current of 500 A/cm<sup>2</sup>, showing nearly a 50% improvement.

The performance of the SiC MCD-MOSFET working as a switching device is also studied. The on-state and breakdown characteristics for the SiC C-MOSFET and MCD-MOSFET are depicted in Fig. 9, respectively. The current carrying capability in the saturation regime is weakened in the SiC MCD-MOSFET because of the decreased channel density, which would help improving the short-circuit ruggedness of the devices [26]. However, no serious degradation can be observed in the linear region with comparison of the conventional one, as shown in the inner plot of Fig. 9. Consequently, the  $R_{\rm ON}$  of the SiC C-MOSFET at  $I_{\rm DS}=100~{\rm A/cm^2}$  is 0.89 m $\Omega\cdot{\rm cm^2}$  while 0.96 m $\Omega\cdot{\rm cm^2}$  for the SiC MCD-MOSFET, only an 8% increase. On the one hand, the highly doped JFET region could help spread

FIGURE 9. On-state and breakdown characteristics for the SiC C-MOSFET and SiC MCD-MOSFET, respectively.

FIGURE 10. Total current density distributions at  $I_{\rm DS}=100~{\rm A/cm^2}$  for the SiC MCD-MOSFET (a) without JFET region and (b) with JFET region, respectively.

the current more evenly into the drift region, thus reducing the JFET resistance for both cases. According to our simulation results, if without the JFET region, the  $R_{\rm ON}$  of SiC C-MOSFET is 2.5 m $\Omega$ ·cm<sup>2</sup> while 90.7 m $\Omega$ ·cm<sup>2</sup> for the SiC MCD-MOSFET, and the degradation becomes great. Obviously, the improvement on  $R_{ON}$  brought by the JFET area is more significant for the SiC MCD-MOSFET by comparison, since the dummy gate does not contribute to the current flow, as presented in Fig. 10. The other factor affecting the total on-resistance is the channel resistance, which is an important component of  $R_{ON}$ , especially in SiC-based MOSFET. The RON of the SiC C-MOSFET and MCD-MOSFET can grow to 1.1 m $\Omega$ ·cm<sup>2</sup> and 1.3 m $\Omega$ ·cm<sup>2</sup>, respectively, thus in contrast a 20% increase, if a conservative value 10 cm<sup>2</sup>/V-s of channel mobility is used. In brief, the introduction of JFET region and a high channel mobility both promote the on-state characteristic of SiC MCD-MOSFET. Furthermore, the SiC MCD-MOSFET has the same reverse blocking capability as that of the SiC C-MOSFET. It means that the segmented gate does not give rise to an electric crowding at the bottom of the oxide layer, which would be a threat to the long-term reliability of the devices.

Fig. 11 shows the C-V characteristics of the SiC C-MOSFET and MCD-MOSFET, respectively. The SiC MCD-MOSFET boasts a smaller input capacitance ( $C_{\text{ISS}}$ ) and a much lower reverse transfer capacitance ( $C_{\text{RSS}}$ ) as compared to the conventional one ( $C_{\text{ISS}}$  is reduced by half, while

622 VOLUME 8, 2020

FIGURE 11. C-V characteristics of the SiC C-MOSFET and MCD-MOSFET, respectively.

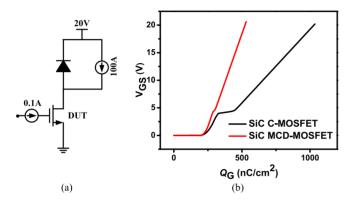

FIGURE 12. (a) Test circuit used for simulating the gate charge characteristics. (b) Gate charge characteristics for the studied MOSFETs.

$C_{\rm RSS}$  is lowered by up to 87%). It means that this top cell design could weaken the capacitive coupling between electrodes effectively due to the reduced area where the gate electrode overlaps the JFET region.

Fig. 12(a) shows the test circuit used to simulate the gate charge characteristics and the simulation results of both cases can be found in Fig. 12(b). The extracted gate charge  $Q_{\rm G}$  at  $V_{\rm GS}=20$  V and gate-to-drain charge  $Q_{\rm GD}$  for the SiC C-MOSFET is 1037 nC/cm² and 121 nC/cm², respectively. While in the SiC MCD-MOSFET,  $Q_{\rm G}=531$  nC/cm² and  $Q_{\rm GD}=12$  nC/cm² are obtained. As a consequence, the figures of merit  $R_{\rm ON}\times Q_{\rm G}$  and  $R_{\rm ON}\times Q_{\rm GD}$  are enhanced by a factor of 1.8 and 9, respectively. This is a remarkable promotion, making the SiC MCD-MOSFET more suitable for higher frequency applications. The main characteristics of the devices are summarized in Table 2.

# **III. PARAMETERS VARIATION**

The superior performance of SiC MCD-MOSFET is demonstrated in the previous section. In this section, the influence of parameters variation on the device characteristics will be explored.

As SiC-based switching devices, the high electric field in the gate oxide under reverse bias is always the major concern on account of the large critical field strength of SiC

**TABLE 2.** Performance comparison.

|                                | SiC<br>C-MOSFET | SiC<br>MCD-MOSFET | Unit                 |

|--------------------------------|-----------------|-------------------|----------------------|

| $V_{\mathrm{F}}$               | 2.82            | 1.75              | V                    |

| BD                             | Yes             | No                | -                    |

| BV                             | 1480            | 1515              | V                    |

| $R_{ m ON}$                    | 0.89            | 0.96              | $m\Omega \cdot cm^2$ |

| $Q_{ m RR}$                    | 3.28            | 1.56              | μC/cm <sup>2</sup>   |

| $C_{\mathrm{ISS}}$             | 20              | 9                 | nF/cm <sup>2</sup>   |

| $C_{ m RSS}$                   | 52              | 7                 | pF/cm <sup>2</sup>   |

| $Q_{ m G}$                     | 1037            | 531               | nC/cm <sup>2</sup>   |

| $Q_{ m GD}$                    | 121             | 12                | nC/cm <sup>2</sup>   |

| $R_{ m ON}\!\!	imes\!Q_{ m G}$ | 923             | 510               | $m\Omega \cdot nC$   |

| $R_{ m ON} 	imes Q_{ m GD}$    | 108             | 12                | mΩ·nC                |

BD: bipolar degradation;

$Q_{RR}$  is measured at  $I_{SD}$ =500 A/cm<sup>2</sup>;

$C_{\rm ISS}$  and  $C_{\rm RSS}$  are measured at  $V_{\rm DS}$ =200 V.

FIGURE 13. Lateral dimension of the SiC MCD-MOSFET.

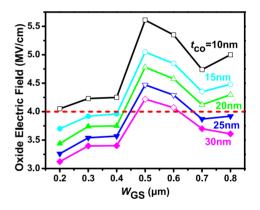

FIGURE 14. Variations of the maximum electric field in the oxide with  $W_{\rm GS}$  as a function of  $t_{\rm co}$ .

material. Fig. 13 shows the lateral dimension of the studied SiC MCD-MOSFET, and the maximum oxide field versus  $W_{\rm GS}$  as a function of  $t_{\rm co}$  is illustrated in Fig. 14. The hollow symbols represent the occurrence of the oxide breakdown. It is shown that a thicker  $t_{co}$  is favourable for electric field suppression as previously described. What's more, we obtain a type of "arch" shaped curve at a specified  $t_{co}$ , and the peak of electric field occurs at  $W_{GS} = 0.5 \mu m$ . This is reasonable since the gate oxide in the middle of the neck area is the weakest point due to the absence of protection by the depletion layer of P-base/N-drift junction where the drain voltage is mainly sustained. The electric field crowding is very likely to happen therein at the corner of the dummy gate, especially with a smaller  $t_{co}$ . Therefore,  $W_{GS}$  and  $t_{co}$ require to be carefully designed to ensure the ruggedness of the device and avoid the premature breakdown of the gate oxide.

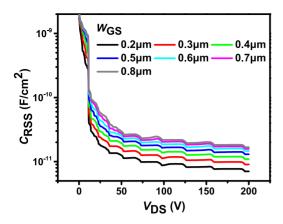

FIGURE 15. Variations of  $C_{RSS}$  with  $V_{DS}$  as a function of  $W_{GS}$ .

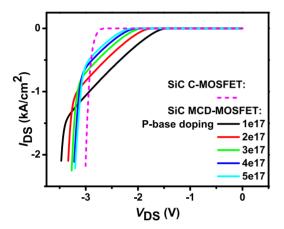

FIGURE 16. Conduction characteristics in the third quadrant for the SiC MCD-MOSFET versus P-base doping at  $t_{co} = 15$  nm.

It should be noted that no significant changes of the device performance are found in our simulations except that of  $V_{\rm F}$  just by modifying  $t_{\rm co}$ , and  $W_{\rm GS}$  has little effect on the first and third quadrant of I-V features for the SiC MCD-MOSFET due to the highly doped JFET region. Therefore, we only talk about the influence of  $W_{GS}$  on the reverse transfer capacitance herein, and the consequent variation of gate-to-drain charge characteristics is easy to reason out due to the proportional relationship between them. Note that  $W_{\rm GS}$  is just adjusted by changing the dummy gate length, and the true gate length keeps constant. Fig. 15 presents the  $C_{RSS}$  versus  $V_{DS}$  as a function of  $W_{GS}$ . It is discerned that a smaller  $W_{GS}$  will result in a lower  $C_{RSS}$ . As we know, C<sub>RSS</sub> is determined by the series combination of  $C_{\rm OX}$  (the electrostatic capacitance of the oxide layer) and  $C_{\rm SM}$  (the semiconductor capacitance under the gate oxide). Meanwhile, it is proportional to the width of the JFET area where the gate electrode overlaps the epitaxy.  $C_{\text{OX}}$  is constant for a particular architecture, while  $C_{\text{SM}}$  decreases with the increase of drain voltage due to the formation of the depletion region at the P-base/N-drift junction. In other word, a deeper bulk depletion will lead to a smaller  $C_{\rm SM}$  [27]. In the SiC MCD-MOSFET with a larger  $W_{GS}$ , there is no

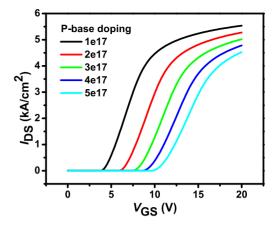

FIGURE 17. Variations of the transfer characteristics of SiC MCD-MOSFET as a function of P-base doping at  $t_{co} = 15$  nm.

depletion region formed in the JFET area under the gate oxide. Hence, a higher  $C_{SM}$  is obtained due to the lack of pinch-off effect at a lower drain voltage. In a word, a smaller  $W_{\rm GS}$  and a thicker  $t_{\rm co}$  is preferred. Of course, the tradeoff between the electric field suppression and  $V_{\rm F}$  should also be taken into account.

The P-base doping is a parameter which can significantly influence the threshold voltage of the device, while it is also a key factor affecting both of the forward and reverse conduction performance of the SiC MCD-MOSFET. As shown in Fig. 16, a larger knee voltage is obtained with higher P-base doping. However, the unipolar feature can be still observed at I<sub>SD</sub> lower than 500 A/cm<sup>2</sup> even with P-base doping of up to  $5 \times 10^{17}$  cm<sup>-3</sup>. In that case, besides, the threshold voltage of the device would reach to 10 V, as exhibited in Fig. 17. That is to say, the increased doping concentration of P-base region will not degrade too much the conduction characteristic of the SiC MCD-MOSFET in the third quadrant with a threshold voltage in a reasonable range. What's more, a high threshold voltage always results in a large  $R_{\rm ON}$ , namely a performance degradation in the first quadrant(not reported here for brevity). However, a lightly doped P-base region, conversely, could induce reach-through breakdown, which would weaken the blocking capability of the device. As a result, the P-base region with proper design should be carefully considered according to different device applications.

### IV. CONCLUSION

The easy-to-implement SiC MCD-MOSFET is studied in this paper utilizing TCAD simulations. The turn-on of the parasitic body diode can be restrained effectively when operating as a freewheeling diode, thus completely eliminating the bipolar degradation. Moreover, for the SiC MCD-MOSFET working as a switching device, the superior characteristics can be observed, such as a rather small  $C_{ISS}$  and  $C_{RSS}$ and a lower  $Q_G$  and  $Q_{GD}$ , when compared to the SiC C-MOSFET. Nevertheless, there is only a slight increase in  $R_{\rm ON}$  (8%), leading to a notably increased figures of merit

624 **VOLUME 8, 2020**  in the SiC MCD-MOSFET. At last, the effect of parameters variation on the device characteristics is discussed as well. These remarkable attributes make the SiC MCD-MOSFET an excellent choice for high-frequency power electronic applications.

#### **REFERENCES**

- [1] K. Hamada, M. Nagao, M. Ajioka, and F. Kawai, "SiC—Emerging power device technology for next-generation electrically powered environmentally friendly vehicles," *IEEE Trans. Electron Devices*, vol. 62, no. 2, pp. 278–285, Feb. 2015, doi: 10.1109/TED.2014.2359240.

- [2] M. Östling, R. Ghandi, and C. Zetterling, "SiC power devices—Present status, applications and future perspective," in *Proc. 23st Int. Symp. Power Semicond. Devices IC's (ISPSD)*, San Diego, CA, USA, 2011, pp. 10–15, doi: 10.1109/ISPSD.2011.5890778.

- [3] J. A. Cooper, Jr., M. R. Melloch, R. Singh, A. Agarwal, and J. W. Palmour, "Status and prospects for SiC power MOSFETs," *IEEE Trans. Electron Devices*, vol. 49, no. 4, pp. 658–664, Apr. 2002, doi: 10.1109/16.992876.

- [4] H. A. Mantooth, M. D. Glover, and P. Shepherd, "Wide bandgap technologies and their implications on miniaturizing power electronic systems," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 2, no. 3, pp. 374–385, Sep. 2014, doi: 10.1109/JESTPE.2014.2313511.

- [5] X. Zhou, Y. Wang, R. Yue, G. Dai, and J. Li, "Physics-based SPICE model on the dynamic characteristics of silicon carbide Schottky barrier diode," *IET Power Electron.*, vol. 9, no. 15, pp. 2803–2807, 2016, doi: 10.1049/iet-pel.2016.0399.

- [6] B. J. Baliga, Fundamentals of Power Semiconductor Devices. New York, NY, USA: Springer, 2008.

- [7] Y. Ebihara, J. Uehara, A. Ichimura, S. Mitani, M. Noborio, Y. Takeuchi, and K. Tsuruta, "Suppression of bipolar degradation in deep-P encapsulated 4H-SiC trench MOSFETs up to ultra-high current density," in *Proc. 31st Int. Symp. Power Semicond. Devices IC's (ISPSD)*, Shanghai, China, 2019, pp. 35–38, doi: 10.1109/ISPSD.2019.8757567.

- [8] H. Jiang et al., "SiC MOSFET with built-in SBD for reduction of reverse recovery charge and switching loss in 10-kV applications," in Proc. 29st Int. Symp. Power Semicond. Devices IC's (ISPSD), Sapporo, Japan, 2017, pp. 49–52, doi: 10.23919/ISPSD.2017.7988890.

- [9] M. Conrad and R. W. DeDoncker, "Avoiding reverse recovery effects in super junction MOSFET based half-bridges," in *Proc. IEEE 6th Int. Symp. Power Electron. Distrib. Gener. Syst.*, Aachen, Germany, Jun. 2015, pp. 1–5, doi: 10.1109/PEDG.2015.7223083.

- [10] N. Yamashita, N. Murakami, and T. Yachi, "Conduction power loss in MOSFET synchronous rectifier with parallel-connected Schottky barrier diode," *IEEE Trans. Power Electron.*, vol. 13, no. 4, pp. 667–673, Jul. 1998, doi: 10.1109/63.704135.

- [11] S. Hino et al., "Superior switching characteristics of SiC-MOSFET embedding SBD," in Proc. 31st Int. Symp. Power Semicond. Devices IC's (ISPSD), Shanghai, China, 2019, pp. 27–30, doi: 10.1109/ISPSD.2019.8757664.

- [12] C. Yen et al., "1700V/30A 4H-SiC MOSFET with low cut-in voltage embedded diode and room temperature boron implanted termination," in Proc. 27th Int. Symp. Power Semicond. Devices IC's (ISPSD), Hong Kong, China, 2015, pp. 265–268, doi: 10.1109/ISPSD.2015.7123440.

- [13] M. Uchida et al., "Novel SiC power MOSFET with integrated unipolar internal inverse MOS-channel diode," in *Int. Electron Devices Meeting Tech. Dig. (IEDM)*, Washington, DC, USA, Dec. 2011, pp. 1–4, doi: 10.1109/IEDM.2011.6131620.

- [14] O. Kusumoto et al., "Reliability of diode-integrated SiC power MOSFET(DioMOS)," Microelectron. Rel., vol. 58, pp. 158–163, Mar. 2016, doi: 10.1016/j.microrel.2015.11.033.

- [15] M. Zhang, J. Wei, X. Zhou, H. Jiang, B. Li, and K. J. Chen, "Simulation study of a power MOSFET with built-in channel diode for enhanced reverse recovery performance," *IEEE Electron Device Lett.*, vol. 40, no. 1, pp. 79–82, Jan. 2019, doi: 10.1109/LED.2018.2881234.

- [16] X. Zhou et al., "SiC double-trench MOSFETs with embedded MOS-channel diode," IEEE Trans. Electron Devices, vol. 67, no. 2, pp. 582–587, Feb. 2020, doi: 10.1109/TED.2019.2961367.

- [17] C. Abbate, G. Busatto, D. Tedesco, A. Sanseverino, F. Velardi, and J. Wyss, "Gate damages induced in SiC power MOSFETs during heavy-ion irradiation—Part II," *IEEE Trans. Electron Devices*, vol. 66, no. 10, pp. 4243–4250, Oct. 2019, doi: 10.1109/TED.2019.2931078.

- [18] Y. Wang, K. Tian, Y. Hao, C.-H. Yu, and Y.-J. Liu, "4H–SiC step trench gate power metal–oxide–semiconductor field-effect transistor," *IEEE Electron Device Lett.*, vol. 37, no. 5, pp. 633–635, May 2016, doi: 10.1109/LED.2016.2542183.

- [19] T. Hatakeyama, T. Watanabe, T. Shinohe, K. Kojima, K. Arai, and N. Sano, "Impact ionization coefficients of 4H silicon carbide," *Appl. Phys. Lett.*, vol. 85, no. 2, pp. 133–135, 1986, doi: 10.1063/1.1784520.

- [20] H. Niwa, J. Suda, and T. Kimoto, "Temperature dependence of impact ionization coefficients in 4H-SiC," *Mater. Sci. Forum*, vols. 778–780, pp. 461–466, Feb. 2014, doi: 10.4028/www.scientific.net/MSF.778-780.461.

- [21] X. Zhou et al., "Single-event effects in SiC double-trench MOSFETs," IEEE Trans. Nucl. Sci., vol. 66, no. 11, pp. 2312–2318, Nov. 2019, doi: 10.1109/TNS.2019.2944944.

- [22] X. Zhou et al., "A deep insight into the degradation of 1.2-kV 4H-SiC MOSFETs under repetitive unclamped inductive switching stresses," *IEEE Trans. Power Electron.*, vol. 33, no. 6, pp. 5251–5261, Jun. 2018, doi: 10.1109/TPEL.2017.2730259.

- [23] J. Wei, M. Zhang, H. Jiang, C. Cheng, and K. J. Chen, "Low ON-resistance SiC trench/planar MOSFET with reduced OFF-state oxide field and low gate charges," *IEEE Electron Device Lett.*, vol. 37, no. 8, pp. 1458–1461, Nov. 2016, doi: 10.1109/LED.2016.2609599.

- [24] X. Zhou, R. Yue, J. Zhang, G. Dai, J. Li, and Y. Wang, "4H-SiC trench MOSFET with floating/grounded junction barrier-controlled gate structure," *IEEE Trans. Electron Devices*, vol. 64, no. 11, pp. 4568–4574, Nov. 2017, doi: 10.1109/TED.2017.2755721.

- [25] J. Lutz, H. Schlangenotto, U. Scheuermann, and R. D. Doncker, Semiconductor Power Devices: Physics, Characteristics, Reliability. New York, NY, USA: Springer, 2011.

- [26] D. Peters et al., "Performance and ruggedness of 1200V SiC— Trench-MOSFET," in Proc. 29th Int. Symp. Power Semicond. Devices IC's (ISPSD), Sapporo, Japan, 2017, pp. 239–242, doi: 10.23919/ISPSD.2017.7988904.

- [27] S. Xu, C. Ren, Y. C. Liang, P.-D. Foo, and J. K. O. Sin, "Theoretical analysis and experimental characterization of the dummy-gated VDMOSFET," *IEEE Trans. Electron Devices*, vol. 48, no. 9, pp. 2168–2176, Sep. 2001, doi: 10.1109/16.944212.