Received 4 July 2019; revised 16 October 2019; accepted 16 November 2019. Date of publication 21 November 2019; date of current version 3 January 2020.

The review of this paper was arranged by Editor A. Nathan.

Digital Object Identifier 10.1109/JEDS.2019.2954889

# A Temperature Compensation Method by Adjusting Gamma Voltages for High Luminance Uniformity of Active Matrix Organic Light-Emitting Diode Displays

JUN-SEOK NA<sup>®</sup> (Student Member, IEEE), SEONG-KWAN HONG<sup>®</sup> (Member, IEEE),

AND OH-KYONG KWON<sup>®</sup> (Member, IEEE)

Department of Electronic Engineering, Hanyang University, Seoul 133-791, South Korea CORRESPONDING AUTHOR: O.-K. KWON (e-mail: okwon@hanyang.ac.kr)

ABSTRACT In this paper, a temperature compensation method is proposed for active-matrix organic light-emitting diode (AMOLED) displays to achieve high luminance uniformity over a wide operating temperature range. The proposed temperature compensation method compensates for variation in OLED luminance according to temperature by adjusting the gamma voltages. To verify the proposed method, a built-in test circuit, which includes temperature sensors, current calculation block, current adjustment block, and gamma voltage generator, was fabricated using 90 nm complementary metal-oxide semiconductor process technology with 6 V high-voltage devices. The measurement results show that the proposed method achieves a high luminance uniformity with an OLED luminance variation of less than 1.54 cd/m² over the temperature range of −45°C to 60°C. Therefore, the proposed temperature compensation method is suitable for AMOLED displays requiring high luminance uniformity.

**INDEX TERMS** Organic light-emitting diode (OLED), temperature compensation, high luminance uniformity, gamma voltage.

#### I. INTRODUCTION

Active matrix organic light-emitting diode (AMOLED) displays have been widely used for small mobile devices including smartphones, smartwatches, head-mounted displays, and smart glasses to large-sized televisions. Recently, these displays have been developed to realize augmented reality (AR) and virtual reality (VR) applications. Compared to liquid crystal displays, OLED displays are more suitable for AR and VR applications because of their high contrast ratio, fast optical response, and excellent color reproducibility [1]–[4]. Particularly, outdoor AR and VR applications are used in a wide operating temperature range.

However, OLED luminance varies according to temperature, which increases due to increased OLED efficiency as the temperature increases [5]–[8]. Therefore,

a driving method that can compensate for variation in OLED luminance according to temperature is necessary to achieve high luminance uniformity of the OLED over a wide operating temperature range.

Conventional AMOLED displays mainly compensated for OLED degradation [9], [10], and variations in threshold voltage and mobility of the backplanes [10], [11], such as thin-film transistors (TFTs) and metal-oxide-semiconductor field-effect transistors (MOSFETs). However, these displays could not properly compensate for variation in the OLED luminance according to the temperature. The external compensation method in [9], [10] compensated for OLED degradation and variations in threshold voltage and mobility of the TFT. However, they could not sufficiently compensate for variation in the OLED luminance only by sensing the

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see http://creativecommons.org/licenses/by/4.0/

anode voltage of the OLED, which could not fully represent the OLED luminance [7]. The internal compensation method in [11] compensated for variation in the threshold voltage of the MOSFET, but only for variation in specific OLED efficiency in a pixel structure, and thus could not accurately compensate for variation in the OLED luminance according to the temperature when the OLED efficiency varies.

In this paper, a temperature compensation method is proposed for AMOLED displays to achieve high luminance uniformity over a wide operating temperature range. The proposed temperature compensation method compensates for variation in the OLED luminance according to the temperature by adjusting the gamma voltages. Section II describes the proposed temperature compensation method along with the OLED luminance and efficiency, and the I-V characteristic of the MOSFET according to the temperature. In addition, the operation principle of the proposed temperature compensation method is explained with flowchart and block diagram. In Section III, the measurement results using a fabricated built-in test circuit are analyzed and compared with previous works to verify the proposed temperature compensation method. Finally, conclusions are given in Section IV.

## II. PROPOSED TEMPERATURE COMPENSATION METHOD A. OLED LUMINANCE AND EFFICIENCY AND I-V CHARACTERISTIC OF THE MOSFET ACCORDING TO TEMPERATURE

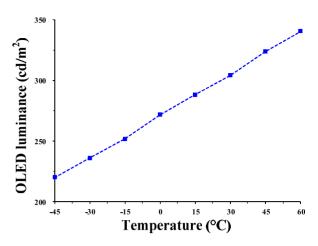

Fig. 1 shows the measurement results of white OLED luminance in the temperature range from  $-45^{\circ}$ C to  $60^{\circ}$ C, representing that the OLED luminance increases as the temperature increases. Here, the OLED luminance is closely related to the OLED efficiency [5]–[8]. The OLED efficiency can be represented as quantum efficiency comprising the external quantum efficiency ( $\eta_{ext}$ ) and internal quantum efficiency ( $\eta_{int}$ ). The external quantum efficiency [5]–[6] is expressed as

$$\eta_{ext}(T) = \eta_{int}(T)\eta_{out} = \eta_r(T)\phi_f \chi \eta_{out},$$

(1)

where  $\eta_{out}$  is an out-coupling efficiency,  $\eta_r$  is the ratio of the number of exciton formation events within an OLED device to the number of electrons,  $\varphi_f$  is the fluorescence quantum efficiency,  $\chi$  is the fraction of excitons formed as singlets, and T is an absolute temperature. In addition,  $\eta_r$  is determined by the charge injection and the recombination of the electrons and holes, which are affected by the mobility. The mobility increases as the temperature increases due to increased hopping speed [5]–[8], which is thermally activated at high temperature. Therefore, the OLED efficiency increases as the temperature increases.

To achieve high luminance uniformity of the OLED over a wide operating temperature range, the current of the MOSFETs in a pixel, which drives the OLED, should be reduced since the OLED efficiency increases as the temperature increases. The drain current of the p-channel MOSFET

FIGURE 1. Measurement results of white OLED luminance in the temperature range from -45°C to 60°C under the OLED bias condition of 3.3 V.

$(I_D)$  can be expressed as [12]

$$I_D(T) = \frac{1}{2} \mu \left( \frac{T}{T_{NOM}} \right)^{UTE} C_{ox} \frac{W}{L} (V_{SG} - |V_{th}|)^2, \qquad (2)$$

where  $\mu$ ,  $T_{NOM}$ , UTE,  $C_{ox}$ , W, L,  $V_{SG}$ , and  $V_{th}$  are the mobility, nominal temperature at which the mobility is extracted, mobility temperature exponent, gate capacitance per unit area, channel width and length of the MOSFET, source-to-gate voltage of the MOSFET, and threshold voltage, respectively. Since UTE has a value between -1 and -1.5 in most CMOS process technologies, the mobility decreases as the temperature increases, and thereby  $I_D$  decreases as well [12]–[14]. Since the OLED luminance can be represented as a product of the OLED efficiency in (1) and the pixel driving current in (2) [11], the OLED luminance  $(L_{OLED})$  can be expressed as

$$L_{OLED}(T) = \eta_{ext}(T)I_D(T). \tag{3}$$

Equation (3) should be independent of the temperature to achieve high luminance uniformity of the OLED over a wide operating temperature range. Therefore, the proposed temperature compensation method calculates the pixel current according to the temperature and adjusts the gamma voltages, which drive the pixel circuit, thus eventually making (3) independent of the temperature.

### B. FLOWCHART AND ARCHITECTURE FOR THE PROPOSED TEMPERATURE COMPENSATION METHOD

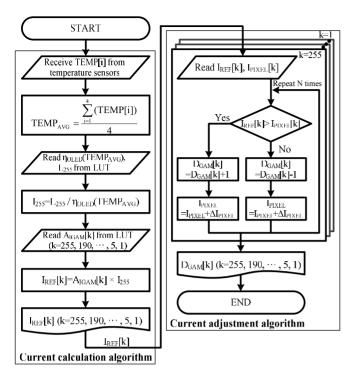

Fig. 2 shows the flowchart of the proposed current calculation algorithm and current adjustment algorithm for the proposed temperature compensation method. The proposed current calculation algorithm performs the following steps (i) to (iii) to calculate the reference currents (I<sub>REF</sub>[k]) according to the temperatures sensed by the four temperature sensors, and the OLED efficiency and driving current ratio for each gamma tap (A<sub>IGAM</sub>[k]) in a look-uptable (LUT), where k is the gray level of 255, 190, 144, 98, 65, 40, 21, 10, 5, and 1.

FIGURE 2. Flowchart of the proposed current calculation and current adjustment algorithms.

(i) The proposed current calculation algorithm reads the sensed temperatures (TEMP[i]) and averages them to determine a final temperature value (TEMP<sub>AVG</sub>), where TEMP[i] is the temperature value sensed by the i<sup>th</sup> temperature sensor. (ii) It reads the OLED efficiency according to TEMP<sub>AVG</sub> ( $\eta_{OLED}$  (TEMP<sub>AVG</sub>)) and the OLED luminance at the 255 gray level ( $L_{255}$ ) in the LUT, and it divides  $L_{255}$  by  $\eta_{OLED}$  (TEMP<sub>AVG</sub>) to determine the driving current required to drive the OLED to  $L_{255}$  ( $I_{255}$ ). (iii) It reads  $I_{IGAM}[k]$  in the LUT and produces  $I_{REF}[k]$  by multiplying  $I_{IGAM}[k]$  and  $I_{255}$ . Through this simple arithmetic calculation, the proposed current calculation algorithm produces the final  $I_{REF}[k]$  according to the gray level of the gamma tap.

Next, the proposed current adjustment algorithm performs the following steps (iv) to (vii) to adjust the current of the dummy pixel array ( $I_{PIXEL}[k]$ ) and produces the gamma digital codes ( $D_{GAM}[k]$ ). (iv) It receives  $I_{REF}[k]$  and compares it with  $I_{PIXEL}[k]$  when k is 255 at the 255 gray gamma tap. (v) It adjusts  $I_{PIXEL}$  [255] by increasing  $I_{PIXEL}$  [255] with  $D_{GAM}$  [255] when  $I_{REF}$  [255] is greater than  $I_{PIXEL}$  [255], and by decreasing  $I_{PIXEL}$  [255] with  $D_{GAM}$  [255] when  $I_{REF}$  [255] is less than  $I_{PIXEL}$  [255]. (vi) After N iterations, where N is the bit number of  $D_{GAM}[k]$ , it produces  $D_{GAM}$  [255] corresponding to the final  $I_{PIXEL}$  [255]. (vii) It sequentially repeats steps (iv) to (vi) from 255 to 1 gray gamma tap and then produces the final  $D_{GAM}[k]$ , which is used to produce gamma voltages.

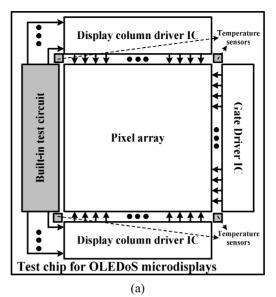

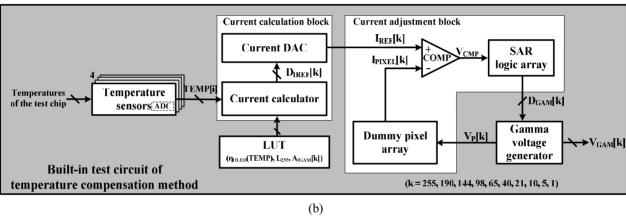

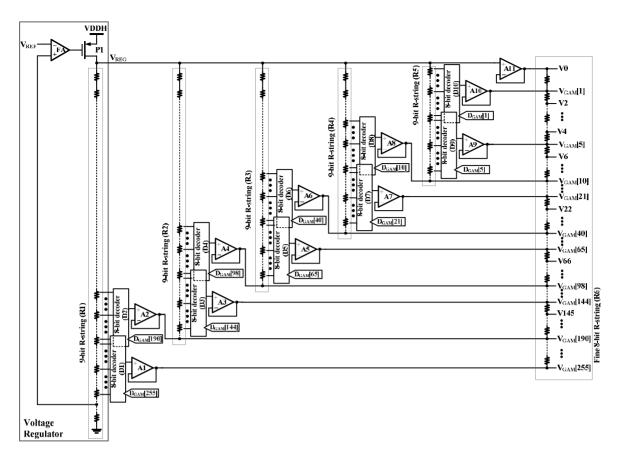

Fig. 3(a) shows the block diagram of the test chip for organic light-emitting diode-on-silicon (OLEDoS) microdisplays. Fig. 3(b) shows the built-in test circuit implemented in

the test chip to verify the proposed temperature compensation method by adjusting the gamma voltages. The built-in test circuit consists of four temperature sensors, a current calculation block, a current adjustment block, a gamma voltage generator, and a LUT containing information on OLED efficiency and driving current ratio for the gamma taps of the display as shown in Fig. 3(b).

The temperature sensors, which are located at the four corners of the pixel array of the test chip, sense the temperatures of the test chip and convert them to TEMP[i] using analog-todigital converters (ADCs), and then average them as shown in Fig. 3(b). Since the single crystalline silicon substrate used in this work has a good thermal conductivity, which is 1.412 W/(cm·K) at 300K, the difference between the temperatures sensed at four corners was measured to be less than  $\pm 1$ °C, representing that the sensed temperatures varied little depending on the images and the location of the pixel circuit in a chip. In addition, in order to reduce the temperature error, the temperature sensors perform one-point calibration. The current calculation block, which employs the proposed current calculation algorithm, consists of a current calculator and a current digital-to-analog converter (DAC). The current calculator calculates DIREF[k] based on the sensed temperature and the information in the LUT. The current DAC converts D<sub>IREF</sub>[k] to I<sub>REF</sub>[k]. The current adjustment block, which employs the proposed current adjustment algorithm to produce D<sub>GAM</sub>[k], consists of a dummy pixel array, a current comparator (COMP), and a successive approximation register (SAR) logic array. COMP compares I<sub>REF</sub>[k] with I<sub>PIXEL</sub>[k] generated by the dummy pixel array and then produces a compared voltage (V<sub>CMP</sub>). The SAR logic array performs the SAR operation according to V<sub>CMP</sub> using the binary search algorithm [15] for each gamma tap, and it produces D<sub>GAM</sub>[k]. Next, the gamma voltage generator produces  $V_P[k]$  according to  $D_{GAM}[k]$ , and the dummy pixel array, which is driven by V<sub>P</sub>[k], produces I<sub>PIXEL</sub>[k]. In the SAR operation, the SAR logic array initially resets D<sub>GAM</sub>[k] to 0 for all k and then changes the most significant bit (MSB) of D<sub>GAM</sub> [255] to 1. COMP then compares I<sub>PIXEL</sub> [255] corresponding to D<sub>GAM</sub> [255] with I<sub>REF</sub> [255] and produces V<sub>CMP</sub>. When I<sub>REF</sub> [255] is greater than I<sub>PIXEL</sub> [255], V<sub>CMP</sub> becomes high, and the SAR logic array maintains the MSB of D<sub>GAM</sub>[k] at 1. When I<sub>REF</sub> [255] is less than I<sub>PIXEL</sub> [255], V<sub>CMP</sub> becomes low, and the SAR logic array changes the MSB of  $D_{GAM}[k]$  to 0.

These comparison operations are repeated from the MSB to the least significant bit (LSB) of  $D_{GAM}$  [255] to produce the final  $D_{GAM}$  [255] as shown in Fig. 3(b). The gamma voltage generator then produces the final  $V_P$  [255] according to the final  $D_{GAM}$  [255], which is in the I-V curve of the driving MOSFETs used in the dummy pixel according to the temperature, when  $I_{PIXEL}$  [255] is near  $I_{REF}$  [255]. The current adjustment block sequentially repeats the SAR operation from 255 to 1 gray gamma tap and produces  $D_{GAM}[k]$ . Finally, the gamma voltage generator sends the above final  $V_P[k]$  as gamma voltage ( $V_{GAM}[k]$ ),

VOLUME 8, 2020 3

FIGURE 3. Block diagrams of (a) the test chip for OLEDoS microdisplays and (b) the built-in test circuit implemented in the test chip to verify the proposed temperature compensation method by adjusting gamma voltages.

corresponding to  $I_{PIXEL}[k]$  in the I-V curve, to the display column driver IC in the test chip. Thus, the proposed temperature compensation method compensates for variations in OLED efficiency and the I-V characteristic of the driving MOSFET according to the temperature.

#### C. CIRCUIT IMPLEMENTATION

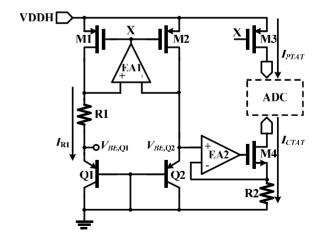

Fig. 4 shows the schematic of the temperature sensor core using bipolar junction transistors (BJTs), which produces a proportional-to-absolute temperature current ( $I_{PTAT}$ ) and a complementary-to-absolute temperature current ( $I_{CTAT}$ ). The temperature sensor core senses the temperature using  $I_{PTAT}$  and  $I_{CTAT}$ , which is obtained by  $I_{PTAT}/(I_{PTAT}+I_{CTAT})$  to reduce the error caused by the process variations. Then, the sigma-delta ADC in the temperature sensors converts the sensed temperature to TEMP[i] [16]–[17]. Here,  $I_{PTAT}$  and  $I_{CTAT}$  are generated as follows. The voltage between the base and emitter of Q2 ( $V_{BE,Q2}$ ) is equal to the sum of the voltage between the base and emitter of Q1 ( $V_{BE,Q1}$ ) and the voltage drop across R1 because the node X is biased by an

FIGURE 4. Schematic of the temperature sensor core.

error amplifier (EA1). Thus, the drain voltages of M1 and M2 become equal. Therefore,  $V_{BE,O2}$  can be expressed as

$$V_{BE,O2} = V_{BE,O1} + I_{R1} \cdot R1,$$

(4)

FIGURE 5. Schematic of the gamma voltage generator.

where  $I_{R1}$  is the current flowing through R1. The voltage between the base and emitter of BJT ( $V_{BE}$ ) can be expressed as [16]

$$V_{BE} = \frac{kT}{q} \cdot \ln\left(\frac{I_C}{I_S}\right),\tag{5}$$

where k, T, q,  $I_C$ , and  $I_S$  are the Boltzmann's constant, temperature, electron charge, collector current, and saturation current, respectively. From (4) and (5),  $I_{PTAT}$  of M3 mirrored by M1 and M2 can be expressed as

$$I_{PTAT} = \frac{kT}{q} \cdot \frac{\ln(K_{M2}/K_{M1})}{K_{M3}/K_{M1} \cdot R1},$$

(6)

where K is the aspect ratio of the MOSFET. Therefore,  $I_{PTAT}$  is linearly proportional to the temperature. Moreover,  $V_{BE,Q2}$ , which becomes equal to the source voltage of M4 using the error amplifier (EA2), generates a current flowing through R2 ( $I_{CTAT}$ ) that can be expressed as

$$I_{CTAT} = \frac{V_{BE,Q2}}{R2}. (7)$$

From [16]–[17],  $I_{CTAT}$  is inversely proportional to the temperature because  $V_{BE,Q2}$  decreases as the temperature increases.

Fig. 5 shows the schematic of the gamma voltage generator, which consists of a p-channel MOSFET (P1), a feedback amplifier (FA), five 9-bit R-strings (R1-R5),

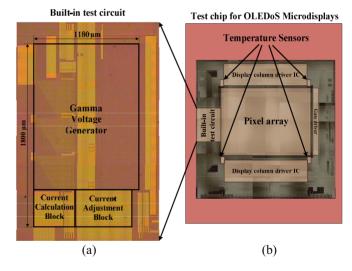

FIGURE 6. Photomicrographs of the (a) built-in test circuit for the proposed temperature compensation method and (b) test chip for OLEDOS microdisplays.

ten 8-bit decoders (D1-D10), eleven gamma buffer amplifiers (A1-A11), and a fine 8-bit R-string (R6). The five 9-bit R-strings produce fine voltages as the gray level lowers, while reducing the number of resistors by dividing the stage of the R-strings [18]. Each pair of 8-bit decoders (D1 and D2, D3 and D4, D5 and D6, D7 and D8, and

VOLUME 8, 2020 5

FIGURE 7. Measured voltage waveforms of (a) 255, (b) 144, and (c) 5 gray gamma taps at room temperature.

D9 and D10) shares the voltages produced by the 9-bit R-string depending on the gamma voltage of the corresponding 8-bit decoder. The voltage regulator, including P1, FA, and R1, receives a bandgap reference voltage (V<sub>REF</sub>) as an input and generates a regulated voltage (V<sub>REG</sub>), which is buffered through A11. Then, a 0 gray voltage (V0) is produced. D1 selects a voltage among the 9-bit voltages between V<sub>REG</sub> and ground, which are divided by R1, according to D<sub>GAM</sub> [255]. The selected voltage is then buffered through A1, and a gamma voltage of 255 gray gamma tap (V<sub>GAM</sub> [255]) is produced. In the same manner as V<sub>GAM</sub> [255], D2 selects a voltage among the 9-bit voltages between V<sub>REG</sub> and ground, which are divided by R1, according to D<sub>GAM</sub> [190]. The selected voltage is then buffered through A2, and a gamma voltage of 190 gray gamma tap (V<sub>GAM</sub> [190]) is produced. Next, D3 selects a voltage among the 9-bit voltages between V<sub>REG</sub> and V<sub>GAM</sub> [190], which are divided by R2, according to D<sub>GAM</sub> [140]. The selected voltage is then buffered through A3, and a gamma voltage of 140 gray gamma tap (V<sub>GAM</sub> [140]) is produced. D4 selects a voltage among the 9-bit voltages between V<sub>REG</sub> and V<sub>GAM</sub> [190], which are divided by R2, according to D<sub>GAM</sub> [98]. The selected voltage is then buffered through A4, and a gamma voltage of 98 gray gamma tap (V<sub>GAM</sub> [98]) is produced. In this way, each gamma voltage is sequentially produced from a gray level of 255 to 1. The voltage interval of the 9-bit voltages for the gamma voltages selection decreases as the gray level lowers, thus increasing the sensitivity in the lower gray levels.

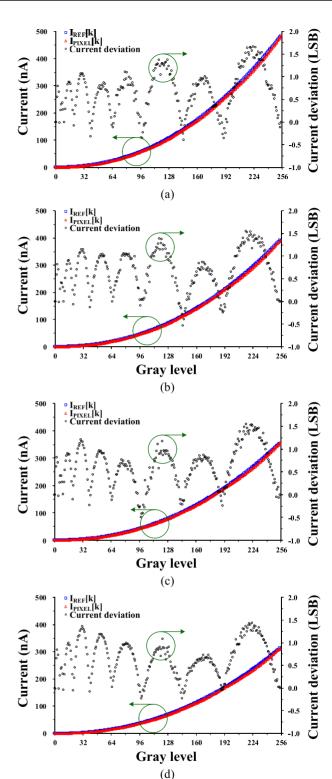

FIGURE 8. Measurement results of  $I_{PIXEL}[k]$  and calculated  $I_{REF}[k]$  (on the left y-axis) and the current deviation (on the right y-axis) with respect to gray level when the temperatures is (a)  $-40^{\circ}$ C, (b)  $0^{\circ}$ C, (c)  $25^{\circ}$ C, and (d)  $60^{\circ}$ C.

#### **III. MEASUREMENT RESULTS**

To verify the proposed temperature compensation method, a built-in test circuit implemented in a test chip for OLEDoS

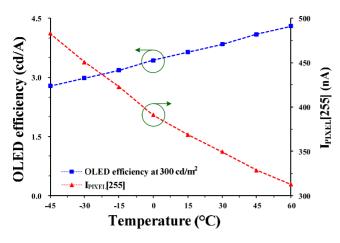

FIGURE 9. Measurement results of OLED efficiency at 300 cd/m<sup>2</sup> and IpIXEL [255] in the temperature range from -45°C to 60°C.

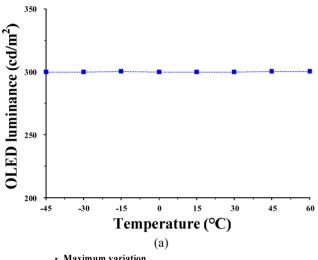

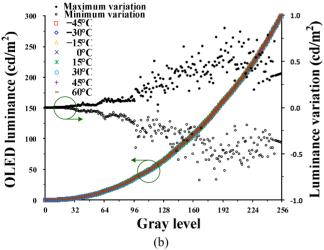

FIGURE 10. (a) Calculated OLED luminance according to temperature at the 255 gray level and (b) calculated OLED luminance (on the left y-axis) and its variation (on the right y-axis) according to the gray level in the temperature range from -45°C to 60°C.

microdisplays was fabricated using 90 nm standard CMOS process technology with 6 V high-voltage devices. Figs. 6(a) and (b) show the photomicrographs of the built-in test circuit

TABLE 1. Performance summary.

| Index                                                 | [9]                                   | [10]                                  | [11]                                           | This work                                      |

|-------------------------------------------------------|---------------------------------------|---------------------------------------|------------------------------------------------|------------------------------------------------|

| Process with device                                   | Low-<br>temperature<br>poly-Si<br>TFT | Low-<br>temperature<br>poly-Si<br>TFT | 90 nm<br>CMOS<br>process<br>with 6 V<br>device | 90 nm<br>CMOS<br>process<br>with 6 V<br>device |

| Area<br>(μm × μm)                                     | -                                     | -                                     | -                                              | 1180 ×<br>1800                                 |

| Temperature<br>error of<br>temperature<br>sensor (°C) | -                                     | -                                     | -                                              | -0.84 to<br>0.79                               |

| Current deviation (LSB)                               | -                                     | -                                     | -                                              | -0.53 to<br>1.65                               |

| Temperature range (°C)                                | -20 to 60                             | -20 to 80                             | -45 to 60                                      | -45 to 60                                      |

| Luminance<br>variation<br>(cd/m²)                     | 28.00                                 | 2.76                                  | 11.30                                          | 1.54                                           |

and the test chip for OLEDoS microdisplays, respectively. The built-in test circuit includes the current calculation block, current adjustment block, and gamma voltage generator, and the test chip for OLEDoS microdisplays includes the built-in test circuit, temperature sensors, display column driver ICs, a gate driver, and a pixel array. The built-in test circuit occupies an area of  $1180 \times 1800~\mu m^2$ , excluding the temperature sensors, which are located at the four corners of the pixel array in the test chip.

Figs. 7(a), (b), and (c) show the measured voltage waveforms of the 255, 144, and 5 gray gamma taps at room temperature, respectively. In the reset phase, the gamma digital codes are 0 to reset the gamma voltages. In the gamma voltage adjustment phase, the gamma voltages are adjusted until  $I_{PIXEL}[k]$  is near to  $I_{REF}[k]$ .

Figs. 8(a), (b), (c), and (d) show the measurement results of  $I_{PIXEL}[k]$  and the calculated  $I_{REF}[k]$  (on the left y-axis) and the current deviation (on the right y-axis) with respect to the gray level when the temperatures are -45, 0, 25, and  $60^{\circ}$ C, respectively. The current deviation between  $I_{PIXEL}[k]$  and  $I_{REF}[k]$  ranges from -0.53 LSB to +1.65 LSB over the entire gray level, demonstrating that the proposed compensation method effectively works.

Fig. 9 shows the measurement results of the OLED efficiency at 300 cd/m<sup>2</sup> and I<sub>PIXEL</sub> [255] in the temperature range from -45°C to 60°C. The measured OLED efficiency, which is modeled as a linear equation, varies from 2.78 cd/A to 4.30 cd/A and the measured I<sub>PIXEL</sub> [255] varies from 483 nA to 312 nA according to the temperature. The OLED luminance can be calculated as the product of the OLED efficiency and I<sub>PIXEL</sub> [255]. Fig. 10(a) shows the calculated OLED luminance according to the temperature at the 255 gray level, which varies from 299.60 cd/m<sup>2</sup> to 300.34 cd/m<sup>2</sup> over the temperature range of -45°C to 60°C. Fig. 10(b) shows the calculated OLED luminance

VOLUME 8, 2020 7

(on the left y-axis) and its variation (on the right y-axis) according to the entire gray level in the temperature range from  $-45^{\circ}$ C to  $60^{\circ}$ C, indicating that the proposed temperature compensation method achieves high luminance uniformity, which has an OLED luminance variation of less than  $1.54 \text{ cd/m}^2$ .

The performances of the proposed temperature compensation method are summarized and compared with those of previous works in Table 1. The proposed temperature compensation method achieves the least luminance variation, representing the best luminance uniformity compared to previous works.

#### **IV. CONCLUSION**

In this paper, a temperature compensation method is proposed and verified using a built-in-test circuit on a singlecrystalline silicon wafer for high luminance uniformity AMOLED displays. The proposed temperature compensation method employs a simple algorithm to calculate the reference current. In addition, it employs a current adjustment algorithm, which compares the reference current with the current of the dummy pixel array to compensate for OLED luminance variation according to the temperature by adjusting the gamma voltages. To verify the proposed temperature compensation method, a built-in-test circuit was fabricated using 90-nm CMOS process technology with 6-V high-voltage devices. The measurement results show that the current deviation ranges from -0.53 LSB to +1.65 LSB over the temperature range of  $-45^{\circ}$ C to  $60^{\circ}$ C. Moreover, the proposed temperature compensation method has an almost constant value of OLED luminance ranging between 299.60 cd/m<sup>2</sup> and 300.34 cd/m<sup>2</sup> over the temperature range of -45°C to 60°C, resulting in OLED luminance variation less than 1.54 cd/m<sup>2</sup>. Therefore, the proposed temperature compensation method is suitable for AMOLED displays requiring high luminance uniformity.

#### **REFERENCES**

- J. L. Sanford and E. S. Schlig, "Direct view active matrix VGA OLEDon-crystalline-silicon display," in *Soc. Int. Display (SID) Symp. Dig.*, 2001, pp. 376–379.

- [2] U. Vogel *et al.*, "Bi-directional OLED microdisplay for interactive HMD," in *Soc. Int. Display (SID) Symp. Dig.*, 2008, pp. 81–84.

- [3] B. Richter et al., "Bidirectional OLED microdisplay: Combining display and image sensor functionality into monolithic CMOS chip," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, 2011, pp. 314–316.

- [4] A. Misra, P. Kumar, M. N. Kamalasanan, and S. Chandra, "White organic LEDs and their recent advancements," *Semicond. Sci. Technol.*, vol. 21, no. 7, pp. R35–R47, Jul. 2006.

- [5] M. Shukla and N. Brahme, "Analytical measurements for quantum efficiency of organic light emitting diodes," J. Int. Acad. Phys. Sci., vol. 15, no. 2, pp. 231–238, 2011.

- [6] J. Shinar, Organic Light-Emitting Devices. New York, NY, USA: Springer, 2004.

- [7] S. K. Saha, Y. K. Su, and F. S. Juang, "Temperature dependence of electroluminescence in a tris-(8-hydroxy) quinoline aluminum (Alq/sub 3/) light emitting diode," *IEEE J. Quantum Electron.*, vol. 37, no. 6, pp. 807–812, Jun. 2001.

- [8] L. Yang, W. Chen, B. Wei, and J. Zhang, "Temperature and emitting area dependence of red organic light-emitting diode performance," *Phys. Status Solidi A*, vol. 211, no. 7, pp. 1488–1492, Jul. 2014.

- [9] S.-W. Wang et al., "Low-power consumptive luminance compensation for a digital driving AMOLED display using a multiple output boost converter," in Soc. Int. Display (SID) Symp. Dig., 2010, pp. 898–901.

- [10] H.-J. In et al., "An advanced external compensation system for active matrix organic light-emitting diode displays with poly-Si thin-film transistor backplane," *IEEE Trans. Electron Devices*, vol. 57, no. 11, pp. 3012–3019, Nov. 2010.

- [11] B.-C. Kwak and O.-K. Kwon, "A 2822-ppi resolution pixel circuit with high luminance uniformity for OLED microdisplays," *J. Display Technol*, vol. 12, no. 10, pp. 1083–1088, Oct. 2016.

- [12] HSPICE Reference Manual: MOSFET Models, Version P-2019.06-SP1, Synopsys, Inc., Mountain View, CA, USA, 2019.

- [13] P. Vimala and N. B. Balamurugan, "New analytical model for nanoscale tri-gate SOI MOSFETs including quantum effects," *IEEE J. Electron Devices Soc.*, vol. 2, no. 1, pp. 1–7, Jan. 2014.

[14] M. Kimura, J. Taya, and A. Nakashima, "Temperature dependences

- [14] M. Kimura, J. Taya, and A. Nakashima, "Temperature dependences of *I - V* characteristics of SD and LDD poly-Si TFTs," *IEEE Electron Device Lett.*, vol. 33, no. 5, pp. 682–684, May 2012.

- [15] Y.-R. Jo, S.-K. Hong, and O.-K. Kwon, "A multi-bit incremental ADC based on successive approximation for low noise and high resolution column-parallel readout circuits," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 9, pp. 2156–2166, Sep. 2015.

- [16] A. Heidary, G. Wang, K. Makinwa, and G. Meijer, "A BJT-based CMOS temperature sensor with a 3.6pJ-K<sup>2</sup>-resolution FoM," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2014, pp. 224–225.

- [17] M. A. P. Pertijs, K. A. A. Makinwa, and J. H. Huijsing, "A CMOS smart temperature sensor with a 3σ inaccuracy of ±0.1°C from −55°C to 125°C," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2805–2815, Dec. 2005.

- [18] P.-M. Lee and H.-Y. Chen, "Adjustable gamma correction circuit for TFT LCD," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, 2005, pp. 780–783.

**JUN-SEOK NA** received the B.S. degree in electronics and computer engineering from Hanyang University, Seoul, South Korea, in 2010, where he is currently pursuing the Ph.D. degree. His research interests include driving circuits for microdisplay applications and readout circuits for sensor applications.

**SEONG-KWAN HONG** received the Ph.D. degree in electrical engineering from the Georgia Institute of Technology, Atlanta, GA, USA, in 1994.

He is currently a Research Professor with Hanyang University, Seoul, South Korea.

**OH-KYONG KWON** (S'83–M'88) received the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, USA, in 1988.

He is currently a Professor with the Department of Electronic Engineering, Hanyang University, Seoul, South Korea.