Received 23 May 2019; revised 26 August 2019 and 7 October 2019; accepted 11 October 2019. Date of publication 22 October 2019; date of current version 6 December 2019. The review of this article was arranged by Editor H. T. E. Teo.

Digital Object Identifier 10.1109/JEDS.2019.2948648

# Leading-Edge Thin-Layer MOSFET Potential Modeling Toward Short-Channel Effect Suppression and Device Optimization

FERNANDO ÁVILA HERRERA<sup>® 1</sup> (Member, IEEE), YOKO HIRANO<sup>1</sup>, TAKAHIRO IIZUKA<sup>® 1</sup> (Member, IEEE), MITIKO MIURA-MATTAUSCH<sup>® 1</sup> (Fellow, IEEE), HIDEYUKI KIKUCHIHARA<sup>1</sup>,

DONDEE NAVARRO<sup>® 1</sup> (Member, IEEE), HANS JÜRGEN MATTAUSCH<sup>® 1</sup> (Senior Member, IEEE),

## AND AKIRA ITO<sup>2</sup>

1 HiSIM Research Center, Hiroshima University, Kagamiyama, Higashihiroshima 739-8530, Japan 2 Department of Design, Broadcom Inc., Irvine, CA 92618, USA

CORRESPONDING AUTHOR: F. Á. HERRERA (e-mail: herrera@hiroshima-u.ac.jp)

**ABSTRACT** A novel compact model has been developed, which considers the origin of the short-channel effect (SCE) on the basis of the potential distribution along the channel. Thus an enlargement of the insight into SCE suppression in advanced thin-layer MOSFETs is enabled. The model is extended to include the diffusion region resistance effects caused by the drain-side doping by applying the methodology of the industry-standard high-voltage MOSFET model HiSIM\_HV. Usage for studying possible device optimizations revealed that clear improvements in the subthreshold characteristics due to suppression of SCEs can be achieved by slightly increasing the drain-side diffusion resistance. Disadvantageous effects on the device and circuit performances were found to be negligible.

**INDEX TERMS** Short channel transistor, compact modeling, double-gate MOSFET, subthreshold characteristics.

#### I. INTRODUCTION

Scaling-down of the MOSFET size continues further to fulfill in particular low-power and increased integrationdensity requirements. For the high integration densities, 3D chip-bonding techniques have also been developed [1]-[7]. In addition to the integration-density increase, however, a device-performance enhancement is of course desirable. As solutions for both requirements, thin-layer MOSFETs have been developed such as extremely thin SOI MOSFET (ETSOI) [8]-[12], multi-gate MOSFETs (MG-MOS) with thin silicon layer-thickness  $(t_S)$  [13]–[17], or FinFETs [13], [18]-[21]. Nevertheless, even such very thin layer devices are still suffering from the shortchannel (SC) effects in spite of an aggressive substratethickness reduction [22]–[25]. Our present investigation aims at analyzing the reasons for the SC effects observed in these leading-edge device technologies and at developing a deviceoptimization scheme for enabling further suppression of the

SC effects. The focus is given on MG-MOSFETs, which provide the common structure for any type of thin-layer MOSFETs.

The scaling rule of  $L/t_S \approx 2.5$ , where *L* is the channel length and  $t_S$  is the substrate thickness, has been proposed for MG-MOSFETs and has been verified to preserve the principle MOSFET function of the gate control [26]. By reducing *L*, the potential distribution along the channel direction becomes non-negligible. Several analytical models usually applied a semi-parabolic function of the potential distribution to describe the SC effects along the channel, leading to the traditional solution originally developed by Young 30 years ago [27], [28]. We have developed a compact description of the SC effects by considering the complete channelpotential distribution, which results from the superposition of the contributions due to source/channel junction, channel part controlled by gate, and channel/drain junction [29]. This SCE-model has been verified to reproduce the SC effects

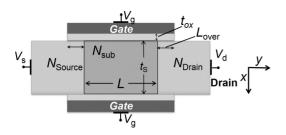

FIGURE 1. DGMOS device structure and main device parameters.

accurately. Here we extend our previous SCE-model [30], for inclusion of the diffusion resistance effects, which is realistic for actually fabricated devices. Change in drain doping concentration N<sub>Drain</sub> leads to an increase/decrease of the resistance in the drain-side diffusion region. The double-gate (DG) MOS is applied as a specific MG-MOS for the quantitative optimization, because the gate contributions from other sides is usually not large and most of the device performance is determined by the control from two opposite gates. The present investigation is based on 2D numerical device simulations [31], where microscopic physical insights are available for any structural variations. The developed extended SCE-model is implemented into HiSIM, an industry-standard compact model developed on the basis of the complete potential distribution [32]. An improved device structure is studied, which has a reduced drain doping concentration respect to the highly doped region typically used. Device optimization is achieved in order to reduce the impact of the SC effects without seriously affecting the ON-state performance of the transistor. Important parameters, such as Subthreshold-slope (SS), Drain Induced Barrier Lowering (DIBL), OFF/ONstate current ( $I_{OFF}/I_{ON}$ ), effective current ( $I_{eff}$ ), maximum transconductance  $(g_{m,max})$ , output conductance  $(g_{ds})$  are compared to analyze the improvements obtained after optimization.

This paper is organized as follows: Section II presents main performance features of the studied DG-MOSFET. The compact SCE-model development is reported in Section III. The device optimizations for suppressing the SC effects are presented and discussed in Sections IV and V. Finally, Section VI concludes our investigation.

### **II. DEVICE AND PERFORMANCE CHARACTERISTICS**

The studied DG-MOSFET structure is depicted in Fig. 1 together with the main device parameters. Table 1 lists the device-parameter values used in this work. High impurity concentrations at source ( $N_{\text{Source}}$ ) and drain ( $N_{\text{Drain}}$ ) diffusion regions are normally important to keep the device operation within ideal conditions by avoiding the resistance effects. A high impurity concentration in the diffusion regions induces only negligible potential drop within these regions, resulting also in a negligible depletion extensions into the source/drain diffusion regions. The potential distribution along the channel direction in the middle of the substrate

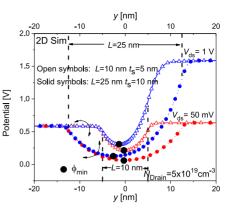

**FIGURE 2.** 2D numerical device simulation results of potential distributions in the middle of the substrate along the channel of the studied scaled devices at the gate voltage  $V_{gs}$  of -0.2V with channel lengths *L* of 10nm and 25nm.

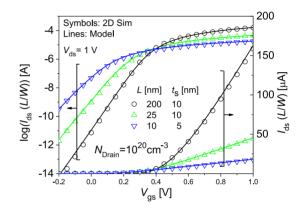

FIGURE 3. Drain current characteristics for different scaled technologies normalized by the channel length *L* and the width *W*. Device parameters are listed in Table 1.

TABLE 1. Device parameters used in simulations.

| Symbol              | Quantity                     | Value                                                    |

|---------------------|------------------------------|----------------------------------------------------------|

| L                   | Channel length               | 200, 25, 10 nm                                           |

| W                   | Channel width                | 1 μm                                                     |

| $t_{\rm S}$         | Silicon thickness            | 10, 5 nm                                                 |

| $t_{\rm ox}$        | Equivalent Oxide Thickness   | 1.5 nm                                                   |

| $L_{\rm over}$      | Gate overlap length          | 10 nm                                                    |

| $N_{\rm sub}$       | Channel doping concentration | $10^{15} \text{ cm}^{-3}$                                |

| $N_{\text{Source}}$ | Source doping concentration  | $10^{20} \text{ cm}^{-3}$                                |

| $N_{\text{Drain}}$  | Drain doping concentration   | $1 \times 10^{20}$ , $5 \times 10^{19}$ cm <sup>-3</sup> |

in depth, obtained from 2D device simulation results, is shown in Fig. 2 for two different channel lengths L. The resulting *I*-V characteristics of 2D device simulations are depicted in Fig. 3 for different L lengths for studied devices (see Fig. 1). It can be seen that the subthreshold slope is still further degraded, even when L is scaled down together with an additional  $t_S$  reduction. The potential distribution within the substrate along the channel is confirmed to accurately describe the SC effects.

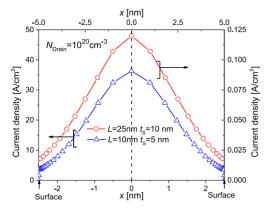

**FIGURE 4.** Current densities across the substrate between the 2 gate surfaces in the middle of the channel y = 0, at  $V_{gs} = -0.2V$  and  $V_{ds} = 50$  mV.

### III. COMPACT SCE MODELING AND ITS VERIFICATION A. BASIC MODELING OF SC EFFECTS

As can be concluded from Fig. 4 the main origin of the SC effects is the deeper current flow in the *x* direction around the middle of the substrate. The ratio of this current flow deeper in the substrate diminishes according to the gate voltage  $V_{gs}$  increase, namely according to the formation of an inversion layer at surface. A relatively large source-drain leakage current occurs around the substrate middle when the unavoidable electric field, induced between source and drain diffusion regions, exceeds the field induced by  $V_{gs}$ , which then leads to a punch-through effect. In principle the lateral-electric-field contribution can be modeled by considering the 2D Poisson equation

$$\frac{d^2\phi(x,y)}{dx^2} + \frac{d^2\phi(x,y)}{dy^2} = \frac{qN_{\rm sub}}{\varepsilon_{\rm S}}$$

(1)

where  $\phi(x,y)$  is the potential at the channel position (x, y), and  $\varepsilon_S$  is the semiconductor permittivity. A compact SCEmodel has been developed by focusing on the potential distribution along the channel at the depth where the maximum-current flow occurs. For modeling this potential distribution, the overlap of the two junction distributions, one at source/channel and other at channel/drain, and the gate-control induced potential determined by  $V_{gs}$  are superimposed. The resulting total potential distribution for a long-channel transistor is approximated by a cubic function of position y

$$\phi(y) = A_0 \cdot (y + B_0)^3 + C_0 \tag{2}$$

where,  $A_0$ ,  $B_0$  and  $C_0$  are model parameters, which are mostly determined by the junction profile. Thus the values of these model parameters are written as a function of the electric field induced in the junctions summarized in Table 2. By reducing the channel length the two potential distributions at the junctions start to overlap, which leads to an increase of the minimum potential  $\phi_{min}$  along the channel (see Fig. 2). This described mechanism is exactly the origin TABLE 2. Analytical description and explanations used in model equations.

| Parameter                    | Quantity                   | Value                                                                       |

|------------------------------|----------------------------|-----------------------------------------------------------------------------|

| $A_0$                        | Potential gradient         | $(V_{\rm biSource} - \phi_{\rm min}) / (L_0/2)^3$                           |

| $B_0$                        | Position of potential      | $\mathcal{Y}_{\min}$                                                        |

|                              | minimum                    |                                                                             |

| $C_0$                        | Potential minimum          | $\phi_{\min}$                                                               |

| $L_0$                        | Minimum long-channel       | Value to extract.                                                           |

|                              | length that preserves no   |                                                                             |

|                              | subthreshold degradation   |                                                                             |

| $\mathcal{Y}_{\mathrm{sym}}$ | Auxiliary variable         | $L/2 - \frac{2 \cdot (V_{biDrain} - V_{biSource})}{E_{Source} + E_{Drain}}$ |

| ${\cal Y}_{ m min}$          | Potential minimum position | $-L/4 + y_{sym}/2$                                                          |

| $V_{biSource}$               | Built in potential at      |                                                                             |

|                              | source/channel junction    |                                                                             |

| $V_{ m biDrain}$             | Built in potential at      |                                                                             |

|                              | drain/channel junction     |                                                                             |

of the SC effects. The final SCE-model equations are [29].

$$\Delta\phi_{\min}(V_{\rm gs}, V_{\rm ds}, L) = -2 \cdot A_0 \cdot \left(y_{\rm min} - \frac{L_0 - L}{2}\right)^3 \quad (3)$$

where  $\Delta \phi_{\min}$  is the potential-minimum increase in comparison to the long-channel device, and  $y_{\min}$  is the position where this minimum potential occurs.  $y_{\min}$  is determined by the balance between the fields at the source/channel and the channel/drain junctions as

$$y_{\min} = -\frac{V_{ds}}{E_{\text{Source}} + E_{\text{Drain}}} \tag{4}$$

The electric fields  $E_{\text{Source}}$  and  $E_{\text{Drain}}$  at source and drain junctions, respectively, are determined by the impurity profiles at these junctions and  $V_{\text{ds}}$ . The potential minimum  $\phi_{\text{min}}$ for the long-channel transistor is calculated by solving the Poisson equation. For the long-channel transistor this value is practically independent of the drain voltage ( $V_{\text{ds}}$ ). However, for a short-channel case the  $\phi_{\text{min}}$  value is influenced strongly by  $V_{\text{ds}}$  additionally, due to the overlap between the potential distribution at source/channel and channel/drain junctions.

The modeled  $\Delta \phi_{\min}$  has been implemented into HiSIM\_MG as the lateral potential distribution in the form [33], [34]

$$V'_{\rm G} = V_{\rm gs} - V_{\rm FB} + \Delta \phi_{\rm min} \tag{5}$$

which is used to calculate the value of the surface potential  $f_S$  at x = 0 by solving the Poisson equation together with the Gauss Law

$$\phi_{\rm S}(y) = V'_{\rm G} + \frac{Q_{\rm sem}(y)}{C_{\rm ox}} \tag{6}$$

where  $Q_{\text{sem}}$  is the total charge induced in the semiconductor channel, which is a function of  $\phi_{\text{S}}$ .  $C_{\text{ox}} = \varepsilon_{\text{ox}}/t_{\text{ox}}$  is the gate capacitance per unit of area for oxide permittivity  $\varepsilon_{\text{ox}}$ . This implicit function is solved iteratively using a 1D Newton method implemented in Verilog-A, an accurate initial analytical value is used to increase the speed of calculation with very low cost in terms of time. Once  $f_{\text{S}}$  is determined

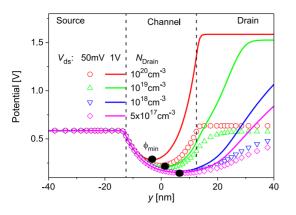

**FIGURE 5.** Potential distribution along the channel in the substrate middle for different drain doping concentrations  $N_{\text{Drain}}$  at  $V_{\text{ds}} = 50$ mV and 1V by fixing  $V_{\text{gs}} = 0$ . The studied device parameters are L = 25nm,  $t_{\text{s}} = 10$ nm,  $t_{\text{ox}} = 1.5$ nm and  $N_{\text{sub}} = 10^{15}$  cm<sup>-3</sup>.

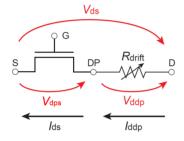

FIGURE 6. MOSFET modeling including the bias-dependent drain-resistance effect.

as a function of bias conditions, all device performances are written as a function of these potential values. Since the potential distribution is known, the drain current can be written by considering both the diffusion and the drift component. Particularly, in the subthreshold regime the diffusion contribution dominates the device characteristics.

#### **B. INCLUSION OF RESISTANCE EFFECT**

We have further extended the SCE-model to include the resistance effect of the diffusion regions, which is needed for measured-data reproduction of fabricated devices. The potential distributions from 2D device simulation are depicted in Fig. 5 for different drain-side doping concentrations, i.e., different drain-diffusion resistances and for two different  $V_{ds}$  values. It can be seen that the potential distribution extends deep into the drain region, when  $N_{Drain}$  reduces. According to the potential-distribution extension into the drain region, a reduction of the minimum potential value  $f_{min}$ , which is the main origin of the SC effects, is observed. This means a suppression of the SC effects [29] is achieved.

Modeling of the potential-distribution extension into the drain is done by using the HiSIM\_HV modeling concept [35], as schematically illustrated in Fig. 6. Due to the resistive drain region, the major potential drop for the potential applied between source and drain occurs within the drain diffusion region. This feature of the potential distribution is modeled by introducing the internal node DP obtained by an iterative solution. The position of DP is where the gate control is diminished and the field induced within the resistive drain-side diffusion region drives the current flow. The difference of potential between the drain terminal with applied voltage  $V_{\rm ds}$  and the node DP is the potential drop along the resistance  $R_{\rm drift}$ . Thus model parameters of the diffusion region are mostly related to the impurity concentration in this region, and the potential-distribution feature is strongly influenced by the impurity-concentration difference between the channel and the diffusion region.

Eq. (6) is solved within the framework of the HiSIM\_HV modeling. Namely, the node-DP potential is determined so that the intrinsic current density determined by the conventional MOSFET function becomes equal to that flowing within the resistive diffusion region [35].

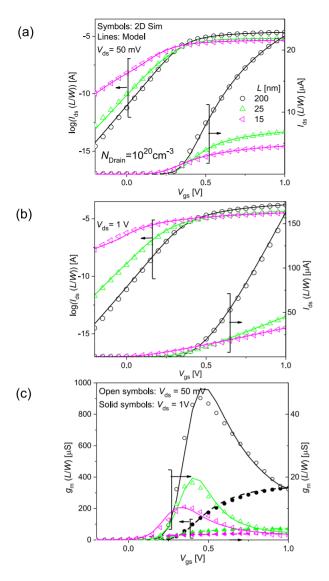

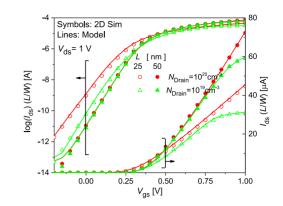

## C. MODEL VERIFICATION

To verify the developed model, calculated I-V characteristics are compared to those of 2D-device simulation results [31]. Silicon and Silicon Dioxide are used as semiconductor and oxide materials. Fig. 7 compares the studied devices with  $t_s = 10$ nm for different L without the draindiffusion-resistance effect. For the shortest channel length, a huge leakage current in subthreshold region is observed. This device with L=15nm, presents high degradation due to SC effects, which is never used for real applications. Non-smoothness is observed only for extreme cases, the limitation of the developed model is  $L > 2t_S$ , when the normal MOSFET control is maintained as the scaling rule determines. Fig. 8 shows the comparison using the same technology but with the diffusive drain resistance effect. It is seen that the SC effect is obviously reduced with reduced  $N_{\text{Drain}}$ , which is well reproduced with the developed model. Low drain doping concentration in the drain side can benefit the subthreshold region ensuring the turn-off of the transistor, however, the transistor will drive a lower current in the ON-state condition due to the potential drop within the low doped drain region. Influence of the drain resistance effect for SCE-suppression is discussed in the next section.

## **IV. DEVICE OPTIMIZATION**

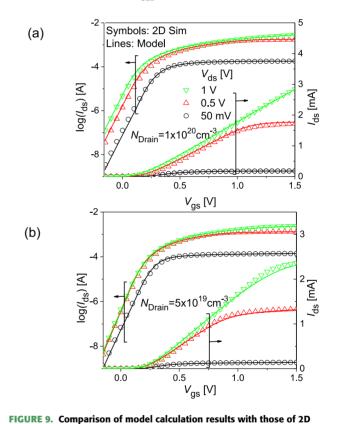

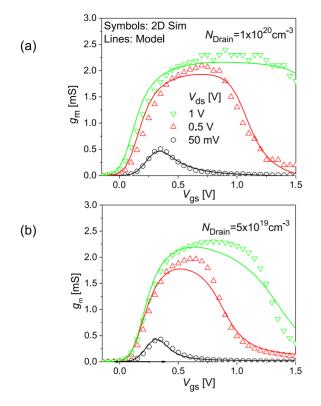

With use of the SCE-model including the diffusion-resistance effects, the device optimization for further suppressing the SC effect is investigated. For this purpose, we have fixed the device parameters to the values shown in Table 1 and only  $N_{\text{Drain}}$  is varied. Figs. 9 and 10 compare the device characteristics of a transistor with  $t_s = 5$ nm and L = 10nm for different bias conditions and two different drain doping concentrations,  $N_{\text{Drain}} = 1 \times 10^{20}$  and  $5 \times 10^{19}$  cm<sup>-3</sup>. The subthreshold characteristics are strongly improved with the  $t_s$  reduction in comparison to the  $t_s = 10$ nm case (see Fig. 7). However, the short-channel effect is still observable in the  $V_{ds}$  dependence of the subthreshold region. Reduction in drain doping clearly improves the immunity of the device to SC effects.

**FIGURE 7.** Transfer characteristics at (a)  $V_{ds} = 50$ mV and (b)  $V_{ds} = 1$ V for different channel length *L*. (c) Transconductances at  $V_{ds} = 50$ mV and 1V. The studied device parameters are  $t_{S} = 10$ nm,  $t_{ox} = 1.5$ nm and  $N_{sub} = 10^{15}$  cm<sup>-3</sup>.

**FIGURE 8.** Comparison of *I-V* characteristics with 2D device simulation and developed model at  $V_{ds} = 1V$  for different drain doping concentrations and channel lengths. The studied device parameters are  $t_{S} = 10$ nm,  $t_{ox} = 1.5$ nm and  $N_{sub} = 10^{15}$  cm<sup>-3</sup>.

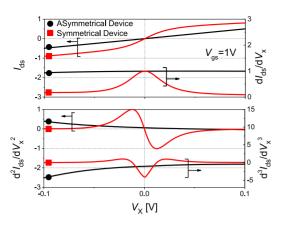

Fig. 11 shows the output characteristics and conductance of the same devices, where clear resistance effect is detected, namely the quasi-saturation effect is already observed for the  $N_{\text{Drain}} = 5 \times 10^{19} \text{cm}^{-3}$  case. A Gummel Symmetry Test is performed to both devices when a set of symmetrical ( $N_{\text{Drain}} = N_{\text{Source}}$ ) and asymmetrical ( $N_{\text{Drain}} < N_{\text{Source}}$ ) device parameters are used. Fig. 12 shows the results, the model presents smoothness around the  $V_{\text{ds}} = 0$  and symmetry for a symmetrical device. On the case of the asymmetrical device, the test helps to show the continuity around the origin and asymmetry is expected due to the asymmetry of the device.

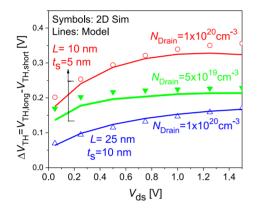

Fig. 13 compares the threshold-voltage shift  $\Delta V_{\text{th}}$  of the studied transistors in comparison to the long-channel  $V_{\text{th}}$  as a function of  $V_{\text{ds}}$ , which gives a measure for the SC effects.

device simulation for transfer characteristics between devices with (a)  $N_{\text{Drain}} = 1 \times 10^{20} \text{ cm}^{-3}$  and (b)  $N_{\text{Drain}} = 5 \times 10^{19} \text{ cm}^{-3}$  at different  $V_{\text{ds}}$  cases. The studied device parameters are L = 10 nm,  $t_{\text{S}} = 5 \text{ nm}$ ,  $t_{\text{ox}} = 1.5 \text{ nm}$  and  $N_{\text{sub}} = 10^{15} \text{ cm}^{-3}$ .

The threshold voltage is determined by the GLME method, which provides more reliable  $V_{\text{th}}$  values than the constant current method [36]. Since the  $L/t_{\text{s}}$  ratio for the L = 10nm case is smaller than that for the L = 25nm case, the  $\Delta V_{\text{th}}$ difference from small to large  $V_{\text{ds}}$  becomes larger in spite of the  $t_{\text{s}}$  reduction. The result with a reduced impurity concentration of the drain diffusion region  $N_{\text{Drain}}$  from  $1 \times 10^{20}$  cm<sup>-3</sup> to  $5 \times 10^{19}$  cm<sup>-3</sup> for the L = 10nm case is also depicted in Fig. 13, showing an obvious reduction of  $V_{\text{ds}}$  dependence,

**FIGURE 10.** Comparison of model calculation results with those of 2D device simulation for transconductance characteristics between devices with (a)  $N_{\text{Drain}} = 1 \times 10^{20} \text{ cm}^{-3}$  and (b)  $N_{\text{Drain}} = 5 \times 10^{19} \text{ cm}^{-3}$  at different  $V_{\text{ds}}$  cases. The studied device parameters are L = 10 nm,  $t_{\text{S}} = 5 \text{ nm}$ ,  $t_{\text{ox}} = 1.5 \text{ nm}$  and  $N_{\text{sub}} = 10^{15} \text{ cm}^{-3}$ .

i.e., the SC effect. The reason is attributed to the fact that the potential increase due to the increased  $V_{ds}$  is absorbed within the drain diffusion region as can be seen in Fig. 5, so that the potential minimum is decreased accordingly.

In order to observe the differences between the studied devices, model and simulation results of important parameters are compared in Table 3. High improvements in *SS* and *DIBL* are major achievements.

As the drain voltage increases, the potential drop occurs mostly in the resistive drain diffusion region, suppressing the lateral electric field increase in the channel region, and as a consequence the better  $V_{\text{th}}$  characteristics for high  $V_{\text{ds}}$ is achieved.

A specific attention has to be paid to the drain doping region, since a high resistive region affects negatively the ON state performance. The OFF/ON state current  $I_{OFF}/I_{ON}$ is presented in Table 3 as well. A ten times reduction in the OFF current is achieved, which reduces the leakage power consumption of the transistor. On the other hand,  $I_{ON}$  shows a very small difference between two devices, which results in no big penalties in the ON state by the slight reduction of  $N_{\text{Drain}}$ . The effective drain current  $I_{\text{eff}}$  is also compared.  $g_{\text{m,max}}$  used for analog design presents similar values for the two presented cases.

TABLE 3. Benchmarking for optimized/non-optimized device.

|                  |                                            | Device I: Non-                             | Device II:                                        |

|------------------|--------------------------------------------|--------------------------------------------|---------------------------------------------------|

|                  |                                            | optimized                                  | Optimized                                         |

| Symbol           | Quantity                                   | L=10nm                                     | L=10nm                                            |

| -                |                                            | $N_{\text{Drain}}=10^{20} \text{ cm}^{-3}$ | $N_{\rm Drain} = 5 \times 10^{19} {\rm ~cm}^{-3}$ |

|                  |                                            | [Sim/Model]                                | [Sim / Model]                                     |

| SS               | Subthreshold slope                         | 93 / 95                                    | 83.7 / 86.5                                       |

|                  | [mV/dec]                                   |                                            |                                                   |

| DIBL             | Drain Induced                              | 144.36 / 177.26                            | 53.7 / 55.1                                       |

|                  | Barrier Lowering                           |                                            |                                                   |

|                  | $[mV \cdot V^{-1}]$                        |                                            |                                                   |

| ${V}_{ m th}$    | Threshold Voltage                          | 0.234 / 0.22                               | 0.23 / 0.212                                      |

|                  | [V]                                        |                                            |                                                   |

| $I_{\text{OFF}}$ | Off-current $[\mu A]$                      | 4.78 / 5.3                                 | 0.446 / 0.290                                     |

|                  | $I_{\rm ds}(V_{\rm gs}=0, V_{\rm ds}=1V)$  |                                            |                                                   |

| $I_{\rm ON}$     | On-current [mA]                            | 1.76 / 1.78                                | 1.67 / 1.63                                       |

|                  | $I_{\rm ds}(V_{\rm gs}=1V, V_{\rm ds}=1V)$ |                                            |                                                   |

| $I_{\rm eff}$    | Effective current                          | 1.05 / 1.11                                | 0.886 / 0.895                                     |

|                  | [mA]                                       |                                            |                                                   |

| $g_{m,max}$      | Maximum                                    |                                            |                                                   |

|                  | transconductance at                        | 2.1 / 1.93                                 | 1.96 / 1.77                                       |

|                  | $V_{ds}=1V [mS]$                           |                                            |                                                   |

| $g_{ m ds}$      | Conductance at                             |                                            |                                                   |

|                  | $V_{gs} = V_{ds} = 1 V [mS]$               | 0.798 / 0.66                               | 1.62 / 1.54                                       |

|                  |                                            |                                            |                                                   |

**FIGURE 11.** Comparison of model calculation results with those of 2D device simulation for output characteristics between devices with (a)  $N_{\text{Drain}} = 1 \times 10^{20} \text{ cm}^{-3}$  and (b)  $N_{\text{Drain}} = 5 \times 10^{19} \text{ cm}^{-3}$  at different  $V_{\text{ds}}$  cases. The studied device parameters are L = 10 nm,  $t_{\text{S}} = 5 \text{ nm}$ ,  $t_{\text{ox}} = 1.5 \text{ nm}$  and  $N_{\text{sub}} = 10^{15} \text{ cm}^{-3}$ .

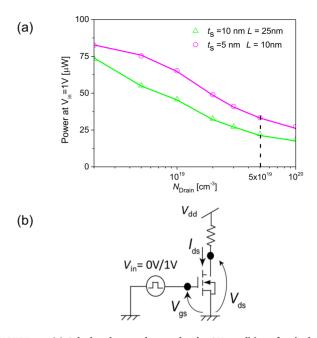

It is known that the SC effects cause the device-reliability reduction. Therefore, a lot of effort has been paid to reduce the SC effects [37], [38]. Since the drain resistance increase causes a degradation in device performances, the tradeoff between the SCE reduction and the device-performance reduction must be investigated. Fig. 14 demonstrates the

**FIGURE 12.** Normalized Gummel symmetry test for the drain current of the studied symmetrical ( $N_{\text{Drain}} = N_{\text{Source}}$ ) and the asymmetrical ( $N_{\text{Drain}} < N_{\text{Source}}$ ) device structures as a function of the voltage difference  $V_{\chi} = (\text{Drain node voltage} - \text{Source node voltage})/2.$

**FIGURE 13.** Threshold-voltage shift  $\Delta V_{th}$  as a function of  $V_{ds}$  for three different transistors, demonstrating the SCE-reduction with reduced  $N_{\text{Drain}}$ . The studied device parameters are  $t_{ox} = 1.5$ nm and  $N_{sub} = 10^{15}$  cm<sup>-3</sup>.

conduction loss of the two devices compared in Fig. 13 as a function of  $N_{\text{Drain}}$ . The circuit used for the simulation is depicted in Fig. 14b. The conduction loss is calculated by multiplying the current flowing under the on condition and the internal drain voltage as

$$Power = V_{\rm ds} \cdot I_{\rm ds} = V_{\rm out} \cdot I_{\rm out} \tag{7}$$

As can be expected the power loss decreases as  $N_{\text{Drain}}$  increases. However, it is also seen that the reduction characteristic saturates as  $N_{\text{Drain}}$  approaches  $N_{\text{Drain}} = 1 \times 10^{20} \text{ cm}^{-3}$ . It is known that the value of  $1 \times 10^{20} \text{ cm}^{-3}$  is already conductive and no potential drop occurs. Fig. 14 confirms that  $N_{\text{Drain}} = 5 \times 10^{19} \text{ cm}^{-3}$  causes a small power-loss increase.

#### **V. DISCUSSION**

We demonstrated that the developed model can be well applied for device optimization to realize high circuit performance. Here the model accuracy is a key to achieve reliable results, which are dependent on an accurate potential distribution along the channel. However, the impurity profile

**FIGURE 14.** (a) Calculated power loss under the ON condition of a single N-MOS inverter with  $V_{in} = 1V$  as a function of  $N_{Drain}$ .  $V_{in}$  is the input voltage and  $V_{DD}$  is the power-supply voltage. (b) Circuit used for the power loss calculation. The studied device parameters are  $t_{ox} = 1.5$ nm and  $N_{sub} = 10^{15}$  cm<sup>-3</sup>.

at the diffusion-region/channel junction must be known for this purpose, which is generally a very hard task and the same problematic situation as encountered for 2D device simulation.

In order to enable the modeling of the potential distribution, the magnitude of the fields  $E_{\text{Source}}$  and  $E_{\text{Drain}}$  at source/channel and channel/drain junctions are required (see Table 2), which are determined by the impurity profiles at junctions. These data for junction fields and impurity profiles then determine the potential-distribution modeling by a cubic function with model parameters  $A_0$ ,  $B_0$ , and  $C_0$ . An advantage of such an analytical description for compact modeling in comparison to 2D-numerical device simulation is that measured SC effects, such as those shown in Fig. 13, allows to know the balance between the fields  $E_{\text{Source}}$  and  $E_{\text{Drain}}$ . This becomes possible, because the 2D impurity profile is reduced to just 1 dimension along the channel direction, where the device characteristic is mainly determined. In particular, the middle of the substrate is the most important position for determination of the device characteristics under the subthreshold condition.

The extension of the developed compact SCE-model for general MOSFETs can be done in a similar way by determining the position and path where the major current flow occurs, which, e.g., can be approximated by the diffusion region junction depth in case of the bulk MOSFET. For the DG-MOSFET with independent control by the two gate contacts, the position can be approximated by the ratio of the fields induced at the two independent gates. The proposed model approach is based on device-physics considering SC effects for the subthreshold region and several effects above threshold, such as mobility degradation due to vertical and lateral electric fields, velocity saturation and also resistance effect. Performance of experimental devices is basically controlled by such effects.

#### **VI. CONCLUSION**

A new and complete compact model for short-channel effects is introduced and can be applied for device and circuit optimization of any technology node. The core improvements come from the developed potential-based modeling of the subthreshold region, which is verified with several structural and device variations. The reported compact SCEmodel is suitable for multi-gate MOS devices. With the practical application of the proposed SCE-model it is verified that a slightly-resistive drain diffusion region can lead to a substantial suppression of SCEs without significantly sacrificing circuit and device performances.

#### REFERENCES

- W. R. Davis *et al.*, "Demystifying 3D ICs: The pros and cons of going vertical," *IEEE Des. Test. Comput.*, vol. 22, no. 6, pp. 498–510, Nov./Dec. 2005. doi: 10.1109/MDT.2005.136.

- [2] A. W. Topol *et al.*, "Three-dimensional integrated circuits," *IBM J. Res. Develop.*, vol. 50, no. 4.5, pp. 491–506, Jul. 2006. doi: 10.1147/rd.504.0491.

- [3] G. H. Loh, "3D-stacked memory architectures for multi-core processors," in *Proc. Int. Symp. Comput. Architect.*, Beijing, China, 2008, pp. 453–464. doi: 10.1109/ISCA.2008.15.

- [4] R. Ritzenthaler et al., "Vertically stacked gate-all-around Si nanowire CMOS transistors with reduced vertical nanowires separation, new work function metal gate solutions, and DC/AC performance optimization," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2018, pp. 21.5.1–21.5.4. doi: 10.1109/IEDM.2018.8614528.

- [5] W. J. Yu *et al.*, "Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters," *Nature Mater.*, vol. 12, no. 3, pp. 246–252, Mar. 2013. doi: 10.1038/NMAT3518.

- [6] M. M. Shulaker *et al.*, "Three-dimensional integration of nanotechnologies for computing and data storage on a single chip," *Nature*, vol. 547, no. 7661, pp. 74–78, Jul. 2017. doi: 10.1038/nature22994.

[7] P. Batude *et al.*, "3D sequential integration opportunities

- [7] P. Batude *et al.*, "3D sequential integration opportunities and technology optimization," in *Proc. IEEE Int. Interconnect Technol. Conf.*, San Jose, CA, USA, 2014, pp. 373–376. doi: 10.1109/IITC.2014.6831837.

- [8] A. Majumdar, Z. Ren, S. J. Koester, and W. Haensch, "Undopedbody extremely thin SOI MOSFETs with back gates," *IEEE Trans. Electron Devices*, vol. 56, no. 10, pp. 2270–2276, Oct. 2009. doi: 10.1109/TED.2009.2028057.

- [9] A. Majumdar *et al.*, "High-performance undoped-body 8-nm-thin SOI field-effect transistors," *IEEE Electron Device Lett.*, vol. 29, no. 5, pp. 515–517, May 2008. doi: 10.1109/LED.2008.920975.

- [10] A. Litty, S. Ortolland, D. Golanski, and S. Cristoloveanu, "Optimization of a high-voltage MOSFET in ultra-thin 14nm FDSOI technology," in *Proc. IEEE 27th Int. Symp. Power Semicond. Devices IC's (ISPSD)*, Hong Kong, 2015, pp. 73–76. doi: 10.1109/ISPSD.2015.7123392.

- [11] R. Carter *et al.*, "22nm FDSOI technology for emerging mobile, Internet-of-Things, and RF applications," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, 2016, pp. 2.2.1–2.2.4. doi: 10.1109/IEDM.2016.7838029.

- [12] T. B. Hook, "Fully depleted devices for designers: FDSOI and FinFETs," in *Proc. IEEE Custom Integr. Circuits Conf.*, San Jose, CA, USA, 2012, pp. 1–7. doi: 10.1109/CICC.2012.6330653.

- [13] J.-P. Colinge, Ed., FinFETs and Other Multi-Gate Transistors. New York, NY, USA: Springer, 2008. doi: 10.1007/978-0-387-71752-4.

- [14] I. Ferain, C. A. Colinge, and J.-P. Colinge, "Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors," *Nature*, vol. 479, no. 7373, pp. 310–316, Nov. 2011. doi: 10.1038/nature10676.

- [15] J. Conde, A. Cerdeira, M. Pavanello, V. Kilchytska, and D. Flandre, "3D simulation of triple-gate MOSFETs," in *Proc. 27th Int. Conf. Microelectron.*, Niš, Serbia, 2010, pp. 409–411. doi: 10.1109/MIEL.2010.5490454.

- [16] S. Barraud *et al.*, "Scaling of trigate junctionless nanowire MOSFET with gate length down to 13 nm," *IEEE Electron Device Lett.*, vol. 33, no. 9, pp. 1225–1227, Sep. 2012. doi: 10.1109/LED.2012.2203091.

- [17] M. Mohamed *et al.*, "Size effects and performance assessment in nanoscale multigate MOSFET structures," *J. Comput. Theor. Nanosci.*, vol. 6, no. 8, pp. 1927–1936, Aug. 2009. doi: 10.1166/jctn.2009.1248.

- [18] X. Huang et al., "Sub 50-nm FinFET: PMOS," in Int. Electron Devices Meeting Tech. Dig., Washington, DC, USA, 1999, pp. 67–70. doi: 10.1109/IEDM.1999.823848.

- [19] G. Pei, J. Kedzierski, P. Oldiges, M. Ieong, and E.C.-C. Kan, "FinFET design considerations based on 3-D simulation and analytical modeling," *IEEE Trans. Electron Devices*, vol. 49, no. 8, pp. 1411–1419, Aug. 2002. doi: 10.1109/TED.2002.801263.

- [20] M. Masahara et al., "Demonstration, analysis, and device design considerations for independent DG MOSFETs," *IEEE Trans. Electron Devices*, vol. 52, no. 9, pp. 2046–2053, Sep. 2005. doi: 10.1109/TED.2005.855063.

- [21] J.-P. Raskin, "FinFET and UTBB for RF SOI communication systems," *Solid State Electron.*, vol. 125, pp. 73–81, Nov. 2016. doi: 10.1016/j.sse.2016.07.004.

- [22] G. Tsutsui, M. Saitoh, T. Nagumo, and T. Hiramoto, "Impact of SOI thickness fluctuation on threshold voltage variation in ultrathin body SOI MOSFETs," *IEEE Trans. Nanotechnol.*, vol. 4, no. 3, pp. 369–373, May 2005. doi: 10.1109/TNANO.2005.846913.

- [23] R.-H. Yan, A. Ourmazd, and K. F. Lee, "Scaling the Si MOSFET: From bulk to SOI to bulk," *IEEE Trans. Electron Devices*, vol. 39, no. 7, pp. 1704–1710, Jul. 1992. doi: 10.1109/16.141237.

- [24] N. Pandey, H.-H Lin, A. Nandi, and Y. Taur, "Modeling of shortchannel effects in DG MOSFETs: Green's Function method versus scale length model," *IEEE Trans. Electron Devices*, vol. 65, no. 8, pp. 3112–3119, Aug. 2018. doi: 10.1109/TED.2018.2845875.

- [25] V. P. Trivedi and J. G. Fossum, "Scaling fully depleted SOI CMOS," *IEEE Trans. Electron Devices*, vol. 50, no. 10, pp. 2095–2103, Oct. 2003. doi: 10.1109/TED.2003.816915.

- [26] H. Oka, R. Tanabe, N. Sadachika, A. Yumisaki, and M. Miura-Mattausch, "Suppressed short-channel effect of double-gate metal oxide semiconductor field-effect transistor and its modeling," *Jpn. J. Appl. Phys.*, vol. 46, no. 4B, pp. 2096–2100, Apr. 2007. doi: 10.1143/JJAP.46.2096.

- [27] K. K. Young, "Short-channel effect in fully depleted SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 36, no. 2, pp. 399–402, Feb. 1989. doi: 10.1109/16.19942.

- [28] K. K. Young, "Analysis of conduction in fully depleted SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 36, no. 3, pp. 504–506, Mar. 1989. doi: 10.1109/16.19960.

- [29] F. Á. Herrera *et al.*, "Advanced Short-channel-effect modeling with applicability to device optimization—Potentials and scaling," *IEEE Trans. Electron Devices*, vol. 66, no. 9, pp. 3726–3733, Sep. 2019. doi: 10.1109/TED.2019.2931749.

- [30] F. A. Herrera *et al.*, "Compact modeling for leading-edge thinlayer MOSFETs with additional applicability in device optimization toward suppressed short-channel effects," in *Proc. Electron Devices Technol. Manuf. Conf. (EDTM)*, Singapore, 2019, pp. 29–31. doi: 10.1109/EDTM.2019.8731246.

- [31] ATLAS User's Manual, Silvaco, Inc., Santa Clara, CA, USA, Apr. 2018.

- [32] HiSIM: Hiroshima-University STARC IGFET Model. (May 23, 2018).

[Online]. Available: https://www.hisim.hiroshima-u.ac.jp

- [33] M. Miura-Mattausch, H. J. Mattausch, and T. Ezaki, *The Physics and Modeling of MOSFETs*. Singapore: World Scientific, 2008. doi: 10.1142/6159.

- [34] N. Sadachika, T. Murakami, H. Oka, R. Tanabe, H. J. Mattausch, and M. Miura-Mattausch, "Compact double-gate metal-oxidesemiconductor field effect transistor model for device/circuit optimization," *IEICE Trans. Electron*, vol. E91-C, pp. 1379–1381, Aug. 2008. doi: 10.1093/ietele/e91-c.8.1379.

- [35] H. J. Mattausch, M. Miyake, T. Iizuka, H. Kikuchihara, and M. Miura-Mattausch, "The second-generation of HiSIM\_HV compact models for high-voltage MOSFETs," *IEEE Trans. Electron Devices*, vol. 60, no. 2, pp. 653–661, Feb. 2013. doi: 10.1109/TED.2012.2225836.

- [36] A. Ortiz-Conde, F. J. G. Sánchez, J. J. Liou, A. Cerdeira, M. Estrada, and Y. Yue, "A review of recent MOSFET threshold voltage extraction methods," *Microelectron. Rel.*, vol. 42, nos. 4–5, pp. 583–596, Apr./May 2002. doi: 10.1016/S0026-2714(02)00027-6.

- [37] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deepsubmicrometer CMOS circuits," *Proc. IEEE*, vol. 91, no. 2, pp. 305–327, Feb. 2003. doi: 10.1109/JPROC.2002.808156.

- [38] Y.-C. Eng et al., "A new figure of merit, ΔV<sub>DIBLSS</sub> / (I<sub>d,sat</sub>/I<sub>sd,leak</sub>), to characterize short-channel performance of a bulk-Si n-channel FinFET device," *IEEE J. Electron Devices Soc.*, vol. 5, no. 1, pp. 18–22, Jan. 2017. doi: 10.1109/JEDS.2016.2626464.

**FERNANDO ÁVILA HERRERA** (M'17) received the Ph.D. degree in electrical engineering from CINVESTAV-IPN, Mexico City, in 2017.

He is currently a Post-Doctoral Researcher with the HiSIM Research Center, Hiroshima University, Japan, where he is involved in the device compact modeling development for circuit simulation.

**YOKO HIRANO** received the B.Eng. and M.Eng. degrees in electrical engineering from Hiroshima University, Higashihiroshima, Japan, in 2015 and 2017, respectively.

She is currently with Kubota Corporation, Osaka, Japan. Her current research interest includes ultrathin power MOSFET device.

**TAKAHIRO IIZUKA** (M'95) received the Ph.D. degree from Hiroshima University, Higashihiroshima, Japan, in 2013.

From 1986 to 2012, he was with the Semiconductor-Chip Manufacturing Industry, Japan. He is currently with the HiSIM Research Center, Hiroshima University.

**MITIKO MIURA-MATTAUSCH** (M'96–SM'00–F'07) received the D.Sc. degree from Hiroshima University, Higashihiroshima, Japan.

Since 1996, she has been a Professor with Hiroshima University, where she led Ultra-Scaled Device Laboratory.

**HIDEYUKI KIKUCHIHARA** was with the CAD Development Group, Oki Electric Industry, Tokyo, Japan, in 1974. Since 2007, he has been with the HiSIM Research Center, Hiroshima University, Higashihiroshima, Japan, where he is involved in the model development of HiSIM\_HV and HiSIM2, including the model release and user support.

**DONDEE NAVARRO** (M'00) received the Ph.D. degree in engineering from Hiroshima University, Higashihiroshima, Japan, in 2006.

From 2006 to 2016, he was with SILVACO Japan Company Ltd., Yokohama, Japan. He is currently an Associate Professor with the HiSIM Research Center, Hiroshima University, where he is involved in device models for circuit simulation.

**HANS JÜRGEN MATTAUSCH** (M'96–SM'00) received the Ph.D. degree from Stuttgart University, Stuttgart, Germany.

Since 1996, he has been a Professor with Hiroshima University, Higashihiroshima, Japan, where he is involved in very large scale integration design, nanoelectronics, and compact modeling.

**AKIRA ITO**, photograph and biography not available at the time of publication.