Received 26 February 2018; revised 26 March 2018; accepted 27 March 2018. Date of publication 6 April 2018; date of current version 19 April 2018. The review of this paper was arranged by Editor C.-M. Zetterling.

Digital Object Identifier 10.1109/JEDS.2018.2820729

# Direct Measurement of Active Near-Interface Traps in the Strong-Accumulation Region of 4H-SiC MOS Capacitors

PEYUSH PANDE<sup>®</sup>, SIMA DIMITRIJEV (Senior Member, IEEE), DANIEL HAASMANN, HAMID AMINI MOGHADAM, PHILIP TANNER (Member, IEEE), AND JISHENG HAN

Queensland Micro- and Nanotechnology Centre, Griffith University, Brisbane, QLD 4111, Australia CORRESPONDING AUTHOR: P. PANDE (e-mail: peyush.pande@griffithuni.edu.au)

This work was supported by SICC Material Company Ltd., China, as the industry partner in the Australian Research Council Linkage Project under Grant ARC LP 50100525.

**ABSTRACT** This brief presents direct electrical measurement of active defects in the strong-accumulation region of N-type 4H-SiC MOS capacitors, which corresponds to the strong-inversion region of N-channel MOSFETs. The results demonstrate the existence of an active defect in the gate oxide, located very close to the SiC surface, with localized energy levels between 0.13 eV and 0.23 eV above the bottom of the conduction band. The observed spatial and energy localizations indicates that this is a well-defined defect.

**INDEX TERMS** 4H-SiC MOSFET, N-type SiC MOS capacitor, gate oxide, near-interface traps, trap measurement.

## I. INTRODUCTION

Silicon carbide MOSFETs on 4H-SiC are now commercially available, performing beyond the theoretical limits of Si-based MOSFETs in terms of on resistance and blocking voltage. However, SiC MOSFETs are yet to reach the theoretical limits of SiC, the key problem being low channelcarrier mobility due to a high density of defects at or near the interface between SiC and the gate oxide [1]-[3]. The characterization of the interface between SiC and the gate oxide is typically based on capacitance and conductance measurements of N-type SiC MOS capacitors. These measurements are particularly sensitive in the depletion region, which has been adequate for the analysis of interface traps that are the dominant active defects in the case of Si-based MOS capacitors. Consequently, most of the characterization work for SiC-based capacitors has been focused on the depletion region [4], [5]. However, it has been shown recently that the active defects—the defects responsible for the low channel-carrier mobility in SiC MOSFETsare in the strong-inversion of SiC MOSFETs [6]-[15], which corresponds to the strong-accumulation region of N-type SiC MOS capacitors [9]. These defects are identified as near-interface traps (NITs) [6]-[11], [14]-[21].

Three different techniques have been used to measure these defects: 1) conductance-based measurement in accumulation [9], [10], 2) measurements of current transients [8], and 3) thermal dielectric relaxation current (TDRC) technique [20]-[23]. There are possible issues with the conductance measurements in accumulation, due to the potential impact of the contact resistance and also due to high sensitivity to the specific calibration of the measurement equipment. With regards to the transient-current measurements, they can only measure traps with response times longer than tens of milliseconds. The TDRC technique fills traps by biasing MOS capacitors in accumulation, but this technique is limited to detecting traps with energy levels below the bottom of the conduction band because thermal emission—as distinct from tunneling—creates the thermal dielectric relaxation current. Therefore, there is a need for an alternative method of measuring the effects of defects in the strong-accumulation region of N-type 4H-SiC MOS capacitors.

In this brief, we present a direct experimental demonstration of active defects in the strong-accumulation region of N-type 4H-SiC MOS capacitors, which corresponds to the strong-inversion region in the case of N-channel 4H-SiC

MOSFETs. The difference between measured alternating current through an MOS capacitor and the alternating current that corresponds to a trap-free MOS capacitor with a constant capacitance value is used to calculate the density of NITs as the active defects.

#### II. THE DIRECT MEASUREMENT METHOD

The voltage across a capacitor,  $v_C$ , is related to the current through the capacitor,  $i_C$ , by the following fundamental equation:

$$i_C = C \frac{dv_C}{dt} \tag{1}$$

The assumption of constant capacitance, C, in (1) is justified for the case of an ideal MOS capacitor in the accumulation region, especially for the case of small changes in the voltage  $v_C$ . If NITs impact the charging and discharging of the MOS capacitor due to a changing voltage  $v_C$ , then the measured current through the MOS capacitor,  $i_{C\text{-meas}}$ , will differ from the current given by (1). The difference between these two currents,  $\Delta i_C = i_C - i_{C\text{-meas}}$ , can be used to determine the density of NITs by the following equation:

$$D_{NIT} = \frac{1}{2kTqA} \int_{t_1}^{t_2} \Delta i_C(t) dt \tag{2}$$

In (2), the numerical integration of the current difference corresponds to captured/released charge from the NITs, which is divided by the capacitor area A and the electron charge q to obtain the density of NITs per unit area. Denoting the period of the sinusoidal signal by T, the integration limits are  $t_1 = 0$  and  $t_2 = T/2$  for the case of active NITs during capacitor charging, and  $t_1 = T/2$  and  $t_2 = T$  for the case of active NITs during capacitor discharging. Assuming that the energy width of NITs that are capturing and releasing electrons is 2kT [24], centered at the Fermi level, the density of NITs per unit area is divided by 2kT to obtain the density of NITs per unit area and per unit energy, labeled by  $D_{NIT}$ .

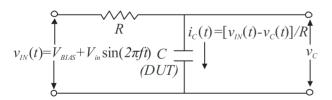

The direct measurement of current through a MOS capacitor can be performed by the *RC* circuit shown in Fig. 1.

FIGURE 1. Configuration of the measurement circuit with R as an external resistor and C as the device under test (DUT).

The relationship between an arbitrary input voltage,  $v_{IN}$ , and the measured voltage across the capacitor,  $v_C$ , is

$$v_C = v_{IN} - Ri_C \tag{3}$$

From (1) and (3), the following differential equation is obtained:

$$\frac{dv_C}{dt} + \frac{1}{RC}v_C = \frac{1}{RC}v_{IN} \tag{4}$$

The solution of differential equation (4) is

$$v_C(t) = \exp\left(-\frac{t}{RC}\right) \left[ A_0 + \frac{1}{RC} \int_0^t v_{IN}(t_S) \exp\left(\frac{t_S}{RC}\right) dt_S \right]$$

(5)

where  $A_0$  is the integration constant and  $t_S$  is the variable time within the integration interval  $(0 \le t_S \le t)$ . The measured input voltage  $v_{IN}(t)$  is numerically integrated according to (5) to obtain the value of the voltage across the capacitor,  $v_C(t)$ , for the case of  $D_{NIT} = 0$ . The current through the MOS capacitor for the case of  $D_{NIT} = 0$  is obtained by the following equation:

$$i_C(t) = \frac{v_{IN}(t) - v_C(t)}{R} \tag{6}$$

The condition that the DC component of the capacitor current has to be zero is used to set the correct value of the integration constant  $A_0$ .

The described procedure can be used to obtain the current  $i_C(t)$  for arbitrary input voltages. However, high frequency sinusoidal signals are the most suitable because they minimize the signal distortion. In this work we have used sinusoidal input voltages, offset by a bias voltage  $V_{BIAS}$ :

$$v_{IN}(t) = V_{BIAS} + V_{in}\sin(2\pi f) \tag{7}$$

where f is the frequency of the applied sinusoidal voltage and  $V_{in}$  is the amplitude.

### III. EXPERIMENTAL DETAILS

Measurements were performed on N-type 4H-SiC MOS capacitors, used as the device under test (DUT) in the RC circuit shown in Fig. 1. The MOS capacitors were fabricated on N-type, silicon faced, 4H-SiC wafers with nitrogen doped epitaxial layer at the concentration of 10<sup>16</sup>cm<sup>-3</sup>. Prior to the oxidation, the sample was cleaned by standard Radio Corporation of America (RCA) procedure. The oxidation was performed at 1250°C in dry O<sub>2</sub> for 60 min and then annealed in nitric oxide for 60 min, also at 1250°C. The resulting oxide thickness was 45 nm. The thickness of the oxide was determined from the accumulation capacitance, which was measured by Agilent B1505A LCR meter. Following the oxidation, aluminum was sputtered and patterned by photolithography to form square MOS capacitors with the area of  $500x500 \mu m^2$  and surrounding area of more than ten times the area of square MOS capacitors, to enable top-to-top measurements. Sinusoidal input voltages were applied to the smaller area through the external resistor R by a Tektronix AFG1022 arbitrary function generator and MP 3086 DC power supply, whereas the larger surrounding area was connected to the electrical ground. To measure the voltage across the capacitor, a Tektronix DPO7104 oscilloscope with Tektronix P6139A oscilloscope probes was used. The use of unshielded wires was minimized to avoid the impact of parasitic inductances, which was possible up to the frequency of f = 8 MHz (confirmed by the use of a constant-value

VOLUME 6, 2018 469

ceramic capacitor as the DUT). The lowest measurement frequency was 10 kHz. The measurements were performed with continuous sinusoids, therefore the presented results are the repetitive currents at given frequency. The parasitic capacitance is taken into account by matching the  $i_C$  waveform to  $i_{C-meas}$ , measured with constant-value ceramic capacitor as the DUT. The bias voltage was changed from  $V_{BIAS} = 5 \text{ V}$ to 20 V whereas the amplitude of the input voltage was kept constant at  $V_{in} = 500$  mV. Different resistor values were used to maintain similar output voltages at all measurement frequencies:  $R = 180 \Omega$  for 5 MHz,  $R = 120 \Omega$ for 6 and 7 MHz, and  $R = 82 \Omega$  for 8 MHz. It should be noted that a large leakage current would appear as a conductance in parallel with the capacitor and would impact the measured current. We measured the DC leakage through the capacitor (DUT) and confirmed that it was insignificant in comparison to the measured signal current. All the measurements were performed at room temperature.

#### **IV. RESULTS AND DISCUSSION**

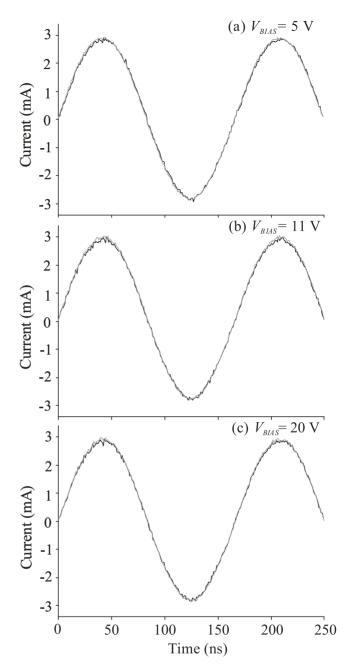

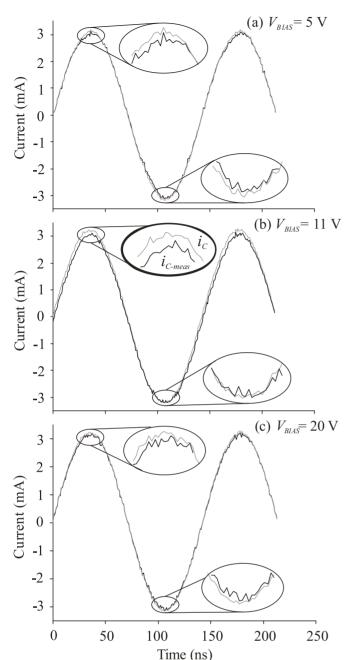

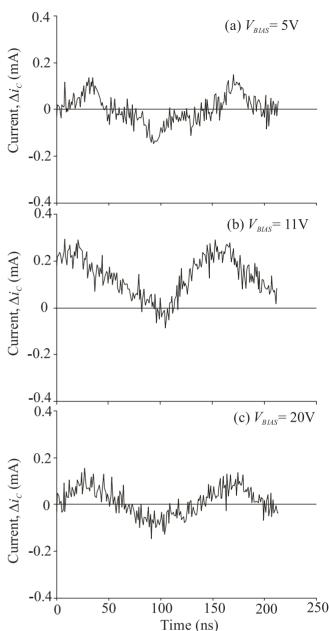

The typical measured current,  $i_{C\text{-meas}}$ , is shown by the black lines in Figs. 2 and 3 for f = 6 MHz and f = 7 MHz, respectively, along with the current  $i_C$  that corresponds to the constant-capacitance value C (the gray lines). The difference between  $i_{C-meas}$  and  $i_{C}$  is much larger at 7 MHz in comparison to 6 MHz. For the case of 7 MHz, the difference between these currents is the largest at  $V_{BIAS} = 11$  V, which can also be seen from the plots of  $\Delta i_C$  shown in Fig. 4. For the case of  $V_{BIAS} = 11$  V, it is clear that  $i_{C\text{-meas}}$  is smaller than  $i_C$  during charging of the capacitor, which indicates that the charging current is reduced by delayed emission of electrons from the NITs. The difference during discharging of the capacitor is much smaller, indicating that there is almost no delayed electron capturing to reduce the charging current. Multiple devices were measured to confirm the repeatability of the results. We have not observed larger measured current in comparison to the ideal current.

The observed impact of the bias voltage can be related to the surface position of the Fermi level,  $E_F$ , and the energy location of the active NITs,  $E_{NIT}$ . Because of the quantum confinement effect, the Fermi level is above the bottom of the conduction band,  $E_C$ , in the case of strong inversion of P-type SiC and accumulation of N-type SiC [9]. As a consequence, the energy levels of the active defects-centered around the Fermi level—are also above  $E_C$ , which means that these defects have to be NITs positioned near the SiC surface that trap and release electrons by tunneling. In [12], the quantum confinement effect is considered to calculate the areal density of electrons in strong-inversion  $(N_{inv})$  as a function of the position of the Fermi level  $E_F$ - $E_C$ . Taking into account that the energy bands of P-type SiC in stronginversion are very similar to the energy bands of N-type SiC in accumulation [9], we used the results from [12] for  $N_{inv}$  versus  $E_F$ - $E_C$  to determine the positions of the Fermi levels for different applied bias voltages in our samples. To do so, we replaced  $N_{inv}$  by  $N_{acc}$ , which was calculated by

FIGURE 2. The measured current (black lines) and the current corresponding to constant capacitance C (gray lines) at 6 MHz for (a) 5 V bias voltage, (b) 11 V bias voltage and (c) 20 V bias voltage.

the following equation:

$$N_{acc} = \frac{(V_{BIAS} - V_{FB}) C_{ox}}{q} \tag{8}$$

where  $V_{FB}$  is flat-band voltage and  $C_{ox}$  is oxide capacitance in accumulation per unit area. The value of the flat-band voltage was  $V_{FB} = 0$  V, as determined concurrently with the gate oxide thickness by fitting the theoretical to the measured C–V curve. This relationship between  $V_{BIAS}$  and  $N_{acc} \approx N_{inv}$ , combined with Pennington and Goldsman's

470 VOLUME 6, 2018

FIGURE 3. The measured current (black lines) and the current corresponding to constant capacitance C (gray lines) at 7 MHz for (a) 5 V bias voltage, (b) 11 V bias voltage and (c) 20 V bias voltage. The difference between these currents is the largest for 11 V bias voltage, indicating NITs with localized energy levels.

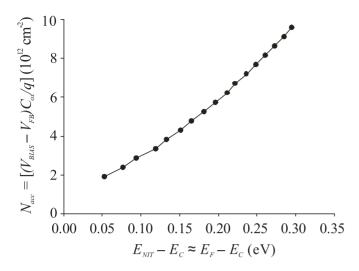

relationship between  $N_{inv}$  and  $E_F$ - $E_C \approx E_{NIT}$ - $E_C$ , enabled us to convert  $V_{BIAS}$  into  $E_{NIT}$ - $E_C$ , as shown in Fig. 5.

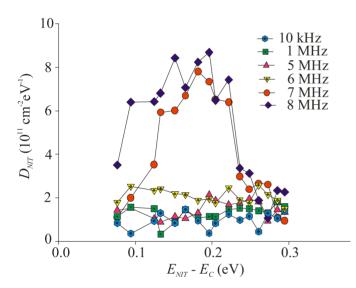

The energy distributions of  $D_{NIT}$ , calculated by (2) for the case of charging currents, are shown in Fig. 6. The first implication from the results shown in Fig. 6 is that the energy levels of the dominant NITs are localized between 0.13 eV to 0.23 eV above  $E_C$  indicating a well-defined defect. The results in Fig. 6 also show that the localized defect is spatially localized as well, appearing very close to

FIGURE 4. Current difference  $\Delta i_C = i_C - i_{C-meas}$  at 7 MHz for (a) 5 V bias voltage, (b) 11 V bias voltage and (c) 20 V bias voltage.

the SiC surface. We conclude this from the fact that there is a sharp increase in the  $D_{NIT}$  from about  $2x10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> to  $8x10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> when the frequency is increased from 6 MHz to 7 MHz. As mentioned previously, the delay of electron emission from the NITs is observed at 7 MHz, indicating that the emission time constant is approximately equal to the quarter of the signal period: 1/4f = 36 ns. The emission of these electrons at around the quarter of the period opposes the charging current, causing the smaller  $i_{C\text{-meas}}$  in comparison to the ideal case of  $D_{NIT} = 0$ . The quarter of the period in the case of the 6 MHz signal is 1/4f = 42 ns, which is a sufficiently long time for the NITs

VOLUME 6, 2018 471

FIGURE 5. Conversion of  $V_{BIAS}$  to  $E_{NIT}$ - $E_C$ , based on the data from [12] for the relationship between the electron density,  $N_{inv} \approx N_{acc}$ , and the position of the Fermi level,  $E_F$ - $E_C$ .

FIGURE 6. Measured density of near-interface traps.

to emit the captured electrons, as evidenced by the absence of significant reduction in  $i_{C-meas}$ . This sharp increase of  $D_{NIT}$  with emission time shorter than 42 ns corresponds to a sharp localization of NITs near the interface.

Although the result about the localisation of NITs is new, the range of  $D_{NIT}$  values obtained by the measurement technique presented in this paper are in a good agreement with the values of  $1x10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup>,  $9x10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> and  $1x10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> published in [14], [16], and [18], respectively.

The results of our direct measurements of the current through the DUT,  $i_{C\text{-meas}}$ , in response to sinusoidal voltage,  $v_{IN}$ , have an important implication for the capacitance and conductance measurements by commercial LCR meters. The LCR meters model the DUT by an equivalent capacitance and an equivalent conductance (or resistance). An implicit

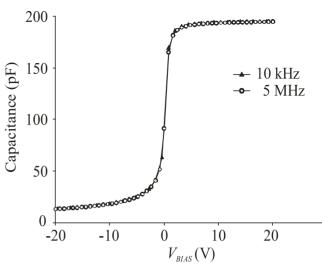

FIGURE 7. Capacitance-voltage curves of the measured MOS capacitors. For clarity the lowest and highest frequency C–V curves are shown. There was no difference observed in the C–V measurement at the following measurement frequencies: 10 kHz, 100 kHz, 1 MHz, 2 MHz, 3 MHz, 4 MHz, and 5 MHz.

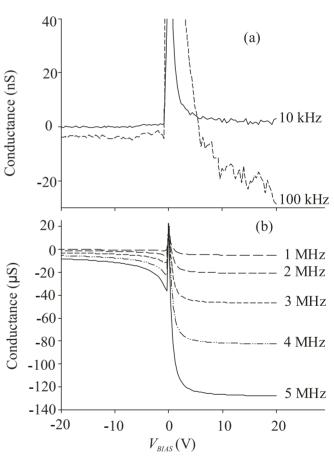

FIGURE 8. Conductance-voltage curves of the measured MOS capacitors: (a) 10 kHz and 100 kHz, (b) 1–5 MHz.

assumption in this approach is that the current through the DUT is sinusoidal with amplitude and phase shift corresponding to the values of the capacitance and conductance

472 VOLUME 6, 2018

in the equivalent circuit. Our direct measurement of the current through the DUT shows a distortion from the sinusoidal shape, which cannot be adequately represented by a simple phase shift due to a conductance in parallel with the capacitance C. A consequence is that the distorted sinusoid cannot be properly fitted by the LCR models to result in physically meaningful capacitance and conductance. We measured the MOS capacitors by Agilent B1505A LCR meter, and with careful calibration, we were able to obtain constant capacitance in accumulation up to 5 MHz (the Agilent frequency limit), as shown in Fig. 7. However, the corresponding conductance in accumulation appears as positive only at 10 kHz and then becomes negative at higher frequencies, as shown in Fig. 8. Although this does correlate with the fact that there is a small discrepancy between  $i_C$  and  $i_{C\text{-meas}}$ , the physical meaning of the conductance is lost. We assume that the fitting problem (impossibility to fit ideal sinusoid with a phase shift to measured distorted sinusoids) results in conductance calculations that are highly sensitive to small differences between  $i_C$  and  $i_{C\text{-meas}}$ .

#### V. CONCLUSION

In this brief, N-type 4H-SiC MOS capacitors are used to perform direct measurements of near-interface traps that capture channel electrons in SiC MOSFETs, reducing the average channel-carrier mobility. The measurement technique utilizes the difference between measured alternating current through an MOS capacitor and alternating current that corresponds to a trap-free MOS capacitor with a constant capacitance value. The measurements performed on nitrided gate oxides identified a defect with energy levels localized between 0.13 eV and 0.23 eV above the bottom of the conduction band, which is also spatially localized very close to the SiC surface.

#### **ACKNOWLEDGMENT**

This work was performed at the Queensland node of the Australia National Fabrication Facility (ANFF), a company established under the National Collaboration Research Infrastructure Strategy to provide nano and microfabrication facilities for Australia's researchers.

#### **REFERENCES**

- S. Dhar et al., "Inversion layer carrier concentration and mobility in 4H-SiC metal-oxide-semiconductor field-effect transistors," J. Appl. Phys., vol. 108, no. 5, pp. 1–5, Sep. 2010, doi: 10.1063/1.3484043.

- [2] F. Devynck, A. Alkauskas, P. Broqvist, and A. Pasquarello, "Charge transition levels of carbon-, oxygen-, and hydrogen-related defects at the SiC/SiO<sub>2</sub> interface through hybrid functionals," *Phys. Rev. B, Condens. Matter*, vol. 84, no. 23, pp. 1–18, Dec. 2011, doi: 10.1103/PhysRevB.84.235320.

- [3] J. M. Knaup et al., "Defects in SiO<sub>2</sub> as the possible origin of near interface traps in the SiC/SiO<sub>2</sub> system: A systematic theoretical study," *Phys. Rev. B, Condens. Matter*, vol. 72, no. 11, pp. 1–9, Sep. 2005, doi: 10.1103/PhysRevB.72.115323.

- [4] V. V. Afanas'ev, F. Ciobanu, G. Pensl, and A. Stesmans, "Contributions to the density of interface states in SiC MOS structures," in *Silicon Carbide: Recent Major Advances*, W. J. Choyke, H. Matsunami, and G. Pensl, Eds. Berlin, Germany: Springer, 2004, pp. 343–371, doi: 10.1007/978-3-642-18870-1\_14.

- [5] H. Yoshioka, T. Nakamura, and T. Kimoto, "Accurate evaluation of interface state density in SiC metal-oxide-semiconductor structures using surface potential based on depletion capacitance," *J. Appl. Phys.*, vol. 111, no. 1, pp. 1–5, Jan. 2012, doi: 10.1063/1.3673572.

- [6] H. A. Moghadam, S. Dimitrijev, J. Han, and D. Haasmann, "Active defects in MOS devices on 4H-SiC: A critical review," *Microelectron. Rel.*, vol. 60, pp. 1–9, Feb. 2016, doi: 10.1016/j.microrel.2016.02.006.

- [7] X. Zhang et al., "Characterization of near-interface traps at 4H-SiC metal-oxide-semiconductor interfaces using modified distributed circuit model," Appl. Phys. Exp., vol. 10, no. 6, pp. 1–4, May 2017, doi: 10.7567/APEX.10.064101.

- [8] H. A. Moghadam, S. Dimitrijev, J. Han, D. Haasmann, and A. Aminbeidokhti, "Transient-current method for measurement of active near-interface oxide traps in 4H-SiC MOS capacitors and MOSFETs," *IEEE Trans. Electron Devices*, vol. 62, no. 8, pp. 2670–2674, Aug. 2015, doi: 10.1109/TED.2015.2440444.

- [9] D. Haasmann and S. Dimitrijev, "Energy position of the active near-interface traps in metal-oxide-semiconductor field-effect transistors on 4H-SiC," *Appl. Phys. Lett.*, vol. 103, no. 11, pp. 1–3, Sep. 2013, doi: 10.1063/1.4821362.

- [10] R. Y. Khosa and E. Ö. Sveinbjörnsson, "Conductance signal from near-interface traps in n-type 4H-SiC MOS capacitors under strong accumulation," *Mater. Sci. Forum*, vol. 897, pp. 147–150, May 2017, doi: 10.4028/www.scientific.net/MSF.897.147.

- [11] M. Gurfinkel et al., "Characterization of transient gate oxide trapping in SiC MOSFETs using fast I-V techniques," IEEE Trans. Electron Devices, vol. 55, no. 8, pp. 2004–2012, Aug. 2008, doi: 10.1109/TED.2008.926626.

- [12] G. Pennington and N. Goldsman, "Self-consistent calculations for *n*-type hexagonal SiC inversion layers," *J. Appl. Phys.*, vol. 95, no. 8, pp. 4223–4234, Mar. 2004, doi: 10.1063/1.1687977.

- [13] V. Tilak, K. Matocha, and G. Dunne, "Electron-scattering mechanisms in heavily doped silicon carbide MOSFET inversion layers," *IEEE Trans. Electron Devices*, vol. 54, no. 11, pp. 2823–2829, Nov. 2007, doi: 10.1109/TED.2007.906929.

- [14] V. Tilak, K. Matocha, G. Dunne, F. Allerstam, and E. Ö. Sveinbjörnsson, "Trap and inversion layer mobility characterization using hall effect in silicon carbide-based MOSFETs with gate oxides grown by sodium enhanced oxidation," *IEEE Trans. Electron Devices*, vol. 56, no. 2, pp. 162–169, Feb. 2009, doi: 10.1109/TED.2008.2010601.

- [15] A. J. Lelis, R. Green, D. B. Habersat, and M. El, "Basic mechanisms of threshold-voltage instability and implications for reliability testing of SiC MOSFETs," *IEEE Trans. Electron Devices*, vol. 62, no. 2, pp. 316–323, Feb. 2015, doi: 10.1109/TED.2014.2356172.

- [16] H. A. Moghadam, S. Dimitrijev, J. S. Han, A. Aminbeidokhti, "Quantified D. Haasmann. density of active near interface 4H-SiC MOS capacitors," oxide traps in Mater. Sci. Forum, vol. 858, pp. 603 - 606, 2016, doi: 10.4028/www.scientific.net/MSF.858.603.

- [17] D. J. Meyer, N. A. Bohna, P. M. Lenahan, and A. J. Lelis, "Structure of 6H silicon carbide/silicon dioxide interface trapping defects," *Appl. Phys. Lett.*, vol. 84, no. 17, pp. 3406–3408, Apr. 2004, doi: 10.1063/1.1723693.

- [18] R. R. Rao, S. Balaji, K. Matocha, and V. Tilak, "An approach to model temperature effects of interface traps in 4H-SiC," *Mater. Sci. Forum*, vols. 556–557, pp. 497–500, Sep. 2007, doi: 10.4028/www.scientific.net/MSF.556-557.497.

- [19] K. Matocha and V. Tilak, "Understanding the inversion-layer properties of the 4H-SiC/SiO<sub>2</sub> interface," *Mater. Sci. Forum*, vols. 679–680, pp. 318–325, Mar. 2011, doi: 10.4028/www.scientific.net/MSF.679-680.318.

- [20] D. Okamoto, H. Yano, T. Hatayama, and T. Fuyuki, "Removal of near-interface traps at SiO<sub>2</sub>/4H–SiC (0001) interfaces by phosphorus incorporation," *Appl. Phys. Lett.*, vol. 96, no. 20, pp. 1–3, May 2010, doi: 10.1063/1.3432404.

- [21] B. R. Tuttle, X. Shen, and S. T. Pantelides, "Theory of near-interface trap quenching by impurities in SiC-based metal-oxide-semiconductor devices," *Appl. Phys. Lett.*, vol. 102, no. 12, pp. 1–4, Mar. 2013, doi: 10.1063/1.4798536.

- [22] T. E. Rudenko, I. N. Osiyuk, I. P. Tyagulski, H. Ö. Ólafsson, and E. Ö. Sveinbjörnsson, "Interface trap properties of thermally oxidized n-type 4H–SiC and 6H–SiC," *Solid-State Electron.*, vol. 49, no. 4, pp. 545–553, Apr. 2005, doi: 10.1016/j.sse.2004.12.006.

VOLUME 6, 2018 473

- [23] F. Allerstam et al., "A strong reduction in the density of near-interface traps at the SiO<sub>2</sub>/4H–SiC interface by sodium enhanced oxidation," J. Appl. Phys., vol. 101, no. 12, pp. 1–5, Jun. 2007, doi: 10.1063/1.2745321.

- [24] S. Dimitrijev, Principles of Semiconductor Devices, 2nd ed. New York, NY, USA: Oxford Univ. Press, 2012, pp. 183–187.

**PEYUSH PANDE** received the B.Eng. degree in electronics and telecommunication from Amravati University, Amravati, India, in 2002, the M.Eng. degree in VLSI system design and the Graduate Diploma of Research Studies in Engineering from Griffith University, Nathan, QLD, Australia, in 2004 and 2017, respectively, where he is currently pursuing the Ph.D. degree with the Queensland Micro- and Nanotechnology Centre.

His current research interests include characterization techniques and active defects in SiC MOSFET

**SIMA DIMITRIJEV** (S'87–M'88–SM'01) received the B.Eng., M.Sci., and Ph.D. degrees in electronic engineering from the University of Nis, Nis, Yugoslavia, in 1982, 1985, and 1989, respectively. He is currently a Professor with the Griffith School of Engineering and the Deputy Director of Queensland Micro- and Nanotechnology Centre, Griffith University, Brisbane, Australia.

He has authored the book entitled *Principles* of Semiconductor Devices, 2nd Ed. (New York: Oxford University Press, 2011).

HAMID AMINI MOGHADAM received the B.Eng. degree from Azad University, Bojnord, Iran, in 2005, the M.Eng. degree in electronic engineering from Semnan University, Semnan, Iran, in 2011, and Ph.D. degree from Griffith University, Australia, in 2016. He is currently a Research Fellow with the Queensland Micro- and Nanotechnology Centre, Griffith University.

His current research interests include design, fabrication, and electrical characterization of wide

bandgap power semiconductor (4H-SiC, AlGaN/GaN) devices.

**PHILIP TANNER** received the B.Eng. degree in electrical engineering from the University of Queensland, Australia, in 1979 and the Ph.D. degree in microelectronics from Griffith University, Australia, in 1996, where he is currently a Research Fellow with the Queensland Micro- and Nanotechnology Centre.

His research interests include silicon carbide and gallium nitride-based materials and devices for high power, sensor, and MEMs applications.

**DANIEL HAASMANN** received the bachelor's degree (Hons.) in microelectronic engineering from Griffith University, Brisbane, Australia, in 2008 and the Ph.D. degree from the Queensland Micro- and Nanotechnology Centre, Griffith University in 2015, where he is currently a Research Fellow.

His current research interests include 4H-SiC gate-oxide growth and electrical characterization of SiC MOS devices.

JISHENG HAN received the B.S. and M.S. degrees in solid-state physics from Shandong University, Jinan, China, and the Ph.D. degree from the University of South Australia, Adelaide, SA, Australia. He was a Research Fellow with the School of Microelectronic Engineering, Griffith University, where he has been a Research Fellow, a Senior Research Fellow, and an Associate Professor with the Queensland Micro- and Nanotechnology Centre since 2006.

474 VOLUME 6, 2018