Digital Object Identifier 10.1109/JEDS.2016.2586116

# Modeling of Charge and Quantum Capacitance in Low Effective Mass III-V FinFETs

MOHIT D. GANERIWALA<sup>1</sup> (Student Member, IEEE), CHANDAN YADAV<sup>2</sup> (Student Member, IEEE), NIHAR R. MOHAPATRA<sup>1</sup>, SOURABH KHANDELWAL<sup>3</sup> (Member, IEEE), CHENMING HU<sup>3</sup> (Fellow, IEEE), AND YOGESH SINGH CHAUHAN<sup>2</sup> (Senior Member, IEEE)

Department of Electrical Engineering, Indian Institute of Technology Gandhinagar, Gandhinagar 382355, India

Department of Electrical Engineering, Indian Institute of Technology Kanpur, Kanpur 208016, India

Department of Electrical Engineering and Computer Science, University of California, Berkeley, CA 94720, USA

CORRESPONDING AUTHOR: Y. S. CHAUHAN (e-mail: chauhan@iitk.ac.in)

This work was supported in part by the Semiconductor Research Corporation, in part by the Ramanujan Fellowship, in part by the Science and Engineering Research Board, and in part by the Council of Scientific and Industrial Research.

**ABSTRACT** In this paper, we present a compact model for semiconductor charge and quantum capacitance in III-V channel FETs. With III-V being viewed as the most promising candidate for future technology node, a compact model is needed for their circuit simulation. The model presented in this paper addresses this need and is completely explicit and computationally efficient which makes it highly suitable for SPICE implementation. The proposed model is verified against the numerical solution of coupled Schrödinger–Poisson equation for FinFET with various channel thickness and effective mass.

**INDEX TERMS** III-V, density of states (DOS), SPICE, FinFET, quantum capacitance.

# I. INTRODUCTION

As the current CMOS technology with conventional silicon channel is reaching to it's scaling limits, several new materials and device architectures are being actively explored for future generation [1]–[5]. Among them the III-V channel material with ultrathin-body and multigate architecture is probably the most promising candidate, especially for nMOSFETs [6]–[10]. The III-V materials because of their lower effective mass offer higher channel mobility along with the possibility of integration with the conventional silicon CMOS technology [11]–[13]. The ultrathin-body and multigate architecture offer superior electrostatic control [14]. If III-V materials had to replace silicon, especially for logic applications, it is necessary to analyze their performance at circuit level. This requires a computationally efficient compact model for circuit simulators.

Several performance metrics for circuits such as switching delay (CV/I), transconductance, and dynamic power consumption (CV<sup>2</sup>) depend directly on the gate capacitance ( $C_g$ ). Therefore, the analysis of  $C_g$  is very important for any circuit simulation and development of future technology generation. Typically in inversion regime, the total  $C_g$  of a metal-insulator-semiconductor (MIS) system

can be modeled as a series combination of the insulator capacitance ( $C_{ins} = \epsilon_{ins}/t_{ins}$ ) and inversion layer capacitance ( $C_{inv}$ ) [15]. The  $C_{inv}$  for an undoped fully depleted ultrathin-body device comprises of the centroid capacitance ( $C_{cen}$ ) [16] in series with quantum capacitance ( $C_Q$ ) [17], [18]. Of these, the  $C_Q$  is proportional to the density of state (DOS) and valley degeneracy. The III-V materials have lower DOS (due to their lower effective mass) and valley degeneracy as compared to the silicon. This results in a much lower  $C_Q$  and the overall  $C_g$  is then limited by the  $C_Q$  [18]. Therefore it is necessary to accurately model the impact of low DOS on the total  $C_g$  in III-V channel FETs.

Several different models have been presented in literature which include the effect of  $C_Q$  in total  $C_g$ . The formulation presented in [19] is computationally expensive and is not fit for the SPICE simulators. The models presented in [20] and [21] are physical but require iterations and result into a complicated formulation. Also these models do not consider the effect of band non-parabolicity on  $C_g$ . In this paper, we have presented a physics based model for  $C_Q$ . We have then developed a compact formulation of  $C_Q$  by utilizing this form of equation with suitable approximation.

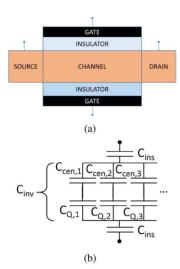

FIGURE 1. (a) Schematic diagram of the FinFET structure used in this work, (b) Equivalent capacitance network for the device shown in fig (a).  $C_{ins}$  is the gate insulator capacitance and  $C_{inv}$  is inversion capacitance, which is represented in terms of the contribution form centroid capacitance ( $C_{cen,i}$ ) and quantum capacitance ( $C_{Q,i}$ ) in each subband. The subscript i represents the subband number.

The developed model is computationally efficient, simple yet accurate without compromising much of the physics. The model is also extended to include the effect of conduction band non-parabolicity on  $C_g$  without compromising the computational efficiency. The proposed model is completely explicit in terms of the applied gate voltage  $V_G$  thereby making it highly suitable for SPICE implementation.

This paper is organized as follows: Section II presents the formulation and model description. Section III includes the model verification and discussion regarding the same, followed by conclusion in Section IV.

## II. MODEL DESCRIPTION

Fig. 1 shows the device geometry considered in this work along with the total  $C_g$ . The  $C_{inv}$  consists of parallel combination of the contributions from each of the occupied electron subband in the channel. For each subband, the  $C_{inv}$  in turn consists of a series combination of  $C_{cen}$  and  $C_Q$  as shown in fig. 1(b) [18]. Therefore, the  $C_{inv}$  can be written as,

$$C_{inv} = \sum_{i} \left( \frac{1}{C_{Q,i}} + \frac{1}{C_{cen,i}} \right)^{-1} \tag{1}$$

where  $C_{Q,i}$  and  $C_{cent,i}$  is the quantum capacitance and centroid capacitance associated with each subband respectively. Here, we have neglected the effect of charge centroid which can later be added using conventional method of introducing a correction factor to the oxide thickness [22], [23]. Therefore the total gate capacitance  $(C_g)$  is given by

$$C_g = \left(\frac{1}{2C_{ins}} + \frac{1}{\sum_i C_{O,i}}\right)^{-1} \tag{2}$$

Following the methodology described in [18] the quantum capacitance for each subband can be written as,

$$C_{Q,i} = q \frac{\partial \left(-Q_i\right)}{\partial \left(E_f - E_i\right)} \tag{3}$$

where  $Q_i$  is the contribution of  $i^{th}$  subband to the total semiconductor charge  $(Q_s)$ ,  $E_i$  is the energy level of  $i^{th}$  subband and  $E_f$  is the fermi energy. In order to get  $Q_s$  for a two dimensional (2D) system such as the FinFET structure discussed in this work, 2D DOS should be considered. Considering 2D DOS,  $Q_s$  can be formulated as,

$$Q_s = \sum_i Q_i = \sum_i \int_{E_i}^{\infty} \frac{\frac{m_{\parallel}^* q}{\pi \hbar^2}}{1 + \exp\left(\frac{E - E_f}{kT}\right)} dE \tag{4}$$

where  $m_{\parallel}^*$  is the in plane electron effective mass. Substituting (4) in (3) and differentiating (3) we get,

$$C_{Q,i} = \frac{\frac{m_{\parallel}^* q^2}{\pi \hbar^2}}{1 + \exp\left(\frac{E_i - E_f}{kT}\right)}.$$

(5)

Eq. (5) along with (2) gives us the total  $C_g$ . But in order to get the  $C_g$  as a function of the applied  $V_G$ , it is necessary to get the variation of  $C_{Q,i}$  with respect to  $V_G$ . Note that both the subband energy level  $E_i$  and fermi level  $E_f$  appearing in expression of  $C_{Q,i}$  change with  $V_G$  (considering bottom of the conduction band  $E_c$  as the reference). Therefore, to get the variation of  $C_{Q,i}$  with  $V_G$  we need to express  $E_f$  and  $E_i$  as a function of  $V_G$ . This has been derived analytically in [20] and [21] which results in complex expression of total  $C_g$ .

From (5) it can be seen that for a particular subband when  $E_f \ll E_i$  the denominator is very large and  $C_{Q,i}$  is negligible. When  $E_f \gg E_i$ , the denominator can be approximated to unity and  $C_{Q,i}$  becomes constant and independent of  $V_G$ . Therefore, for both this extreme the exact relation of  $E_f$  vs  $V_G$  becomes unimportant for modeling of  $C_{Q,i}$ . An accurate form of this relation is only needed for a very narrow range around  $E_i$ . Leveraging this fact, instead of modeling  $E_f$  as a function  $V_G$  for entire bias range, we treat each subband separately and approximate the relation between  $E_f$  and  $V_G$  by a straight line  $(E_f \propto V_G)$  around the subband energy  $E_i$ . Therefore, the above expression of  $C_{Q,i}$  can be written in a compact form as a function of  $V_G$  as,

$$C_{Q,i} = \frac{A_i \frac{m_{\parallel}^* q^2}{\pi \hbar^2}}{1 + \exp\left(\frac{E_i - (B_i q V_G)}{C_i k T}\right)}$$

(6)

Here  $A_i$ ,  $B_i$ ,  $C_i$  are fitting parameters included in order to provide the flexibility to fit various real data.

The value of subband energy required to find the quantum capacitance can be derived as in [20]. However this approach still requires an implicit equation to be solved iteratively.

VOLUME 4, NO. 6, NOVEMBER 2016

Since our model has a parameter to control the capacitance inflection points, we can use the subband energy calculated from an explicit expression for infinite quantum well [24]

$$E_i = \frac{i^2 \pi^2 \hbar^2}{2m_{\parallel}^* t_{ch}^2} \tag{7}$$

where  $t_{ch}$  is the channel thickness and i is the eigennumber of the subband.

Expression of  $C_{Q,i}$  given by (6) along with (7) can be used in (2) to obtain an explicit expression of  $C_g$  in terms of  $V_G$ . However due to the traditional problem of charge conservation it is preferable to have a charge based implementation instead of a capacitance based which requires a continuous model of semiconductor charge [25]. Solving (4),  $Q_s$  as a function of  $E_f$  can be written as,

$$Q_{s} = \sum_{i} \frac{m_{\parallel}^{*} qkT}{\pi \hbar^{2}} ln \left[ 1 + exp\left(\frac{E_{f} - Ei}{kT}\right) \right]$$

(8)

Using the same form of approximations as for  $C_Q$  discussed above, a new compact expression of  $Q_s$  is derived as,

$$Q_s = \sum_{i} D_i \frac{m_{\parallel}^* q k T}{\pi \hbar^2} ln \left[ 1 + exp \left( \frac{(B_i q V_G) - E_i}{C_i k T} \right) \right]$$

(9)

Eq. (9) gives a continuous model of charge valid for all the regions of operation. The form of the model also ensures that the derivatives are continuous. Differentiation of (9) gives C<sub>Q</sub> and has the same form as derived earlier.

The model is derived assuming parabolic conduction band structure, hence a constant value of effective mass is used. But, the non-parabolicity of conduction band causes effective mass to vary with energy. This is particularly important in case of III-V materials and changes the  $C_g$  in inversion [26], [27]. The effect of non-parabolic band structure could be modeled by modifying the effective mass as follows:

$$m_{\parallel}^* = m_b^* (1 + 2\alpha E) \tag{10}$$

where  $m_b^*$  is the effective mass at bottom of the conduction band, and  $\alpha$  is known as non-parabolicity factor [28]. But, modifying the effective mass will cause difficulty in analytical derivation of  $Q_s$  and an explicit expression could not be derived. This in turn will affect the computational efficiency of the model. However, the presented model could still be modified to include this effect. For a parabolic band structure approximation, the  $C_Q$  doesn't change with  $V_G$  once the Fermi level moves above a particular subband. This is due to constant effective mass and thus constant DOS for 2D materials. But for non-parabolic bands, increase in  $V_G$  causes an increase in  $C_Q$  even after the Fermi level moves above the subband [29]. This effect could be modeled by

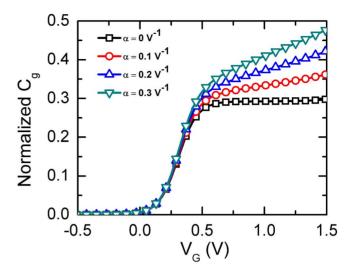

FIGURE 2. Normalized gate capacitance,  $C_g$  for different  $V_G$  at  $V_{DS}=0$  V with insulator thickness,  $t_{ins}=1$  nm and  $m_b^*=0.048m_0$ , where  $m_0$  is the free electron mass. Different curves are for different value of factor  $\alpha$ . The normalization of  $C_g$  is done with the insulator capacitance. It can be seen that the effect of band non-parabolicity on  $C_g$  is similar to what described by Ali *et al.* [29]. Note that only one subband is considered here.

modifying (9) as follow:

$$Q_{s} = \sum_{i} D_{i} \frac{m_{b}^{*} (1 + \alpha V_{G}) qkT}{\pi \hbar^{2}}$$

$$ln \left[ 1 + exp \left( \frac{(B_{i}qV_{G}) - E_{i}}{C_{i}kT} \right) \right]$$

(11)

here the factor  $\alpha$  is similar to the non-parabolicity factor in (10) with unit  $V^{-1}$  and could be used to tune the effect of non-parabolicity.

Equation (11) captures the effect of non-parabolicity in band structure by making effective mass a function of  $V_G$ . The effect of including non-parabolicity in the model is shown in fig. 2. It can be seen that the  $C_G$  varies with  $V_G$  for non zero value of constant  $\alpha$ , where as  $\alpha=0$  gives a constant plateau.

In the subsequent section we will verify the presented model against the numerical simulation data. The simulation assumes the parabolic band structure and hence the model with value of  $\alpha=0$  is used to match the results. However, it is shown that the model could include the effect of non-parabolicity through the factor  $\alpha$ .

### III. MODEL VERIFICATION

In this section, the  $C_g$  and  $Q_s$ , derived from the model described in Section II, are verified with the data obtained from numerical simulation of the FinFET device (shown in fig. 1). The simulation data are obtained from self-consistent solution of coupled Schrödinger-Poisson equation [30]. The simulation takes into account the finite barrier height at the insulator/semiconductor interface. A barrier height of 3.4 eV is considered in the simulation. The simulation therefore, considers the wavefunction penetration into the insulator. It also takes into account the difference in carrier effective

398 VOLUME 4, NO. 6, NOVEMBER 2016

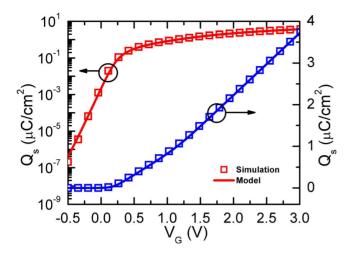

FIGURE 3. Semiconductor charge,  $Q_S$  vs  $V_G$  at  $V_{DS}=0$  V for device shown in fig. 1(a) with insulator thickness,  $t_{ins}=1$  nm, in plane effective mass,  $m_i^*=0.048m_0$  and channel thickness,  $t_{ch}=7$  nm.

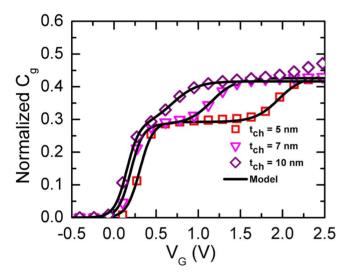

FIGURE 4. Comparison of the presented model with the simulated gate capacitance,  $C_g$  for different  $V_G$  at  $V_{DS}=0$  V with insulator thickness,  $t_{ins}=1$  nm and in plane effective mass,  $m_\parallel^*=0.048m_0$ . Different curves are for different channel thickness. The normalization of  $C_g$  is done with the insulator capacitance. Different inflection points in  $C_g$  corresponds to different electron subbands. Note that as only lowest two subbands are considered while plotting the capacitance using the model, the third peak in  $C_g$  for  $t_{ch}=10$  nm which corresponds to the  $3^{rd}$  electron subband is not captured using the model. Reduction in the channel thickness causes an increase in the subband energy which results in the shifting of the inflection point toward higher  $V_G$  values.

mass of the oxide and channel material. The  $SiO_2$  insulator material with an effective mass of  $m_{ox}=0.55m_0$ , where  $m_0$  is the free electron mass and an undoped channel is considered.

Fig. 3 compares the semiconductor charge obtained from the model to the numerical simulation data. The data corresponds to  $In_{0.53}Ga_{0.47}As$  channel with  $m_{\parallel}^*=0.048m_0$ . It can be seen from fig. 3 that the proposed model provides an excellent match to the simulation data.

Fig. 4 shows  $C_g$  versus  $V_G$  for different channel thickness with  $t_{ins}=1$  nm and  $m_{\parallel}^*=0.048m_0$ . Here only the

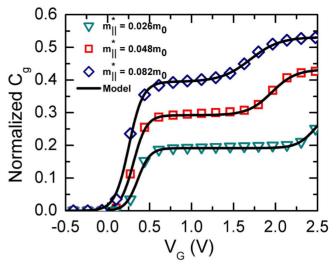

FIGURE 5. Gate capacitance,  $C_g$  versus  $V_G$  at  $V_{DS}=0$  V for devices with channel thickness,  $t_{ch}=5$  nm and insulator thickness,  $t_{ins}=1$  nm for different in-plane effective mass  $m_\parallel^*$ . The normalization of  $C_g$  is done with insulator capacitance. In-plane effective mass of  $0.026m_0$ ,  $0.048m_0$  and  $0.082m_0$  corresponds to InAs,  $In_{0.53}Ga_{0.47}As$  and GaAs channel materials respectively. Lower in-plane effective mass gives lower  $C_Q$  and a greater impact of  $C_Q$  on  $C_g$  due to a series combination of  $C_{ins}$  and  $C_Q$ .

contribution from first two subbands is considered. Note that, this is not a limitation of the model and the effect from any number of subbands can be included. The step like behavior of  $C_g$  is due to the 2D DOS appearing in  $C_Q$ . This also shows that for low effective mass material  $C_g$  is mainly dictated by  $C_Q$  and hence the  $C_Q$  should be modeled accurately.

Fig. 5 shows the impact of  $m_{\parallel}^*$  on  $C_g$  for  $t_{ch}=5$ nm and  $t_{ins}=1$  nm. With decrease in the effective mass, the subband energy increases which shifts the capacitance inflection points towards the higher  $V_g$  values. Moreover with lower effective mass,  $C_Q$  decreases and its impact on total  $C_g$  is more pronounced (due to series combination of  $C_{ins}$  and  $C_Q$ ) and hence overall  $C_g$  also decreases. Therefore, it is extremely important that the model should be efficient enough to capture the effect of quantum capacitance in low effective mass regime.

#### **IV. CONCLUSION**

To summarize, we have presented a compact model of semiconductor charge and quantum capacitance for transistors with low DOS III-V channel materials. It is shown that for future III-V FETs quantum capacitance plays an important role in deciding the total gate capacitance and the proposed model accurately captures this effect. The proposed model also has the flexibility to include the effect of non-parabolicity in the band structure. The model is simple, explicit and computationally efficient which is desired for SPICE simulators. The accuracy of the model is also verified by comparing it with the numerical simulation data for different channel thickness and in-plane effective mass.

VOLUME 4, NO. 6, NOVEMBER 2016 399

#### **REFERENCES**

- [1] S. Khandelwal, J. P. Duarte, Y. S. Chauhan, and C. Hu, "Modeling 20-nm germanium FinFET with the industry standard FinFET model," *IEEE Electron Device Lett.*, vol. 35, no. 7, pp. 711–713, Jul. 2014.

- [2] Y. Sun et al., "High-performance CMOS-compatible self-aligned In<sub>0.7</sub>Ga<sub>0.3</sub>As MOSFETs with GMSAT over 2200 μs/μm at VDD = 0.5 V," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, Dec. 2014, pp. 25.3.1–25.3.4.

- [3] S. Yadav et al., "First monolithic integration of Ge P-FETs and InAs N-FETs on silicon substrate: Sub-120 nm III-V buffer, sub-5 nm ultrathin body, common raised S/D, and gate stack modules," in Proc. IEEE Int. Electron Devices Meeting (IEDM), Washington, DC, USA, Dec. 2015, pp. 2.3.1–2.3.4.

- [4] G. Fiori and G. Iannaccone, "The challenging promise of 2D materials for electronics," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, Washington, DC, USA, Dec. 2015, pp. 27.1.1–27.1.4.

- [5] N. Taoka et al., "Impact of fermi level pinning inside conduction band on electron mobility of In<sub>x</sub>Ga<sub>1-x</sub>As MOSFETs and mobility enhancement by pinning modulation," in Proc. IEEE Int. Electron Devices Meeting (IEDM), Washington, DC, USA, Dec. 2011, pp. 27.2.1–27.2.4.

- [6] J. A. D. Alamo, "Nanometre-scale electronics with III-V compound semiconductors," *Nature*, vol. 479, no. 7373, pp. 317–323, 2011.

- [7] K. J. Kuhn, "Considerations for ultimate CMOS scaling," *IEEE Trans. Electron Devices*, vol. 59, no. 7, pp. 1813–1828, Jul. 2012.

- [8] C. Zhang and X. Li, "III-V nanowire transistors for low-power logic applications: A review and outlook," *IEEE Trans. Electron Devices*, vol. 63, no. 1, pp. 223–234, Jan. 2016.

- [9] R. Kim, U. E. Avci, and I. A. Young, "CMOS performance benchmarking of Si, InAs, GaAs, and Ge nanowire n- and pMOSFETs with Lg=13 nm based on atomistic quantum transport simulation including strain effects," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, Washington, DC, USA, Dec. 2015, pp. 34.1.1–34.1.4.

- [10] V. Deshpande et al., "Advanced 3D monolithic hybrid CMOS with sub-50 nm gate inverters featuring replacement metal gate (RMG)-InGaAs nFETs on SiGe-OI fin pFETs," in Proc. IEEE Int. Electron Devices Meeting (IEDM), Washington, DC, USA, Dec. 2015, pp. 8.8.1–8.8.4.

- [11] M. K. Hudait et al., "Heterogeneous integration of enhancement mode In<sub>0.7</sub>Ga<sub>0.3</sub>As quantum well transistor on silicon substrate using thin (les 2 μm) composite buffer architecture for high-speed and low-voltage (0.5 v) logic applications," in Proc. IEEE Int. Electron Devices Meeting, Washington, DC, USA, Dec. 2007, pp. 625–628.

- [12] M. L. Huang et al., "In<sub>0.53</sub>Ga<sub>0.47</sub> MOSFETs with high channel mobility and gate stack quality fabricated on 300 mm Si substrate," in *Proc. IEEE Symp. VLSI Technol.*, Kyoto, Japan, 2015, pp. T204–T205.

- [13] V. Djara et al., "CMOS-compatible replacement metal gate InGaAs-OI FinFET with I<sub>ON</sub>=156 μA/μm at V<sub>DD</sub>=0.5 V and I<sub>OFF</sub>=100 nA/μm," *IEEE Electron Device Lett.*, vol. 37, no. 2, pp. 169–172, Feb. 2016.

- [14] J. P. Colinge, "Multi-gate SOI MOSFETS," Microelectron. Eng., vol. 84, nos. 9–10, pp. 2071–2076, 2007.

- [15] S.-I. Takagi and A. Toriumi, "Quantitative understanding of inversion-layer capacitance in Si MOSFET's," *IEEE Trans. Electron Devices*, vol. 42, no. 12, pp. 2125–2130, Dec. 1995.

- [16] A. Hartstein and N. Albert, "Determination of the inversion-layer thickness from capacitance measurements of metal-oxide-semiconductor field-effect transistors with ultrathin oxide layers," *Phys. Rev. B*, vol. 38, no. 2, pp. 1235–1240, 1988.

- [17] S. Luryi, "Quantum capacitance devices," Appl. Phys. Lett., vol. 52, no. 6, pp. 501–503, 1988.

- [18] D. Jin, D. Kim, T. Kim, and J. del Alamo, "Quantum capacitance in scaled down III–V FETs," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, Baltimore, MD, USA, Dec. 2009, pp. 1–4.

- [19] S. Oh and H.-S. Wong, "Physics-based compact model of III-V heterostructure FETs for digital logic applications," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, Dec. 2008, pp. 1–4.

- [20] S. Mudanai, A. Roy, R. Kotlyar, T. Rakshit, and M. Stettler, "Capacitance compact model for ultrathin low-electron-effective-mass materials," *IEEE Trans. Electron Devices*, vol. 58, no. 12, pp. 4204–4211, Dec. 2011.

- [21] C. Yadav et al., "Capacitance modeling in III-V FinFETs," IEEE Trans. Electron Devices, vol. 62, no. 11, pp. 3892–3897, Nov. 2015.

- [22] Y. S. Chauhan et al., "BSIM6: Analog and RF compact model for bulk MOSFET," *IEEE Trans. Electron Devices*, vol. 61, no. 2, pp. 234–244, Feb. 2014.

- [23] Y. S. Chauhan et al., FinFET Modeling for IC Simulation and Design: Using the BSIM-CMG Standard. London, U.K.: Academic Press, 2015.

- [24] R. Eisberg and R. Resnick, Quantum Physics of Atoms, Molecules, Solids, Nuclei, and Particles. New York, NY, USA: Wiley, 1974.

- [25] B. P. Yang, B. Epler, and P. K. Chatterjee, "An investigation of the charge conservation problem for MOSFET circuit simulation," *IEEE J. Solid-State Circuits*, vol. 18, no. 1, pp. 128–138, Feb. 1983.

- [26] Y. Liu, N. Neophytou, G. Klimeck, and M. S. Lundstrom, "Band-structure effects on the performance of III–V ultrathin-body SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 55, no. 5, pp. 1116–1122, May 2008.

- [27] G. Hiblot, G. Mugny, Q. Rafhay, F. Boeuf, and G. Ghibaudo, "Compact model for inversion charge in III-V bulk MOSFET including non-parabolicity," *IEEE Trans. Nanotechnol.*, vol. 14, no. 4, pp. 768–775, Jul. 2015.

- [28] V. A. Altschul, A. Fraenkel, and E. Finkman, "Effects of band non-parabolicity on two-dimensional electron gas," *J. Appl. Phys.*, vol. 71, no. 9, pp. 4382–4384, 1992.

- [29] A. Ali et al., "Experimental determination of quantum and centroid capacitance in arsenide-antimonide quantum-well MOSFETs incorporating nonparabolicity effect," *IEEE Trans. Electron Devices*, vol. 58, no. 5, pp. 1397–1403, May 2011.

- [30] S. Datta, Quantum Transport: Atom to Transistor. Cambridge, U.K.: Cambridge Univ. Press, 2005.

MOHIT D. GANERIWALA received the B.Tech. degree from Nirma University, India, in 2012, and the M.Tech. degree in electrical engineering from the Indian Institute of Technology Gandhinagar, India, in 2015, where he is currently pursuing the Ph.D. degree in electrical engineering. His research interest include nano-scale device physics, compact modeling, and simulation of advanced semiconductor devices.

CHANDAN YADAV (S'14) received the B.E. degree in electronics and communication from RJIT Gwalior, India, in 2009, and the M.Tech. degree in microelectronics from the Indian Institute of Information Technology Allahabad, India, in 2011. He is currently pursuing the Ph.D. degree with the Indian Institute of Technology Kanpur, Kanpur, India. His research interests include compact modeling and simulation of UTB SOI, FinFETs, and nanowire.

NIHAR R. MOHAPATRA received the Ph.D. degree in electrical engineering from IIT Bombay, Mumbai, India, in 2004 He with IHPMicroelectronics, AMD. and GLOBALFOUNDRIES. He joined IIT Gandhinagar, in 2011, as an Assistant Professor with the Department of Electrical Engineering, where he has been an Associate Professor since 2015. His present research interests are nano-scale device physics, CMOS technology development, reliability of semiconductor devices, and compact modeling.

400

**SOURABH KHANDELWAL** (M'14) received the master's degree from the Indian Institute of Technology (IIT) Bombay, in 2007, and the Ph.D. degree from the Norwegian University of Science and Technology, in 2013. He is currently a BSIM Group Program Manager/Post-Doctoral Researcher with the BSIM Group, University of California at Berkeley. From 2007 to 2010, he was a Research Engineer with IBM Semiconductor Research and Development Centre, developing compact models for RF SOI devices. He holds

a patent and has authored several international journal and conference publications in the area of device modeling and characterization. His Ph.D. work on GaN compact model is under consideration for industry standardization at the Compact Model Coalition. He is a Reviewer of the IEEE Transactions on Electron Devices, the IEEE Electron Device Letters, the IEEE Access, *Solid State Electronics Journal*, the *Journal of Numerical Modeling*, and *Microelectronics Journal*.

YOGESH SINGH CHAUHAN (SM'12) received the Ph.D. degree from École Polytechnique Fédérale de Lausanne, Switzerland, in 2007. He was with IBM in 2007 - 2010 and University of California Berkeley 2010-2012. Since 2012, he is a faculty at IIT Kanpur, India. He received Ramanujan fellowship in 2012, IBM faculty award in 2013 and P. K. Kelkar fellowship in 2015. He is co-developer of ASM-HEMT model for GaN HEMTs which is under industry standardization at the Compact Model Coalition. His

research interests are characterization, modeling, and simulation of advanced semiconductor devices.

**CHENMING HU** (F'90) is a Distinguished Professor Emeritus of University of California Berkeley, a Former Chief Technology Officer of TSMC. He is the Board Director of SanDisk Inc. and Friends of Children with Special Needs. He is known for his work on FinFET—the 3-D transistor capable of scaling to single digit nanometer nodes, widely used IC reliability models, and BSIM—the industry standard transistor models used by most IC companies, since 1997, to design CMOS products. He was a recipient of the IEEE Andrew

Grove Award, the Solid State Circuits Award and Nishizawa Medal, the EDA Industry's Kaufman Award, the Asian American Engineer of the Year Award, and the UC Berkeley's highest honor for teaching—the Berkeley Distinguished Teaching Award.

VOLUME 4, NO. 6, NOVEMBER 2016