Received 2 September 2014; revised 5 January 2015; accepted 8 January 2015. Date of current version 22 April 2015. The review of this paper was arranged by Editor A. C. Seabaugh.

Digital Object Identifier 10.1109/JEDS.2015.2390971

# **Band-Offset Engineering for GeSn-SiGeSn** Hetero Tunnel FETs and the Role of Strain

## SAURABH SANT AND ANDREAS SCHENK

Integrated Systems Laboratory, Department of Information Technology and Electrical Engineering, ETH Zurich, Zurich CH-8092, Switzerland CORRESPONDING AUTHOR: S. SANT (e-mail: sasant@iis.ee.ethz.ch)

This work was supported by the European Community's Seventh Frame-Work Programme under Grant 619509 (Project E<sup>2</sup>SWITCH).

**ABSTRACT** In this paper a simulation study of the effect of conduction and valence band offsets on the subthreshold swing (SS) of a double-gate tunnel field-effect transistor (TFET) with gate-overlapped source is presented. The simulations show that if the pn-junction and the hetero-junction coincide, the band offsets can significantly improve the SS by suppressing the so-called point tunneling at the pn-junction. It turns out that the performance of an n-channel TFET is determined by the direct conduction band offset whereas that of a p-channel TFET is mainly effected by the energy difference between the light hole bands of the two materials. Thus, the performance of the hetero-junction TFET can be improved by selecting material systems with high conduction or valence band offsets. The misalignment between the pn-junction and the hetero-junction is shown to degrade the SS. The above-described band-offset engineering has been applied to the GeSn/SiGeSn hetero-structure system with and without strain. Simulations of GeSn/SiGeSn hetero-TFETs with band-to-band-tunneling parameters determined from pseudopotential calculations show that compressive strain in GeSn widens the design space for TFET application while tensile strain reduces it.

**INDEX TERMS** Tunnel FETs, GeSn-SiGeSn hetero structures, band offset optimization.

# I. INTRODUCTION

The scaling of channel length and width of the MOSFET was accompanied by the scaling of supply voltage and power consumed per device. At the current technology node further reduction of the supply voltage would result in an exponential increase of the off-state leakage owing to the phenomenon of thermionic emission inherent in the switching mechanism of the MOSFET [1]. In order to make progress in power scaling, nano-scale solid-state switches based on various other switching mechanisms such as band-to-band tunneling (BTBT) [2], impact ionization [3] and nano-electro-mechanical switching [4] have been proposed. The Tunnel Field Effect Transistor (TFET) based on BTBT in semiconductors is considered a promising candidate for further scaling of the supply voltage [2]. TFETs with different geometrical structures such as planar [5]–[7], nanowire-based [8] or FinFET-like [9] have been proposed. These geometries differ in the electrostatic coupling of the gate to the channel region of the FET [10]. Stronger coupling results in a steeper sub-threshold slope. Being a truism for

MOSFETs, in a TFET the major boost to the sub-threshold swing comes from the emergence of BTBT between the source and the channel region at the onset of switching. This mechanism of an exponentially growing BTBT generation rate, in principle, enables TFETs to exhibit a steeper sub-threshold slope than the "conventional" MOSFETs. The BTBT rate is enhanced by a small direct band gap of the material which improves the on-state current of the TFET. Therefore, a small-gap material is preferred in the source region. However, the use of a small-gap material in the drain region turns on BTBT there which results in a high drain current below the off-voltage (ambipolarity). Using a wide-gap material in the drain region can suppress ambipolarity by hampering or inhibiting BTBT below the off-voltage. Thus, hetero-structure TFETs with small-gap material in the source and wide-gap material in the drain region can provide a high on-current along with suppressed ambipolar leakage. The ambipolarity could also be suppressed by low drain doping for intermediate band gap materials such as Si. However, for small gap materials, lowering the doping in the drain

region cannot suppress ambipolarity as seen in the transfer characteristics of Si<sub>0.5</sub>Ge<sub>0.5</sub> homojunction TFETs reported in [9]. As the small gap materials are required for the source region, lowering the drain doping to suppress the ambipolarity might not be a viable alternative. The effect of the band gap on the SS is more involved. Due to the typical field dependence of the BTBT rate, the speed at which the BTBT rate rises with gate voltage becomes higher for a wide band gap. Therefore, the minimum SS worsens in a small-gap material. Additionally, the high intrinsic carrier density of the small-gap material in combination with defect-assisted tunneling (DAT) can result in a high Shockley-Read-Hall (SRH) generation rate which easily deteriorates the SS [11]. In this paper, GeSn/SiGeSn hetero-junction TFETs are analyzed for complimentary logic gate applications. In principle, GeSn/SiGeSn hetero-structures provide three degrees of freedom, viz, Sn content in GeSn, Si and Sn content in SiGeSn. However, technological constraints, such as maximum allowable strain, Si and Sn contents in the alloys shrink the design space. In this work, the three-dimensional design space of the GeSn/SiGeSn material system is spanned to extract most suitable alloy compositions taking into account the technological constraints.

The paper is divided into two parts. The first part describes the band engineering that would enable sub-thermal SS. The effect of conduction and valence band offsets on the BTBT rate and on the sub-threshold swing are explained in detail in this part. The effect of misalignment of pn-junction and hetero-junction is also described here. In the second part, the band engineering is applied to the GeSn/SiGeSn hetero-structure system to determine the suitable alloy compositions.

# **II. DEVICE SIMULATION**

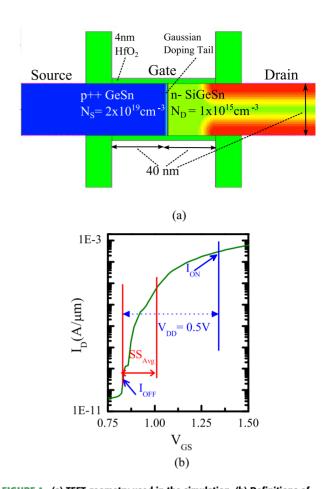

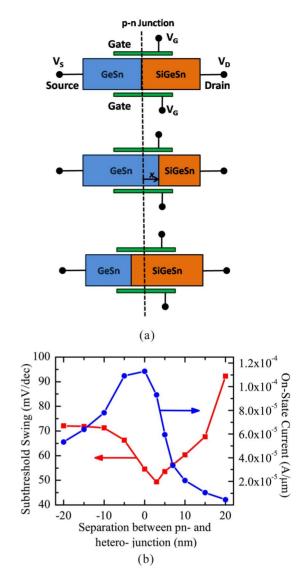

In order to study the impact of the composition of both materials of the TFET, the device structure was kept unchanged throughout the exercise. A double-gate TFET based on a GeSn/SiGeSn hetero-structure was simulated using the commercial TCAD simulator S-Device [12]. Device structure and hetero-junction position are shown in Fig. 1(a). For a p-channel TFET, GeSn is n-doped while for an n-channel TFET it is p-doped. Conversely, SiGeSn is p-doped and n-doped for p-channel and n-channel TFETs, respectively. Since the two materials are in-situ doped during their growth over the substrate, the doping concentration was assumed constant in each individual material. The doping in GeSn was fixed to 2e19 cm<sup>-3</sup>. This value of source doping delivers minimum sub-threshold swing with maximum on-current for the given device geometry in the case of a  $GeSn_{0.06}/Si_{0.28}GeSn_{0.1}$  hetero-structure [13]. The doping in the SiGeSn region was fixed to 1e15 cm<sup>-3</sup>. In order to include the effect of the diffusion of dopant atoms from highly doped GeSn into SiGeSn (possibly induced during activation of the dopant species), a Gaussian profile was added at the pn-junction towards the SiGeSn region

FIGURE 1. (a) TFET geometry used in the simulation. (b) Definitions of on-voltage, off-voltage, on-state current, off-state current, and sub-threshold swing averaged over four decades of  $I_D$ .

(Fig. 1(a)). This profile shifts the pn-junction 3 nm away from the GeSn/SiGeSn hetero-junction.

The "nonlocal dynamic path BTBT" model which is based on Kane's theory of tunneling [15], [16] was used to simulate the TFET. This model requires various band structure quantities such as conduction band (CB) effective mass values in  $\Gamma$ -valley, light hole (LH) effective mass and direct band gap to calculate the tunnel rate due to direct BTBT. In order to model the indirect BTBT rate, the model requires the value of L-valley (or  $\Delta$ -valley, whichever has a lower energy) CB effective mass, LH effective mass, indirect band gap, the degeneracy of the CB valley, the optical phonon energy, the phonon deformation potential and the density of the semiconductor. The degeneracy is defined as  $g_{Tunnel} = 2 \times g_C \times g_V$ , where  $g_C$  and  $g_V$  are the degeneracies of the CB and the valence band (VB), respectively. In the case of direct tunneling, both  $g_C$  and  $g_V$  are unity. For indirect tunneling, the CB degeneracy depends on the type of the valley that constitutes CB minima and the strain in the semiconductor. Both, the indirect and direct BTBT mechanisms were activated in the simulations. Device simulations using this BTBT model with

parameters extracted from pseudopotential calculation [14] have shown good agreement with experimental I<sub>D</sub>-V<sub>GS</sub> characteristics [17]. Following the same procedure, the above mentioned band structure parameters which are required for the BTBT model were obtained from pseudopotential calculations. The values of all the band structure quantities for any given biaxial strain and composition are provided in [17]. The values of additional parameters required for indirect-BTBT are listed for the materials Si, Ge and Sn in Table 1. The values of the parameters for the alloys GeSn and SiGeSn were obtained by linear interpolation. The phonon deformation potential for Sn was set to the value of Ge. As the Sn content in the alloys is low (always less than 15%), the above approximation is less likely to affect the indirect BTBT rate. When the GeSn layer is biaxially strained along {100} plane, the degeneracy of eight L-valleys remains intact. Therefore, for indirect BTBT,  $g_C$  is set to eight. SRH generation (neglecting DAT) was also turned on in the simulation with parameters for Germanium [18] used both in the GeSn and SiGeSn alloys. Confinement in the channel was taken into account by the semi-classical modified local density approximation (MLDA) model [19]. This model mimics the carrier distribution in the triangular quantum well formed at the gate-oxide/semiconductor interface due to application of the gate bias. This modified carrier distribution in turn enters the self-consistent Poisson solver. Also, it alters the Fermi level in the channel region which is imported in the above described Kane model for the calculation of BTBT. Thus, the impact of carrier redistribution due to channel quantization on BTBT enters the simulations when MLDA is used. However, the model does not take into account the increase of the effective band gap in the channel due to sub-band formation (basically resulting in a shift of the on-voltage) and a modification of the DOS-related pre-factor caused by the 2D-3D wave function overlap. Although quantization in the channel is not expected to seriously alter the effects described in the paper, its analysis and inclusion in the semi-classical simulation framework is required for a more accurate modeling of TFETs.

TABLE 1. Additional Parameters Required to Model Indirect Tunneling Using Kane's Model in the TCAD Simulator.

| Parameter                       | Unit                       | Si    | Ge    | Sn    |

|---------------------------------|----------------------------|-------|-------|-------|

| Density                         | kg/m <sup>3</sup>          | 2,329 | 5,323 | 7,285 |

| Elastic constants               |                            |       |       |       |

| $c_{11}$                        | $10^{12}\mathrm{dyn/cm^2}$ | 1.675 | 1.315 | 6.9   |

| $c_{12}$                        | $10^{12}\mathrm{dyn/cm^2}$ | 0.65  | 0.494 | 2.93  |

| $c_{44}$                        | $10^{12}\mathrm{dyn/cm^2}$ | 0.8   | 0.668 | 3.32  |

| Phonon energy $(\epsilon_{op})$ | meV                        | 19.0  | 8.6   | 4.14  |

| Deformation potential           | $10^{10}\mathrm{eV/m}$     | 2.45  | 0.8   | 0.8   |

In a semiconductor, tunneling can take place from either the light hole (LH) or the heavy hole (HH) band to the conduction band (CB). The HH band has a higher density of states (DOS) which acts towards an increase of the tunnel rate. However, the BTBT probability is far less influenced

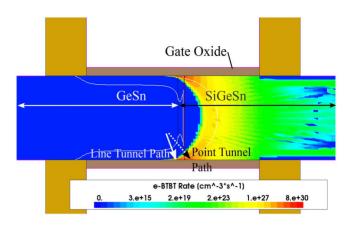

FIGURE 2. Distribution of the electron generation rate due to BTBT in the TFET simulation domain at the onset of switching. Both, BTBT along "line" and "point" tunnel paths can be observed.

by the DOS than by the effective mass of carriers, in particular in the sub-threshold regime where the transmission of the tunnel barrier is still exponentially small. Therefore, the HH→CB tunneling is orders of magnitude less probable than the LH→CB tunneling and thus ignored in the analysis. The relative influence of the HH→CB tunneling could in principle change due to the lifting of the degeneracy between HH and LH bands, e.g., in the presence of large strain or due to hole quantization in the channel region. Then, the analysis is more complicated and beyond the scope of this work.

The  $I_D-V_{GS}$  characteristics were extracted at the drain bias  $V_{DS}=0.5\,V$ . The gate voltage at which the contribution of the BTBT current at the source-channel junction starts to dominate over the joint contribution of SRH generation current and ambipolar BTBT current in  $I_D$  is defined as the off-voltage,  $V_{OFF}$ . The on-state voltage is defined as  $V_{ON}=V_{OFF}+0.5\,V$  to target the device application at a supply voltage of 0.5 V. The drain currents at  $V_{OFF}$  and  $V_{ON}$  are defined as off-state current ( $I_{OFF}$ ) and on-state current ( $I_{ON}$ ), respectively. The average sub-threshold swing is obtained by an average over four decades of the drain current above the off-state current (see Fig. 1(b)).

## **III. BAND OFFSET OPTIMIZATION IN HETERO-TFETS**

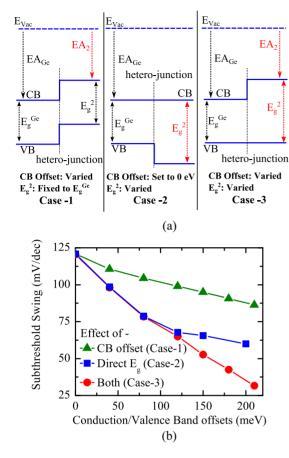

In the device under consideration, due to the overlap of the gate with the source region, electrons tunnel along two different types of tunnel paths in the on-state as shown in Fig. 2. The pn-junction lies 3 nm to the right of the hetero-junction here. The intra-material (intra-GeSn) tunnel paths begin at the valence band (VB) edge of GeSn and end at the conduction band (CB) edge of GeSn in the inversion layer under the gate which overlaps GeSn. The inter-material (GeSn to SiGeSn) tunnel paths begin at the VB edge of GeSn but end at the CB edge of SiGeSn. The mentioned intra-material tunneling which does not take place across the pn-junction is often referred to as "line tunneling" while the inter-material tunneling which crosses the pn-junction is often referred to

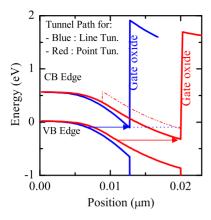

FIGURE 3. Band diagram of an n-channel TFET along the tunnel paths shown in Fig. 2 corresponding to line and point tunneling, respectively. The biasing conditions are  $V_{\rm DS}=0.5\,\rm V$  and  $V_{\rm GS}=0.6\,\rm V$  in both cases. The snapshot of the band diagrams in the figure is taken at the gate bias at which the line tunneling has just begun. At this gate bias, for the case of zero CB offset (solid red line), a large point tunnel window is already open indicating that the point tunneling has begun at lower gate bias. Similarly, for large CB offset (dotted red line), the tunnel window for point tunneling is yet to open, indicating that it will begin at a later bias point. This implies that increasing the CB offset delays the onset of point tunneling relative to that of line tunneling.

as "point tunneling", in the TFET literature. Although these names do not establish any meaningful association to the actual tunnel paths, they will be used also in this paper. The various effects discussed below are primarily linked to the competition between these two current-carrying tunnel paths.

In the case of an n-channel TFET at  $V_{DS} = 0.5 \, V_{c}$ the entire channel region in the device is depleted due to the low doping level when the device is turned off. This results in SRH generation in the channel region. Additionally, undesired tunneling at the channel-drain interface turns on because the tunnel gap of the channel material is relatively small (ambipolarity effect). As the gate voltage is ramped up, the depletion region in the channel begins to shrink and the ambipolar tunneling current reduces. At the same time an electron inversion layer begins to form in the source region which is overlapped by the gate. Along the line tunneling path, which does not cross the pn-junction, only the gate influences the band bending, whereas along the point tunneling path, which crosses the pn-junction, both gate and pn-junction influence the band bending. Hence, there is a built-in band bending due to the presence of a pn-junction along the point tunnel path which is absent along the line tunnel path. As a result, less gate bias is required to achieve the band bending at which BTBT turns on along the point tunnel path. On the contrary, larger gate bias is necessary to achieve strong band bending in the source region to turn-on BTBT along the line tunnel path. Therefore, at the onset of switching, tunneling begins at the pn-junction along the point tunneling path before it emerges along the line tunneling path. Since the hetero-junction coincides with the pn-junction apart from the small shift due to the Gaussian

doping tail, the band offsets at the hetero-junction affect the sub-threshold swing and other characteristics of the TFET. The effect of band alignment on the TFET characteristics is discussed in the following.

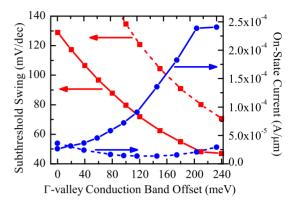

FIGURE 4. Effect of the variation of the direct CB offset at the interface on the average SS and the on-state current density of an n-channel TFET with the source doping  $(N_S)$  of  $2\times 10^{19}\,\mathrm{cm}^{-3}$  (solid line) and  $5\times 10^{19}\,\mathrm{cm}^{-3}$  (dashed line). All other parameters had the same values in both regions. For both the doping values, the performance of the n-TFET improves with increasing direct CB offset. The drain bias  $(V_{DS})$  was set to 0.5 V in the simulations

#### A. EFFECT OF BAND OFFSETS AT THE HETERO-JUNCTION

In order to analyze the effect of the band offsets, a homojunction n-channel TFET with a GeSn<sub>0.05</sub> alloy in both the source and the channel region was simulated. The band offset at the pn-junction was artificially changed by varying the direct band gap of GeSn<sub>0.05</sub> in the channel region. Increasing the Si content in the channel region results in such an increase of the direct CB offset. Variation of the Si content also changes the indirect band gap, the effective mass values, etc. of the alloy in the channel region. However, as the analysis is aimed at studying the effect of direct CB offset only, changes in the rest of the parameters is undesirable. Therefore, the direct CB offset was increased artificially by increasing the direct band gap while keeping the effective mass values and indirect gap identical in both the source and the channel region. The results of the variation of the direct CB offset on SS and on-state current density in the TFET are shown in Fig. 4 for two values of source doping (N<sub>S</sub>). It is clearly seen that increasing the direct CB offset decreases the SS in the n-TFET irrespective of source doping. Since all other tunnel parameters are given the same values in source and channel, this effect can be attributed to the direct CB offsets. The explanation of this behavior is provided below.

The point tunnel path always passes through the lowly doped n-type region as it crosses the pn-junction. In a lowly doped region the band bending is weak which results in a longer tunnel path. The line tunnel path remains entirely inside the highly doped p-type region where the band bending is strong. This makes the point tunnel path longer than the line tunnel path as shown in Fig. 3. The longer the

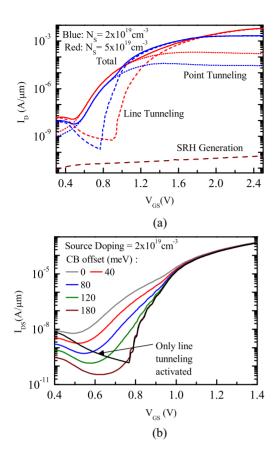

FIGURE 5. (a) Contribution of line tunneling and point tunneling to the total drain current in the absence of a direct CB offset for the source doping of  $2 \times 10^{19} \, \mathrm{cm}^{-3}$  (red) and  $5 \times 10^{19} \, \mathrm{cm}^{-3}$  (blue). Increased source doping delays the onset of line tunneling relative to that of point tunnel ing which results in the degradation of the subthreshold swing. (b) Effect of the direct CB offsets on the  $I_D - V_{GS}$  characteristics of the n-channel TFET. As the CB offset increases, the point tunneling is suppressed which significantly improves the slope of the curves.  $V_{DS}$  is set to 0.5 V.

FIGURE 6. Band diagram along the point tunnel path for different direct CB offsets. The snapshot of the band diagrams is taken at the gate bias at which the line tunneling has just begun. As seen in the figure, the point tunnel path becomes longer and the "point tunnel window" shrinks with increasing the direct CB offset. This results in the suppression of the point tunneling. Note that the actual pn-junction is shifted inside the SiGeSn material due to the doping tail. Due to the inclination of the point tunnel path to the channel direction, the pn-junction along the point tunnel path lies  $\sim 4.5$  nm inside the SiGeSn region as labeled in the figure.  $V_{\rm DS}$  was set to 0.5 V.

tunnel path, the smaller the tunnel rate and the larger the SS<sup>1</sup>. Without a CB offset the point tunneling begins before the onset of line tunneling as shown in Fig. 5(a). The drain current due to line tunneling increases faster than that due to point tunneling as it is determined by the rapid overlap between the DOS of initial and final states. However, since point tunneling begins earlier than line tunneling, the SS of the total drain current is determined mainly by that of point tunneling with its degraded SS. Increasing the direct CB offset decreases the rate of point tunneling. (see Fig. 3). It also reduces the point tunnel window at the onset of line tunneling as demonstrated in Fig. 6. The above three effects, namely, increased tunnel gap, reduced tunnel window, and delayed onset reduce the contribution of point tunneling to the total drain current. The I<sub>D</sub>-V<sub>GS</sub> plots for different CB offsets are presented in Fig. 5(b). The initial "bulge" in the curves due to the early occurrence of point tunneling gradually reduces with increasing CB offset and finally disappears at the direct CB offset of 0.18 eV. The I<sub>D</sub>-V<sub>GS</sub> curve for the case of 0.18 eV CB offset coincides with the I<sub>D</sub>-V<sub>GS</sub> curve with only line tunneling activated which suggests that the point tunneling is indeed suppressed. In this way, an increasing CB offset enhances the SS in the case of an n-channel TFET.

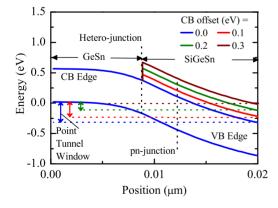

The artificial increase in the direct band gap also results in the suppression of the direct BTBT at the channel-drain interface which results in reduced leakage current. As a result, the steeper branch of the line tunnel current which was initially masked by the high level of the leakage current, appears in the I<sub>D</sub>-V<sub>GS</sub> plot. Thus, in addition to the increased CB offset, the increased direct band gap also contributes to the improvement of the SS. In order to study the individual contributions of the CB offset and direct band gap on the SS, the CB offset was varied by changing the electron affinity of the channel material and keeping the direct gap fixed (See case-1 of Fig. 7(a)). Similarly, the direct gap was varied while keeping the CB offset at the interface fixed to zero, which results in the increase in the VB offset (See case-2 of Fig. 7(a)). The rest of the parameters in the BTBT model

1. The BTBT current is governed by the WKB probability

$$\exp\left(-\frac{4\sqrt{2m_{\rm red}E_{\rm g}^3}}{3q\hbar F}\right). \tag{1}$$

Assuming that the local electric field F is proportional to the applied gate voltage, it immediately turns out that the slope of  $I_{\rm D}$  as function of  $V_{\rm GS}$  (=  $\frac{d(\log I_{\rm D})}{dV_{\rm GS}}$ ) becomes proportional to  $E_{\rm g}^{3/2}$ . Hence, at a given  $V_{\rm GS}$ , the SS (inverse slope) is expected to decrease with increasing  $E_{\rm g}$ . However, the simulation of the average SS results in an increase with increasing direct band gap. The reason for this apparent anomaly lies in the method for calculating the average SS. It is obtained by averaging over four decades of the drain current starting at the off-current as shown in Fig. 1(b). Increasing the band gap reduces the tunnel probability exponentially, and the  $I_{\rm D}$ -VGs curve in Fig. 1(b) shifts downwards with the consequence that its flatter portion enters the averaging interval. Thus, the average SS increases with increasing the band gap, although the above equation predicts the opposite for the continuous SS. The steep portion of the  $I_{\rm D}$ -VGs curve is buried below the level of the leakage current, hence becomes inefficacious for the TFET performance.

FIGURE 7. (a) Schematic showing the three cases considered to investigate the individual effects of CB offset and direct band gap on the SS of a n-TFET. The quantities that are varied in each case are denoted in red. The change in the VB offset in first two cases can be ignored as it is not expected to exert any influence on the SS of the n-TFET. (b) Variation of the SS due to variation of the direct CB offset only, the direct band gap only, and both the quantities is plotted versus CB offset (cases 1 and 3) or VB offset (case 2). This procedure decouples the effects of increasing direct CB offset and increasing direct  $E_q$  on the SS. The drain bias ( $V_{DS}$ ) was set to 0.5 V in the simulations.

were set to their values in Ge in the simulations of the above cases. The effects of the variations in the above mentioned quantities on the SS are shown in Fig. 7(b). It is clearly observed that both the CB offset and the direct Eg improve the SS in the absence of the other. However, a combination of the two effects can further enhance the SS. For lower values of CB offsets, the increase in the direct Eg predominantly controls the SS. The contribution of the CB offsets is pronounced at higher values.

In the above explanation the indirect CB edges have been ignored. In a semiconductor with small direct band gap the tunnel rate of an electron from the LH band to the indirect CB gives a negligible contribution to the total tunnel rate [20], [21]. Hence, the effect of the indirect CB offset can be ignored in the analysis. If the direct band gap in the source material is wide, the variation of the indirect CB offset is expected to have the same consequences demonstrated for the direct CB offset. It must be noted that the indirect BTBT has been ignored only while explaining the effect of

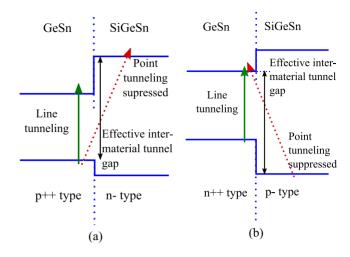

FIGURE 8. Schematic diagram showing the effect of increased band offsets on the point tunneling in n-channel and p-channel TFETs. The band offsets increase the effective inter-material tunnel gap which in turn results in the suppression of point tunneling. (a) n-TFET. (b) p-TFET.

band offsets, in order to make it lucid. Both direct and indirect BTBT mechanisms were activated in all the simulations reported in the paper.

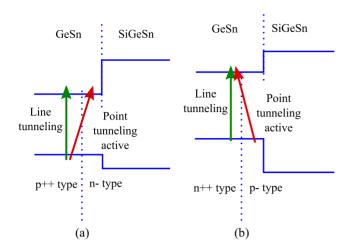

The same exercise for the p-channel TFET yields that the LH band offset affects the SS in the same manner as explained above for the CB offset. The LH band offset is the difference of the LH band maxima in the two materials at the hetero-junction. HH band can be ignored for the tunnel current due to the reasons explained earlier. Therefore, the "effective" VB edge for tunneling is the LH band edge. This is particularly important in the case of strain as will be explained later.

In short, the larger band offset results in larger effective inter-material tunnel gap which suppresses the point tunneling and improves the SS. This is schematically shown in Fig. 8(a) and (b) for the case of n-channel and p-channel TFETs, respectively.

### B. EFFECT OF VARIATIONS IN THE SOURCE DOPING

The increased source doping (N<sub>S</sub>) improves the SS as it results in a sharper band bending [13]. However this effect saturates at high N<sub>S</sub>. The effect of the variation in the source doping (N<sub>S</sub>) on the relative strength of line and point tunneling is presented in Fig. 5(a). Increasing N<sub>S</sub> shifts the SS vs. CB offset plot towards higher CB offset values. This is because the onset of line tunneling is delayed with increasing N<sub>S</sub> (which is similar to the threshold voltage shift in a MOSFET with increasing channel doping) while the onset of point tunneling remains unaffected (see Fig. 5(a)). Therefore, the larger CB offset is required to delay the onset of point tunneling such that it occurs after line tunneling. The slight increase in the strength of point tunneling might lead one to conclude that the point tunneling is slightly delayed with increased source doping which is misleading.

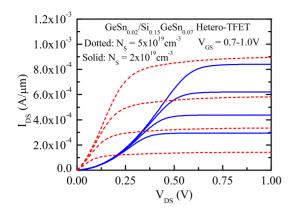

FIGURE 9. Output characteristics ( $I_D$ - $V_{DS}$ ) of a heterojunction n-TFET for two different doping concentrations. Here, gate voltage is defined relative to off-voltage of the TFET, i.e.,  $V'_G = V_{GS} - V_{OFF}$ . The definition of off-voltage is schematically described in Fig. 1(b).

The effect of source doping  $(N_S)$  on the simulated output characteristics of an n-channel TFET is shown in Fig. 9. Increased source doping results in a rapid increase of the drain current when  $V_{DS}$  is ramped up for any given  $V_{GS}$  [22].

# C. EFFECT OF MISALIGNMENT BETWEEN PN- AND HETERO-JUNCTION

The pn-junction was assumed to coincide with the hetero-junction in the above analysis. The in-situ doping during growth can be adjusted to deliberately place the pn-junction away from the hetero-junction which would provide an additional mean of tuning the device characteristics. Process variations during the growth of the materials can also result in a misalignment between pn-junction and hetero-junction. Device simulations were performed to study the impact of this misalignment on the TFET characteristics. A hetero-structure system consisting of GeSn<sub>0.05</sub>/Si<sub>0.08</sub>GeSn<sub>0.06</sub> was selected for the simulations. The same device geometry as in Fig. 1(a) was used and n-channel TFETs were simulated. The position of the pn-junction in the device was kept unchanged while varying the position of the hetero-junction as demonstrated schematically in Fig. 10(a).

The on-state current density and the SS of the device are plotted in Fig. 10(b) versus the distance between hetero-junction and abrupt pn-junction, i.e., for the case where the Gaussian doping tail is ignored. The on-state current density becomes maximum when the hetero-junction is aligned with the actual pn-junction. The SS becomes minimum in case of a slight misalignment, i.e., when the hetero-junction is 3 nm away from the pn-junction. This is a result of the shift of the actual pn-junction from the location of the abrupt junction due to the inclusion of the Gaussian doping tail. The size of this tail determines the misalignment.

This result is nothing but a consequence of the effect of band offsets on the SS as explained in the previous

FIGURE 10. (a) Schematic representation of the variation of the position of the pn-junction. (b) Effect of misalignment between pn-junction and hetero-junction on the SS and the on-state current density.

subsection. Since the BTBT rate first arises in the vicinity of the pn-junction when the transistor turns on, the band offsets at the pn-junction affect the SS. In the case of junction misalignment, the pn-junction is located inside one of the two materials, GeSn or SiGeSn. As the band offsets at the pn-junction are zero (bands are continuous inside each individual material), the SS degrades as the pn-junction stirs out of the hetero-junction. This is schematically shown in Fig. 11(a) and (b) for the cases of n-channel and p-channel TFETs, respectively. The change in the SS is not abrupt despite the abrupt change of the band offsets at the pn-junction with misalignment. BTBT is a non-local process and its rate is distributed over a relatively wide region at the onset of turn-on, hence the abruptness in the band offsets is "averaged" over this region which results in a smooth change of the SS.

FIGURE 11. Schematic diagram showing the effect of misalignment of the pn-junction with the heterojunction on the point tunneling in n-channel and p-channel TFETs. The effective tunnel gap for point tunneling is equal to that for line tunneling which results in enhanced point tunneling.

(a) n-TFET. (b) p-TFET.

## D. EFFECT OF STRAIN IN THE GESN LAYER

When point tunneling is suppressed by large band offsets, the line tunneling contribution to the total current increases. Since line tunneling takes place entirely in GeSn (when the pn-junction is aligned with the hetero-junction), the strain in SiGeSn is less likely to affect the total tunnel rate. Therefore, the effect of strain in GeSn on the band structure is discussed here. Biaxial strain is induced in GeSn by growing it over a lattice-mismatched substrate. Biaxial tensile (compressive) strain lowers (raises) the direct CB edge. On the contrary, the biaxial tensile (compressive) strain raises (lowers) the LH band edge. As a result, the effective direct tunnel gap ( $E_{Tun}^{\Gamma} = E_{CB}^{\Gamma} - E_{LH}^{\Gamma}$ ) reduces rapidly by applying biaxial tensile strain [17]. This increases the tunnel rate which can improve the on-current of the TFET.

## **IV. GESN/SIGESN COMPOSITION VARIATION**

The "band-offset engineering" can be effectively employed in hetero-structure TFETs by selecting suitable material pairs which can deliver large direct CB and LH band offset. The GeSn/SiGeSn alloy system is particularly useful for TFET application due to the small direct band gap of GeSn. Addition of Si to GeSn significantly increases the direct band gap of the alloy. Therefore, using GeSn as a source material will improve the line tunneling rate while introducing SiGeSn as channel and drain material will suppress ambipolarity caused by tunneling at the drain side. Furthermore, a tunable direct CB offset between GeSn and SiGeSn can be used to suppress point tunneling and to improve the SS. On the other hand, reducing the band gap of GeSn and SiGeSn by increasing the Sn content also increases the SRH generation rate which leads to a larger off-state leakage current. In order to find the alloy composition that can deliver minimum SS, the three-dimensional design space of GeSn/SiGeSn is

spanned by simulating the double-gate TFET of the previous section. The band structure parameters required for BTBT have been obtained from empirical pseudo-potential calculations [17].

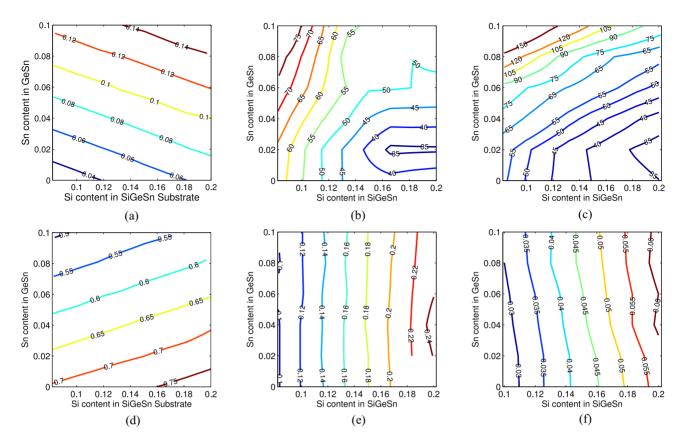

Concerning the growth of the GeSn/SiGeSn alloy system, it is generally assumed that SiGeSn is relaxed while the strain in the GeSn layer is generated by pseudomorphic growth of GeSn over a buffer layer with the same in-plane lattice constant as that of SiGeSn. In other words, the in-plane lattice constant of strained-GeSn is matched to that of the relaxed SiGeSn layer. The strain analysis presented here is aimed at examining the effect of introducing small strain in the GeSn active layer. A strain of 0.5% is chosen to ensure that the strain effect will be perceptible from the transfer characteristics. The cases of GeSn layers with no strain, 0.5% compressive strain, and 0.5% tensile strain are considered. Fixing the strain in GeSn reduces the three-dimensional design space of the alloy system to a twodimensional space, viz, the Sn content in GeSn and the Si content in SiGeSn. The Sn content in SiGeSn is fixed as soon as the Si content in SiGeSn and Sn content in GeSn is fixed for each individual strain value. All the simulation results are displayed in the form of contour diagrams of the output quantities against the Si content in SiGeSn (x-axis) and the Sn content in GeSn (y-axis). In the following text, the direct CB offset is the difference between the energy of the  $\Gamma$ -valley CB edge in GeSn and that of the  $\Gamma$ -valley CB edge in SiGeSn ( $E_{CB}^{\Gamma}$ (GeSn) –  $E_{CB}^{\Gamma}$ (SiGeSn)). Similarly, the LH band offset is defined as the difference between LH band energy in GeSn and that in SiGeSn.

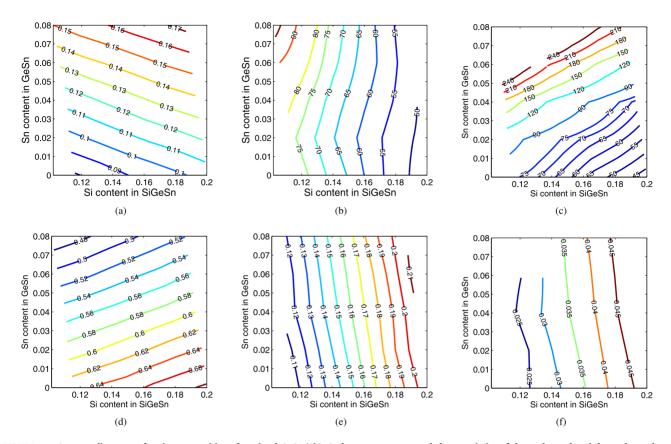

# A. LATTICE-MATCHED COMPOSITIONS OF GESN/SIGESN

The growth of relaxed GeSn layers lattice-matched to SiGeSn is expected to result in a better quality of the GeSn/SiGeSn interface with low interface trap density. Therefore, the case of lattice-matched compositions is particularly important. The lattice-matched compositions of GeSn/SiGeSn are obtained by setting the Sn content in GeSn and the Si content in SiGeSn to a suitable value and selecting the Sn content in SiGeSn such that both alloys have the same lattice constant. The Sn content in the SiGeSn layer that is lattice matched to the GeSn layer is given in Fig. 12(a) in form of a contour diagram.

A GeSn/SiGeSn hetero n-channel TFET was simulated over a suitable range of Sn content in GeSn and Si content in SiGeSn. The average SS was extracted by averaging the SS over four decades of I<sub>D</sub>. It is plotted in the form of a contour diagram in Fig. 12(b). The contour diagram shows two regions with distinctive contour shapes in the design space. The shape of the contours of SS resembles the shape of the contours of the direct CB offset (Fig. 12(e)) at low Si content, while at high Si content it resembles the contours of the band gap of SiGeSn (Fig. 12(d)). At low Si content, the direct CB offset is small, but it changes significantly with rising Si content. Therefore, it has a high impact on the subthreshold characteristics as explained in the previous section.

FIGURE 12. Contour diagrams of various quantities of relaxed-GeSn/SiGeSn hetero-structures and characteristics of the n-channel and the p-channel TFETs. The latter were simulated using the compositions given by the contour diagram in (a). The compositions of SiGeSn are selected such that the alloy is lattice matched to relaxed GeSn alloy for various values of Sn content. (a) Sn content in SiGeSn lattice-matched to relaxed GeSn. (b) Sub-threshold swing of an n-TFET (mV/dec). (c) Sub-threshold swing of a p-TFET (mV/dec). (d)  $E_q$  in SiGeSn (eV). (e) Direct CB offset (eV). (f) LH band offset (eV).

At high Si content, the direct CB offset is large and its effect on the SS is already saturated. Therefore, the SS depends on the magnitude of SRH generation and the ambipolarity due to tunneling in the drain region. Both of these quantities increase the leakage current. The SRH generation and the ambipolarity effects depend exponentially on the band gap of SiGeSn. Therefore, the SS of the n-channel TFET takes the shape of the contours of the band gap of SiGeSn at high Si content.

A p-channel TFET was also simulated to extract the average SS. The contour diagram of the average SS is given in Fig. 12(c). The diagram shows two regions with distinctive contour shapes as in the case of the SS diagram of the n-TFET in Fig. 12(b). They have the same origin as already discussed for the case of the n-channel TFET. However, the influence of the LH band offset on the SS is reduced. This comes from the lower sensitivity of the LH band offsets to the Si content in SiGeSn as compared to the sensitivity of the direct CB offsets to the Si content. Therefore, the contour diagram of the SS resembles the contours of the band gap of SiGeSn for both high and low Si content. For low Sn content in the GeSn layer, the band gap in the SiGeSn layer is sufficiently large which reduces the influence of the band gap on SS. Therefore, in the bottom half of the SS contour diagram

the contours are vertically arranged resembling those of the VB offset.

Fig. 12(a), (b), and (c) provide a relation between the composition of the GeSn/SiGeSn alloy system and the simulated SS of n- and p-channel TFETs for that specific composition. Selection of the same alloy composition for both n- and p-channel TFETs could ease the fabrication process of complementary TFETs. The contour diagrams in Fig. 12 can assist technologists in selecting the most suitable GeSn/SiGeSn composition.

# **B. STRAINED GESN WITH 0.5% COMPRESSIVE STRAIN**

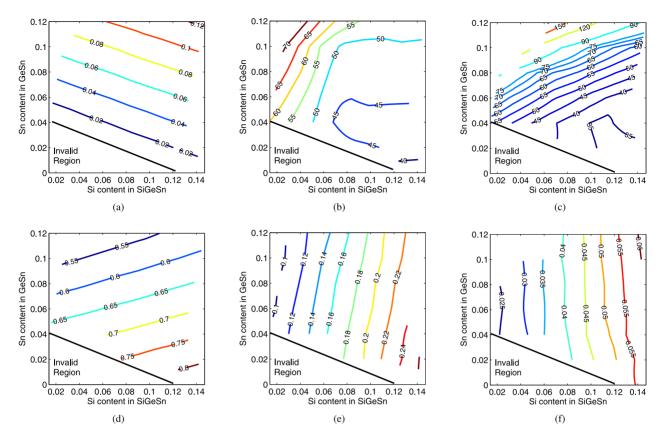

The GeSn/SiGeSn alloy compositions with 0.5% compressively strained GeSn and relaxed SiGeSn were obtained by the same procedure as outlined above except that, here, SiGeSn was lattice-matched to the in-plane lattice constant of compressively strained GeSn instead of relaxed GeSn. The Sn content in SiGeSn that is lattice-matched to the in-plane lattice constant of the 0.5% compressively strained GeSn is given in Fig. 13(a). The n- and p-channel TFETs with a suitable range of alloy compositions were simulated and the average SS was extracted. The contour diagram of the average SS of the n-TFET for different alloy compositions is shown in Fig. 13(b) along with the contour diagrams of the

FIGURE 13. Contour diagrams of various quantities of strained-GeSn/SiGeSn heterostructures and characteristics of the n-channel and the p-channel TFETs. The latter were simulated using the compositions given by the contour diagram in (a). The GeSn layer was biaxially strained with 0.5% compressive strain. The relaxed SiGeSn layer was lattice matched to the strained GeSn layer. (a) Sn content in the SiGeSn lattice-matched to biaxially strained GeSn with 0.5% compressive strain. (b) Sub-threshold swing of an n-TFET (mV/dec). (c) Sub-threshold swing of an p-TFET (mV/dec). (d) E<sub>g</sub> in SiGeSn (eV). (e) Direct CB offset (eV). (f) LH band offset (eV).

direct CB offset and the band gap in SiGeSn. The SS for the strained case shows the same trends as for the relaxed case discussed in the previous subsection. The dominant influence of the band offsets for low Si content and the dominant influence of the band gap of SiGeSn for high Si content is again visible in the contour diagrams. A major difference to the SS contours in the relaxed case (Fig. 12(b) is the range of the Si content in SiGeSn. Comparing the contour diagrams of the SS in these two cases suggests that the same SS can be obtained with strained GeSn for smaller values of Si content in SiGeSn. This means that the technological constraints on the growth of SiGeSn can be circumvented by using compressively strained GeSn. In this way, a compressive strain in GeSn can provide a wider design space for selecting the GeSn/SiGeSn alloy compositions for n-TFET applications.

The contour diagram of the average SS of p-TFETs for different alloy compositions is shown in Fig. 13(c). The shape of the contours suggests that the band gap of SiGeSn seems to exert influence on the SS. This is because the LH band offsets (Fig. 13(f)) do not change rapidly with Si content and hence do not have a significant impact on the SS. Comparing the contours of the SS of the p-TFET between the relaxed and the strained case for the same values of Si and Sn contents leads to the conclusion that the

SS has markedly improved in the strained case. This is a consequence of the increased band gap in SiGeSn resulting in the suppression of ambipolar leakage. In this way, biaxial compressive strain in GeSn improves the design space to select the alloy compositions for p-TFET applications.

## C. STRAINED GESN WITH 0.5% TENSILE STRAIN

Also in this case the GeSn/SiGeSn alloy compositions were obtained by the above-mentioned method, except that here the lattice constant of SiGeSn was matched to the in-plane lattice constant of GeSn with 0.5% tensile strain. The Sn content in the SiGeSn lattice matched to the biaxially strained GeSn with 0.5% tensile strain is shown in Fig. 14(a). The n-channel TFET was simulated over a suitable range of alloy compositions. The contour diagram of the average SS is displayed in Fig. 14(b). Similar to the previous two cases, the SS shows the influence of the direct CB offset and the band gap in SiGeSn. However, compared to the SS contour diagrams in the previous two cases there is some degradation in the SS. This is a result of the increased Sn content in SiGeSn relative to its Si content which reduces the band gap of SiGeSn. The result is a stronger SRH generation and a more pronounced ambipolarity which causes the degradation of the SS.

FIGURE 14. Contour diagrams of various quantities of strained-GeSn/SiGeSn heterostructures and characteristics of the n-channel and the p-channel TFETs simulated using the heterostructures with the compositions given by the contour diagram in (a). The GeSn layer was biaxially strained with a 0.5% tensile strain. (a) Sn content in the SiGeSn lattice-matched to biaxially strained GeSn with 0.5% tensile strain. (b) Sub-threshold swing of an n-TFET (mV/dec). (c) Sub-threshold swing of a p-TFET (mV/dec). (d) Eq in SiGeSn (eV). (e) Direct CB offset (eV). (f) LH band offset (eV).

The SS contour diagram of the p-TFET (Fig. 14(b)) shows that for the same Si and Sn contents, the SS has significantly degraded compared to the zero strain case. The SS contours seem to follow the trends observed in the band gap of SiGeSn. This is a result of negligible change in the LH band offset over the given composition range and increased ambipolar leakage due to the lower band gap of SiGeSn.

### D. LIMITATIONS OF THE ABOVE ANALYSIS

For the above analysis the band alignment between GeSn and SiGeSn was obtained by using Jaros' [24] analytical model as explained in Ref. [23]. The average SS of the TFETs strongly depends on the direct CB offset or the VB offset. Deviations of the experimental band offsets from those calculated by the analytical model might change the resulting SS. The CB and LH effective mass values along (001) direction have been used in the Kane model irrespective of the direction of the tunnel path. Since the SS mainly depends on the band gaps and band alignments, this will not change the SS much. However, for a more accurate modeling of BTBT, the effective masses along the tunnel direction must be used. The SRH parameters of Germanium [18] have been used to model SRH in both GeSn and SiGeSn alloys. Therefore, the effect of the alloy composition on

the SRH parameters is not covered by the above analysis. As shown in Fig. 5(a), "default" SRH lifetimes result in a negligible thermal generation current. However, higher trap concentrations in conjunction with field-enhanced generation (trap-assisted tunneling) could severely degrade the SS. The effect of band gap narrowing due to heavy doping which would alter the effective tunnel gap was also not taken into account. Channel quantization in the thin GeSn channel was modeled using the semi-classical Modified Local Density Approximation (MLDA) model [12], which cannot exactly predict the delayed turn-on. A possible way to include the effect of delayed turn-on using semiclassical simulations is outlined in Ref. [21]. In this procedure, the transfer characteristics are shifted forward by a potential equal to that of the first energy level from the base of the triangular well in the channel. Since the shift is not going to change the SS of the I<sub>D</sub>-V<sub>GS</sub> plots, it is less likely affect the results presented in the paper. It is, however, advisable to follow the procedure for a more accurate modeling of the effect of channel quantization using semiclassical approach.

### V. CONCLUSION

In a hetero-junction TFET with gate-overlapped source, a material with small direct gap in the source increases the

BTBT rate while the wide-gap material in the channel and drain regions reduces the off-state leakage current caused by ambipolarity and SRH generation. Furthermore, when the hetero-junction coincides with the pn-junction, the performance of the TFET is also influenced by the valence and conduction band offsets between the two materials which was studied in this work. The following conclusions can be drawn based on the simulation results:

- The performance of the n-channel GeSn/SiGeSn TFET is influenced by the direct CB offset at the hetero-junction as well as the direct band gap of the channel and drain material. The larger the band offset (E<sup>Γ</sup><sub>CB</sub>(SiGeSn) E<sup>Γ</sup><sub>CB</sub>(GeSn)), the smaller the average sub-threshold swing.

- 2) The performance of the p-channel TFET is influenced by the LH band offset at the hetero-junction along with the direct band gap of the channel and drain material. The larger the band offset  $(E_{LH}^{\Gamma}(GeSn) E_{LH}^{\Gamma}(SiGeSn))$ , the smaller the average sub-threshold swing and the higher the on-current.

An immediate extension to the above conclusion is that the misalignment between pn- and hetero-junction degrades the sub-threshold swing and the on-current of the TFET. This is a consequence of zero band offsets directly *at* the pn-junction as it moves away from the hetero-junction.

The direct CB and LH band offsets at the GeSn/SiGeSn interface can be tuned by varying the alloy compositions to further improve the TFET performance. The suitable range of alloy compositions was analyzed by simulating the n- and p-channel TFETs with gate-overlapped source. The constraint of limited Si content on the growth of SiGeSn which is required for the fabrication process of GeSn/SiGeSn TFETs was taken into consideration in the analysis. The conclusions of the analysis are as follows:

- In the case of n-channel TFETs, the inclusion of compressive strain in the GeSn layer can provide good performance at lower Si content compared to the case of relaxed GeSn. This will improve the design space available for the selection of alloy compositions for n-TFETs. Tensile strain in the GeSn layer reduces the design space for the selection of alloy compositions.

- 2) In the case of p-channel TFETs, compressive strain improves the design space whereas tensile strain reduces the design space as in the case of n-TFETs

Hence, the GeSn/SiGeSn alloy composition with compressive strain in GeSn will be suitable for both p- and n- channel TFETs. The provided contour diagrams that relate the sub-threshold swing to the alloy compositions can help technologists in selecting the most suitable composition for specific requirements.

### **REFERENCES**

- K. L. Wang, "Issues of nanoelectronics: A possible roadmap," J. Nanosci. Nanotechnol., vol. 2, nos. 3–4, pp. 235–266, 2002.

- [2] A. M. Ionescu and H. Riel, "Tunnel field-effect transistors as energy-efficient electronic switches," *Nature*, vol. 479, pp. 329–337, Nov. 2011.

- [3] K. Moselund, V. Pott, D. Bouvet, and A. Ionescu, "Abrupt current switching due to impact ionization effects in Ω-MOSFET on low doped bulk silicon," in *Proc. 37th Eur. Solid State Device Res. Conf.* (ESSERC), Munich, Germany, 2007, pp. 287–290.

- [4] O. Loh and H. Espinosa, "Nanoelectromechanical contact switches," Nature Nanotechnol., vol. 7, pp. 283–295, Apr. 2012.

- [5] A. Walke et al., "Fabrication and analysis of a Si/Si<sub>0.55</sub>Ge<sub>0.45</sub> heterojunction line tunnel FET," *IEEE Trans. Electron Devices*, vol. 61, no. 3, pp. 707–715, Mar. 2014.

- [6] G. Zhou et al., "InGaAs/InP tunnel FETs with a subthreshold swing of 93 mV/dec and I<sub>ON</sub>/I<sub>OFF</sub> ratio near 10<sup>6</sup>," IEEE Electron Device Lett., vol. 33, no. 6, pp. 782–784, Jun. 2012.

- [7] R. Asra et al., "A tunnel FET for V<sub>DD</sub> scaling below 0.6 V with a CMOS comparable performance," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 1855–1863, Jul. 2011.

- [8] H. Riel et al., "InAs-Si heterojunction nanowire tunnel diodes and tunnel FETs," in Proc. IEEE Int. Electron Devices Meeting (IDEM), San Francisco, CA, USA, 2012, pp. 16.6.1–16.6.4.

- [9] S. Richter et al., "SiGe on SOI nanowire array TFETs with homoand heterostructure tunnel junctions," in Proc. IEEE 14th Int. Conf. Ultimate Integr. Silicon (ULIS), Coventry, U.K., 2013, pp. 25–28.

- [10] K. J. Kuhn, "Considerations for ultimate CMOS Scaling," *IEEE Trans. Electron Devices*, vol. 59, no. 7, pp. 1813–1828, Jul. 2012.

- [11] A. Schenk, R. Rhyner, M. Luisier, and C. Bessire, "Simulation study of nanowire tunnel FETs," in *Proc. 70th Device Res. Conf. (DRC)*, University Park, TX, USA, 2012, pp. 201–202.

- [12] Sentaurus Device User Guide, Version 2013.03, Synopsys Inc., Mountain View, CA, USA, 2013.

- [13] S. Sant, Q. Zhao, D. Buca, S. Mantl, and A. Schenk, "Analysis of GeSn-SiGeSn hetero-tunnel FETs," in *Proc. IEEE Simul. Semicond. Process. Devices (SISPAD)*, Yokohama, Japan, 2014, pp. 125–128.

- [14] Sentaurus Device Monte Carlo User Guide, Version 2013.03, Synopsys Inc., Mountain View, CA, USA, 2013.

- [15] E. O. Kane, "Zener tunneling in semiconductors," J. Phys. Chem. Solids, vol. 12, no. 2, pp. 181–188, 1959.

- [16] E. O. Kane, "Theory of tunneling," J. Appl. Phys., vol. 32, no. 1, pp. 83–91, Jan. 1961.

- [17] S. Sant and A. Schenk, "Pseudopotential calculations of strained-GeSn/SiGeSn hetero-structures," Appl. Phys. Lett., vol. 105, no. 16, 2014, Art. ID 162101.

- [18] G. Hellings et al., "Electrical TCAD simulations of a germanium pMOSFET technology," *IEEE Trans. Electron Devices*, vol. 57, no. 10, pp. 2539–2546, Oct. 2010.

- [19] O. Penzin, G. Paasch, F. O. Heinz, and L. Smith, "Extended quantum correction model applied to six-band k · p valence bands near silicon/oxide interfaces," *IEEE Trans. Electron Devices*, vol. 58, no. 6, pp. 1614–1619, Jun. 2011.

- [20] M. Luisier and G. Klimeck, "Simulation of nanowire tunneling transistors: From the Wentzel-Kramers-Brillouin approximation to full-band phonon-assisted tunneling," J. Appl. Phys., vol. 107, Apr. 2010, Art. ID 084507.

- [21] K. Kao et al., "Direct and indirect band-to-band tunneling in germanium-based TFETs," IEEE Trans. ELectron Devices, vol. 59, no. 2, pp. 292–301, Feb. 2012.

- [22] L. Michielis, L. Lattanzio, and A. Ionescu, "Understanding the super-linear onset of tunnel-FET output characteristic," *IEEE Electron Device Lett.*, vol. 33, no. 11, pp. 1523–1525, Nov. 2012.

- [23] P. Moontragoon, R. A. Soref, and Z. Ikonic, "The direct and indirect bandgaps of unstrained Si<sub>x</sub>Ge<sub>1-x-y</sub>Sn<sub>y</sub> and their photonic device applications," *J. Appl. Phys.*, vol. 112, no. 7, Oct. 2012, Art. ID 073106.

- [24] M. Jaros, "Simple analytical model for heterojunction band offsets," Phys. Rev. B, vol. 37, no. 12, pp. 7112–7114, 1988.

Authors' photographs and biographies not available at the time of publication.