# A Flexible 0.18 μm BiCMOS Technology Suitable for Various Applications

Takashi Hashimoto, *Member, IEEE*, Yusuke Nonaka, Tatsuya Tominari, Tsuyoshi Fujiwara, Tsutomu Udo, Hidenori Satoh, Kunihiko Watanabe, Tomoko Jimbo, Hiromi Shimamoto, and Satoru Isomura

Abstract—Hitachi's SiGe BiCMOS technology, which integrates 0.18  $\mu$ m CMOS and a SiGe heterojunction bipolar transistor (HBT), does not degrade MOS or bipolar performance. The BiCMOS process is divided into blocks, and the ordering of their processing is optimized so that they do not interfere with each other. Low-thermal-budget SiGe HBT formation is achieved using a minimal-moisture-desorption oxide layer, thereby avoiding disturbing the CMOS process. This technology, which can also be applied to the 0.13  $\mu$ m generation, has been used for applications ranging from high-speed ones like automotive radar and 40 Gbps optical communication to consumer ones like wireless.

*Index Terms*—Bipolar transistor, BiCMOS, hydrogen termination, SiGe heterojunction bipolar transistor (HBT).

#### I. INTRODUCTION

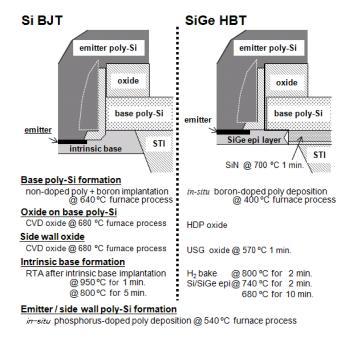

**B** ICMOS TECHNOLOGIES have a long history of being used for various applications because they enable a high-speed and low-noise bipolar circuit to be flexibly combined with a low-dissipation CMOS circuit on the same chip. Initially, the formation of a bipolar junction transistor (BJT) in a BiCMOS process was very simple, so the BJT formation did not affect the MOS process or MOS device characteristics. Only a few additional processing steps were needed for forming the vertical junction structure of the BJT for the  $1.3 \,\mu\text{m}$  and  $2.0 \,\mu\text{m}$  generations [1]–[6]. Since the base region should be as thin as possible in the BJT formation process, the MOS-first process scheme was a natural choice for suppressing undesirable diffusion of the narrow and highimpurity-concentration emitter and base layers during MOS gate formation.

A double-polysilicon self-aligned BJT structure became possible with the  $0.8 \,\mu$ m generation, and a complex

Manuscript received September 21, 2013; revised November 26, 2013; accepted December 3, 2013. Date of publication December 11, 2013; date of current version January 30, 2014. The review of this paper was arranged by Editor R. Singh.

T. Hashimoto, Y. Nonaka, T. Tominari, T. Fujiwara, H. Satoh, T. Jimbo, and S. Isomura are with the Micro Device Division, Hitachi Ltd., Tokyo 198-8512, Japan (e-mail: takashi.hashimoto.rf@hitachi.com; yusuke.nonaka.xs@hitachi.com; tatsuya.tominari.xb@hitachi.com; tsuyoshi. fujiwara.gt@hitachi.com; hidenori.sato.rq@hitachi.com; tomoko.jimbo. vq@hitachi.com; satoru.isomura.ra@hitachi.com).

T. Udoh is with Sony Semiconductor Corporation, Kumamoto 869-1102, Japan (e-mail: Tsutomu.Udo@jp.sony.com).

H. Shimamoto is with Renesas Design Corporation, Kokubunji, Tokyo 187-8588, Japan (e-mail: hiromi.shimamoto.yk@rdc.renesas.com).

K. Watanabe is with KOGA SOKEN Ltd., Hachiouji, Tokyo 192-0904, Japan (e-mail: watanabek@rd5.so-net.ne.jp).

Digital Object Identifier 10.1109/JEDS.2013.2294202

bipolar /BiCMOS process was added [7]-[12]. The selfaligned BJT structure and deep trench isolation structure boosted transistor performance by reducing the parasitic resistance and capacitance. The next wave of BiCMOS technologies included new circuit technologies combining the same BJT high-performance as the base bipolar process with CMOS devices. The BiCMOS process enabled the fabrication of a composite circuit containing a CMOS logic gate and a current amplification circuit consisting of BJTs. A composite BiCMOS circuit that balanced circuit speed and power dissipation was developed in the 1980s [7]. Since CMOS performance had become good enough to handle the complex signal processing requirements of the  $0.25 \,\mu m$  generation, circuits combining high-speed emitter-coupled logic (ECL) and high-density CMOS received attention as an alternative to BiCMOS gate technology [10].

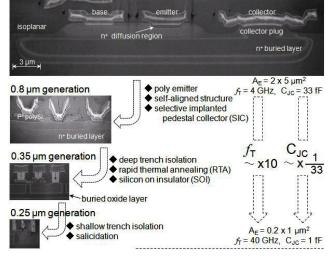

The CMOS technology that came with the 0.25  $\mu$ m generation was a driver of new technologies such as shallow trench isolation and silicide formation, which reduced the parasitic resistance and capacitance of bipolar transistors [13]. The cutoff frequency ( $f_T$ ) improved from 4 GHz to 40 GHz, and the parasitic collector-base capacitance (Cjc) decreased from 33 fF to 1 fF, as illustrated in Fig. 1. The emitter size was reduced from  $2 \mu m \times 5 \mu m$  to  $0.2 \mu m \times 1 \mu m$  with increased collector current density, and the ECL gate delay time was reduced from 250 ps/gate to 25 ps/gate [11]. An accompanying technology was the application of a thick bonded SOI substrate in the BiCMOS process combined with deep trench isolation, enabling fabrication of RF leakage current through the substrate [8]–[10], [12]–[14].

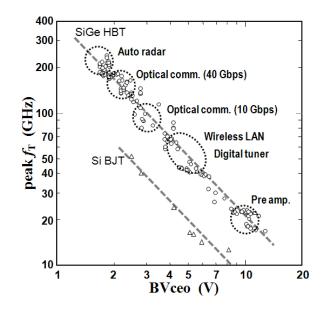

In the 2000s, SiGe technology has played the leading role in the formation of shallow base regions and thereby dramatically boosting bipolar performance [15]–[30]. Fig. 2 shows the tradeoff between  $f_T$  and the collector-emitter breakdown voltage (BVceo) of Si BJTs and SiGe heterojunction bipolar transistor (HBTs). The  $f_T$  with SiGe technology is two and half times that with Si BJT technology at the same BVceo. An  $f_T$  of over 240 GHz and an ECL gate delay time of less than 3 ps/gate were recently achieved with SiGe technology [23].

The enhancement of the CMOS technology used in the BiCMOS process in the  $0.18 \,\mu\text{m}$  and  $0.13 \,\mu\text{m}$  generations led to the quick development of various processes for combining different SiGe HBTs and different CMOS devices to meet various demands in different marketplaces. Device

181

2168-6734 © 2013 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information

2.0 µm generation

Fig. 1. SEM cross-sections of Si BJTs from  $2.0\,\mu\text{m}$  to  $0.25\,\mu\text{m}$  generation [13]; description of main technology innovation of each generation. Samples were slightly wet-etched using diluted fluonitric acid to emphasize highly doped areas.

Fig. 2. Tradeoff between  $f_{\rm T}$  and BVceo of SiGe HBTs and Si BJTs; both types were fabricated on Hitachi's 8 inch line. SiGe HBT performance is for  $0.13 \,\mu$ m/0.18  $\mu$ m/0.25  $\mu$ m generations; Si BJT performance is for  $0.35 \,\mu$ m/0.25  $\mu$ m generations.

characteristics have tended to be optimized for specific market applications because each application has a different priority for the tradeoff between the  $f_{\rm T}$  and BVceo of the SiGe HBTs. Moreover, the MOSFET supply voltage depends on the application. The combination of different kinds of MOSFETs and BJTs thus resulted in a great number of different BiCMOS technologies. Each one incurs its own development costs, including those for tuning the process conditions to match the device parameters, for confirming the reliability of new devices, and for preparing new design kits. A design kit consists of a set of compact models for both active and passive devices as well as interconnects, design checking rules that support circuit simulation and layout design, and intellectual property like a CMOS standard logic cell library.

This paper presents Hitachi's SiGe BiCMOS technology, which integrates 0.18  $\mu$ m CMOS and 200 GHz SiGe HBTs, and explains why the changes in CMOS characteristics and layout rules must be minimized when implementing the original CMOS technology into the BiCMOS process. Section II explains the concept of constructing a flexible 0.18  $\mu$ m BiCMOS technology suitable for various applications. Compatibility with a standard logic library was emphasized in previous papers [18], [23], [30], but a detailed description was not provided. A low thermal budget process, which does not affect MOS characteristics, may affect transistor yield. Section III describes the low thermal budget process used for forming SiGe HBTs so that changes in the CMOS characteristics are minimized and side effects are avoided. Section IV concludes with a summary of the key points.

# II. BASIC CONCEPT OF CONSTRUCTING BICMOS PROCESS

The basic concept of constructing Hitachi's BiCMOS process is to avoid disturbing the MOS process and to avoid degrading MOS and bipolar performance. Hitachi developed a 40 Gbps optical communication integrated circuit using a  $0.25\,\mu m$  SiGe bipolar process [31]. The same device performance as for a SiGe HBT made using the  $0.25 \,\mu m$  process was achieved using  $0.18 \,\mu m$  SiGe BiCMOS technology, which features CMOS circuits that handle signal speeds of up to 2.7 Gbps and ECL circuits on the same chip that handle 43 Gbps signals for use in optical communication systems. The drain currents of the NMOS and PMOS were 660 and 295  $\mu$ A/ $\mu$ m, respectively. The high drain currents were achieved by inserting the P gate doping step before low thermal budget process of SiGe HBT formation. This process differs from other BiCMOS processes [15], [17], [18], [23]–[30], [35] as described in detail in Section III. A reported SiGe HBT has an  $f_{\rm T}$  of 140 GHz, a maximum oscillation frequency (f<sub>MAX</sub>) of 183 GHz, and a BVceo of 1.9 V [19], [21]. The application of carbon doping of 0.1 % in the intrinsic base region increased the  $f_{\rm T}$  of the SiGe HBT to 211 GHz and the  $f_{MAX}$  to 204 GHz with 1.5 V BVceo, making it suitable to applications requiring even higher speed. The parasitic collector-base capacitance was 2.0 fF for an emitter size of  $0.2 \,\mu m \times 1.0 \,\mu m.$

The three keys to implementing this concept are to optimize the order of the processing steps from the viewpoint of the thermal budget, to perform global planarization, and to avoid disturbing the optimized process module to reduce the length of the process.

#### A. Optimize Order of Thermal Processing Steps

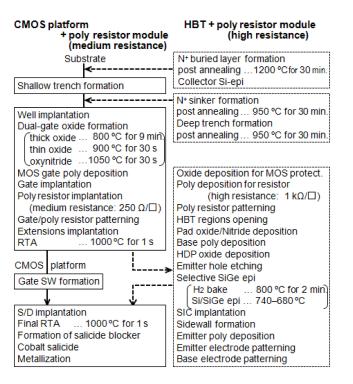

In the 0.18  $\mu$ m SiGe BiCMOS process sequence (Fig. 3), the bipolar fabrication blocks were added to the most appropriate places in the base CMOS process [19]. The heavy thermal processing steps for fabricating an n<sup>+</sup> buried layer (NBL), a collector Si epitaxial growth layer, a collector plug to n<sup>+</sup> buried

Fig. 3. Sequence of  $0.18 \,\mu\text{m}$  SiGe BiCMOS process. Formation of passive components of sinker/metal-insulator-metal capacitors and Schottky barrier/varactor diodes explanation is omitted.

collector, and a deep trench are performed prior to the MOS process block.

A 30 nm thick pad oxide is formed at 1000 °C before deposition of high-density plasma (HDP) oxide for the shallow trenches, and a 4 nm thick pad oxide is formed at 750 °C before filling the deep trenches with high-temperature low-pressure oxide (HTO) at 800 °C. Both deposited oxide layers are densified at 950 °C for 30 minutes. Another 950 °C annealing immediately after implantation of phosphorus  $(5 \times 10^{15} \text{ cm}^{-2})$ at an acceleration energy of 80 keV into the n<sup>+</sup> sinker region of the HBT is needed to recrystallize the damaged region because small defects due to the implantation might magnify the problem during a subsequent lower temperature deposition process step. A low-temperature process instead of the heavy thermal process cannot prevent the n<sup>+</sup> sinker layer and deep trench from possibly inducing crystal defects. The kind of material placed in the deep trench could also increase the possibility of defect occurrence. If polysilicon is used as the trench filling material [32], stress due to cap oxidation can cause crystal defects and/or changes in the BJT characteristics [9], [33]. The combination of low-stress oxide deposition and post annealing prevents this problem.

Dual gate oxide layers with thicknesses of 3.5 nm and 6.5 nm are fabricated for 1.8 V MOSFETs and 3.3 V MOSFETs, respectively. The oxynitride processing step (1050 °C for 30 s) is the step in the MOS formation block with the highest thermal budget. Deposition of a non-doped polysilicon layer is followed by N/P impurity MOS gate implantation, medium- resistance polysilicon resistor implantation, and dry etch patterning. A processing step using rapid thermal annealing (RTA) at over 1000 °C is carried out immediately

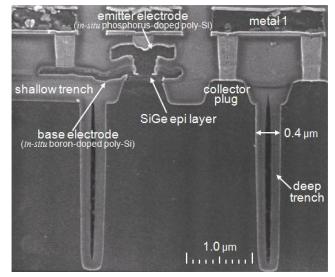

Fig. 4. SEM cross-sectional view of  $0.18\,\mu\text{m}$  based SiGe HBT. Cross-section of sample was slightly wet-etched using diluted HF.

after extension implantation to reduce the transient enhanced diffusion (TED) of impurities implanted in the extension and halo regions. The TED effect is usually observed in relatively low-temperature furnace annealing processes, and immediate RTA after implantation has been used to suppress the short channel effects in CMOS devices from the 0.18  $\mu$ m generation [34]. The gate sidewall (SW) formation processing step includes thermal deposition of an oxide layer at a relatively low temperature.

Several SiGe HBTs have been developed using a combination of blanket SiGe epitaxial growth to form the intrinsic base region and selective boron-doped Si epitaxial growth to form the elevated extrinsic base layer [23], [30], [35]. The intrinsic base region of Hitachi's SiGe HBT is formed using selective SiGe epitaxial growth inside an emitter hole (Fig. 4, [20]). This process, which forms an emitter-base spacer as a self-aligned structure [29], enables formation of a fine emitter region that is beyond the ability of lithography technology. The processing steps start after deposition of an oxide layer on the MOS gates and a medium-resistance resistor. They include depositing in-situ boron-doped polysilicon and oxide layers, opening a bipolar hole where the SiGe epitaxial base will be grown, selectively growing the SiGe epitaxial base, depositing a series of dielectric and *in-situ* phosphorus-doped polysilicon layers, etching back the doped polysilicon to form a SW to separate the emitter and base electrodes, depositing an n<sup>+</sup> emitter polysilicon layer, and patterning emitter and base polysilicon electrodes. Final high-temperature (1000 °C) spike annealing is used to activate the impurities and form emitter regions in the HBT by diffusing phosphorus from the in-situ doped polysilicon into the Si layer selectively grown on the SiGe epitaxial base. Because the low thermal budgets throughout the HBT formation process are not sufficient to drive the boron impurities in non-doped polysilicon, the previous combination of non-doped polysilicon deposition and boron implantation was replaced by boron in-situ polysilicon deposition for the base electrode.

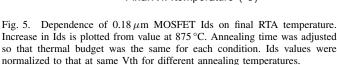

The source/drain current (Ids) of MOSFETs fabricated with different final RTA temperatures normalized to that at the same Vth are plotted in Fig. 5. High-temperature annealing reduced the parasitic resistance and improved the current drivability of the MOSFETs. However, the final RTA needs to be performed quickly at high temperature to prevent excess phosphorus diffusion from the highly doped emitter poly-Si electrode. The cobalt self-aligned silicidation and metallization process steps are carried out, and the electrodes of a SiGe HBT with a high  $f_T$  of 200 GHz are connected by metallization [22].

#### B. Perform Global Planarization

Both the shallow and deep trenches should be planarized to enable fine MOS gates to be patterned on them even though the deep trenches are not used for separating MOSFETs. Because filling a deep trench is more difficult than filling a shallow one, the shallow and  $0.4 \,\mu m$  wide deep trenches are formed separately in our SiGe BiCMOS process, as shown in Fig. 3.

Undoped silicate glass (USG) and HDP chemical vapor deposition (CVD) oxide have been widely used for filling shallow (0.35  $\mu$ m deep) trenches. The USG process, which uses low-temperature and sub-atmospheric (600 Torr) conditions for mixing organic raw materials and ozone, results in good coverage for shallow high-aspect trenches but cannot fill a deep (2.5  $\mu$ m) trench due to a short mean free path in the gas phase. The HDP CVD oxide process, which achieves good coverage by preventing clogging during Ar sputtering, creates reactive molecules with a short mean free path in the gas phase under low-temperature and relatively high-pressure (5 Torr) conditions, so it also cannot fill a deep trench. An HTO CVD process can fill a deep trench due to the long mean free path of the molecules in the gas phase, but its low coverage performance due to the short mean free path at the surface produces a weak adherence of the HTO layer at joints. This problem is overcome by depositing the HTO into the deep trenches twice by etching after the first deposition, resulting in joints that are not exposed on the device surface [12]. Fig. 4 shows a well-planarized deep trench structure underneath a base polysilicon electrode.

The use of a 1.0  $\mu$ m wide trench with an air gap was reported to result in a record peripheral substrate capacitance of 0.02 fF/ $\mu$ m [35]. While a wider trench can suppress parasitic substrate capacitance, thicker oxide deposition is needed to fill a wider deep trench. A total deposition thickness of 1.0  $\mu$ m was used to achieve a well-planarized surface on the 0.4  $\mu$ m wide deep trenches (Fig. 4). Even though chemical mechanical polishing (CMP) was used to planarize the deep trenches, thickness fluctuation of the HTO layer on a wafer affects the planarization. We thus limited the deep trench width to 0.4  $\mu$ m.

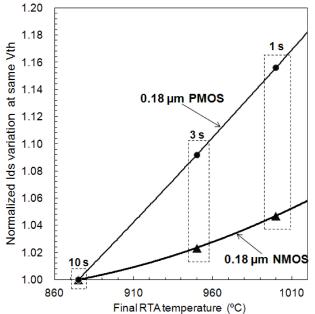

The height of Hitachi's first SiGe HBT was  $0.8 \,\mu\text{m}$  [31]. It was subsequently reduced to  $0.6 \,\mu\text{m}$  to enable integration of the 0.25  $\mu\text{m}$  SiGe BiCMOS process without causing problems during inter-metal dielectric layer (IML) formation because the IML thickness is determined by the CMOS process technology. The height of the 0.18  $\mu\text{m}$  based SiGe HBT was reduced to 0.48  $\mu\text{m}$  to enable application to both 0.18  $\mu\text{m}$  and 0.15  $\mu\text{m}$  CMOS [19], [20].

Fig. 6 compares the height of the  $0.18 \,\mu$ m based SiGe HBT and the IML thickness of  $0.18 \,\mu$ m to  $0.13 \,\mu$ m MOSFETs. The IML thickness is usually determined by the contact hole size, i.e., the need to keep the aspect ratio of the hole to around three. Although a self-aligned HBT using double poly-Si layers tends to be taller than the MOS gate, the height of the SiGe HBT must be reduced in accordance with the thickness of the IML. The height of the SiGe HBT can be reduced without degrading its performance when it is applied to  $0.13 \,\mu$ m CMOS by using a thinner emitter and thinner base polysilicon layers [29]. An advanced BiCMOS could be integrated without reducing the IML thickness and contact hole size by reducing the gate length and optimizing the impurity profile of the MOSFET, but this would require much effort to redesign the standard CMOS circuit.

### C. Keep Scheme of Optimized Process Module

Combining the CMOS process and bipolar process increases the number of processing steps, so techniques for reducing the number have been proposed. For instance, the N-well of the PMOS could use the NBL of the BJTs. Since the sheet resistance of the NBL in which Sb ions ( $2 \times 10^{15}$  cm<sup>-3</sup>) are implanted is  $38 \Omega/\Box$ , which is one-tenth that of the N-well in conventional PMOS, the PMOS N-well could be formed in the same layer as the NBL. However, this would reduce the flexibility needed to support a wide variety of applications.

Device characteristics are optimized by changing the Si epitaxial thickness and selective collector implantation (SIC) doping level in accordance with the tradeoff between  $f_{\rm T}$  and BVceo (Fig. 2). If the PMOS N-well uses the NBL of the BJTs, the Si epitaxial thickness depends on the PMOS characteristics, and the flexibility of the BJT process is limited. The thickness of the Si epitaxial layer used for high-frequency

Fig. 6. Schematic cross-section and standard values for  $0.18 \,\mu\text{m}$  SiGe HBT and  $0.18 \,\mu\text{m}$  to  $0.13 \,\mu\text{m}$  MOSFETs (all measurements in  $\mu\text{m}$ ).

applications is less than  $0.3 \,\mu$ m, and that for high-voltage applications could be more than  $1.5 \,\mu$ m. SIC doping does not cover all areas from high frequency like 200 GHz to high voltage.

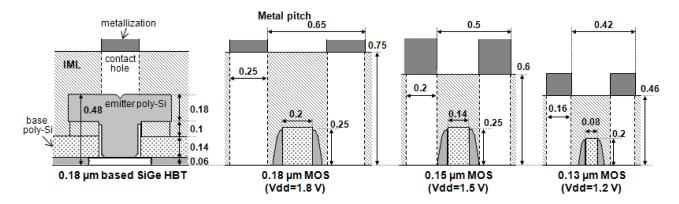

Another approach is to use the same polysilicon layer for a poly resistor and a MOS gate. However, doped NMOS and PMOS gates are not suitable as precise poly resistors for analog applications. The sheet resistance should have a small temperature coefficient of resistance (TCR), and the process conditions for the N and P gates should be independent of the TCR. A small TCR can be obtained during the formation of a polysilicon resistor through layer-by-layer polysilicon formation [16]. The polysilicon initially has small grains following deposition, and impurity implantation results in the formation of an amorphous layer on the upper layer of the polysilicon. This layer turns into large-grain polysilicon due to recrystallization after annealing.

The TCR for large-grain polysilicon is positive while that for small-grain polysilicon is negative due to the electrical characteristics of the grain boundary. The positive TCR reflects resistivity inside the grains, and the negative TCR reflects the barrier resistance of the grain boundary [36]. These opposite characteristics cancel out the temperature dependency of the resistivity. Implantation of BF<sub>2</sub> or Ge is used to form an exact layer-to-layer structure. Low-temperature implantation using fluorinate at -40 °C as a refrigerant can be used to suppress the formation of microcrystallines in the implanted amorphous layer.

The acceleration energy of the Ge implantation can change the TCR, as shown in Fig. 7. The TCR fluctuation was of the order of 100 ppm/°C, and a slightly negative TCR helps prevent thermal runaway of the circuit function. However, the process conditions for achieving a small-TCR 1 k $\Omega/\Box$ resistor are not suitable for achieving 250 nm thick poly-Si. It is difficult to achieve a small TCR from low resistance to high resistance with the same polysilicon thickness. A higher Ge acceleration energy can be used to increase the relative amount of bigger grain sizes inside a polysilicon resistor. The thickness of the MOS gate with the 0.18  $\mu$ m SiGe BiCMOS process is 0.25  $\mu$ m, which is suitable for achieving 250  $\Omega/\Box$ . In this case, 0.25  $\mu$ m is too thick to achieve 1 k $\Omega/\Box$  with a small TCR. Thinner poly-Si is needed to achieve a small TCR and high-resistance resistor.

Fig. 7. Relationship between TCR and sheet resistance of high-resistance poly-Si resistor with implanted Ge  $(5 \times 10^{14} \text{ cm}^{-2})$ .

Commonization is used to disturb the optimized process module and change the characteristics. The divide-intodependent-blocks process flow must therefore be retained to realize maximum device performance.

# III. LOW THERMAL BUDGET PROCESS FOR FORMING HBTS

The BJT formation process is inserted into the CMOS process as a module, and there are various ways to insert the BJT module. Impurity diffusion from heavily doped source/drain (S/D) regions during BJT block processing was adjustable until the 0.25  $\mu$ m generation. Expanding the MOSFET SW length and adjusting the impurity profile of the halo regions suppress the short channel effects, so the SiGe HBT module can be integrated into the base CMOS process after MOS formation [9], [12], [16]. However, things became more difficult from the 0.18  $\mu$ m generation. First, the tight metal pitch does not allow expansion of the SW length, as shown in Fig. 6. Second, boron diffusion from the heavily boron-doped area of the PMOS is especially problematic compared to the arsenic or phosphorus diffusion from an NMOSFET, and the heavily

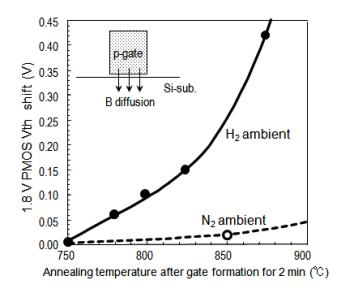

Fig. 8. PMOS Vth shift due to  $H_2$  bake prior to SiGe epitaxial growth. Gate oxide thickness was 3.5 nm for 0.18  $\mu$ m CMOS. Gate length of PMOS was set to 2  $\mu$ m to evaluate degree of boron penetration.

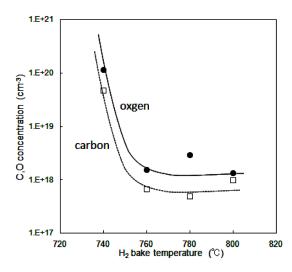

Fig. 9. SIMS-measured C and O concentrations on surface between SiGe epitaxial growth layer and Si substrate.

doped p-type S/D regions extended by the thermal budget of the bipolar process increase the short channel effect. The doping levels for the extensions and halo regions are lower than that for the S/D regions, so the effect of the SiGe HBT module on the extension regions is small. To avoid this second problem, the SiGe HBT formation module was inserted after patterning of the MOS gate and before S/D implantation, starting with the 0.18  $\mu$ m generation, as shown in Fig. 3 [19], [20], [22].

The thermal budget for SiGe HBT formation is mainly used for H<sub>2</sub> bake prior to SiGe epitaxial growth. From the viewpoint of MOS device characteristics, the H<sub>2</sub> bake temperature must be below 800 °C to suppress threshold voltage (V<sub>TH</sub>) shift due to the H<sub>2</sub> bake. Hydrogen atoms during annealing promote boron diffusion throughout the gate oxide layer and enhance the V<sub>TH</sub> shifting of the P-gate PMOS much more than N<sub>2</sub> annealing, as shown in Fig. 8. The N-gate PMOS, commonly used until the 0.25  $\mu$ m generation,

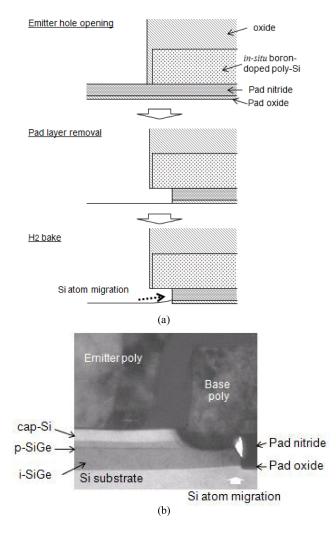

Fig. 10. Si/SiGe epitaxial growth in base contact cavity. (a) Cross-section of epitaxial growth layers; (b) TEM cross-sectional view of base region of SiGe HBT. H<sub>2</sub> bake temperature prior to epitaxial growth was 875 °C.

is not affected by this problem. In contrast, the P-gate PMOS, commonly used from the 0.18  $\mu$ m generation, is affected by boron penetration through the gate oxide during the H<sub>2</sub> bake. This problem can be avoided by placing the BJT fabrication process after source/drain/gate (S/D/G) NMOS implantation and before S/D/G PMOS implantation [15]. Because impurities are spontaneously implanted into the MOS gate and S/D regions, there is no boron inside the P-gate during the H<sub>2</sub> bake. However, a final spike annealing at 1000 °C alone could be insufficient to make the boron diffuse in the P-gate poly-Si in the case of spontaneous S/D/G implantation. This would induce the formation of a thick depletion layer in the P-gate and thereby degrade PMOS performance.

An intrinsic base region is selectively formed at an open emitter hole using a conventional single-wafer LP-CVD technique [19], [20], [22]. An H2 bake is used to eliminate surface contamination (C, O, etc.) prior to SiGe epitaxial growth. For conventional blanket Si epitaxial growth for a collector region, a 10-minute H2 bake at 1040 °C is used for surface cleaning. This condition is not appropriate for intrinsic base regions. An 800 °C H<sub>2</sub> bake is sufficient to

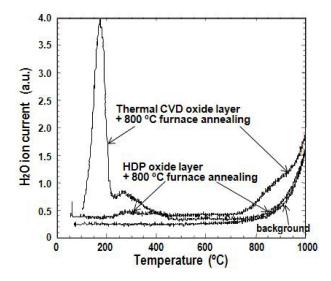

Fig. 11. Thermal desorption spectrum of thermally stimulated moisture from oxide layers.

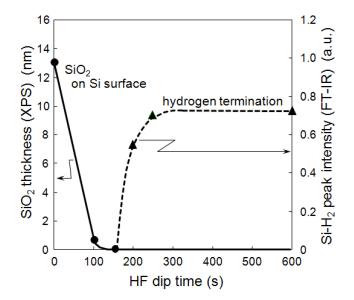

remove the natural oxide layer. Fig. 9 shows the measured C and O concentrations after the  $H_2$  bake and Si/SiGe epitaxial growth. The concentrations were measured on a bare Si wafer by secondary ion mass spectrometry (SIMS). A 760 °C  $H_2$  bake was sufficient to remove the C and O from the Si surface. Hydrogen termination, which forms during wet etching in HF dip, prevents natural oxide growth on a Si surface [37].

After an emitter hole is opened on the pad SiN layer, the SiN layer and pad SiO<sub>2</sub> layer are removed by wet etching, as shown in Fig. 10(a). A TEM cross-sectional view of the base region (Fig. 10(b)) shows that the Si migrated during H<sub>2</sub> bake at 875 °C. This indicates that the thin natural oxide is removed by baking at 875 °C. Even at 800 °C, slight Si migration was observed, and a clean Si surface was obtained.

Two things must be done in order to finish epitaxial growth with a low-temperature H<sub>2</sub> bake. One is suppressing the effect of the wafer. Fig. 11 shows the measured moisture emission from the oxide layers. A thermal CVD oxide layer, which was deposited at 680 °C, tended to absorb moisture in the atmospheric environment and to desorb a great deal at 170 °C, resulting in the formation of a thin thermal oxide layer. An 800 °C H<sub>2</sub> bake was not sufficient to remove this layer. Since the quality of HDP oxide is close to that of thermal oxide, a slight amount of moisture emission from the HDP layer was observed, as shown in Fig. 11.

The second thing that needs to be done is optimizing the HF dip time. Formation of hydrogen termination on a silicon surface takes time after removal of the surface pad oxide, as shown in Fig. 12. A 300 s HF dipping process creates hydrogen termination with Si bonds on the Si surface, which prevents the formation of natural oxide. In addition, a pad oxide layer is formed by USG oxide under low-pressure conditions, resulting in quality close to that of thermal oxide. Low thermal budget BJT fabrication using these techniques achieves a high bipolar transistor yield (99.99993 %) and maintains  $0.13 \,\mu$ m and  $0.18 \,\mu$ m CMOS performance with little process condition tuning [19], [20], [22].

Fig. 12. Oxide layer thickness and H termination dependencies on HF dip time. Thickness of thin oxide layer was measured by x-ray photoelectron spectroscopy (XPS); amount of H termination was measured by Fourier transform infrared spectroscopy (FT-IR). Si-H<sub>2</sub> intensity was measured because two dangling bonds are on Si(100) surface.

Fig. 13. Comparison of thermal budgets needed to form Si BJT described elsewhere [13] and SiGe HBT.

An intrinsic base region for a 40 GHz  $f_T$  Si BJT was formed by N<sub>2</sub> annealing at 950 °C for 1 minute and wet oxidation (pyrogenic) at 800 °C for 5 minutes [13]. The N<sub>2</sub> annealing recrystallized the damaged Si surface immediately after BF<sub>2</sub> low-acceleration implantation, and the segregation by wet oxidation fixed the surface boron profile, which reduced the emitter-base leakage current. It may be possible to reduce the annealing time to recrystallize, but the oxidation time cannot be reduced because lengthy oxidation is needed to suppress the peak boron concentration at the Si surface. The process temperature during the intrinsic SiGe epitaxial growth for 10 minutes is 670 °C, and that during cap-Si growth for 2 minutes is 740 °C. The heavy Ge concentration enhances the SiGe growth rate, so the thermal budget for the SiGe growth step is lower than that for the 800 °C H<sub>2</sub> bake.

The other thermal processes in the SiGe HBT process were adjusted to reduce the thermal budget, as shown in Fig. 13. The thermal budget for the SiGe process is lower than that for the conventional intrinsic base formation. A double-digit difference in the impurity diffusion coefficients at 800 °C and 700 °C is equivalent to a single-digit difference in the diffusion time at both temperatures [38]. However, a furnace process usually takes hours, so using the HDP process instead of the thermal CVD oxide process effectively reduces the total thermal budget during HBT formation. Since the SiGe HBT technology is more flexible than the Si BJT technology for adjusting the CMOS process, the SiGe HBT technology must be used instead of the Si BJT technology to integrate advanced CMOS. Low-thermal-budget SiGe HBT process technology has been demonstrated to be applicable from the  $0.18\,\mu m$ generation to the 90 nm and 0.13  $\mu$ m generations [19], [20], [22].

#### **IV. CONCLUSION**

Use of a divide-into-dependent-blocks process flow and a low-thermal-budget bipolar process enable construction of a flexible  $0.18 \,\mu\text{m}$  BiCMOS technology that can be applied without major change to CMOS process conditions. A minimal-moisture-desorption oxide process is used to reduce the H<sub>2</sub> bake temperature to 800 °C, resulting in a bipolar transistor yield of 99.99993 %. The height of a bipolar device was reduced to enable application to both  $0.18 \,\mu\text{m}$  and  $0.15 \,\mu\text{m}$  CMOS technologies. Full optimization throughout the series of BiCMOS technologies is needed to reduce the total cost of device development, reliability testing, and PDK preparation. The proposed technology can also be applied to the 0.13  $\mu$ m generation.

#### REFERENCES

- M. A. Polinsky, O. Schade, Jr., and J. P. Keller, "CMOS-Bipolar monolithic integrated-circuit technology," in *Proc. IEEE IEDM*, 1973, pp. 229–231.

- [2] H. Higuchi, G. Kitsukawa, T. Ikeda, Y. Nishio, N. Sasaki, and K. Ogiue, "Performance and structures of scaled-down bipolar devices merged with CMOSFETS," in *Proc. IEEE IEDM*, 1984, pp. 694–697.

- [3] T. Ikeda, A. Watanabe, Y. Nishio, I. Masuda, N. Tamba, M. Odaka, et al., "High-Speed BiCMOS technology with a buried twin well Structure," *IEEE Trans. Electron. Devices*, vol. 34, no. 6, pp. 1304–1310, Jun. 1987.

- [4] H. Momose, H. Shibata, S. Saitoh, J. Miyamoto, K. Kanzaki, and S. Kohyama, "1.0-μm n-Well CMOS/Bipolar Technology," *IEEE Trans. Electron. Devices*, vol. 32, no. 2, pp. 217–223, Feb. 1985.

- [5] A. Watanabe, T. Ikeda, T. Nagano, N. Momma, Y. Nishio, N. Tamba, et al., "High speed BiCMOS VLSI technology with buried twin well structure," in Proc. IEEE IEDM, 1985, pp. 423–426.

- [6] A. R. Alvarez, "Future trends in BiCMOS technology," in Proc. ESS-DERC, 1991, pp. 493–500.

- [7] A. Watanabe, T. Nagano, S. Shukuri, and T. Ikeda, "Future BiCMOS technology for scaled supply voltage," in *Proc. IEEE IEDM*, 1985, pp. 429–432.

- [8] T. Nakamura and H. Nishizawa, "Recent progress in bipolar transistor technology," *IEEE Trans. Electron. Devices*, vol. 42, no. 3, pp. 390–398, Mar. 1995.

- [9] T. Hiramoto, T. Tamba, M. Yoshida, T. Hashimoto, T. Fujiwara, K. Watanabe, *et al.*, "A 27 GHz double poly-silicon bipolar technology on bonded SOI with embedded 58 μm<sup>2</sup> CMOS memory cells for ECL-CMOS SRAM applications," in *Proc. IEEE IEDM*, 1992, pp. 39–42.

- [10] K. Higeta, M. Usami, M. Ohayashi, Y. Fujimura, M. Nishiyama, S. Isomura, et al., "A Soft-Immune 0.9 ns 1.15 Mb ECL-CMOS SRAM with 30-ps 120K logic gates and on-chip test circuitry," *IEEE J. Solid-State Circuits*, vol. 31, no. 10, pp. 1443–1450, Oct. 1996.

- [11] T. Yamaguchi, S. Uppili, J. S. Lee, G. H. Kawamoto, T. Dousluoglu, and S. Simpkins, "Process and device characterization for a 30 GHz f<sub>T</sub> submicrometer double poly-Si bipolar technology using BF<sub>2</sub>-implanted base with rapid thermal process," *IEEE Trans. Electron. Devices*, vol. 40, no. 8, pp. 1484–1495, Aug. 1993.

- [12] T. Kikuchi, Y. Onishi, T. Hashimoto, E. Yoshida, H. Yamaguchi, S. Wada, *et al.*, "A 0.35 μm ECL-CMOS process technology on SOI for 1 ns Mega-bits SRAM's with 40 ps gate array," in *Proc. IEEE IEDM*, 1995, pp. 923–926.

- [13] T. Hashimoto, T. Kikuchi, K. Watanabe, N. Ohashi, T. Saito, H. Yamaguchi, *et al.*, "A 0.2-μm Bipolar-CMOS technology on bonded SOI with copper metallization for ultra high-speed processors," in *Proc. IEEE IEDM*, 1998, pp. 209–212.

- [14] S. V. Kishore, G. Chang, and C. Hull, "A SOI-BiCMOS RF-Transmitter for personal digital cellular communication (PDC)," in *Proc. IEEE Symp. VLSI Circuits*, 2000, pp. 62–65.

- [15] D. L. Harame, D. C. Ahlgren, D. D. Coolbaugh, J. S. Dunn, G. G. Freeman, J. D. Gillis, *et al.*, "Current status and future trends of SiGe BiCMOS technology," *IEEE Trans. Electron. Devices*, vol. 48, no. 11, pp. 2575–2594, Nov. 2001.

- [16] K. Washio, E. Ohue, H. Shimamoto, K. Oda, R. Hayami, Y. Kiyota, et al., "A 0.2 μm 180 GHz-f<sub>MAX</sub> 6.7-ps-ECL SOI/HRS self-aligned SEG SiGe HBT/CMOS Technology for microwave and high-speed digital applications," *IEEE Trans. Electron. Devices*, vol. 49, no. 2, pp. 271–278, Feb. 2002.

- [17] D. Knoll, B. Heinemann, K. E. Ehwald, A. Fox, H. Rücker, R. Barth, et al., "A low-cost, high-performance, high-voltage complementary BiCMOS process," in *Proc. IEEE IEDM*, 2006, pp. 1–4.

- [18] A. Joseph, D. Coolbaugh, M. Zierak, R. Wuthrich, P. Geiss, Z. He, et al., "A 0.18 μm BiCMOS technology featuring 120/100 GHz (f<sub>T</sub>/f<sub>MAX</sub>) HBT ASIC-Compatible CMOS using copper interconnect," in Proc. IEEE BCTM, 2001, pp. 143–146.

- [19] S. Wada, Y. Nonaka, T. Saito, T. Tominari, K. Koyu, K. Ikeda, et al., "A manufacturable 0.18 μm SiGe BiCMOS technology for 40 Gb/s optical communication LSIs," in *Proc. IEEE BCTM*, 2002, pp. 84–87.

- [20] T. Hashimoto, Y. Nonaka, T. Saito, K. Sasahara, T. Tominari, K. Sakai, et al., "Integration of a 0.13-μm CMOS and a high performance selfaligned SiGe HBT featuring low base resistance," in *Proc. IEEE IEDM*, 2002, pp. 779–782.

- [21] A. Koyama, T. Harada, H. Yamashita, R. Takeyari, N. Shiramizu, K. Ishikawa, *et al.*, "43 Gb/s full-rate-clock 16:1 multi-plexer and 1:16 demultiplexer with SFI-5 interface in SiGe BiCMOS technology," in *Proc. IEEE ISSCC*, 2003, pp. 232–235.

- [22] T. Hashimoto, Y. Nonaka, T. Tominari, H. Fujiwara, K. Tokunaga, M. Arai, *et al.*, "Direction to improve SiGe BiCMOS technology featuring 200 GHz SiGe HBT and 80 nm gate CMOS," in *Proc. IEEE IEDM*, 2003, pp. 129–132.

- [23] H. Rücker, B. Heinemann, W. Winkler, R. Barth, J. Borngräber, J. Drews, *et al.*, "A 0.13 μm SiGe BiCMOS Technology featuring *f*<sub>T</sub>/*f*<sub>MAX</sub> of 240/330 GHz and gate delays below 3 ps," *IEEE J. Solid-State Circuits*, vol. 45, no. 9, pp. 1678–1681, Sep. 2010.

- [24] J. Dunn, D. L. Harame, A. J. Joseph, S. A. St. Onge, N. B. Feilchenfeld, L. Lanzerotti, *et al.*, "SiGe BiCMOS trends-today and tomorrow," in *Proc. IEEE CICC*, 2006, pp. 695–702.

- [25] M. Racanelli and P. Kempf, "SiGe BiCMOS technology for RF circuit applications," *IEEE Trans. Electron Devices*, vol. 52, no. 7, pp. 1259–1270, Jul. 2005.

- [26] H. Rücker and B. Heinemann, "SiGe BiCMOS technology for mm-wave systems," in *Proc. IEEE ISOCC*, 2012, pp. 266–268.

- [27] A. J. Joseph, D. L. Harame, B. Jagannathan, D. Coolbaugh, D. Ahlgren, J. Magerlein, *et al.*, "Status and direction of communication technologies—SiGe BiCMOS and RFCMOS," *Proc. IEEE*, vol. 93, no. 9, pp. 1539–1558, Sep. 2005.

- [28] H. Rücker, B. Heinemann, and A. Fox, "Half-Terahertz SiGe BiCMOS Technology," in *Proc. IEEE SiRF*, 2012, pp. 133–136.

- [29] G. Avenier, M. Diop, P. Chevalier, G. Troillard, N. Loubet, J. Bouvier, et al., "0.13 μm SiGe BiCMOS technology fully dedicated to mm-Wave applications," *IEEE J. Solid-State Circuits*, vol. 44, no. 9, pp. 2312–2321, Sep. 2009.

- [30] B. A. Orner, M. Dahlstrom, A. Pothiawala, R. M. Rassel, Q. Liu, H. Ding, et al., "A BiCMOS technology featuring a 300/330 GHz (fT/fmax) SiGe HBT for millimeter wave applications," in Proc. IEEE BCTM, 2006, pp. 1-4.

- [31] T. Masuda, K. Ohhata, N. Shiramizu, E. Ohue, K. Oda, R. Hayami, et al., "40 Gb/s 4:1 multiplexer and 1:4 demultiplexer IC module," in Proc. IEEE MTT-S Int. Microw. Symp., 2001, vol. 3, pp. 1697-1700.

- [32] Y. C. Simon Yu, C. A. Hacherl, E. E. Patton, E. L. Lane, T. Yamaguchi, and S. S. Dottara, "Planarized deep-trench process for self-aligned double polysilicon bipolar device isolation," J. Electrochem. Soc., vol. 137, no. 6, pp. 1942-1950, Jun. 1990.

- [33] M. Yoshida, T. Hiramoto, T. Fujiwara, T. Hashimoto, T. Muraya, S. Murata, et al., "Bipolar-based 0.5  $\mu$ m BiCMOS technology on bonded SOI for high-speed LSIs," IEICE Trans. Electron., vol. 77, no. 8, pp. 1395-1403, Aug. 1994.

- [34] A. Shimizu, N. Ohki, H. Ishida, T. Yamanaka, K. Kikushima, K. Okuyama, et al., "Impact of high-temperature rapid thermal annealing in deep-submicrometer CMOSFET design," IEICE Trans. Electron., vol. 79-C2, no. 6, pp. 252-259, 1996.

- [35] S. Van Huylenbroeck, L. J. Choi, A. Sibaja-Hernandez, A. Piontek, D. Linten, M. Dehan, et al., "A 205/275 GHz fT/fmax Airgap Isolated 0.13 m BiCMOS Technology featuring on-chip high quality passives," in Proc. IEEE BCTM, 2006, pp. 1-4.

- [36] I. Ashuah, E. N. Shauly, and Y. Shacham-Diamand, "Improvement of temperature coefficient of resistance by co-implantation of argon or xenon or fluorine in boron implanted polysilicon resistors," IEEE Trans. Semicond. Manuf., vol. 22, no. 2, pp. 305-316, May 2009.

- [37] D. B. Fenner, D. K. Biegelsen, and R. D. Bringans, "Silicon surface passivation by hydrogen termination: A comparative study of preparation methods," J. Appl. Phys., vol. 66, no. 1, pp. 419-424, Jul. 1989.

- [38] S. M. Sze, Physics of Semiconductor Devices, 2nd ed. New York, NY, USA: Wiley, 1981.

Takashi Hashimoto (M'98) received the B.S. and M.S. degrees in electronic engineering from Tohoku University, Miyagi, Japan, in 1986 and 1988, respectively.

He joined Hitachi's Device Development Center in 1988 and worked on the development of bipolar/BiCMOS technologies. He was a visiting Researcher at the Massachusetts Institute of Technology, Cambridge, MA, USA, in 1996. He has since been working on SiGe BiCMOS technologies at Hitachi's Micro Device Division. His current

interests include mid-voltage (BCD) device and CMOS sensor technologies.

Yusuke Nonaka received the B.S. degree in electronic engineering from the University of Electro-Communications, Tokyo, Japan, in 1990, and the M.S. degree in electronics engineering from the Tokyo Institute of Technology, Tokyo, in 1992.

Since he joined Hitachi, Ltd. in 1992, he has worked on the development of various types of devices such as CMOS, SiGe HBT BiCMOS, SONOS non-volatile memory, IGBT, and CMOS image sensors.

Tatsuya Tominari received the B.S. and M.S. degrees in electrical and electronic engineering from Ritsumeikan University, Kyoto, Japan, in 1996 and 1998, respectively. He joined Hitachi's Device Development Center in 1998 and worked on the development of lithographic processes. Since 2001, he has been working on the development of SiGe BiCMOS technologies at Hitachi's Micro Device Division.

Tsuyoshi Fujiwara received the B.S. degree in applied physics from Hokkaido University, Hokkaido, Japan, in 1987.

In 1987, he joined Hitachi's Device Development Center, where he worked on the development of backend processes. He is now a Senior Engineer in Hitachi's Micro Device Division.

Tsutomu Udo received the B.S. and M.S. degrees in

applied physics from Fukuoka University, Fukuoka, Japan, in 1984 and 1988, respectively.

In 1988, he joined Hitachi ULSI Systems Co., Ltd., where he developed low-pressure chemical vapor deposition (LP-CVD) processes including SiGe epitaxial growth. Since 2004, he has been developing LP CVD processes at Sony Semiconductor Corporation in Nagasaki and Kumamoto, Japan.

Hidenori Satoh received the B.S. and M.S. degrees in physics from the Tokyo University of Science in 1993 and Tohoku University in 1995, respectively.

He joined Hitachi Ltd. in 1995 and helped develop a SiO<sub>2</sub>-CVD process for filling shallow and deep trenches. Since 2004, he has been working on the development of a dielectric layer CVD process for DRAMs, ALD technology for flash memory, and a Si/SiGe epitaxial process at Hitachi's Micro Device Division.

Kunihiko Watanabe received the B.S. and M.S. degrees in material engineering from the University of Tokyo, Tokyo, Japan, in 1978 and 1980, respectively. He joined Hitachi's Device Development Center in 1980, where he worked on the development of a bipolar process and was involved in the study of SOI wafer usage. From 1988 to 2012, he was engaged in the development of BiCMOS/CMOS technologies.

Tomoko Jimbo received the B.S. degree in chemistry from Gakushuin University, Tokyo, Japan, in 1986.

She joined Hitachi's Device Development Center in 1990, where she has been engaged in the development of physical analytical techniques for semiconductor materials. Since 2005, she has been researching ways to reduce process contamination in CMOS imagers at Hitachi's Micro Device Division.

Hiromi Shimamoto received the B.E. and Ph.D. degrees in electrical engineering from Nihon University, Tokyo, Japan, in 1982 and 2004 respectively. In 1982, he joined Hitachi Device Engineering Co., Ltd., Chiba, Japan, where he researched Si bipolar/BiCMOS and SiGe HBT device technologies. Since 2008, he has been involved in the development of secure machine control units (MCU). Currently, he is the MCU Design Department Manager at Renesas Design Corporation.

Satoru Isomura received the B.S. and M.S. degrees

Satoru Isomura received the B.S. and M.S. degrees in electronic engineering from Nagoya University in 1981 and 1983, respectively. He joined Hitachi's Device Development Center in 1983, and worked on the development of high-speed LSI circuits for mainframe computers. From 2001 to 2008, he worked on mixed-signal IC designs at Hitachi's Micro Device Division. Recently, as a Senior Director, he was involved in the management of the mixed-signal IC business and manufacturing operation operation.