# Cryogenic Small Dimension Effects and Design-Oriented Scalable Compact Modeling of a 65-nm CMOS Technology

Alberto Gatti , Graduate Student Member, IEEE, and Filip Tavernier, Senior Member, IEEE

Abstract—This paper presents the cryogenic characterization and compact modeling of thin-oxide MOSFETs in a standard 65-nm Si-bulk CMOS technology. The influence of both short and narrow channel effects at extremely low temperature on key device parameters such as threshold voltage and ON current is highlighted, and the performance of this technology node for cryogenic analog circuit design is discussed. It is then demonstrated, for the widest range of gate geometries in literature, that the BSIM4 parameter editing approach can be successfully used to model small dimension effects at cryogenic temperature. In the absence of cryogenic foundry models, the robustness and simplicity of this modeling technique make it a preferred method to quickly build a design-oriented, fully scalable SPICE compact model. This restores complete freedom in device sizing for cryogenic analog circuit design.

Index Terms— Characterization, Circuit simulation, CMOS technology, Cryogenic electronics, Modeling

#### I. INTRODUCTION

Cryogenic CMOS circuits have become increasingly popular in recent years due to their application in quantum computing [1]. Still, they also find use in a much broader spectrum of applications such as gravitational wave detectors [2]-[4], infrared focal plane arrays, positron emission tomography, and quantum technology in general [5]. Modern thin-oxide devices are usually free of the anomalies that plague thickoxide devices [6], [7], [9] and can therefore take full advantage of the benefits offered by the cryogenic environment, such as increased transconductance [9] and reduced leakage [15]. However, existing foundry models for CMOS technologies are still unable to reliably reproduce the behavior of MOSFETs at very low temperatures [8]. This also prevents the validation of the few cryogenic design methodologies proposed in the literature [23]. Despite the efforts of many research groups in characterization and modeling [9]-[22], there is no uniquely recognized approach to extract a cryogenic SPICE compact model for a CMOS technology yet. Moreover, the vast majority of works focuses on modeling very few gate geometries, thus severely limiting the degrees of freedom for analog

Manuscript submitted for review December 10, 2023. This work was supported in part by internal KU Leuven funds (iBOF-21-084) and in part by Interreg V-A Euregio Maas-Rijn under the E-TEST project (EMR113).

Alberto Gatti and Filip Tavernier are with the Department of Electrical Engineering (ESAT), KU Leuven, 3001 Leuven, Belgium (e-mail: alberto.gatti@kuleuven.be).

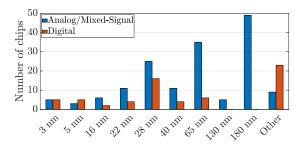

design [24]. An increasingly popular modeling method is to modify model equations by changing the code of the Verilog-A model implementation. This approach has been shown to be sufficiently accurate when scaling the temperature and the size of devices [16], [17]. However, it is prone to errors as for some models (e.g., BSIM4 [25]), there is no official implementation in Verilog-A available. Moreover, the performance of Verilog-A implementations is highly code-dependent [26] and still falls short of SPICE models developed in C and hard-coded in commercial simulators, even when dedicated model compilers are employed [28], [29]. This becomes increasingly problematic as the number of transistors in the circuit increases. To circumvent these limitations, an alternative approach is editing only model parameters, to re-center the model on the target temperature [9], [19]. By retaining the original model code, this method is inherently less error-prone and preserves simulation performance. Furthermore, it allows reusing foundry statistical data for mismatch simulations, albeit to a limited extent [30]. However, to the best of the authors' knowledge, this modeling approach has so far only been applied to a limited number of gate geometries [9], [19]. Therefore, its full scaling capabilities have yet to be demonstrated. In this work, we present the cryogenic performance of a 65-nm Si-bulk CMOS technology and show that the modeling methodology based on BSIM4 parameter editing can be used to obtain a fully scalable cryogenic compact model. Although much of the most recent work in cryogenic device characterization and modeling focuses on nonplanar technologies [17], [18], the 65nm node is still one of the most used for analog and mixed signal chip design, as demonstrated by the statistics from the latest International Solid State Circuits Conference (ISSCC) shown in Fig. 1.

Fig. 1. Number of chips per technology node presented at ISSCC 2024.

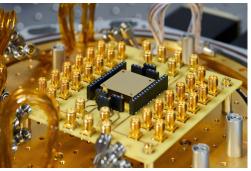

Fig. 2. From left to right: photomicrograph of the test chip; pictures of the sample mounting system employed for the characterization. To ensure the best possible thermal conductivity, the chip is fixed with silver paint on the metal surface of a gold-plated OFHC copper heatsink, placed in direct contact with a cold finger of the same material [32]. Sample temperature is measured with a Cernox® SD thermometer [33] on the chip heatsink.

Fig. 3. Left: gate geometries of the test structures. Devices usually used to characterize short and narrow channel effects are highlighted in red and blue respectively. The green rectangle in the middle encompasses the gate geometries commonly of interest for analog circuit design [24]. Right: the glaring differences in relative increase of the saturation transconductance  $\mathbf{g}_{\mathbf{m},\mathbf{sat}}$  for three different NMOS geometries.

The paper is organized as follows: Section II describes the test structures and the measurement setup; Section III discusses the cryogenic behavior, with a focus on the impact of small dimension effects; Section IV discusses the cryogenic performance of the technology for analog circuit design; Section V presents the modeling procedure and the accuracy of the resulting model; finally, conclusions are drawn in Section VI.

## II. TEST STRUCTURES, SETUP AND MEASUREMENTS

Low-threshold voltage (LVT) MOSFETs ( $t_{\rm ox}\approx 2.7~{\rm nm}$ ) with 25 different gate geometries for both PMOS and NMOS (50 devices in total) were fabricated in a 65-nm Si-bulk CMOS technology. LVT devices were selected because of the known threshold voltage increase at cryogenic temperature [9], [12]. The chosen geometries, shown in the left side of Fig. 3, cover the entire design space available in the foundry PDK. The test transistors are divided into groups that share gate, source, and bulk terminals, while the drain terminals are independent to ensure accurate subthreshold current characterization. The interconnections are designed so that the impact of the overall series resistance on the measurements is negligible. The connections to the pads are made almost entirely of ultra-thick metal ( $R\approx 5 {\rm m}\Omega/\Box$  at room temperature) or thick metal ( $R\approx 25 {\rm m}\Omega/\Box$  at room temperature). These values

are expected to reduce further at cryogenic temperature. The devices are positioned so that those with the largest aspect ratio W/L have the shortest connections to the pads. With these measures, the error on  $V_{\rm DS}$  is always below 0.5%. To ensure that the measurements genuinely represented the process, all test dies were diced from a wafer certified as typical-typical (TT) by the foundry.

The samples were bonded directly to a PCB designed for cryogenic low-current measurements, with guarding [31] down to pad level, and placed in the cryogenic chamber of a Montana Instruments s200 cryostation, modified to extend the guarding along standard coaxial feedthroughs. A custom sample mounting system for in-vacuum cryogenic chip testing, depicted in Fig. 2, was employed to ensure proper thermalization of the samples [32]. The complete test setup achieves a base temperature of 5.7 K. Measurements were conducted with an array of four Keithley 2450 SMUs, connected with triaxial cables and triax-to-coax adapters [31] to the feedthroughs of the cryogenic chamber.

The characterization includes transfer characteristics  $(I_D-V_G)$  in linear  $(|V_{\rm DS}|=50~{\rm mV})$  and saturation  $(|V_{\rm DS}|=1.2~{\rm V})$  regions, and output characteristics  $(I_D-V_D)$  for multiple  $|V_{\rm GS}|$  values. Each measurement was repeated for several  $|V_{\rm BS}|$  for body-effect characterization. Devices were tested at room  $(T=295~{\rm K})$  and cryogenic  $(T=5.7~{\rm K})$  temperatures. This allowed to verify the correct operation by comparing room temperature measurements with simulations, enabling the rejection of any possibly damaged devices.

#### III. EXPERIMENTAL RESULTS

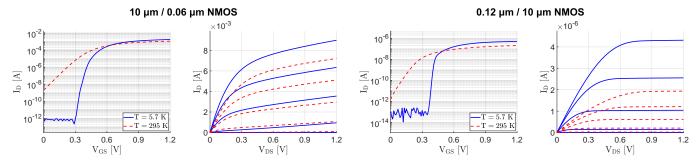

In agreement with previous literature in the field, the test devices showed an overall increase in threshold voltage, a steep increase in subthreshold slope (SS), resulting in a reduction of more than three orders of magnitude in leakage, and a marked increase in transconductance due to increased free carrier mobility at cryogenic temperature [9]–[12]. The variation of electrical parameters with temperature is strongly dependent on channel length and width. The right side of Fig. 3 and the I-V characteristics of Fig. 4 clearly show how the gate geometry affects both the increase in transconductance and drive current at cryogenic temperature. No kink effect [9] was observed, in contrast to previous reports using both the same technology [34] and more recent nodes [35].

Fig. 4. Transfer characteristics with  $V_{DS} = 50 \text{ mV}$  and output characteristics for a wide/short (left) and a narrow/long (right) NMOS device. For the output characteristics,  $V_{GS}$  was stepped from 0.3 V to 1.2 V with a constant step size.

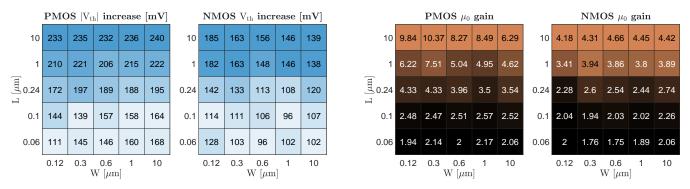

Fig. 5. Increase in threshold voltage  $V_{\rm th}$  and low-field mobility  $\mu_0$  at cryogenic temperature. The gain in  $\mu_0$  is defined as the ratio  $\mu_0(5.7K)/\mu_0(295K)$ . Both  $V_{\rm th}$  and  $\mu_0$  were extracted using the Y-function method [36] with  $|V_{\rm DS}|=50~{\rm mV}$ . Darker shades indicate less desirable cryogenic variations.

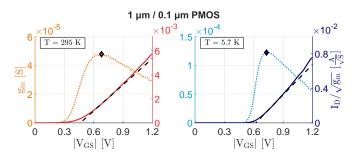

Fig. 6. Transconductance  $\mathbf{g_m}$  for  $|\mathbf{V_{DS}}| = 50~\mathrm{mV}$  (dotted lines) and Y-function [36]  $\mathbf{I_D}/\sqrt{\mathbf{g_m}}$  for a sample device, in both temperature conditions. Markers indicate the peak  $\mathbf{g_m}$  point used for the extraction. Dashed lines indicate the linear approximation at the extraction point.

Figure 5 shows the increase in threshold voltage  $V_{\rm th}$  and in low-field mobility  $\mu_0$  (both extracted with the Y-function method [36]) at cryogenic temperature, for all fabricated gate geometries. It is worth noting that the extraction for thin oxide devices is complicated by the impact of mobility degradation due to surface scattering, which at cryogenic temperature becomes even more prominent and contributes to the bellshaped appearance of the gate voltage dependence of mobility [37], [38]. Mobility becomes then a nonhomographic function of gate voltage [40], [41], thus limiting the applicability of extraction by Y-function to only the range of V<sub>GS</sub> voltages in which it remains linear, as depicted in Fig. 6. Nevertheless, the effectiveness of this method for low-field mobility extraction of nanoscale devices at cryogenic temperature has been demonstrated before [21]. To corroborate the results and also gain more information about the impact of gate geometry,

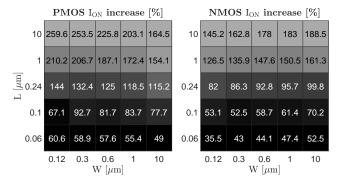

Fig. 7. Device ON current increase at cryogenic temperature. The ON current is defined as the maximum  $|I_D|$  for  $|V_{DS}| = 50 \text{ mV}$  and  $|V_{BS}| = 0 \text{ V}$ . The increase is calculated as  $|[I_{ON}(5.7\text{K}) - I_{ON}(295\text{K})]/I_{ON}(295\text{K})| \cdot 100$ . Darker shades indicate less desirable cryogenic variations.

Fig. 7 adds information on the ON current increase. This allows to directly observe the correlation with the increase in  $V_{\rm th}$  and mobility, thus consolidating the extraction results.

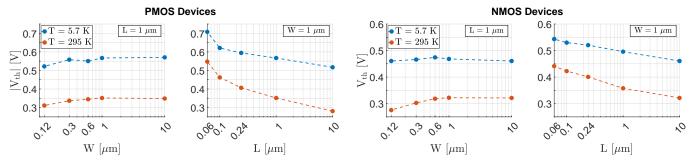

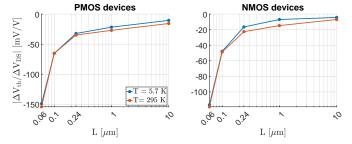

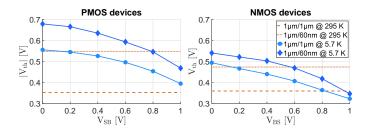

As previously reported for other technologies, short channel effects (SCE) have a larger impact on the threshold voltage at cryogenic temperature [19], also due to the weakening of the reverse short channel effect (RSCE) [42]. In contrast to room temperature conditions, however, at cryogenic temperature this has a positive effect on device operation since it limits the shift of  $V_{\rm th}$  as channel length decreases. Unfortunately, as can be seen from Fig. 8, the cryogenic increase of  $V_{\rm th}$  is still dominant and can become problematic, especially for PMOS devices. On the other hand, the impact of the reverse narrow

Fig. 8. Impact of short channel effects and reverse narrow channel effect on threshold voltage for both temperature conditions.  $V_{\rm th}$  values extracted with the Y-function method at  $|V_{\rm DS}| = 50~{\rm mV}$ .

width effect (RNWE, i.e., the decrease in V<sub>th</sub> for smaller W) [43] at cryogenic temperature is significantly suppressed for long NMOS devices, but shows little temperature dependency for long PMOS devices. The impact of channel width on V<sub>th</sub>, however, appears to change as the channel length is reduced. In fact, short-channel PMOS devices seem to benefit from a smaller increase in threshold voltage as the channel narrows, while the opposite seems to happen for NMOS. This trend is also confirmed by the different increase in ON current (Fig. 7) for the minimum length devices, despite their insubstantial change in mobility gain with channel width. The mobility gain in these devices, in fact, is clearly dominated by the well-known mobility collapse for short channels and its weak temperature dependence [44], [45]. This behavior of V<sub>th</sub> for short channel devices could then be attributed to the complex interactions between three-dimensional carrier scattering [15] and shallow trench isolation (STI) stress effects that occur in the device as the channel shrinks [46], [47], as the latter are enhanced by the significant thermal expansion/contraction at low-temperature [30]. This hypothesis is supported by the fact that STI stress is known to have an opposite impact on electron and hole mobility and a more pronounced channel width dependence in PMOS [48], which can also explain the opposite trend in long channel PMOS and NMOS for both the mobility and the ON current increase as the channel width is reduced. Further investigation with dedicated test structures would be needed for a complete evaluation of the STI stress behavior at cryogenic temperature.

Drain-induced barrier lowering (DIBL) and drain-induced threshold shift (DITS) [25] were characterized with the constant current method [50] and a normalized current  $I_D/(W/L)$  equal to 100 nA. Both effects showed a very weak temperature dependence for this technology, as visible in Fig. 9.

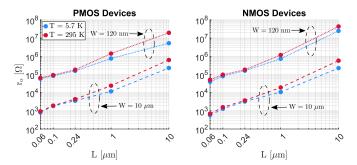

The competing effects of threshold voltage and mobility at cryogenic temperature also have an impact on the output conductance  $g_{\rm o}$ , which can be extracted from the output I-V characteristics. The increase in mobility seems to prevail when the devices are in strong inversion, resulting in a generally higher output conductance at cryogenic temperature. This corresponds to an overall reduction in output resistance  $r_{\rm o}=1/g_{\rm o}$ , visible in Fig. 10, which in turn counterbalances the benefit of a larger saturation  $g_{\rm m}$  (see again Fig. 3) for the intrinsic gain of the device.

Fig. 9. DIBL (DITS for long channel) impact on  $V_{\rm th}$  for both PMOS and NMOS devices.  $W=10\mu m$  for all the data points.

Fig. 10. Extracted saturation output resistance values in strong inversion ( $|\mathbf{V_{GS}}| = |\mathbf{V_{DS}}| = \mathbf{0.9} \; \mathbf{V}$ ) for several gate geometries.

## IV. TECHNOLOGY PERFORMANCE METRICS

Although essential for modeling, the characterization of physical parameters such as  $V_{\rm th}$  and mobility does not allow to get directly valuable information about the performance of a technology at cryogenic temperature for circuit design. For this purpose, it is much more enlightening to use some of the figures of merit commonly used in analog design. To get a better view of the overall cryogenic performance, the following discussion is divided into saturation and linear region.

#### A. Saturation

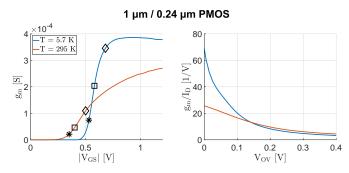

A widely popular analog design methodology is based on the transconductance efficiency  $g_{\rm m}/I_{\rm D}$  [24]. To use the  $g_{\rm m}/I_{\rm D}$  methodology in this performance evaluation, the geometry in Fig. 11 is considered, being a common choice for gate fingers in this technology node [24]. It should be noted that such a gate geometry is almost exclusively affected by short channel effects. Because of the significant increase of  $g_{\rm m}/I_{\rm D}$  at cryogenic temperature in weak inversion [11], a fair comparison

between the two temperature conditions based on the inversion level is not trivial. For this reason, Fig. 11 depicts the extracted  $\rm g_m/I_D$  as a function of the overdrive voltage  $\rm V_{OV}$ , in order to establish a link between the cryogenic and room-temperature values of  $\rm g_m/I_D$ . In this analysis, the subthreshold region is excluded as the impact of mismatch makes biasing in weak inversion an undesirable choice at cryogenic temperature [30]. For the PMOS of Fig. 11, as an example, the subthreshold swing (1/SS) drops to about 12 mV/dec when the device is cooled down. This means that a variation of 10 mV on  $\rm V_{th}$  will cause an error on the subthreshold current of almost one decade.

With reference to Table I, if the transistor is biased just outside the weak inversion region ( $V_{\rm OV}=50~{\rm mV}$ ),  $g_{\rm m}/I_{\rm D}$  at cryogenic temperature becomes significantly higher than at room temperature. Moving the bias point towards strong inversion ( $V_{\rm OV}=200~{\rm mV}$ ), however, causes the cryogenic  $g_{\rm m}/I_{\rm D}$  to drop rapidly, reaching values slightly lower than at room temperature. This aspect has already been reported in literature [9] and is a direct consequence of the enhanced impact of the vertical field-induced mobility degradation [17].

TABLE I PERFORMANCE METRICS FOR A PMOS DEVICE WITH  $W/L = 1~\mu m/0.24~\mu m$

|            |                             | $g_{\rm m}/I_{\rm D}~[{\rm V}^{-1}]$ |       | $I_{\mathrm{D}}/\mathrm{W}~[\mathrm{A/m}]$ |       |

|------------|-----------------------------|--------------------------------------|-------|--------------------------------------------|-------|

|            |                             | 295 K                                | 5.7 K | 295 K                                      | 5.7 K |

| *          | $ V_{OV}  = 50 \text{ mV}$  | 21.4                                 | 34.6  | 0.9                                        | 1.9   |

|            | $ V_{OV}  = 100 \text{ mV}$ | 16.8                                 | 20.2  | 2.6                                        | 8.7   |

| $\Diamond$ | $ V_{OV}  = 200 \text{ mV}$ | 9.7                                  | 8.3   | 10.4                                       | 37.9  |

Symbols correspond to the markers in Fig. 11.

Fig. 11. Analog FoMs for a PMOS test device in saturation with  $W/L=1~\mu m/0.24~\mu m$ . Left: transconductance  $g_m$  in saturation; markers correspond to the different bias conditions listed in Table I. Right: transconductance efficiency  $g_m/I_D$  versus overdrive voltage  $V_{OV}=|V_{GS}-V_{\rm th,sat}|,$  where  $V_{\rm th,sat}$  is the threshold voltage in saturation (extracted with the constant current method).

The current density  $I_{\rm D}/W$  at cryogenic temperature is significantly higher than at room temperature for all three bias points. The difference from room temperature increases with the overdrive voltage, reaching an almost four times increase in strong inversion. Unfortunately, this means that keeping the same bias point (i.e. the same  $V_{\rm OV}$ ), from cryogenic temperature to room temperature, will lead to an increase in power consumption. Conversely, at constant current (constant  $I_{\rm D}/W$ ), the operating point will shift towards weak inversion

as the temperature drops, leading to an increase in  $g_{\rm m}/I_{\rm D}$  and thus an increase in the transconductance  $g_{\rm m}$ , as shown in Fig. 11. Considering that the gate-related capacitances are virtually insensitive to temperature [11], [16], the device will show a similar increase in its transit frequency  $f_{\rm T}$  [24].

However, it should be noted that this shift of the bias point has a direct consequence on the design of low-power circuits. In optimizing power consumption at room temperature, in fact, biasing at or just above subthreshold is widely exploited [51]. By keeping the current (and thus power consumption) constant in the transition from room temperature to cryogenic temperature, the bias point will shift into deep weak inversion, incurring variability problems as highlighted above. This greatly complicates the optimization of low power circuits for a wide temperature range. A possible solution to this issue is to exploit the body terminal to compensate for the variations in V<sub>th</sub>, as already proposed in literature for room temperature [52]. However, maintaining the bias in deep moderate inversion at cryogenic temperature is preferable to obtain a good compromise between matching and efficiency. This bias point has also been previously suggested as the optimal point for the design of cryogenic RF LNAs [53].

TABLE II

ON RESISTANCE PER UNIT WIDTH FOR A

MINIMUM-LENGTH NMOS

|                              | 295 K                        | 5.7 K                       |

|------------------------------|------------------------------|-----------------------------|

| $V_{\rm GS} = 0.6 \ \rm V$   | 2031.2 $\Omega \cdot \mu m$  | 3118.6 $\Omega \cdot \mu m$ |

| $V_{GS} = 0.9 V$             | $716.2 \Omega \cdot \mu m$   | $488.8 \Omega \cdot \mu m$  |

| $V_{\rm GS} = 1.2 \text{ V}$ | $502.3 \ \Omega \cdot \mu m$ | $326.6 \Omega \cdot \mu m$  |

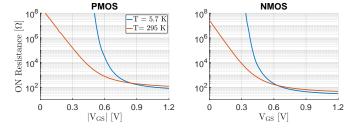

Fig. 12. Extracted ON resistance for a PMOS and NMOS transistor versus the applied  $V_{\rm GS}.~W/L=10~\mu{\rm m}/60~{\rm nm}$  for both devices.

## B. Linear region

The most common use of the MOSFET transistor in linear region is as a switch. For this reason, the cryogenic performance in linear region can be evaluated using the ON resistance of the switch. Table II shows the values of ON resistance per unit gate width of a minimum length NMOS transistor, for three different values of  $V_{\rm GS}$ .

From the values shown in the table, it is evident that the cryogenic increase in mobility results in better MOS switches only when the switch turn-on voltage is sufficiently high. For  $V_{\rm GS}=0.6~V,$  in fact, the resistance per unit width is larger at cryogenic temperature, so the switch behavior is clearly dominated by the increase in  $V_{\rm th}.$

Fig. 13. Threshold voltage for  $|V_{\rm DS}| = 50~{

m mV}$  (extracted with the Y-function method) at different levels of body biasing. Dashed lines indicate the extracted  $V_{\rm th}$  at room temperature with no body effect.

Figure 12 shows the ON resistances for a PMOS and NMOS of a given size. For the PMOS device, given the larger increase in  $V_{\rm th}$  at cryogenic temperature and the fairly limited gain in mobility due to the short channel (see also Fig. 5), the minimum voltage required to exceed the performance at room temperature is even higher. Using complementary transmission gates, therefore, does not bring substantial benefits.

This counter-intuitive aspect of cryogenic switch performance can force design compromises in critical blocks, resulting in higher power consumption [54]. For both highprecision and high-speed applications, circuit techniques such as bootstrapping [55] should be used to circumvent this problem. Another technique that can be effectively used to deal with the increase in V<sub>th</sub> is the forward body biasing (FBB) [56]. By taking advantage of the increased turn-on voltage of parasitic diodes at cryogenic temperature, it is indeed possible to use the body terminal as a back-gate, similar to FDSOI technologies, without incurring large increases in leakage currents to the substrate. As shown in Fig. 13, in fact, the FBB technique allows to considerably reduce the threshold voltage, bringing  $V_{\mathrm{th}}$  even below its nominal value at room temperature. However, the application of FBB appears to be less effective on long channel PMOS devices. While for the NMOS it is always possible to bring  $V_{\rm th}$  below the room temperature value, the long PMOS suffers from both a much greater increase in V<sub>th</sub> at cryogenic temperature (see Fig. 5) and a lower FBB effectiveness.

## V. MODELING AND SIMULATION

Similarly to most previous works in the literature [9]–[19], the modeling effort in this work focuses on the device DC characteristics. This is not a limitation for using the model for analog and mixed-signal circuit design, since MOSFET gate capacitances in inversion are practically independent of temperature [11], [16], [58], [59].

In developing the model, temperature scaling was ignored, since 1) the temperature is stable and well controlled in the target environments (cryogenic chambers), and 2) the properties of Si nanoscale CMOS devices do not change significantly for  $T < 50 \ K \ [15], \ [21], \ [57].$

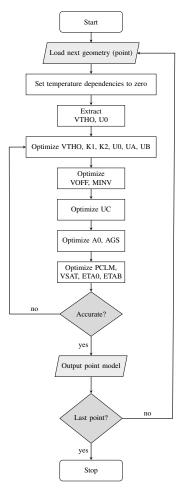

The modeling procedure begins by extracting the target model card from the library in the foundry PDK. The binning in the original model card is exploited to generate a *point model* for each of the measured devices. A custom modeling flow for cryogenic parameter extraction and optimization,

depicted in Fig. 14, is then applied to each point model in order to re-center it on the cryogenic measurement data.

Fig. 14. Simplified cryogenic modeling flow diagram for the individual gate geometries (points). The point models used in this flow are generated starting from the foundry binning and, after being processed with the flow, they are subsequently used to re-build the original binning.

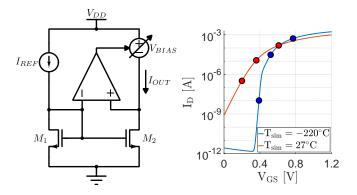

At the beginning of this process, temperature dependencies are set to zero [9], as they lead to a considerable error in the estimation of the parameters at cryogenic temperature (see Fig. 17). The parameters that most influence device behavior are those related to threshold voltage, mobility and bulk charge effect [49]. Therefore, the flow focuses primarily on these parameters. A complete list of parameters used in the flow is given in Tab. III. The simulation temperature for parameter optimization is set to  $T = -220^{\circ}C$  to match the (average) subthreshold slope, as the BSIM4 model is not able to represent the SS deviation at cryogenic temperature [11].

The optimization steps in Fig. 14 should minimize the error on a weighted combination of both the I-V curves and their derivatives (e.g.,  $g_{\rm ds}=\partial I_{\rm D}/\partial V_{\rm DS})$  [46]. A standard Levenberg-Marquardt algorithm can be used for curve fitting. However, since there are many combinations of parameters that can lead to essentially the same quality of model fit on the measured data, care must be taken in the optimization steps. The parameter values should always be limited within reasonable ranges. Physical parameters, in particular, should show values similar to those resulting from direct extractions

TABLE III

LIST OF BSIM4 MODEL PARAMETERS EDITED IN THE FLOW

| Parameter | Description                                                            |

|-----------|------------------------------------------------------------------------|

| VTHO      | Long-channel threshold voltage at $V_{\rm BS}=0$                       |

| K1        | First-order body bias coefficient                                      |

| K2        | Second-order body bias coefficient                                     |

| U0        | Low-field mobility                                                     |

| UA        | Coefficient of first-order mobility degradation                        |

| UB        | Coefficient of second-order mobility degradation                       |

| UC        | Coefficient of mobility degradation due to body-bias                   |

| VSAT      | Saturation velocity                                                    |

| A0        | Coefficient of L dependence of bulk charge effect                      |

| AGS       | Coefficient of V <sub>GS</sub> dependence of bulk charge effect        |

| KETA      | Body-bias coefficient of bulk charge effect                            |

| VOFF      | Offset voltage in subthreshold region for large W and L                |

| MINV      | V <sub>gsteff</sub> fitting parameter for moderate inversion condition |

| ETA0      | DIBL coefficient in subthreshold region                                |

| ETAB      | Body-bias coefficient for the sub-threshold DIBL effect                |

| PCLM      | Channel length modulation parameter                                    |

| RDSW      | Zero-bias LDD resistance per unit width                                |

#### on measurement data.

The overall output of this flow is a set of re-centered cryogenic point models, which are then used to rebuild a single cryogenic model card with binning. At this stage, the model can be further optimized with measurement data, if necessary. The use of binning also provides additional degrees of freedom for fitting and allows the normal scaling capabilities of BSIM4 to be extended [46].

This binned cryogenic model card is then compared with the original one, and the differences in the target parameters are applied to the latter. The modified model code is finally used to overwrite the corresponding section in a copy of the foundry library, thus obtaining a modified version that can be used for cryogenic analog circuit design and simulation.

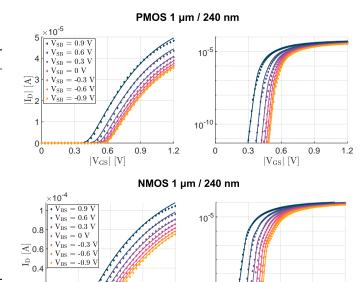

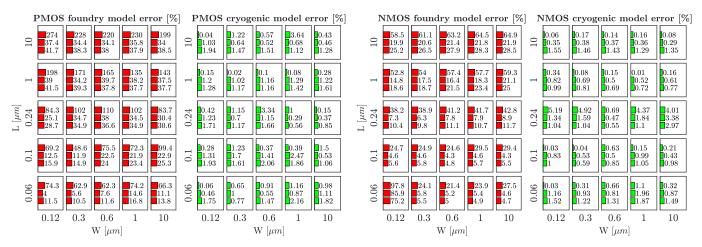

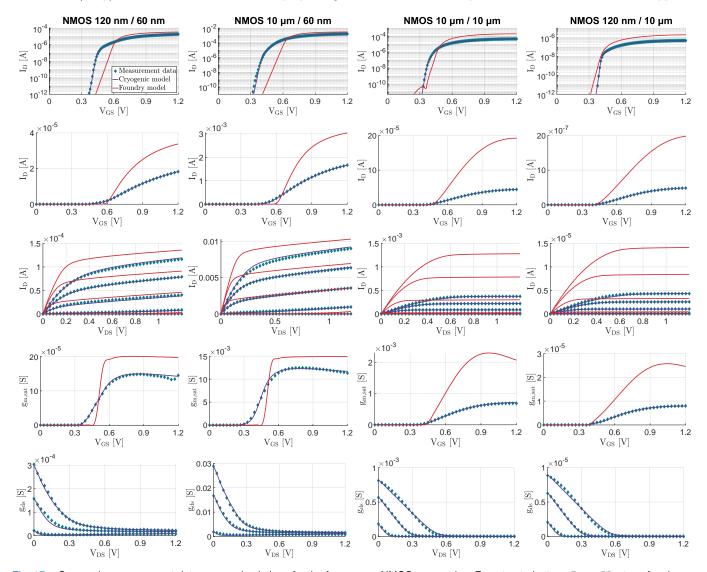

The model obtained with this procedure shows a good fit of the experimental data, visible in Figs. 15, 16 and 17. As shown in Fig. 15, the re-centered model manages to simulate with satisfactory accuracy the body effect at cryogenic temperature, including forward body biasing. It is therefore possible to evaluate the use of this promising technique in simulation. The RMS errors in Fig. 16 are defined as follows [60]:

Error<sub>RMS</sub> [%] =

$$\sqrt{\frac{1}{N} \sum_{i=1}^{N} \left( \frac{X_{meas} - X_{sim}}{\max{\{|X_{meas}|, |(X_{sim}|)\}}} \right)^2}$$

(1)

where X is the quantity of interest (e.g. the drain current). Normally, a fit is considered of excellent quality if the RMS error is below 2% [60]. Although the standard BSIM4 model is clearly not a good candidate for a physically rigorous cryogenic model, the re-centered model constitutes an effective rapid enabler to cryogenic circuit simulation and considerably reduces the foundry model error, which for some geometries can be of more than 200%.

Finally, it is important to note that re-centering the parameters in the modeling procedure in Fig. 14 alters only their nominal value, leaving the statistical changes applied to the parameter unaffected. This allows the modified model to retain mismatch simulation capabilities. Although the results obtainable with the modified model provide only an estimate,

Fig. 15.  $I_D-V_G$  transfer characteristics in linear and logarithmic scale for two sample devices with  $|V_{DS}|=50~\mathrm{mV}$  and different body biases. Markers: measurement data at  $T=5.7~\mathrm{K}$ . Lines: simulation with the re-centered model ( $T_{\mathrm{SIM}}=-220^{\circ}\mathrm{C}$ ).

0

0.3

0.6

$V_{GS}[V]$

1.2

TABLE IV

MONTECARLO SIMULATION RESULTS FOR THE NMOS CURRENT

MIRROR OF FIG. 18

| Simulation temperature                                   | 27°C                      |                              | -220°C                   |                            |

|----------------------------------------------------------|---------------------------|------------------------------|--------------------------|----------------------------|

|                                                          | $I_{REF}$                 | $\sigma_{ m IOUT}$           | $I_{REF}$                | $\sigma_{ m IOUT}$         |

| Weak inversion<br>Moderate inversion<br>Strong inversion | 300 nA<br>10 μA<br>150 μA | 17.4 nA<br>0.38 μA<br>1.8 μA | 10 nA<br>30 μA<br>500 μA | 4.6 nA<br>1.6 μA<br>6.1 μA |

The operating points are shown in Fig. 18.

0.3

they still allow a qualitative assessment that would otherwise be impossible. Even considering resorting to the foundry model only for this type of simulation, the results would not be representative at all because of the shift in the operating point discussed in the previous section.

As an example, Table IV shows the results of a Monte Carlo simulation with 1000 iterations of the circuit in Fig. 18. The strong deterioration of matching in weak inversion due to the steep slope of the subthreshold current, visible in Fig. 18, is very clear from the simulation results.

## VI. CONCLUSION

The cryogenic characterization of a 65-nm Si-Bulk CMOS technology was presented, highlighting the impact of gate geometry effects on the device behavior at cryogenic temperature. The performance of the technology in the context of analog circuit design was discussed. Although the cryogenic environment offers advantages such as the marked increase in transconductance, it also poses challenges for the circuit designer. A design-oriented, robust modeling procedure was proposed, which allows to obtain a fully scalable cryogenic compact model with simple BSIM4 parameter re-centering.

Fig. 16. Accuracy of the foundry model and the cryogenic model for both PMOS and NMOS. For each device, starting from the topmost error bar: 1) error on  $I_{ON}$ , defined as the maximum  $|I_{D}|$  for  $|V_{DS}|=50~mV$  and  $V_{BS}=0~V$ ; 2) average RMS error on the  $I_{D}$ - $V_{GS}$  characteristics in saturation, for  $|V_{DS}|=1.2~V$  and several values of  $V_{BS}$ ; 3) average RMS error on the  $I_{D}$ - $V_{DS}$  characteristics for several values of  $V_{GS}$ .

Fig. 17. Cryogenic measurement data versus simulations for the four corner NMOS geometries. From top to bottom:  $I_D - V_G$  transfer characteristics in logarithmic and linear scale for  $V_{DS} = 50~\mathrm{mV}$ ; output  $I_D - V_D$  characteristics for several values of  $V_{GS}$ ; transconductance  $g_m$  in saturation ( $V_{DS} = 1.2~\mathrm{V}$ ); output conductance  $g_{ds}$  in saturation for three different  $V_{GS}$  voltages (foundry model data omitted due to extremely large error). Data points in linear scale are decimated. Measurement temperature  $T = 5.7~\mathrm{K}$ . Simulation temperature  $T_{SIM} = -220$ °C.

Fig. 18. Left: testbench circuit used for Montecarlo simulations. Transistors  $M_1$  and  $M_2$  are sized identical,  $W/L=6~\mu\mathrm{m}/0.6~\mu\mathrm{m}$ . The ideal feedback loop equalizes the voltage at the two drain terminals. Right: the operating points chosen for the local mismatch simulations.

The proposed approach can be applied to any nanoscale CMOS technology using a model that lacks a Verilog-A official implementation, or another way to access the model equations directly. This improves the design possibilities of cryogenic analog and mixed-signal circuits.

#### REFERENCES

- [1] E. Charbon, "Cryo-CMOS Electronics for Quantum Computing Applications," ESSDERC 2019, Cracow, Poland, 2019, pp. 1-6, doi: 10.1109/ESSDERC.2019.8901812.

- [2] F. Tavernier, A. Gatti and C. Barretto, "Chip Design for Future Gravitational Wave Detectors," 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2020, pp. 25.4.1-25.4.4, doi: 10.1109/IEDM13553.2020.9372071.

- [3] J. V. Van Heijningen et al., "The payload of the Lunar Gravitationalwave Antenna," Journal of Applied Physics, vol. 133, no. 24, p. 244501, Jun. 2023, doi: 10.1063/5.0144687.

- A. Sider et al., "E-TEST: a compact low-frequency isolator for a large cryogenic mirror," Classical and Quantum Gravity, Jun. 2023, doi: 10.1088/1361-6382/ace230.

- [5] D. Braga, S. Li and F. Fahim, "Cryogenic Electronics Development for High-Energy Physics: An Overview of Design Considerations, Benefits, and Unique Challenges," in IEEE Solid-State Circuits Magazine, vol. 13, no. 2, pp. 36-45, Spring 2021, doi: 10.1109/MSSC.2021.3072804.

- [6] F. Balestra, L. Audaire and C. Lucas, "Influence of substrate freeze-out on the characteristics of MOS transistors at very low temperatures," in Solid-State Electronics, vol. 30, no. 3, pp. 321-327, Mar. 1987, doi: 10.1016/0038-1101(87)90190-0.

- [7] B. Dierickx, E. Simoen, S. Cos, J. Vermeiren, C. Claeys and G. J. Declerck, "Anomalous kink-related excess noise in MOSFETs at 4.2 K," in IEEE Transactions on Electron Devices, vol. 38, no. 4, pp. 907-912, Apr. 1991, doi: 10.1109/16.75222.

- [8] A. Akturk, M. Holloway, S. Potbhare, D. Gundlach, B. Li, N. Goldsman, M. Peckerar and K. P. Cheung, "Compact and Distributed Modeling of Cryogenic Bulk MOSFET Operation," in IEEE Transactions on Electron Devices, vol. 57, no. 6, pp. 1334-1342, Jun. 2010, doi: 10.1109/TED.2010.2046458.

- [9] R. M. Incandela, L. Song, H. Homulle, E. Charbon, A. Vladimirescu and F. Sebastiano, "Characterization and Compact Modeling of Nanometer CMOS Transistors at Deep-Cryogenic Temperatures," in IEEE Journal of the Electron Devices Society, vol. 6, pp. 996-1006, 2018, doi: 10.1109/JEDS.2018.2821763.

- [10] A. Beckers, F. Jazaeri and C. Enz, "Cryogenic MOS Transistor Model," in IEEE Transactions on Electron Devices, vol. 65, no. 9, pp. 3617-3625, Sept. 2018, doi: 10.1109/TED.2018.2854701.

- [11] A. Beckers, F. Jazaeri and C. Enz, "Characterization and Modeling of 28-nm Bulk CMOS Technology Down to 4.2 K," in IEEE Journal of the Electron Devices Society, vol. 6, pp. 1007-1018, 2018, doi: 10.1109/JEDS.2018.2817458.

- [12] A. Beckers, F. Jazaeri, A. Grill, S. Narasimhamoorthy, B. Parvais and C. Enz, "Physical Model of Low-Temperature to Cryogenic Threshold Voltage in MOSFETs," in IEEE Journal of the Electron Devices Society, vol. 8, pp. 780-788, 2020, doi: 10.1109/JEDS.2020.2989629.

- [13] A. Kabaoğlu, N. Şahin-Solmaz, S. İlik, Y. Uzun, and M. B. Yelten, "Variability-aware cryogenic models of mosfets: validation and circuit design," Semiconductor Science and Technology, vol. 34, no. 11, p. 115004, Nov. 2019, doi: 10.1088/1361-6641/ab3ff9.

- [14] Z. Wang et al., "Temperature-Driven Gate Geometry Effects in Nanoscale Cryogenic MOSFETs," in IEEE Electron Device Letters, vol. 41, no. 5, pp. 661-664, May 2020, doi: 10.1109/LED.2020.2984280.

- [15] Y. Liu, L. Lang, Y. Chang, Y. Shan, X. Chen and Y. Dong, "Cryogenic Characteristics of Multinanoscales Field-Effect Transistors," in IEEE Transactions on Electron Devices, vol. 68, no. 2, pp. 456-463, Feb. 2021, doi: 10.1109/TED.2020.3041438.

- [16] Z. Tang et al., "Cryogenic CMOS RF Device Modeling for Scalable Quantum Computer Design," in IEEE Journal of the Electron Devices Society, vol. 10, pp. 532-539, 2022, doi: 10.1109/JEDS.2022.3186979.

- [17] G. Pahwa, P. Kushwaha, A. Dasgupta, S. Salahuddin and C. Hu, "Compact Modeling of Temperature Effects in FDSOI and FinFET Devices Down to Cryogenic Temperatures," in IEEE Transactions on Electron Devices, vol. 68, no. 9, pp. 4223-4230, Sept. 2021, doi: 10.1109/TED.2021.3097971.

- S. Gupta, S. K. Singh, R. A. Vega and A. Dixit, "Effective Channel Mobility Extraction and Modeling of 10-nm Bulk CMOS FinFETs in Cryogenic Temperature Operation for Quantum Computing Applications," in IEEE Transactions on Electron Devices, vol. 70, no. 4, pp. 1815-1822, April 2023, doi: 10.1109/TED.2023.3244159.

- [19] J. Huang, Y. Zhang, Y. Chen, J. Xu, C. Luo, G. Guo, Characterization and compact modeling of short channel MOSFETs at cryogenic temperatures, Solid-State Electronics, Volume 204, 2023, 108637, ISSN 0038-1101, doi: 10.1016/j.sse.2023.108637.

- [20] T. Tsai, H. -C. Lin and P. -W. Li, "Temperature-Dependent Narrow Width Effects of 28-nm CMOS Transistors for Cold Electronics," in IEEE Journal of the Electron Devices Society, vol. 10, pp. 289-296, 2022, doi: 10.1109/JEDS.2022.3163251.

- [21] A. Bhardwaj, S. K. Singh and A. Dixit, "Narrow-Width Effects in 28nm FD-SOI Transistors Operating at Cryogenic Temperatures," in IEEE Journal of the Electron Devices Society, vol. 11, pp. 22-29, 2023, doi: 10.1109/JEDS.2022.3233302.

- [22] W. Chakraborty, K. Ni, S. Dutta, B. Grisafe, J. Smith and S. Datta, "Cryogenic Response of HKMG MOSFETs for Quantum Computing Systems," 2019 Device Research Conference (DRC), Ann Arbor, MI, USA, 2019, pp. 115-116, doi: 10.1109/DRC46940.2019.9046346.

- [23] C. Enz and H.-C. Han, "Design of Cryo-CMOS Analog Circuits using the G<sub>m</sub>/I<sub>D</sub> Approach," 2023 IEEE International Symposium on Circuits and Systems (ISCAS), Monterey, CA, USA, 2023, pp. 1-5, doi: 10.1109/ISCAS46773.2023.10181986.

- [24] P. G. A. Jespers and B. Murmann, Systematic Design of Analog CMOS Circuits: Using Pre-Computed Lookup Tables, Cambridge University

- [25] BSIM 4.5.0 Mosfet Model User's Manual, 2005. [Online]. Available: http://bsim.berkeley.edu/models/bsim4/.

- [26] G. J. Coram, "How to (and how not to) write a compact model in Verilog-A," Proceedings of the 2004 IEEE International Behavioral Modeling and Simulation Conference (BMAS) 2004, San Jose, CA, USA, 2004, pp. 97-106, doi: 10.1109/BMAS.2004.1393990.

- [27] C. C. McAndrew, "Practical modeling for circuit simulation," in IEEE Journal of Solid-State Circuits, vol. 33, no. 3, pp. 439-448, March 1998, doi: 10.1109/4.661209.

- [28] M.-A. Chalkiadaki, C. Valla, F. Poullet and M. Bucher, "Why- and how- to integrate Verilog-A compact models in SPICE simulators," International Journal of Circuit Theory and Applications, vol. 41, no. 11, pp. 1203-1211, 2013, doi: 10.1002/cta.1833.

- [29] M. Rudan, R. Brunetti, S. Reggiani, eds., Springer Handbook of Semiconductor Devices, Springer, 2023, doi: 10.1007/978-3-030-79827-7.

- [30] P. A. 'T Hart, M. Babaie, E. Charbon, A. Vladimirescu and F. Sebastiano, "Characterization and Modeling of Mismatch in Cryo-CMOS," in IEEE Journal of the Electron Devices Society, vol. 8, pp. 263-273, 2020, doi: 10.1109/JEDS.2020.2976546.

- [31] Low-Level Measurements Handbook 7th edition. Tektronix, 2016. [Online]. Available: https://download.tek.com/document/LowLevelHand book\_7Ed.pdf

- J. W. Ekin, Experimental techniques for low-temperature measurements, Oxford University Press, 2006.

- [33] Cryogenic Temperature Sensor Selection Guide. Lake Shore. [Online]. Available: https://www.lakeshore.com/products/categories/downloads/ temperature-products/cryogenic-temperature-sensors/cernox

- [34] J. Ning, M. Schormans and A. Demosthenous, "Towards an Improved Model for 65-nm CMOS at Cryogenic Temperatures," 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 2020, pp. 1-5, doi: 10.1109/ISCAS45731.2020.9180666.

- [35] F. Jazaeri, A. Beckers, A. Tajalli and J.-M. Sallese, "A Review on Quantum Computing: From Qubits to Front-end Electronics and Cryogenic MOSFET Physics," 2019 MIXDES - 26th International Conference "Mixed Design of Integrated Circuits and Systems", Rzeszow, Poland, 2019, pp. 15-25, doi: 10.23919/MIXDES.2019.8787164.

- [36] G. Ghibaudo, "New method for the extraction of MOSFET parameters," *Electronics Letters*, vol. 24, no. 9, p. 543, 1988, doi: 10.1049/el:19880369.

- [37] S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFET's: Part I-effects of substrate impurity concentration," IEEE Transactions on Electron Devices, vol. 41, no. 12, pp. 2357–2362, Dec. 1994, doi: 10.1109/16.337449.

- [38] F. Balestra and G. Ghibaudo, "Physics and performance of nanoscale semiconductor devices at cryogenic temperatures," *Semiconductor Science and Technology*, vol. 32, no. 2, p. 023002, Feb. 2017, doi: 10.1088/1361-6641/32/2/023002.

- [39] F. Balestra, G. Ghibaudo, eds., Device and Circuit Cryogenic Operation for Low Temperature Electronics, Springer, 2010, doi: 10.1007/978-1-4757-3318-1

- [40] A. Emrani, F. Balestra and G. Ghibaudo, "Generalized mobility law for drain current modeling in Si MOS transistors from liquid helium to room temperatures," in *IEEE Transactions on Electron Devices*, vol. 40, no. 3, pp. 564-569, March 1993, doi: 10.1109/16.199361.

- [41] F. Jazaeri, A. Pezzotta and C. Enz, "Free Carrier Mobility Extraction in FETs," in IEEE Transactions on Electron Devices, vol. 64, no. 12, pp. 5279-5283, Dec. 2017, doi: 10.1109/TED.2017.2763998.

- [42] B. Szelag, F. Balestra and G. Ghibaudo, "Comprehensive analysis of reverse short-channel effect in silicon MOSFETs from low-temperature operation," in *IEEE Electron Device Letters*, vol. 19, no. 12, pp. 511-513, Dec. 1998, doi: 10.1109/55.735763.

- 513, Dec. 1998, doi: 10.1109/55.735763.

[43] L. A. Akers, "The inverse-narrow-width effect," in *IEEE Electron Device Letters*, vol. 7, no. 7, pp. 419-421, July 1986, doi: 10.1109/EDL.1986.26422.

- [44] A. Cros, K. Romanjek, D. Fleury, S. Harrison, R. Cerutti, P. Coronel, B. Dumont, A. Pouydebasque, R. Wacquez, B. Duriez, R. Gwoziecki, F. Boeuf, H. Brut, G. Ghibaudo and T. Skotnicki, "Unexpected mobility degradation for very short devices: A new challenge for CMOS scaling," in 2006 International Electron Devices Meeting, Dec. 2006, pp. 1–4. doi: 10.1109/IEDM.2006.346872.

- [45] S. Cristoloveanu and G. Ghibaudo, "Intrinsic Mechanism of Mobility Collapse in Short MOSFETs," in *IEEE Transactions on Electron Devices*, vol. 68, no. 10, pp. 5090-5094, Oct. 2021, doi: 10.1109/TED.2021.3105083.

- [46] Y. Tsividis and C. McAndrew, Operation and Modeling of the MOS Transistor, 3rd edition, Oxford University Press, 2010.

- [47] P. Beow Yew Tan, A. V. Kordesch and O. Sidek, "Analysis of deep submicron CMOS transistor Vtlin and Idsat versus channel width," 2005 Asia-Pacific Microwave Conference Proceedings, Suzhou, China, 2005, pp. 4 pp.-, doi: 10.1109/APMC.2005.1606589.

- [48] V. Chan et al., "High speed 45nm gate length CMOSFETs integrated into a 90nm bulk technology incorporating strain engineering," *IEEE International Electron Devices Meeting 2003*, Washington, DC, USA, 2003, pp. 3.8.1-3.8.4, doi: 10.1109/IEDM.2003.1269170.

- [49] C. Hu and W. Liu, BSIM4 and Mosfet Modeling for IC Simulation, World Scientific Publishing Company, 2011.

- [50] A. Ortiz-Conde, F. J. Garcia Sanchez, J. J. Liou, A. Cerdeira, M. Estrada and Y. Yue, A review of recent MOSFET threshold voltage extraction methods, *Microelectronics Reliability*, Volume 42, Issues 4–5, 2002, Pages 583-596, ISSN 0026-2714, doi: 10.1016/S0026-2714(02)00027-6.

- [51] A. D. Grasso and S. Pennisi, "Ultra-Low Power Amplifiers for IoT Nodes," 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Bordeaux, France, 2018, pp. 497-500, doi: 10.1109/ICECS.2018.8617857.

- [52] E. Alpman, H. Lakdawala, L. R. Carley and K. Soumyanath, "A 1.1V 50mW 2.5GS/s 7b Time-Interleaved C-2C SAR ADC in 45nm LP digital CMOS," in 2009 IEEE International Solid-State Circuits Conference - Digest of Technical Papers, Feb. 2009, pp. 76-77,77a. doi: 10.1109/ISSCC.2009.4977315.

- [53] H.-C. Han, F. Jazaeri, A. D'Amico, Z. Zhao, S. Lehmann, C. Kret-zschmar, E. Charbon and Christian Enz, "Cryogenic RF Characterization

- and Simple Modeling of a 22 nm FDSOI Technology," *ESSDERC* 2022 *IEEE 52nd European Solid-State Device Research Conference (ESSDERC)*, Milan, Italy, 2022, pp. 269-272, doi: 10.1109/ESS-DERC55479.2022.9947192.

- [54] J. Lee, K. Kang, D. Minn and J. -Y. Sim, "A 7-10b Programmable Cryo-CMOS TI-SAR ADC for Multichannel Qubit Readout with On-Chip Background Inter-Channel Mismatch Calibrations," ESSCIRC 2023- IEEE 49th European Solid State Circuits Conference (ES-SCIRC), Lisbon, Portugal, 2023, pp. 169-172, doi: 10.1109/ESS-CIRC59616.2023.10268785.

- [55] M. Dessouky and A. Kaiser, "Very low-voltage digital-audio ΔΣ modulator with 88-dB dynamic range using local switch bootstrapping," in *IEEE Journal of Solid-State Circuits*, vol. 36, no. 3, pp. 349-355, March 2001, doi: 10.1109/4.910473.

- [56] R. W. J. Overwater, M. Babaie, and F. Sebastiano, "Cryogenic-Aware Forward Body Biasing in Bulk CMOS," in *IEEE Electron Device Letters*, vol. 45, no. 2, pp. 152-155, Feb. 2024, doi: 10.1109/LED.2023.3337441.

- [57] P. A. T Hart, M. Babaie, A. Vladimirescu and F. Sebastiano, "Characterization and Modeling of Self-Heating in Nanometer Bulk-CMOS at Cryogenic Temperatures," in *IEEE Journal of the Electron Devices Society*, vol. 9, pp. 891-901, 2021, doi: 10.1109/JEDS.2021.3116975.

- [58] A. Akturk, N. Goldsman, Z. Dilli and M. Peckerar, "Effects of cryogenic temperatures on small-signal MOSFET capacitances," 2007 International Semiconductor Device Research Symposium, College Park, MD, USA, 2007, pp. 1-2, doi: 10.1109/ISDRS.2007.4422237.

- [59] Q. Berlingard, J. Lugo-Alvarez, M. Bawedin, T. Mota-Frutuoso, C. Durand, D. Gloria, P. Galy and M. Cassé, "Capacitance RF Characterization and Modeling of 28 FD-SOI CMOS Transistors down to Cryogenic Temperature," 2023 18th European Microwave Integrated Circuits Conference (EuMIC), Berlin, Germany, 2023, pp. 37-40, doi: 10.23919/EuMIC58042.2023.10289100.

- [60] Keysight MBP Documentation, Version 2023u1. [Online]. Available: https://edadocs.software.keysight.com/mbp2023update1.