# Superior Turn-off dV/dt Controllability from Suppression of Dynamic Avalanche in 3300V Scaled IGBTs

X. Zhou, M. Fukui, K. Takeuchi, *Member, IEEE*, T. Saraya, *Member, IEEE*, and T. Hiramoto *Member, IEEE*

Abstract— Systematic comparison of dynamic performance has been made among 3300V scaled IGBTs with scaling factor (k) from 1 to 10 by TCAD simulations. The results from a new evaluation method demonstrate superior turn-off dV/dt controllability in scaled IGBTs, regardless of stronger Injection Enhancement (IE) effect. On the basis of physical reason analysis, including the extraction of extra energy and charge quantity generated from impact ionization, it's convinced that Dynamic Avalanche (DA) is suppressed in scaled IGBTs successfully. Thus IGBT scaling method is proven to be able to break through the trade-off relationships between lower on-state voltage drop and better switching controllability, also lower switching power loss.

*Index Terms*— IGBT, scaling, TCAD simulation, dynamic avalanche, switching controllability

## I. INTRODUCTION

The concept of IGBT scaling, where all the geometrical dimensions in MOS parts as well as gate voltage are scaled down proportionately, has been proposed to enhance the IGBT performances [1]-[2]. We have successfully fabricated scaled IGBTs and demonstrated better  $E_{off}$ - $V_{ce,sat}$  trade-off relationship in scaled IGBTs [3]-[5], where  $E_{off}$  is turn-off loss and  $V_{ce,sat}$  is on-state voltage. The studies from more various aspects of scaled IGBTs have continued to go deeper to achieving real application [6]-[7].

On the other hand, the dynamic avalanche (DA), which happens locally at lower reverse bias than static breakdown voltage, poses fundamental performance limits and reliability concerns on conventional IGBTs [8]-[9]. The major negative influence of DA to device performance, higher switching power loss and worse controllability, has been emphasized from previous works [10]-[13]. Several physical models based on physical analysis of DA during the turn-off process have enabled people to evaluate quantitatively and figure out ways to refrain from DA [14]-[19]. Some fairly novel device structures have been proposed and claimed to be able to stop suffering from DA [20]-[23].

As easily predicted, DA was projected to be more severe in scaled IGBTs because of higher carrier density by the IE effect, which may lead to dV/dt controllability degradation and

This work was supported by JST SPRING, Grant Number JPMJSP2108.

reliability problems because of more transient carriers during the turn-off process. Hopefully, the scaling method was reported to be an effective way to stretch the all-round performance of IGBT [24]-[25], while more detailed physical analysis applied to the trench gate IGBT is mandatory.

In this paper, a new method of extracting dV/dt controllability has been proposed and applied to comparison of DA among scaled trench IGBTs. Systemic analysis is performed to authenticate the advantages of scaling methods in IGBT from various aspects. This paper is an extended version of a conference presentation [25] and will more thoroughly describe the simulation results and discussion.

## II. DEVICE STRUCTURE AND IE EFFECT

Table 1. Structural and electrical parameters of original and scaled trench gate IGBTs.

| Parameters                                                                                                                                                                                                | k=1             | k=3                           | k=5     | k=10 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------|---------|------|

| Cell pitch, W (um)                                                                                                                                                                                        | 16              | 16                            | 16      | 16   |

| Mesa width, S (um)                                                                                                                                                                                        | 3               | 1                             | 0.6     | 0.3  |

| Trench depth, D <sub>T</sub> (um)                                                                                                                                                                         | 6               | 2                             | 1.2     | 0.6  |

| P-base depth, D <sub>P</sub> (um)                                                                                                                                                                         | 3               | 1                             | 0.6     | 0.3  |

| Trench extrusion, $D_T - D_P(um)$                                                                                                                                                                         | 3               | 1                             | 0.6     | 0.3  |

| Gate oxide thickness, $t_{ox}$ (nm)                                                                                                                                                                       | 100             | 33.3                          | 20      | 10   |

| Gate voltage, $V_g(V)$                                                                                                                                                                                    | 15              | 5                             | 3       | 1.5  |

| Threshold Voltage, V <sub>th</sub> (V)                                                                                                                                                                    | 6               | 2                             | 1.2     | 0.6  |

| Trench width, W <sub>T</sub> (um)                                                                                                                                                                         | 1               | 0.33                          | 0.20    | 0.10 |

| Thickness, t <sub>Si</sub> (um)                                                                                                                                                                           | 360             | 360                           | 360     | 360  |

| S/2 W <sub>T</sub><br>Entter<br>D <sub>P</sub> -base<br>D <sub>T</sub> -D <sub>P</sub><br>U <sub>T</sub> -D <sub>P</sub><br>U <sub>T</sub><br>D <sub>T</sub> -D <sub>P</sub><br>U <sub>T</sub><br>P-float | R <sub>pf</sub> | r-Dif<br>k t <sub>ox</sub> /k | P-float |      |

Half cell picth, W/2

Fig. 1. Schematic cross section of original and scaled trench gate IGBTs.

Corresponding author: Xiang Zhou (e-mail: zhou-xiang996@g.ecc.u-tokyo.ac.jp)

Thic

Half cell picth, W/2

Xiang Zhou, Munetoshi Fukui, Kiyoshi Takeuchi, Takuya Saraya, and Toshiro Hiramoto are with the Institute of Industrial Science, The University of Tokyo, Meguro-ku, Tokyo 153-8505, Japan

JEDS-2023-08-0208-SI

As demonstrated in Fig. 1, a full scaling method has been applied to the top cell region in 3300V IGBT with scaling factor k=1, 3, 5, 10. Structural and electrical parameters of reference (k=1) and scaled (k=3, 5, 10) IGBTs are summarized in Table 1. Corresponding device structures were generated in TCAD simulation tool for further study. It's worth mentioning that the p-float region in Fig. 1 was connected to ground through an adjustable resistor  $R_{pf}$ . The baseline doping concentration and thickness of the P-collector region were  $8.0 \times 10^{17} \text{cm}^{-3}$  and  $0.4 \mu \text{m}$  that kept invariable in scaled IGBTs. A typical inductive load circuit was used to evaluate turn-off performance, with default operating voltage of 1700V (V<sub>cc</sub>) and gate voltage source swing of  $\pm V_g$ . The active area of IGBT was  $0.2 \text{cm}^2$  with on-state current of 16A (80A/cm<sup>2</sup>).

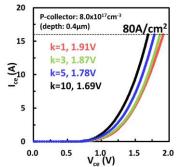

Fig. 2. On-state characteristics of k=1, k=3, k=5 and k=10 IGBTs.

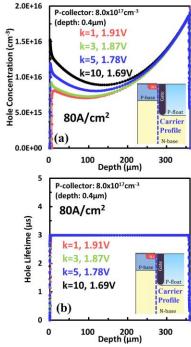

Fig. 3. (a) Holes carrier profile and (b) holes lifetime profile of k=1, k=3, k=5 and k=10 IGBTs along channel region under current density  $80A/cm^2$ .

First, the static performance advantages of scaled IGBT are reviewed. In Fig. 2, the output characteristics of original and scaled IGBTs are overlapped to show the difference. It's obvious that on-state voltage drop  $V_{ce,sat}$  has been improved from 1.91V to 1.69V from k=1 to k=10 devices in spite of scaling gate voltage. The lower on-state voltage drop mostly comes from higher carrier density in the n-base region of the emitter side, see Fig. 3(a). This improvement is thanks to stronger IE effect, a well-known benefit from scaling principle in IGBT. In Fig. 3(b), holes carrier lifetime is also compared among original and scaled IGBTs. As defined by the default physical model of silicon, the holes carrier lifetime is about  $3\mu$ s in all devices. Whereas higher carrier density at emitter side hinders the expansion of space charge region, also increases the transient carrier density in space charge region during turn-off. As a result, a steeper electric field profile with higher maximum value forms under the same switching condition. It becomes reasonable to assume that DA is prone to happen in scaled IGBTs and degrades dynamic performance.

## III. COMPARISON OF DV/DT CONTROLLABILITY

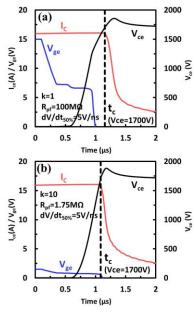

The detailed trigger mechanism of DA during turn-off has to be discussed first. A typical switching waveform of k=1 device with gate resistance Rg=72.5 $\Omega$  is shown in Fig. 4(a), where electron (I<sub>E-e</sub>) and hole current (I<sub>E-h</sub>) parts of the emitter electrode are also included. Benefits from the convenience of simulation tools, the hole and electron current parts of each electrode can be plotted separately to facilitate analysis. At time t<sub>2</sub>, when V<sub>ge</sub> reduces to be equal to threshold voltage V<sub>th</sub>, electron current I<sub>E-e</sub> is shut down by MOS gate and hole current I<sub>E-h</sub> jumps to 100% I<sub>C</sub>. The Eq.(1) shows magnitude of electric field E(t) revolution as function of charge density and space charge region width W<sub>SC</sub>(t).

Fig. 4. (a) A typical turn-off waveforms of k=1 IGBT at dV/dt<sub>50%</sub>= 5V/ns and Rg= 72.5 $\Omega$  and (b) emitter hole current of k=1 IGBT at various Rg.

Where  $J_{E-e}$  is electron current density and  $J_{E-h}$  is hole current density. From Eq.(1), we know that the sudden increase of hole/electron current ratio lifts the maximum electric field in the space charge region substantially. After that, the DA happens (gray area), and it generates electron/hole pairs and stabilizes the electric field peak value. Besides, the slope of  $V_{ce}$  (dV/dt) is reduced because of the stabilized peak electric

field value and slower expansion of space charge region because of generated carriers from impact ionization. As a natural result, the total switching power loss also goes higher when DA happens.

It's a common measure to relieve DA under slower switching speed by increasing Rg. It is found that the peak emitter hole current ratio is reduced under slower switching conditions with larger Rg, as the blue lines shown in Fig. 4(b). Under slower switching conditions, the time point that  $V_{ge}$  reduces to  $V_{th}$  is after the time point that I<sub>C</sub> starts to fall. This makes the hole current peak lower than 100% I<sub>C</sub> and thus suppresses DA significantly. Therefore, a necessary and sufficient condition to avoid DA is that  $V_{ge}$  reaches  $V_{th}$  after I<sub>C</sub> starts to fall. From the other side, the hole current peak becomes equal to 100% I<sub>C</sub> can be taken as a distinguishing feature of whether DA happens.

Now, we start to discuss the controllability of dV/dt. It is indicated previously that DA limits the switching speed as well as controllable range of dV/dt. Then, a judging method is needed for dV/dt controllability comparison. A new method of judging device turn-off controllability by extracting critical dV/dt values will be introduced here. But before that, some essential parameters need to be introduced in Fig. 4(a). Turnoff energy loss of voltage rising part ( $E_{off-VR}$ ) is calculated by integration of I<sub>C</sub> and V<sub>ce</sub> up to t<sub>3</sub> (when V<sub>ce</sub>=V<sub>cc</sub>). Two dV/dt values are calculated as the slopes of V<sub>ce</sub> at 50% V<sub>cc</sub> (dV/dt<sub>50%</sub>) and 90% V<sub>cc</sub> (dV/dt<sub>90%</sub>). Hole current ratio is calculated as the ratio between the peak hole current value and the maximum I<sub>C</sub>.

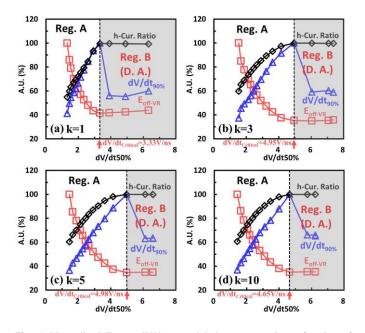

Fig. 5. Normalized  $E_{off\cdot VR}$ ,  $dV/dt_{90\%}$ , and hole current ratio as function of  $dV/dt_{50\%}$  of (a) k=1, (b) k=3, (c) k=5 and (d) k=10 IGBTs.

Those aforementioned parameters of k=1, 3, 5, 10 devices are normalized to their maximum values and plotted as a function of dV/dt<sub>50%</sub> in Fig. 5, where dV/dt<sub>50%</sub> was adjusted by varying Rg. Those four graphs are split into two regions A and B with clear boundaries, where region B is dominated by DA. At the boundary of region A/B, saturation of  $E_{off-VR}$ , saturation of hole current ratio, and drop of dV/dt<sub>90%</sub> occur at same  $dV/dt_{50\%}$  value, where strong DA happens and influences the turn-off waveform intensely which should be avoided. The  $dV/dt_{50\%}$  value at the boundary is defined as  $dV/dt_{Critical}$ . Higher  $dV/dt_{Critical}$  value represents larger controllable dV/dt range during turn-off that is beneficial for high-frequency applications. Surprisingly, better dV/dt controllability in scaled IGBTs than k=1 case is demonstrated from simulation results and it also indicates that DA is suppressed in scaled IGBTs.

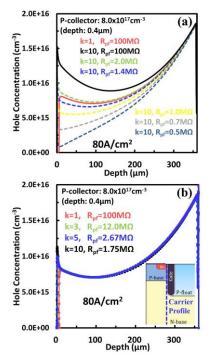

Fig. 6. (a) Holes carrier profile of k=10 IGBT under different  $R_{pf}$  resistance conditions compared to k=1 case; (b) holes carrier profile of k=1, k=3, k=5 and k=10 IGBTs under equivalent IE effect condition after  $R_{pf}$  adjustment.

Fig. 7. Comparison of (a)  $dV/dt_{Critcal}$  and  $V_{ce,sat}$ ; (b)  $E_{off-VR}$  and  $V_{ce,sat}$  as function of scaling factor k under equivalent IE effect condition after adjusted by  $R_{pf}$ .

4

Nevertheless, the change of dV/dt<sub>Critical</sub> value is not monotonous from k=1 to k=10 devices. It's speculated that the stronger IE effect in scaled IGBT makes the results complicated to analyze. Hence, it would be ideal to eliminate the influence of the stronger IE effect in scaled IGBTs and make the circumstance simpler. As a common method in real IGBT device design, p-float region connecting resistor  $R_{pf}$  value is used to optimize device performance. It's also found out that different R<sub>pf</sub> values yield different hole concentration at the emitter side. As Fig. 6(a) shows, the adjustment of  $R_{pf}$  value can tune the carrier profile at the emitter side in k=10 IGBT, where the k=1 case is added for reference. Under on-state, the p-float region is another path besides p-base region for holes that are injected from the collector side to go out. Controlling the hole current flows through the p-float region by Rpf resistance, the holes density at the emitter side is able to be tuned. Which also means that the strength of IE effect can also be adjusted by R<sub>pf</sub> resistance value. To get rid of the influence of stronger IE effect in scaled IGBTs, R<sub>pf</sub> resistance has been adjusted to align carrier profiles of scaled IGBTs with k=1 case, as Fig. 6(b) shows. We call this "equivalent IE effect condition". Compared with the original carrier profile in Fig. 3(a), the carrier profile under equivalent IE effect condition is almost overlapped.

The dV/dt<sub>Critical</sub> values under the equivalent IE effect condition are extracted and plotted as a function of k in Fig. 7(a), where  $V_{ce,sat}$  is also added for comparison. Under this new circumstance (equivalent IE effect condition), dV/dt<sub>Critical</sub> values are improved monotonously with higher scaling factor from 1 to 10, which demonstrates wider controllable dV/dt range. Moreover, even under the equivalent IE effect condition after R<sub>pf</sub> is adjusted, slightly better on-state voltage drop is still shown in scaled IGBTs. Since the influence of IE effect on V<sub>ce,sat</sub> has been removed here which is reflected in the similar carrier profile in drift region. The lower V<sub>ce,sat</sub> is speculated to benefit from the smaller resistance of MOS channel and mesa parts in scaled IGBTs. Moreover, the power loss Eoff-VR is demonstrated to be lower in scaled IGBTs, as shown in Fig. 7(b). Those indisputable results indicate that scaled IGBTs can enjoy lower V<sub>ce,sat</sub>, higher dV/dt<sub>Critical</sub>, lower E<sub>off-VR</sub> at same time. The following discussion is all built on equivalent IE effect condition.

# IV. PHYSICAL REASON AND MORE EVIDENCE

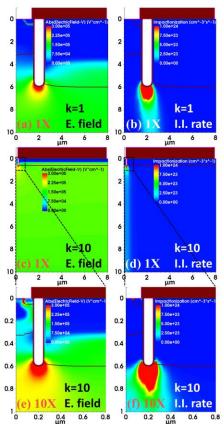

Here, the physical reason behind the suppression of DA in scaled IGBT needs to be discussed. For fair comparison, the physical parameters inside the device should be compared under identical switching condition. The switching wavforms of k=1 and k=10 devices under  $dV/dt_{50\%}=5V/ns$  have been shown in Fig. 8. The dash line marks the capture time point (t<sub>c</sub>) when V<sub>ce</sub> equals to 1700V. In Fig. 9, the 2D graphs show distribution of electric field and impact ionization rate of k=1 and k=10 devices at the same reverse bias (V<sub>ce</sub>= 1700V) and under the same switching conditions ( $dV/dt_{50\%}=5V/ns$ ) as demonstrated in Fig. 8. It's pretty clear that the high electric field and impact ionization rate regions are localized in the neighborhood of trench bottom in k=1 case as shown in Fig. 9(a)-(b), which stems from electric field crowding effect in

cylindrical geometry. Whereas in Fig. 9(c)-(d), the k=10 case, the high impact ionization as well as high electric field regions are hardly to be seen under the same scale. It has to be zoomed in to show the detailed information of k=10 case in Fig. 9(e)-(f). So it's found that DA is limited in an almost 10 times smaller area, compared to k=1 case. In other words, DA is confined to be more localized in scaled IGBTs.

Fig. 8. (a) Turn-off waveforms of k=1 IGBT and (b) k=10 IGBT after  $R_{\rm pf}$  adjustment, where the dash line  $(t_c)$  marks the time point that physical parameters are captured.

Fig. 9. Demonstration of 2D electric field and impact ionization rate of k=1 and k=10 IGBTs when  $V_{ce}$  equals to 1700V under  $dV/dt_{50\%}=5V/ns$ .

## JEDS-2023-08-0208-SI

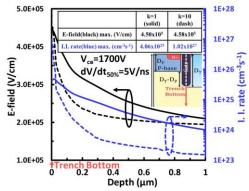

For further comparison, the magnitude of electric field and impact ionization rate along the trench middle line is plotted as a 1D graph in Fig. 10. Although it's seen that the maximum values of both magnitude of electric field and impact ionization rate are higher in scaled IGBT. However, higher maximum values of electric field and impact ionization rate are not equivalent to worse severity of DA. It's more worthwhile to notice that the electric field and impact ionization rate decay more rapidly with distance from trench bottom in the scaled IGBT case. This phenomenon may be attributed to the better electric field uniformity that originates from a smaller mesa region. According to the impact ionization integral, an adequate distance of high enough electric field is essential for avalanche breakdown to happen. In other words, the electric field has to go higher if the space range for impact ionization is limited, just like the scaled IGBT case. As a result, thanks to better electric field uniformity, the condition for DA to happen becomes more stringent in scaled IGBT.

Fig. 10. Comparison of 1D electric field and impact ionization rate between k=1 and k=10 IGBTs along trench middle line when  $V_{ce}$  equals to 1700V under  $dV/dt_{50\%}$ =5V/ns condition.

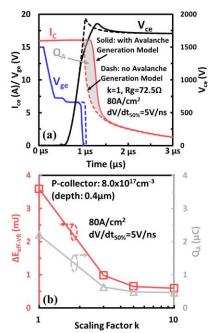

Fig. 11. (a) Comparison of switching waveforms of k=1 IGBT between with avalanche generation model and without avalanche generation model at  $dV/dt_{50\%}$ = 5V/ns and Rg= 72.5 $\Omega$ ; (b) change of  $\Delta E_{off-VR}$  and Q<sub>A</sub> as function of scaling factor k.

With the convenience of TCAD simulation, we are able to extract the quantity of extra charges  $(O_A)$  and extra energy loss  $(\Delta E_{off-VR})$  generated by DA by enabling or disabling the avalanche generation model in the simulation tool. An example comparison of the switching waveforms of k=1 case with and without avalanche generation model is demonstrated in Fig. 11(a). The  $Q_A$  (the gray area between two  $I_C$  curves) is calculated by the difference of two integrals of I<sub>C</sub> curves over time. The  $\Delta E_{off-VR}$  is just the difference of voltage rising part energy loss calculations of two cases. The  $Q_A$  and  $\Delta E_{off-}$ VR values are plotted as a function of scaling factor k in Fig. 11(b). There is no doubt that DA is mitigated in scaled IGBTs since both  $Q_A$  and  $\Delta E_{off-VR}$  values become lower with scaling factor k under the same switching condition. It is persuasive that  $Q_A$  and  $\Delta E_{off-VR}$  are more significant parameters than maximum values of electric field or impact ionization rate to evaluate the severity of DA during turn-off.

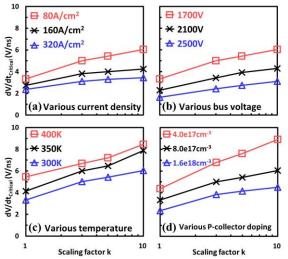

Fig. 12. Comparison of  $dV/dt_{Critcal}$  at various (a) on-state current density; (b) bus voltage; (c) ambient temperature and (d) P-collector doping concentration as function of scaling factor k under equivalent IE effect condition after adjusted by  $R_{pf}$ .

Fig. 13. Comparison of trade-off relationships between (a) dV/dt<sub>Critcal</sub> vs. V<sub>ce,sat</sub>; (b) E<sub>off-VR</sub> vs. V<sub>ce,sat</sub> as function of scaling factor k under equivalent IE effect condition after adjusted by R<sub>pf</sub>. The p-collector doping concentration assumed is  $1.6 \times 10^{18} \text{cm}^{-3}$ ,  $8.0 \times 10^{17} \text{cm}^{-3}$ , and  $4.0 \times 10^{17} \text{cm}^{-3}$ .

This article has been accepted for publication in IEEE Journal of the Electron Devices Society. This is the author's version which has not been fully edited and content may change prior to final publication. Citation information: DOI 10.1109/JEDS.2023.3342869

JEDS-2023-08-0208-SI

In this part, dV/dt<sub>Critical</sub> values are compared among scaled IGBTs as function of scaling factor under various switching conditions. In common sense, DA is easier to happen if the turnoff current density goes higher. That is because the higher density of transient carriers in space charge region increases the impact ionization rate. This point has been proven in Fig. 12(a). But even at higher on-state current density 160A/cm<sup>2</sup> and 320A/cm<sup>2</sup>, the relation that dV/dt<sub>Critical</sub> value increases with higher scaling factor k still holds. On the other hand, dV/dt<sub>Critical</sub> values have been proven to improve in scaled IGBTs even at higher bus voltage 2100V and 2500V in Fig. 12(b). It's supposed that DA is suppressed under higher ambient temperature owing to the lower impact ionization coefficients. Our results in Fig. 12(c) are consistent with this point and demonstrate even greater improvement of dV/dt controllability of scaled IGBTs at higher temperature conditions. Finally, pcollector doping concentration was also modified in simulation to see the difference in Fig. 12(d). At lower doping concentration design of p-collector or faster switching mode IGBT, scaled IGBT reveals further wider controllable dV/dt range during device turn-off. There is enough evidence to assert that scaled IGBT is profitable for higher switching speed applications.

Furthermore, the dV/dt<sub>Critical</sub> and E<sub>off-VR</sub> values are analyzed as function of on-state voltage drop (various p-collector doping concentration) for IGBTs with different scaling factor k in Fig. 13. Please notice that higher doping concentration corresponds to lower V<sub>ce,sat</sub>. It's explicit that with larger scaling factor k, higher  $dV/dt_{Critical}$  and lower  $E_{off-VR}$  values can be realized at the same V<sub>ce,sat</sub> value. In other ways, scaling method in IGBT is able to break through the trade-off relationships between lower on-state voltage drop (V<sub>ce,sat</sub>) and better switching controllability (dV/dt<sub>Critical</sub>), also lower on-state voltage drop (V<sub>ce,sat</sub>) and lower switching power loss (E<sub>off-VR</sub>). Summarizing the above discussion, it is speculated that dV/dt<sub>Critical</sub> in scaled IGBTs may be worsened by higher carrier density at the emitter side by the IE effect, while at same time, dV/dt<sub>Critical</sub> is improved by better electric field uniformity originating from a smaller dimension of the mesa region. So far, all results under equivalent IE effect condition validate that the superior turn-off dV/dt controllability and also lower switching power loss since the successful suppression of DA in scaled IGBTs.

## V. CONCLUSION

After comprehensive analysis based on a new evaluation method, scaled IGBT is believed to benefit from superior dV/dt controllability during turn-off thanks to the suppression of DA. The physical analysis tells us that the prominent improvement of electric field uniformity is capable of mitigating DA in scaled IGBT structure, which is also adequate to compensate for the influence of higher carrier density from stronger IE effect. Finally, with the help of adjustable  $R_{pf}$  approach, scaling method in IGBTs is concluded to be able to enjoy lower  $V_{ce,sat}$  by stronger IE effect and better turn-off dV/dt controllability, also lower switching power loss simultaneously.

#### REFERENCES

[1] M. Tanaka and I. Omura, "Scaling rule for very shallow trench IGBT toward CMOS process compatibility," 2012 24th International Symposium on Power Semiconductor Devices and ICs, Bruges, Belgium, 2012, pp. 177-180, doi: 10.1109/ISPSD.2012.6229052.

[2] M. Tanaka and I. Omura, "IGBT scaling principle toward CMOS compatible wafer processes," in *Solid-State Electronics*, vol. 80, pp. 118–123, Feb. 2013, doi: 10.1016/j.sse.2012.10.020.

[3] K. Kakushima, T. Hoshii, K. Tsutsui, A. Nakajima, S. Nishizawa, H. Wakabayashi, I. Muneta, K. Sato, T. Matsudai, W. Saito, T. Saraya, K. Itou, M. Fukui, S. Suzuki, M. Kobayashi, T. Takakura, T. Hiramoto, A. Ogura, Y. Numasawa, I. Omura, H. Ohashi, and H. Iwai, "Experimental verification of a 3D scaling principle for low Vce(sat) IGBT," 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2016, pp. 10.6.1-10.6.4, doi: 10.1109/IEDM.2016.7838390.

[4] T. Saraya, K. Itou, T. Takakura, M. Fukui, S. Suzuki, K. Takeuchi, M. Tsukuda, Y. Numasawa, K. Satoh, T. Matsudai, W. Saito, K. Kakushima, T. Hoshii, K. Furukawa, M. Watanabe, N. Shigyo, K. Tsutsui, H. Iwai, A. Ogura, S. Nishizawa, I. Omura, H. Ohashi, and T. Hiramoto, "Demonstration of 1200V scaled IGBTs driven by 5V gate voltage with superiorly low switching loss," 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2018, pp. 8.4.1-8.4.4, doi: 10.1109/IEDM.2018.8614491.

[5] T. Saraya, K. Itou, T. Takakura, M. Fukui, S. Suzuki, K. Takeuchi, M. Tsukuda, Y. Numasawa, K. Satoh, T. Matsudai, W. Saito, K. Kakushima, T. Hoshii, K. Furukawa, M. Watanabe, N. Shigyo, H. Wakabayashi, K. Tsutsui, H. Iwai, A. Ogura, S. Nishizawa, I. Omura, H. Ohashi, and T. Hiramoto, "3300V scaled IGBTs driven by 5V gate voltage," 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 2019, pp. 43-46, doi: 10.1109/ISPSD.2019.8757626.

[6] I. Imperiale, R. Baburske, T. Arnold, A. Philippou, E. Griebl, F. Wolter, H.-J. Thees, A. Mauder, F.-J. Niedernostheide and C. Sandow, "Opportunities and challenges of a 1200 V IGBT for 5 V gate voltage operation," 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 2020, pp. 505-508, doi: 10.1109/ISPSD46842.2020.9170076.

[7] K. Nishi, C. Ze, K. Tanaka, K. Eguchi, T. Miyazaki and A. Furukawa, "Selfturn-on-free 1200V scaled CSTBT<sup>™</sup> driven by 5V gate voltage with wide SOA," 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 2021, pp. 23-26, doi: 10.23919/ISPSD50666.2021.9452212.

[8] P. Lefranc, D. Planson, H. Morel and D. Bergogne, "Analysis of the dynamic avalanche of punch through insulated gate bipolar transistor (PT-IGBT)," in *Solid-State Electronics*, vol. 53, no. 9, pp. 944-954, Sept. 2009, doi: 10.1016/j.sse.2009.06.009.

[9] J. Lutz and R. Baburske, "Dynamic avalanche in bipolar power devices," in *Microelectronics Reliability*, vol. 52, no. 3, pp. 475-481, Mar. 2012, doi: 10.1016/j.microrel.2011.10.018.

[10] Y. Onozawa, M. Otsuki and Y. Seki, "Investigation of carrier streaming effect for the low spike fast IGBT turn-off," 2006 IEEE International Symposium on Power Semiconductor Devices and IC's (ISPSD), Naples, Italy, 2006, pp. 1-4, doi: 10.1109/ISPSD.2006.1666099.

[11] M. Tsukuda, I. Omura, Y. Sakiyama, M. Yamaguchi, K. Matsushita and T. Ogura, "Critical IGBT design regarding EMI and switching losses," 2008 20th International Symposium on Power Semiconductor Devices and IC's (ISPSD), Orlando, FL, USA, 2008, pp. 185-188, doi: 10.1109/ISPSD.2008.4538929.

[12] S. Machida, K. Ito and Y. Yamashita, "Micro dynamic avalanche phenomenon during turn-off in Silicon insulated gate bipolar transistors," in *Japanese Journal of Applied Physics*, vol. 53, no. 4S, pp. 04EP01-05, Feb. 2014, doi: 10.7567/JJAP.53.04EP01.

[13] S. Machida, K. Ito and Y. Yamashita, "Approaching the limit of switching loss reduction in Si-IGBTs," 2014 IEEE 26th International Symposium on

## JEDS-2023-08-0208-SI

*Power Semiconductor Devices & IC's (ISPSD)*, Waikoloa, HI, USA, 2014, pp. 107-110, doi: 10.1109/ISPSD.2014.6855987.

[14] T. Ogura, H. Ninomiya, K. Sugiyama and T. Inoue, "Turn-off switching analysis considering dynamic avalanche effect for low turn-off loss high-voltage IGBTs," in *IEEE Transactions on Electron Devices*, vol. 51, no. 4, pp. 629-635, April 2004, doi: 10.1109/TED.2004.825109.

[15] J. Takaishi, S. Harada, M. Tsukuda and I. Omura, "Structure oriented compact model for advanced trench IGBTs without fitting parameters for extreme condition: Part II," in *Microelectronics Reliability*, vol. 54, no. 9, pp. 1891-1896, Sept. 2014, doi: 10.1016/j.microrel.2014.07.158.

[16] T. Ma, Y. Jia and Y. Luo, "Physical model of FS-IGBT considering dynamic avalanche electrical characteristics and analysis of chip non-uniform stress," 2020 IEEE International Conference on Information Technology, Big Data and Artificial Intelligence (ICIBA), Chongqing, China, 2020, pp. 640-644, doi: 10.1109/ICIBA50161.2020.9277207.

[17] Wuhua Yang, Cailin Wang, Jing Yang, Qi Zhang and Ruliang Zhang, "Analytical model for dynamic avalanche onset of planar IGBTs," in *Microelectronics Reliability*, vol. 115, pp. 113958-113964, Dec. 2020, doi: 10.1016/j.microrel.2020.113958.

[18] A. Bryant, S. Yang, P. Mawby, D. Xiang, L. Ran, P. Tavner, and P. R. Palmer, "Investigation into IGBT dV/dt during turn-Off and its temperature dependence," in *IEEE Transactions on Power Electronics*, vol. 26, no. 10, pp. 3019-3031, Oct. 2011, doi: 10.1109/TPEL.2011.2125803.

[19] S. Geissmann, L. De Michielis, Ch. Corvasce, M. Rahimo and M. Andenna, "Extraction of dynamic avalanche during IGBT turn off," in *Microelectronics Reliability*, vol. 76, pp. 495–499, Sept. 2017, doi: 10.1016/j.microrel.2017.08.008.

[20] P. Luo, S. N. Ekkanath Madathil, S. -i. Nishizawa and W. Saito, "Dynamic avalanche free design in 1.2kV Si-IGBTs for ultra high current density operation," *2019 IEEE International Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, 2019, pp. 12.3.1-12.3.4, doi: 10.1109/IEDM19573.2019.8993596.

[21] P. Luo, S. N. E. Madathil, S. -I. Nishizawa and W. Saito, "Evaluation of dynamic avalanche performance in 1.2-kV MOS-bipolar devices," in *IEEE Transactions on Electron Devices*, vol. 67, no. 9, pp. 3691-3697, Sept. 2020, doi: 10.1109/TED.2020.3007594.

[22] W. Saito and S. -i. Nishizawa, "High switching controllability trench gate design in Si-IGBTs," 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 2020, pp. 447-450, doi: 10.1109/ISPSD46842.2020.9170118.

[23] W. Saito and S. -I. Nishizawa, "Alternated trench-gate IGBT for low loss and suppressing negative gate capacitance," in *IEEE Transactions on Electron Devices*, vol. 67, no. 8, pp. 3285-3290, Aug. 2020, doi: 10.1109/TED.2020.3002510.

[24] M. Fukui, T. Saraya, K. Itou, T. Takakura, S. Suzuki, K. Takeuchi, K. Kakushima, T. Hoshii, K. Tsutsui, H. Iwai, S. Nishizawa, I. Omura and T. Hiramoto, "Turn-off loss improvement by IGBT scaling," 2019 51st International Conference on Solid State Devices and Materials (SSDM), Nagoya, Japan, 2019, pp. 453-454, doi: 10.7567/SSDM.2019.PS-4-01.

[25] X. Zhou, M. Fukui, K. Takeuchi, T. Saraya and T. Hiramoto, "Suppressed dynamic avalanche and enhanced turn-off dV/dt controllability in 3300V scaled IGBTs," 2023 7th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Seoul, Republic of Korea, 2023, pp. 1-3, doi: 10.1109/EDTM55494.2023.10103121.