Received 24 October 2023; accepted 26 November 2023. Date of publication 29 November 2023; date of current version 29 January 2024.

The review of this article was arranged by Editor M.-D. Ker

Digital Object Identifier 10.1109/JEDS.2023.3337341

# Design and Simulation Optimization of an Ultra-Low Specific On-Resistance LDMOS Device

SHAOXIN YU<sup>1,2</sup>, WEIHENG SHAO<sup>1</sup> (Member, IEEE), RONGSHENG CHEN<sup>1</sup>, RILIN ZHANG<sup>2</sup>, XIAOOING LIU<sup>1,2</sup>, YONGJUN WU<sup>2</sup>, AND BIN ZHAO<sup>2</sup>

1 School of Microelectronics, South China University of Technology, Guangzhou 510641, China 2 CanSemi Technology Inc., Guangzhou 510535, China

CORRESPONDING AUTHORS: R. CHEN AND B. ZHAO (e-mail: chenrs@scut.edu.cn; jeff.zhao@cansemitech.com)

This work was supported by the Key Area Research and Development Program of Guangdong Province under Grant 2021B0101280001 and Grant 2022B0101180001.

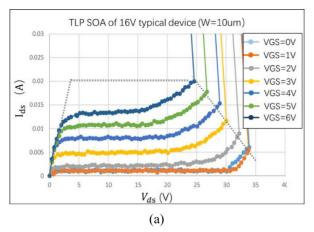

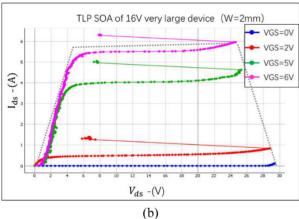

**ABSTRACT** The design of LDMOS (Lateral double diffused metal oxide semiconductor) devices with CFP (Contact field plate) has been of great significance in recent years, according to its advantages of low resistance and high switch efficiency. In this paper, this ultra-low  $R_{\text{on,sp}}$  (Specific on-resistance) LDMOS device is simulated, designed, and fabricated. The effects on FOM (Figures-of-merits) characters from physical dimensions, including field plate length L, field plate thickness H, and slot contact width W, have been analyzed and discussed. The best device structure is proposed through simulation, and a related fabrication process is introduced correspondingly. Finally, the electrical measurement results show that  $R_{\text{on,sp}}$  can achieve as low as  $6.9 \text{m}\Omega \cdot \text{mm}^2$  when the source-drain BV(Breakdown voltage) arrives at 34.1V, which is improved by 47.1% compared with conventional devices. Furthermore, the TLP (Transmission line pulse) test results indicate that the device owns an ideal SOA (Safe operation area) from both typical devices (W =  $10 \mu \text{m}$ ) and very large devices (W = 2 mm).

**INDEX TERMS** Contact field plate (CFP), figures of merits (FOM), lateral double diffusion metal oxide semiconductor (LDMOS), specific on-resistance ( $R_{on,sp}$ ).

## I. INTRODUCTION

Recently, BCD (Bipolar-CMOS-DMOS) circuits based on LDMOS (Lateral double diffusion metal oxide semiconductor) devices have been widely applied in PMICs (Power management integrated), IoT (Internet of Things), AI (Artificial intelligence), and automotive owing to its advantages of high speed and easy integration [1], [2], [3]. In the device structure design and process integration of LDMOS, field plate technology is the most critical technology widely used for source-drain *BV* (Breakdown voltage) improvement [4], [5], [6]. An appropriate field plate structure could produce a uniform distribution of the electric field in the drift region by reducing the surface peak electric field and increasing the lateral electric field, thereby increasing the device's *BV*.

At present, the field plate commonly used in the IC (Integrated circuit) manufacturing industry are two structures: mini-STI (Shallow trench isolation) field plate and

mini-LOCOS (Local oxidation of silicon) field plate [6], [7]. Many new researchers have been published [8], [9], [10], [11], [12], and they focus on optimizing and innovating field plate structures in LDMOS devices. These novel field plate structures indeed bring a significant improvement in device FOM (Figures of merits) performance to a certain degree. However, among all these structures, poly gates have to land on the gate oxide and field plate oxide meanwhile. This inherent feature inevitably causes a higher gate-drain parasitic capacitance  $C_{GD}$ , then results in lower switching efficiency and higher  $R_{on,sp}$  (Specific on-resistance).

For further improvement, an optimized LDMOS device named CFP (Contact field plate) is introduced [13], [14]. In this structure, gate oxide bias and field oxide bias are separated completely. Thus, it yields a lower  $R_{\text{on,sp}}$  and higher switch efficiency. However, this novel device's electrical performance and process fabrication are still under continuous study [15], and related published results are

currently insufficient. Therefore, research works on CFP LDMOS devices are still of great practical significance for our semiconductor IC industry.

#### **II. STRUCTURES AND ANALYSIS**

## A. STRUCTURE DESCRIPTION

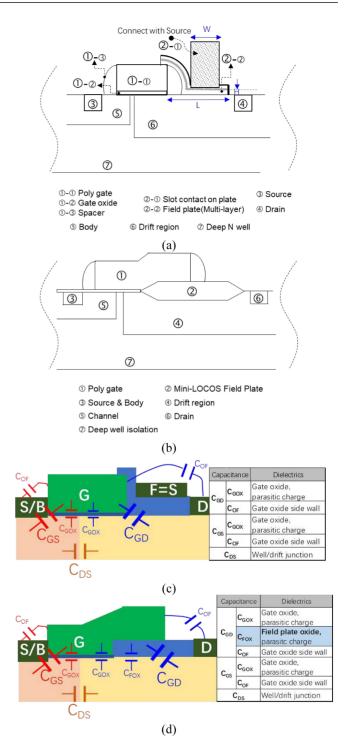

Fig. 1(a) illustrates the basic schematic of CFP LDMOS devices and Fig. 1(b) is the conventional schematic for comparison. From bottom to top, there are:

- (1) Deep N well ⑦: High energy implant and the high-temperature drive in for device full isolation;

- (2) Drift region 6;

- (3) Body region 5;

- (4) Drain terminal 4;

- (5) Source terminal 3;

- (6) Gate terminal ①: include ploy gate ①-①, gate oxide ①-②, and oxide-nitride spacer ①-③ in both sides of poly gate;

- (7) Contact field plate ②: consisting of slot contact ②-① and field plate dielectric layer ②-②. The field plate dielectric layer ②-② is composed of a multi-layer of  $SiO_2$ ,  $Si_3N_4$ , and  $SiO_2$ . The slot contact ②-① passes through the top  $SiO_2$  layer, then penetrates and lands on the middle  $Si_3N_4$  layer. The authors define field plate length as L, contact width as W, and effective thickness (bottom oxide combined  $100\text{\AA}$  remaining  $Si_3N_4$  that post etching) as H.

In which, contact field plate terminal ②-① connects with source terminal ③ via the metal layers. Thus, the CFP device is still considered as a four-terminal device.

Fig. 1(c) and (d) illustrate respectively the CFP LDMOS and conventional LDMOS [16], [17] device's static intrinsic capacitances [18], [19], which is consisting of the gate-to-source capacitance  $C_{GS}$ , the gate-to-drain capacitance  $C_{GD}$  and the drain-to-source capacitance  $C_{DS}$ . In which,  $C_{GS}$  and  $C_{GD}$  are all consisting with oxide capacitance  $C_{GOX}/C_{FOX}$  and gate side wall capacitance  $C_{OF}$ . The capacitance between the field plate electrode and the drift region is not considered since the field plate electrode connects with the source electrode through the metal lines.

## **B. CAPACITANCE & SWITCHING EFFICIENCY**

Higher dynamic performance is required for LDMOS device design and the transit frequency  $f_T$  is linked to  $C_{GS}$  and  $C_{GD}$  capacitances: [20], [21], [22]

$$f_T = \frac{g_m}{2\pi C_0} \propto \frac{1}{C_{GD} + C_{GS}} \tag{1-1}$$

where,  $f_T$  is the transit frequency linked with switching efficiency,  $g_m$  the device trans-conductance, relates with low gate oxide voltage region,  $C_0$  the total capacitance, majorly consist of  $C_{GS}$  and  $C_{GD}$ .

From Fig. 1(c) and (d), the  $C_{GS}$  is with same composition from CFP with conventional LDMOS, and the  $C_{OF}$  is assumed very low and can be ignored, therefore, here only the  $C_{GD}$  related with gate oxide/field plate oxide and parasitic inversion/accumulation charging is discussed.

FIGURE 1. Schematic of (a) CFP devices; (b) conventional devices; capacitances of (c) CFP devices; (d) conventional devices, as [22].

LDMOS capacitance model is totally different with conventional MOSFET models. Reference [23], [24] introduced good  $C_{GD}$  methodology already for conventional LDMOS.

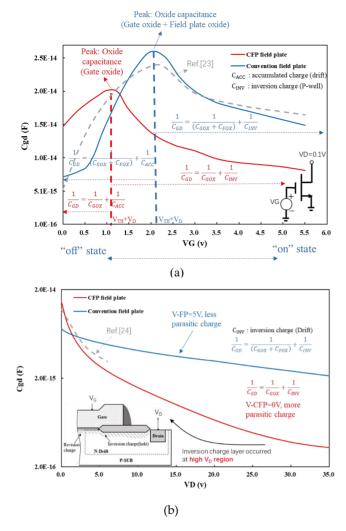

Fig. 2 (a) illustrates the  $C_{\rm GD}$  simulation results versus  $V_{\rm GS}$ , respectively from CFP and conventional LDMOS, in which our conventional curves are similar with [23] (grey dash line).

VOLUME 12, 2024 15

FIGURE 2.  $C_{GD}$  simulation results for CFP and conventional LDMOS respectively (a) versus  $V_{GS}$ ; (b) versus  $V_{DS}$ .

The behavior of  $C_{GD}$  depends on drift region design parameters, and we simulate the results from CFP LDMOS (red solid line) and conventional device (blue solid line) under the same drift concentration. It is indicated that CFP devices can achieve lower  $C_{GD}$  than conventional devices. It is easy to be explained since there is only the gate oxide contribute to the oxide capacitance, while for conventional device, there are both gate oxide and field oxide. For example, at the peak point  $(V_{GS} = V_{TH} + V_D)$ , based on production line experience, the authors give a typical value of gate oxide thickness 150Å, gate oxide length  $0.6\mu$ m, field oxide thickness 800Å, field oxide length  $1.0\mu$ m, and correspondingly calculate the CFP LDMOS capacitance  $C_{CFP}$  is around 24% lower than conventional LDMOS capacitance  $C_{Con}$ .

$$C_{CFP} = (1 - 24\%) \times C_{con}$$

(1-2)

Fig. 2(b) illustrates the  $C_{GD}$  simulation results versus  $V_{DS}$ , respectively from CFP and conventional LDMOS. It is indicated that CFP device also can achieve lower  $C_{GD}$  under

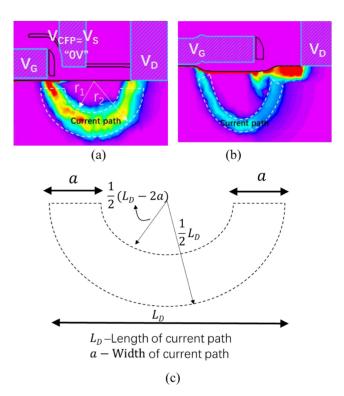

FIGURE 3. Current path in CFP LDMOS (a) simulation from CFP LDMOS; (b) simulation from conventional LDMOS; (c) ideal ring type model.

very high drain voltage. that is due to more parasitic charge under field plate when contact field plate forced 0V instead of 5V.

Of course, LDMOS capacitance is very complex, and in our simulation, the junction capacitance, gate sidewall capacitance, etc., are not considered. Meanwhile, usually CFP LDMOS size (gate length, drift length, field plate thickness, etc.) is lower that of conventional LDMOS, so the results in Fig. 2 cannot be taken as an accurate model. However, for the qualitative evaluation, lower  $C_{GD}$  and high switching efficiency is a confirmed result.

## C. R<sub>ON.SP</sub> - BV FOM CHARACTERS

FOM(Figures-of-merits) character relating the BV and  $R_{\text{on,sp}}$  is well-known for LDMOS device. Baliga introduced a very practical formula in 1989, called Baliga's formula: [25]

$$R_{\text{on,sp}} = \frac{4BV^2}{\varepsilon \mu_n E_C^{s^3}},\tag{2-1}$$

where,  $\varepsilon$  is the dielectric constant of silicon,  $\mu_n$  the electron mobility,  $E_C^s$  silicon surface breakdown voltage.

In Baliga's law (2-1), the current path is considered a linear shape straight along with a silicon surface. However, as shown in Fig. 3(a), in the CFP device, when the CFP terminal connected with source  $V_{CFP} = 0V$ , and force high drain bias  $V_{DS}$  close to BV, the extra "0" potential depletion point enhance the width of the drift depletion region and the current path is not linear shape but likes a ring type. For comparison, Fig. 3(b), illustrates the current path from a

conventional device with the same drift/body concentration. It lacks the extra "0" potential depletion point due to  $V_{FP} = V_{GS}$ , and thus, not a large current width can be acquired correspondingly.

As shown in Fig. 3(b), we consider the current path as an ideal ring shape and define the length of the current path length as  $L_D$  and the width of the current path as a, respectively. Using a similar methodology as [26], the specific on-resistance can be expressed as:

$$R_{\text{on,sp}} = R_{DS} \times HP = \frac{1}{q\mu_n N_D} \frac{1}{\int_{L_D - 2a}^{L_D} \frac{1}{\pi r} dr} \times 2L_D$$

$$= \frac{1}{q\mu_n N_D} \frac{2\pi L_D}{ln(\frac{L_D}{L_D - 2a})},$$

(2-2)

where,  $R_{DS}$  is the drift region resistance; HP the half-pitch of device; q,  $N_{\rm D}$  respectively elementary charge, and drift doping concentration.

Different with the [26],  $N_D$  is still considered as uniform and can be expressed as

$$N_D = \frac{\varepsilon_s E_C^{s^2}}{2qBV} \tag{2-3}$$

And BV is determined by the length of current path  $L_D$ :

$$BV = \pi L_D E_C^s \tag{2-4}$$

Thus.

$$R_{\text{on,sp}} = \frac{1}{\ln\left(\frac{L_D}{L_D - 2a}\right)} \times \frac{4BV^2}{\varepsilon \mu_n E_C^{s^3}}$$

(2-5)

That is, the FOM factor:

$$\frac{BV^2}{R_{\text{on,sp}}} = \frac{1}{4} \varepsilon \mu_n E_C^{s,3} \times \ln\left(\frac{L_D}{L_{D-2a}}\right) = M \times \frac{1}{4} \varepsilon \mu_n E_C^{s,3} \quad (2-6)$$

where

$$M = \ln\left(\frac{1}{1 - \frac{2a}{L_D}}\right),\,$$

where M is defined as a modulator factor. It is determined by the current length  $L_D$  and the current width a, and a larger depletion region (proportional to  $L_D$ ) or a higher a value will yield a better (higher) factor M.

From the comparison between Fig. 3(a) and (b), the CFP device can achieve a larger current path *a* due to extra "0" penitential depletion under the field plate. It could be a mechanism for better FOM characters from CFP devices, and detailed discussions will be introduced in the following simulation and measurement curves.

## III. FIELD PLATE L/W/H EFFECTS AND DISCUSSION

## A. SIMULATION MODEL

TCAD (Technology computer-aided design) simulation has already played an increasingly significant role in the LDMOS device structure designs [27], [28]. For a CFP device, modulation factor M is strongly related to the device's physical

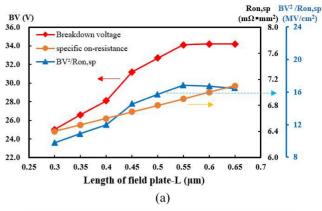

FIGURE 4. L effects (a) on FOM; (b) on depletion region.

dimension, including field plate length L, effective field plate thickness H, and slot field plate contact width W.

As known, FOM performance is strongly correlated with drift concentration and body concentration. To evaluate the physical size effects of the CFP, the authors fix drift implant P,  $2 \times 10^{12} \text{cm}^{-2}$ , p-body implant B,  $6 \times 10^{13} \text{cm}^{-2}$ , and use the Sivaco software 2-D model for TCAD simulation.

For detail, at "on-state", we force gate/drain bias  $V_{\rm GS} = V_{\rm DS} = 5V$ , ground source, and body  $V_{\rm CFP} = V_{\rm S} = V_{\rm B} = 0$ . At "off-state", ground source/body/gate,  $V_{\rm CFP} = V_{\rm S} = V_{\rm B} = V_{\rm GS} = 0$ , force drain bias as high as the breakdown voltage. And the  $R_{\rm on,sp}$  is calculated by measuring the linear current  $I_{\rm dlin}$  of the device,  $R_{\rm on,sp} = 0.1/(I_{\rm dlin} \times W_{\rm device} \times L_{\rm device})$ , 0.1 is the drain voltage for linear current  $I_{\rm dlin}$  measurement.

## **B. FIELD PLATE LENGTH-L EFFECTS**

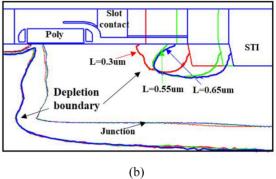

Fig. 4 (a) illustrates the effect of field plate length L on FOM characters. As the L increase, the  $R_{\rm on,sp}$  increases lineally, that is easily to be understand due to the current path increase. When L is small (e.g.,  $L < 0.55 \mu m$ ), the BV increase as well, that is because of the increase of  $L_D$ , as illustrated in formula (2-4). However, when  $L > 0.55 \mu m$ , the decrease for both BV and FOM factor  $BV^2/R_{\rm on,sp}$  is observed.

To understand the degradation, the depletion region is illustrated in Fig. 4(b). It can be seen when L increase from  $0.3\mu m$  to  $0.55\mu m$ , the depletion region increase obviously, while the depletion boundary keeps nearly no change from

VOLUME 12, 2024 17

FIGURE 5. H effects (a) on FOM; (b) on electric field distribution.

FIGURE 6. W effects (a) on FOM; (b) on depletion region.

$L=0.55\mu \mathrm{m}$  to  $L=0.65\mu \mathrm{m}$ . Since the current path length  $L_D$ , which is discussed in Section II-C, is proportional to the depletion region, the result consists of equation (2-6). The reason for BV limitation at  $L=0.55\mu \mathrm{m}$  is due to depletion region limitation, which is considered related to drift/body concentration, and another possible reason is that the current path length  $L_D$  is not circular again at higher drift region.

## C. FIELD PLATE THICKNESS H EFFECTS

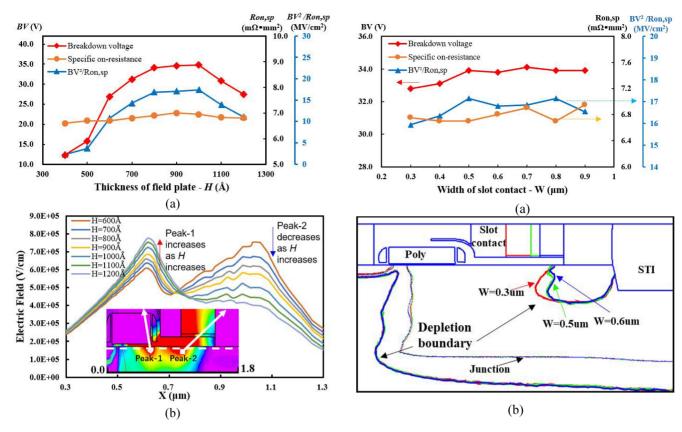

Fig. 5 (a) illustrates the effects of field plate thickness H on FOM characters. Where the H is effective field plate thickness, that can be considered as equal to bottom  $SiO_2$  thickness, as shown in Fig. 1(a) blue marks.

As the H increase, the  $R_{\rm on,sp}$  nearly no increases, that is easily to be understand according to current path  $L_D$  and current width a should be slightly changed. The BV appears a trend of increasing first and then decreasing (e.g., H > 900Å), and the FOM factor degradation occurs correspondingly.

To understand the degradation of *BV*, electric field distribution is illustrated in Fig. 5(b). The electric field distribution is modulated while the current path keeps a ring shape. There are two electric field peaks (peak means Silicon surface breakdown point). Peak-1 is at the poly gate edge close to CFP, and Peak-2 is at the CFP edge towards to the

drain terminal. At H < 900Å, when H increases, peak-2 decreases. This is the reason why BV increased. At H > 900Å, when H increases, the peak-1 increases obviously, and it becomes to dominate the degradation of BV. The electric field peak modulation is assumed to be induced by the lower capability of modulation under higher CFP oxide thickness.

## D. CONTACT WIDTH W EFFECTS

Fig. 6 (a) illustrates the effect of field plate contact width W on FOM characters. As the W increase, both the  $R_{\rm on,sp}$  and BV increases slightly, possible reason is  $L_D$  and a introduced formula (2-5), (2-6) are majorly limited by field plate length L. To indicate it, Fig. 6(b) illustrates the depletion region variations. It can be seen nearly the same depletion boundary is acquired at variable contact width W. It indicates the field plate oxide dominated the modulation on the drift region instead of the slot contact. This observation could bring us the probability of other shapes field plat contact design, such as square shape contacts, rectangle shape contacts, tomatoes on sticks shape contacts, etc.

Finally, from the simulation results, for the fixed doping condition (drift: P,  $2 \times 10^{12} cm^{-2}$ ; p-body: B,  $6 \times 10^{13} cm^{-2}$ ), the best device physical size is proposed, as shown in Table 1. The best dimension could have some changes concerning variations in drift region length, doping, and thickness.

TABLE 1. Best physical size and doping concentration of device (under concentration condition: drift, P,  $2 \times 10^{12} cm^{-2}$ ; p-body, B,  $6 \times 10^{13} cm^{-2}$ ).

| Physical structure         | Best                           | Electrical results                                    |

|----------------------------|--------------------------------|-------------------------------------------------------|

| Field plate length - L     | $0.5\sim0.6\mu m$              | FOM $(BV^2/R_{\text{on,sp}})$                         |

| Field plate thickness- $H$ | $800\sim1000 \rm \mathring{A}$ | =17.25 MW/cm <sup>2</sup><br>$R_{\text{on,sp}} = 6.9$ |

| Slot contact width-W       | $0.3\sim0.5~\mu m$             | $m\Omega \cdot mm^2$ ,<br>BV = 34.5V                  |

FIGURE 7. Brief process flow and key process.

## IV. PROCESS AND ELECTRICAL RESULTS

#### A. PROCESS FLOW

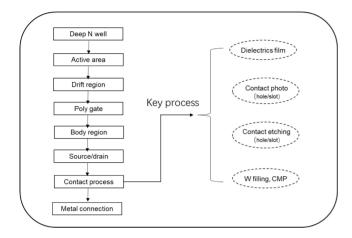

Relying on the most advanced 12-inch IC production line in (CanSemi semiconductor corp.), series of CFP LDMOS devices have been produced. Fig. 7 is the brief process flow and CFP contact key process modules:

① Deep N well; ② Active area; ③ Drift region; N-concentration, high resistance region for electric field reduction [29]; ④ Poly gate; ⑤ Body region, P type implant works as channel [30], ⑥ Source/drain; ⑦ Contact process and ⑥ Metal connection.

The contact process is the most critical and most challenging process step due to the demands of both hole-type contacts and slot-type contacts should be processed same time. The authors divide it into four process modules:

Dielectrics film: Sandwich films SiO<sub>2</sub>-Si<sub>3</sub>N<sub>4</sub>-SiO<sub>2</sub> are applied. The bottom SiO<sub>2</sub> works as field plate capacitor dielectrics, and its thickness can be considered as effective thickness *H*, illustrated in Fig. 1(a) in blue marks. The middle Si<sub>3</sub>N<sub>4</sub> film is a stop layer for dry etching, and the top SiO<sub>2</sub> a cap layer, respectively. The slot field plate contact passes through the top SiO<sub>2</sub> and then lands on the Si<sub>3</sub>N<sub>4</sub> film, keeping around 100Å Si<sub>3</sub>N<sub>4</sub> film remaining for the process margin.

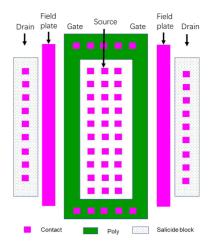

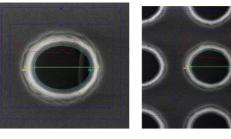

Contact photo: Both circular hole contacts and slot contacts are required, and the layout diagram of the device is shown in Figure 8.

Contact etching: It is apparent in the generation of the polymer during the dry plasma etching process, and the

FIGURE 8. Layout diagram of LDMOS devices with CFP.

polymer is a good material for the hole pattern side-wall protection during dry RF (Radio frequency) etching. However, an excessive polymer can easily lead to self-stopping during slot contact etching. It is known as "etch stop" [31]. Therefore, in the etching recipe, we adjusted the etching bias power and reduced the flow ratio of carbon-based gas, thereby reducing the polymer generation during the etching process and preventing the etching from self-stopping effectively [32].

W filling, CMP(Chemical mechanical polar): Additional amount of tungsten metal deposition is required for the enlarged slot contact pattern.

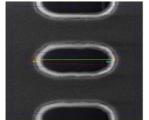

Finally, perfect SEM(Scanning electron microscope) images of the top view of the contact are shown in Fig. 9(a), including both single-hole type contacts, array-type contacts, and slot-type field plate contacts with different sizes. The TEM (Transmission electron microscope) cross-section profile, alone X direction of the device structure, also is produced. Except for perfect profiles, normal contacts (such as source contacts) landed on the silicon surface well, and field plate contacts land on the middle Si<sub>3</sub>N<sub>4</sub> film well, as shown in Fig. 9(b).

#### **B. FOM RESULTS**

Wafer level electrical parameters were tested with Agilent B1500 tools.

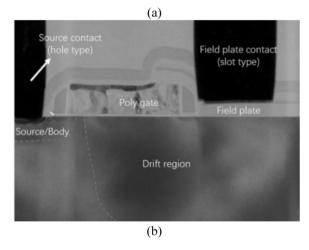

Fig. 10 illustrates the FOM  $(R_{\text{on,sp}} - BV)$  curves. The two blue lines are Baliga's formula from [25] and [26] conventional devices, respectively. [26] Baliga's curve seems high than that of [25], but the author didn't give out explanations. The green line is this work, and the red line is conventional devices fabricated in our same production lines. The grey line is [7], [33], [34], [35] devices with conventional field plates as well, these data is at similar level, and we put them together into one group.

It can be seen that the CFP devices can achieve much better FOM performance. Taking 16V devices as an example, the specific on-resistance  $R_{sp,on}$  can be achieved as low as 6.9  $m\Omega \cdot mm^2$  when the source-drain breakdown voltage BV

Single hole type contact

Array hole type contact

Slot contact (0.6µm)

Slot contact (1.0 µm)

FIGURE 9. Physical results (a) SEM top view of contacts; (b) TEM cross section (along X direction).

arrives at 34.1V, which is nearly 47.1% improved compared with conventional devices.

What is more, the slope of the CFP FOM curve is not the same as Baliga's line, and it tends to be closer to the ideal Baliga's value at a higher BV region. It is consistent with the improvement of the modulator factor M (formula (2-6), in Section II-C), which is related to the increase of current path length  $L_D$ . However, there is a "jump" point away from Baliga's line at around BV = 40V. A possible reason the current path is not "circular type" again is due to depletion region limitation at the very long drift region. The behavior of the "jump" point indicates that CFP is not suitable for high BV (such as > 40V) applications so far.

#### C. TLP-SOA RESULTS

Fig. 11(a) and (b) illustrate the TLP [36] (Transmission line pulse)-SOA (Safe operation area) curves, and it is a good indication of the CFP device's robustness.

FIGURE 10. FOM curves with log-scale.

TABLE 2. TLP-SOA test environment.

| Test setting           | Conditions                                   |  |

|------------------------|----------------------------------------------|--|

| Vs (V <sub>CFP</sub> ) | Ground                                       |  |

| $V_B$                  | Ground                                       |  |

| $V_{GS}$               | $0\text{V}\sim6\text{V}~(>1.1\times V_{DD})$ |  |

| $V_{DS}$               | Pulse, $0V \sim BV$                          |  |

| External $C$ (10nF)    | 10nF                                         |  |

| Pulse width            | 100ns                                        |  |

| Rise time              | 10ns                                         |  |

SOA curves are measured with the ES620 pulse generation tools, and the TLP test environment is described in Table 2.

Fig. 11(a) illustrates the TLP-SOA results of the 16V typical device with channel width  $W=10\mu m$ , and the device can achieve a similar ideal SOA region published in [10] and [36].

More comprehensively, Fig. 11(b) illustrates TLP-SOA results from a very large device with channel width W=2mm. The design of a very large device is a good monitor for the quality of gate oxide and field plate oxide, and it can indicate the process and device robustness better. The results also show an ideal TLP-SOA performance.

#### V. CONCLUSION

The device's structure analysis indicates that the CFP LDMOS owns better switching efficiency due to its lower  $C_{GD}$  contributed by the full separation for poly gate and field plate oxide. Also, a ring shape current path model is built, and a modulated Baliga's formula is introduced, which can indicate the CFP device's advantage of better FOM performance.

Through the CFP device's TCAD simulation on its physical dimensions, including field plate length L, field plate thickness H, and slot contact width W, an ideal device's physical size is proposed. At the same time, L, H, and W effects on FOM characters are discussed.

Relying on the advanced 12-inch IC production line, a series of CFP devices have been fabricated and tested. The process is indicated by the SEM and TEM images. The FOM curves show that CFP device indeed yields much

FIGURE 11. The TLP-SOA test results (a) from typical device (W =  $10\mu$ m); (b) from very large device (W = 2mm).

better performance than conventional devices. The specific on-resistance  $R_{\rm sp,on}$  achieves as low as 6.9  $m\Omega \cdot mm^2$  when BV arrives at 34.1V, which is nearly 47.1% improved. Furthermore, ideal TLP- SOA curves are acquired from both typical device  $W=10\mu m$  and very large device W=2mm, which is evidence of the device's robustness as well.

**Conflicts of Interest:** The authors declare no conflict of interest.

## **REFERENCES**

- [1] K. N. Kaushal and N. R. Mohapatra, "A physics-based compact model to capture cryogenic behavior of LDMOS transistors," *IEEE Trans. Electron Devices*, vol. 70, no. 3, pp. 857–863, Mar. 2023, doi: 10.1109/TED.2022.3233813.

- [2] T. Chun-Ping, D. Bao-Xing, S. Kun, W. Yan-Dong, and Y. Yin-Tang, "Analysis of novel silicon based lateral power devices with floating substrate on insulator," *Acta Phys. Sin.*, vol. 70, no. 14, 2021, Art. no. 148501. doi: 10.7498/aps.70.20202065.

- [3] S. Mehrotra et al., "Towards ultimate scaling of LDMOS with ultralow specific on-resistance," in *Proc. 32nd Int. Symp. Power Semicond. Devices ICs (ISPSD)*, Vienna, Austria, 2020, pp. 42–45, doi: 10.1109/ISPSD46842.2020.9170198.

- [4] F. Lin et al., "A Study of n-LDMOS off-state breakdown degradation with 0.18μm BCD technology," in *Proc. IEEE 26th Int. Symp. Phys. Fail. Anal. Integr. Circuits (IPFA)*, Hangzhou, China, 2019, pp. 1–4, doi: 10.1109/IPFA47161.2019.8984858.

- [5] J.-F. Yao, Y.-F. Guo, Z.-Y. Zhang, K.-M. Yang, M.-L. Zhang, and T. Xia, "Numerical and analytical investigations for the SOI LDMOS with alternated high-k dielectric and step doped silicon pillars," *Chin. Phys. B*, vol. 29, no. 3, 2020, Art. no. 38503.

- [6] W.-C. Hung et al., "Analysis of hump effect induced by positive bias temperature instability in the local oxidation of silicon n-MOSFETs," *IEEE Trans. Device Mater. Rel.*, vol. 29, no. 3, pp. 263–268, Jun. 2023, doi: 10.1109/TDMR.2023.3263868.

- [7] F. Hébert, P. Parvarandeh, M. Li, G. Zhang, P. C. Li, and J. Mo Koo, "Building blocks of past, present and future BCD technologies," in *Proc. 33rd Int. Symp. Power Semicond. Devices ICs (ISPSD)*, Nagoya, Japan, 2021, pp. 11–16, doi: 10.23919/ISPSD50666.2021.9452276.

- [8] M. Li, B. Duan, and Y. Yang, "New strained lateral MOSFET with ultralow on-resistance by surrounded stress dielectric layer," *IEEE Electron Device Lett.*, vol. 43, no. 4, pp. 525–528, Apr. 2022, doi: 10.1109/LED.2022.3155729.

- [9] Y. Wang, B. Duan, and Y. Yang, "Experimental of folded accumulation lateral double-diffused transistor with low specific on resistance," in *Proc. 33rd Int. Symp. Power Semicond. Devices ICs (ISPSD)*, Nagoya, Japan, 2021, pp. 195–198, doi: 10.23919/ISPSD50666.2021.9452249.

- [10] D. Kim, K. Lee, J. Kim, J. Choi, J. Lee, and I. Cho, "The lowest onresistance and robust 130nm BCDMOS technology implementation utilizing HFP and DPN for mobile PMIC applications," in *Proc. 31st Int. Symp. Power Semicond. Devices ICs (ISPSD)*, Shanghai, China, 2019, pp. 391–394, doi: 10.1109/ISPSD.2019.8757571.

- [11] Q. Li, Z.-Y. Zhang, H.-O. Li, T.-Y. Sun, Y.-H. Chen, and Y. Zuo, "Stacked lateral double-diffused metal-oxide-semiconductor field effect transistor with enhanced depletion effect by surface substrate, *Chin. Phys. B*, vol. 28, no. 3, 2019, Art. no. 37201.

- [12] S. Liu, R. Ye, W. Sun, and L. Shi, "A novel lateral DMOS transistor with H-shape shallow-trench-isolation structure," *IEEE Trans. Electron Devices*, vol. 65, no. 11, pp. 5218–5221, Nov. 2018.

- [13] L. Wei, C. Chao, U. Singh, R. Jain, L. L. Goh, and P. R. Verma, "A novel contact field plate application in drainextended-MOSFET transistors," in *Proc. 29th Int. Symp. Power Semicond. Devices IC's (ISPSD)*, Sapporo, Japan, 2017, pp. 335–337, doi: 10.23919/ISPSD.2017.7988957.

- [14] L. Wei, U. Singh, C. Chao, R. Jain, and P. R. Verma, "Effect of contact field plate on hot-carrier-induced on-resistance degradation in n-Drain extended MOS transistors," in *Proc. IEEE Int. Reliabil. Phys. Symp. (IRPS)*, Monterey, CA, USA, 2017, pp. FA-3.1–FA-3.4, doi: 10.1109/IRPS.2017.7936373.

- [15] W.-C. Hung et al., "Abnormal on-current degradation under non-conductive stress in contact field plate lateral double-diffused metal-oxide- semiconductor transistor with 0.13-μm bipolar-CMOS-DMOS technology," *IEEE Electron Device Lett.*, vol. 43, no. 5, pp. 769–772, May 2022, doi: 10.1109/LED.2022.3164475.

- [16] Y. Yao et al., "Advanced N-channel LDMOS with ultralow specific on-resistance by 0.18 μm epitaxial BCD technology," in *Proc. China Semicond. Technol. Int. Conf. (CSTIC)*, Shanghai, China, 2018, pp. 1–3, doi: 10.1109/CSTIC.2018.8369286.

- [17] A. Tannenbaum, D. Mistele, and Y. Stav, "Optimization of integrated 0.18μm nLDMOS, for power management ICs rated at 40–60V," in *Proc. IEEE Int. Conf. Microw. Antennas Commun. Electron. Syst. (COMCAS)*, Tel-Aviv, Israel, 2017, pp. 1–5, doi: 10.1109/COMCAS.2017.8244821.

- [18] T. Kumari, J. Singh, and P. K. Tiwari, "Unified modeling of gate insulator capacitance of nonplanar MOSFETs including the impact of inclined sidewalls and rounded-corners," *IEEE Trans. Electron Devices*, vol. 70, no. 1, pp. 13–19, Jan. 2023, doi: 10.1109/TED.2022.3221357.

- [19] Y. Wei, X. R. Luo, W. Ge, Z. Zhao, Z. Ma, and J. Wei, "A split triple-gate power LDMOS with improved static-state and switching performance," *IEEE Trans. Electron Devices*, vol. 66, no. 6, pp. 2669–2674, Jun. 2019, doi: 10.1109/TED.2019.2910126.

- [20] X. Lin, R. Burgos, and D. Dong, "Improved variable switching frequency control for capacitor voltage ripple regulation in multilevel flying capacitor converter," *IEEE Trans. Power Electron.*, vol. 38, no. 5, pp. 5700–5705, May 2023, doi: 10.1109/TPEL.2023.3242204.

- [21] R. Asanovski et al., "Understanding the excess 1/F noise in MOSFETs at cryogenic temperatures," *IEEE Trans. Electron Devices*, vol. 70, no. 4, pp. 2135–2141, Apr. 2023, doi: 10.1109/TED.2022.3233551.

- [22] D. Muller, A. Giry, D. Pache, J. Mourier, B. Szelag, and A. Monroy, "Architecture optimization of an N-channel LDMOS device dedicated to RF-power application," in *Proc. 17th Int. Symp. Power Semicond. Devices ICs*, Santa Barbara, CA, USA, 2005, pp. 159–162, doi: 10.1109/ISPSD.2005.1487975.

VOLUME 12, 2024 21

- [23] Y. S. Chauhan, F. Krummenacher, R. Gillon, B. Bakeroot, M. Declercq, and A. M. Ionescu, "A new charge based compact model for lateral asymmetric MOSFET and its application to high voltage MOSFET modeling," in *Proc. 20th Int. Conf. VLSI Design Held Jointly 6th Int. Conf. Embedded Syst. (VLSID)*, Bengaluru, India, 2007, pp. 177–182, doi: 10.1109/VLSID.2007.15.

- [24] Y. S. Chauhan, F. Krummenacher, R. Gillon, B. Bakeroot, M. J. Declercq, and A. M. Ionescu, "Compact modeling of lateral nonuniform doping in high-voltage MOSFETs," *IEEE Trans. Electron Devices*, vol. 54, no. 6, pp. 1527–1539, Jun. 2007, doi: 10.1109/TED.2007.896597.

- [25] B. J. Baliga, Fundamentals of Power Semiconductor Devices, 2nd ed. Raleigh, NC, USA: Springer, 2007, ch. 1, pp. 14–15, doi: 10.1007/978-3-319-93988-9.

- [26] A. Saadat, M. L. Van de Put, H. Edwards, and W. G. Vandenberghe, "LDMOS drift region with field oxides: Figure-of-merit derivation and verification," *IEEE J. Electron Devices Soc.*, vol. 10, pp. 361–366, 2022. doi: 10.1109/JEDS.2022.3169702.

- [27] J. Yoo et al., "Machine-learning based TCAD optimization method for next generation BCD process development," in *Proc. 33rd Int. Symp. Power Semicond. Devices ICs (ISPSD)*, Nagoya, Japan, 2021, pp. 279–282, doi: 10.23919/ISPSD50666.2021.9452285.

- [28] F. Giuliano et al., "TCAD predictions of hot-electron injection in p-type LDMOS transistors," in *Proc. 49th Eur. Solid-State Device Res. Conf. (ESSDERC)*, Cracow, Poland, 2019, pp. 86–89, doi: 10.1109/ESSDERC.2019.8901703.

- [29] G. Pahwa et al., "Robust compact model of high-voltage MOSFET's drift region," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 42, no. 1, pp. 337–340, Jan. 2023, doi: 10.1109/TCAD.2022.3172599.

- [30] S. Pali, N. Kumar, and A. Gupta, "Drain extended MOS body region engineering for switching reliability under unclamped inductive load conditions," *IEEE Trans. Device Mater. Rel.*, vol. 23, no. 1, pp. 134–141, Mar. 2023, doi: 10.1109/TDMR.2023.3237467.

- [31] J. Luo, J. Meng, B. Han, H. Sun, D. Xiao, and C. Zhao, "High aspect ratio contact profile control and cryogenic etch process," in *Proc. Int. Workshop Adv. Pattern. Solut. (IWAPS)*, Foshan, China, 2021, pp. 1–4, doi: 10.1109/IWAPS54037.2021.9671072.

- [32] S. Dasgupta et al., "Novel process for screen-printed selective area front polysilicon contacts for TOPCon cells using laser oxidation," *IEEE J. Photovolt.*, vol. 12, no. 6, pp. 1282–1288, Nov. 2022, doi: 10.1109/JPHOTOV.2022.3196822.

- [33] K. Lee et al., "0.35μm, 30V fully isolated and low-Ron nLDMOS for DC-DC applications," in *Proc. 25th Int. Symp. Power Semicond. Devices & IC's (ISPSD)*, Kanazawa, Japan, 2013, pp. 163–166, doi: 10.1109/ISPSD.2013.6694454.

- [34] J. Lee et al., "0.13 μm modular BCD technology enable to embedding high density E2PROM, RF and hall sensor suitable for IoT application," in *Proc. 28th Int. Symp. Power Semicond. Devices* and ICs (ISPSD), Prague, Czech Republic, 2016, pp. 419–422, doi: 10.1109/ISPSD.2016.7520867.

- [35] T.-Y. Huang et al., "0.18um BCD technology with best-in-class LDMOS from 6 V to 45 V," in *Proc. IEEE 26th Int. Symp. Power Semicond. Devices & IC's (ISPSD)*, Waikoloa, HI, USA, 2014, pp. 179–181, doi: 10.1109/ISPSD.2014.6856005.

- [36] M. S. Bhoir, K. N. Kaushal, S. R. Panda, A. K. Singh, H. S. Jatana, and N. R. Mohapatra, "Source underlap—A novel technique to improve safe operating area and output-conductance in LDMOS transistors," *IEEE Trans. Electron Devices*, vol. 66, no. 11, pp. 4823–4828, Nov. 2019, doi: 10.1109/TED.2019.2942372.