Received 7 March 2023; revised 19 April 2023 and 12 May 2023; accepted 16 May 2023. Date of publication 18 May 2023; date of current version 29 May 2023.

The review of this article was arranged by Editor G. I. Ng.

Digital Object Identifier 10.1109/JEDS.2023.3277796

# Over 10W/mm High Power Density AlGaN/GaN HEMTs With Small Gate Length by the Stepper Lithography for Ka-Band Applications

MING-WEN LEE<sup>® 1,2</sup> (Graduate Student Member, IEEE), YUEH-CHIN LIN<sup>1</sup>, PO-SHENG CHANG<sup>1</sup>, YI-FAN TSAO<sup>® 1</sup> (Member, IEEE), HENG-TUNG HSU<sup>® 1</sup> (Senior Member, IEEE), CHANG-FU DEE<sup>® 3</sup>, AND EDWARD YI CHANG<sup>® 1,3,4,5</sup> (Life Fellow, IEEE)

1 International College of Semiconductor Technology, National Yang Ming Chiao Tung University, Hsinchu 300, Taiwan 2 Doctorate Programme in Information and Communication Technologies, University of Granada, 18012 Granada, Spain 3 Institute of Microengineering and Nanoelectronics, Universiti Kebangsaan Malaysia, Bangi 43600, Malaysia 4 Department of Materials Science and Engineering, National Yang Ming Chiao Tung University, Hsinchu 300, Taiwan 5 Department of Electronics Engineering, National Yang Ming Chiao Tung University, Hsinchu 300, Taiwan

CORRESPONDING AUTHOR: E. Y. CHANG (e-mail: edc@nycu.edu.tw)

This work was supported in part by the "Center for the Semiconductor Technology Research" from the Featured Areas Research Center Program within the Framework of the Higher Education Sprout Project by the Ministry of Education (MOE), Taiwan, and in part by the Ministry of Science and Technology, Taiwan, under Grant NSTC 111-2218-E-A49-021, Grant NSTC 111-2634-F-A49-008, Grant NSTC 111-2221-E-A49-173-MY3, and Grant NSTC 112-2622-8-A49-013-SB.

**ABSTRACT** This study reports AlGaN/GaN high-electron-mobility transistors (HEMTs) fabricated by the Stepper Lithography on a 4-inch wafer for Ka-Band applications. Small gate length ( $L_G$ ) of 100 nm was achieved through a 2-Step Photolithography Process and the gate region of the AlGaN/GaN HEMT was defined by using two lithography steps to form gamma-shaped gates. The 4-inch AlGaN/GaN HEMT wafer demonstrated high electrical performance uniformity with respect to the maximum drain-source current density ( $I_{DSS}$ ), the peak extrinsic output transconductance ( $G_m$ ), and the threshold voltage ( $V_{th}$ ). At  $V_{DS} = 20$  V, the AlGaN/GaN HEMT exhibits an  $I_{DSS}$  of 1004.2 mA/mm, a Gm value of 363.6 mS/mm, a maximum output power density ( $P_{OUT}$  ( $P_{OUT}$

**INDEX TERMS** 5G, high uniformity, output power, stepper lithography, small gate length.

# I. INTRODUCTION

Gallium Nitride, with its outstanding characteristics by forming 2-Dimensional Electron Gas (2DEG) through piezo-electric and spontaneous polarizations using AlGaN/GaN heterojunction, was used for power high-electron-mobility transistor (HEMT) devices with multi-gigahertz frequency range in the year of 2005 by Eudyna Corporation in Japan [1]. Later, with its high mobility, high bandgap and high thermal conductivity features [2], the GaN HEMT devices became popular worldwide for RF applications due to the inherent material properties which include

high breakdown voltage, high current density, low thermal resistance, and low substrate parasitic capacitances [3], [4]. GaN-based HEMTs outperform Si and GaAs-based devices [5] owing to their higher output power characteristics and higher thermal resistance. With the increasing demands of RF power devices at Ka-Band and beyond for applications such as 5G, military radars, satellites, and networks for advanced communication systems, it is essential to reduce the GaN high frequency device manufacturing cost by increasing the device yield and to improve the device DC and RF performance.

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 License. For more information, see https://creativecommons.org/licenses/by-nc-nd/4.0/

VOLUME 11, 2023 311

Traditionally, researchers fabricate small gate length  $(L_G)$  devices with the E-beam Lithography System [6], [7], [8], [33]. However, for mass production of the GaN HEMT for 5G commercial applications, the E-beam Lithography Process is complicated, high cost, and time consuming. Therefore, it is essential to develop more efficient and economical methods with higher yield to meet the industrial needs.

Over the past few decades, Steppers, also known as the Step-and-Repeat Lithography System, have been widely adopted for large scale commercial application of III-V semiconductor integrated circuits for its' simple and direct process steps and capability to utilize a fine reticle with less particles [9], [10], [11]. However, for the conventional stepper process, it is difficult to achieve submicron gate lengths to reduce gate resistance, increase cut-off frequency, and switching speed for high frequency applications.

To scale down the  $L_G$  with the Stepper, a 2-Step Photolithography Process is introduced in this study. High performance Ka band HEMT devices on a 4-inch SiC wafer with excellent wafer uniformity using the Stepper Lithography is realized by the approach in this paper.

### II. DEVICE FABRICATION

To provide high 2DEG density for the device for high RF power operation, wafers with AlGaN/AlN/GaN layers grown on top of the SiC substrate by the metal organic chemical vapor deposition (MOCVD) system were used. The epitaxy of the SiC wafer includes a 0.3  $\mu m$  Fe-GaN buffer layer with doping concentration of  $1\times10^{18}~cm^{-3}$ , a 0.9  $\mu m$  i-GaN buffer layer, a 0.8-nm AlN layer, and a 17-nm AlGaN barrier layer to realize the heterojunction structure. A 2DEG density of  $1.3\times10^{13}~cm^{-2}$  and an electron mobility of  $2300~cm^2/V\cdot s$  were obtained based on the Hall measurement of the structure.

Standard fabrication steps of source/drain ohmic contact formation, device isolation, gate Schottky contact formation, passivation and contact via hole formation were processed. After the wafer cleaning process by Acetone (ACE) and Isopropyl alcohol (IPA), the wafer was then immersed in a 10% Hydrochloric acid (HCl) solution to remove the native oxides.

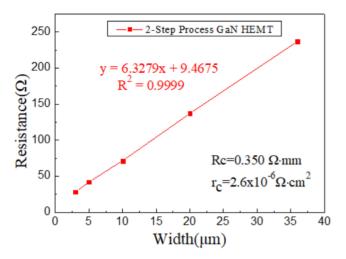

Transfer length method (TLM) was used for the extraction of  $R_C$ . The contact resistance was 0.35  $\Omega$ ·mm, and the contact resistivity is  $2.6\times10^{-6}~\Omega$ ·cm<sup>2</sup>, as shown in Fig. 4. The Ti/Al/Ni/Au ohmic contact was then deposited by the E-gun evaporator (E-gun) and then annealed at 850 °C for 30 s in  $N_2$  ambient for alloying.

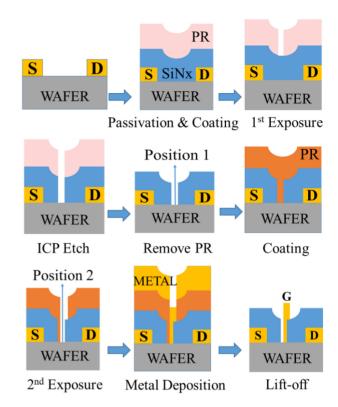

Device isolation was defined by Boron implantation. The gate formation process is shown in Fig. 1. A 150-nm thick  $SiN_x$  film was first deposited with Plasma-Enhanced Chemical Vapor Deposition System (PECVD) on the wafer. Then, the first stepper lithography process was done and Position 1 was defined after ICP etch. To ensure the  $1^{st}$  nitride etch reach the barrier layer, the  $SiN_x$  layer was etched with  $CF_4$  plasma [12]. The second photolithography step

FIGURE 1. 2-Step Photolithography Process shown with its cross section of AlGaN/GaN HEMTs.

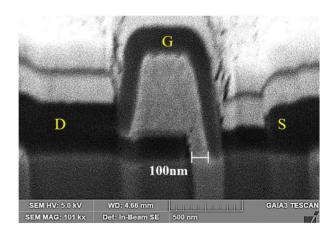

FIGURE 2. SEM image of the gate cross section with gate length of 100 nm.

begins with a shifted gate mask, which is the patterning of the  $2^{\rm nd}$  photoresist layer. Finally, a small opening in the etched  ${\rm SiN_x}$  (Position 2) is defined by the  $2^{\rm nd}$  stepper lithography process. Gate formation was completed by the deposition of Ni/Au stack metal using E-gun.  ${\rm SiN_x}$  passivation layer was grown by the PECVD to protect the wafer surface [13] after gate metal deposition. To reduce the skin effect at high frequency operation,  $2\mu {\rm m}$  thick metal interconnects were evaporated on the device contact pads.

The SEM image of the gate is shown in Fig. 2. The bottom of the gate is firmly deposited on the 100 nm opening and the top  $L_G$  distribution is defined by the lateral etching of  $SiN_x$

layers [14]. The charges accumulated on the  $SiN_x$  surface edges may deflect the incoming ions, leaving a trapezoidal-shaped top gate [15].

### III. RESULTS AND DISCUSSION

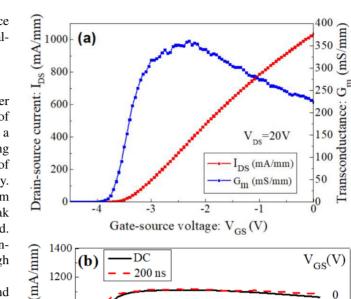

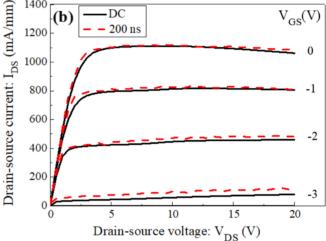

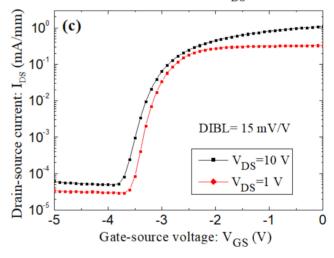

The  $I_{DS}$ - $V_{GS}$ ,  $I_{DS}$ - $V_{DS}$  and pulsed  $I_{DS}$ - $V_{DS}$ , and the transfer characteristics in semi-log scale at  $V_{DS}$ =10 V and 1 V of the 2×25  $\mu$ m AlGaN/GaN HEMT with a  $L_G$  of 100 nm, a source-drain spacing ( $L_{SD}$ ) of 2.250  $\mu$ m, a gate-drain spacing ( $L_{GD}$ ) of 1.425  $\mu$ m, and a gate-source spacing ( $L_{GS}$ ) of 0.725  $\mu$ m, as shown in Fig. 3 (a), (b), and (c) respectively.

With the 2-Step Photolithography Process, a maximum drain-source current density of 1004.2 mA/mm and a peak extrinsic transconductance of 363.6 mS/mm were measured. The AlGaN/GaN HEMT DC performance shows the potential of using the proposed lithography method to realize high RF performance Ka band transistors.

The  $I_{DS}$ - $V_{DS}$  curves for the 100-nm device with and without pulsed biases ( $V_{GS,\,Q}$  =0V,  $V_{DS,\,Q}$ =0V) have been measured and shown in Fig. 3 (b), which show little current dispersion. The pulsed  $I_{DS}$ - $V_{DS}$  measurement has a pulse width of 200 ns and a duty cycle of 0.1%. The applied pulse width of 200 ns is shorter than the time constant of most traps, therefore could eliminate thermal and trap effects [36].

Fig. 3 (d) shows the transfer characteristics in semi-log scale at  $V_{DS}$ =10 V and 1 V of the 2×25  $\mu$ m AlGaN/GaN HEMT. In this study, drain induced barrier lowering (DIBL) is defined as  $\Delta V_{th}/\Delta V_{DS}$  with  $V_{th}$  defined as the gate voltage at  $I_{DS}$ =1 mA/mm. A DIBL value of 15 mV/V is further extracted from  $V_{DS}$ =10 V and 1 V, showing an increased DIBL due to smaller gate length and smaller gate-to-channel aspect ratio compared to the 150 nm devices [35].

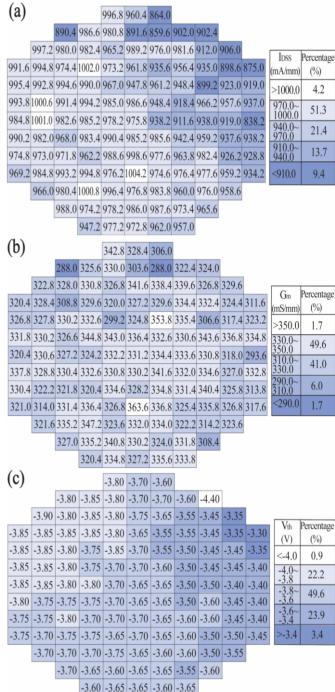

DC mapping for  $2\times25~\mu m$  devices was done to confirm the high wafer uniformity of the 4-inch wafer fabrication with the Stepper lithography, and is shown in Fig. 5. The  $I_{DSS}$ ,  $G_m$  and  $V_{th}$  mapping results were shown in Fig. 4(a), (b), and (c), respectively. More than 85% of the AlGaN/GaN HEMTs on the wafer exhibited an  $I_{DSS}$  value between 910 to 1000 mA/mm. More than 90% of the AlGaN/GaN HEMTs on the wafer exhibited a  $G_m$  value between 310 to 350 mS/mm and more than 95% of the AlGaN/GaN HEMTs on the wafer exhibited a  $V_{th}$  value between -4.0 to -3.4 V. The high uniformity is attributed to both the reproducibility of the Stepper Lithography [10] and the simplicity of the 2-Step Photolithography Process.

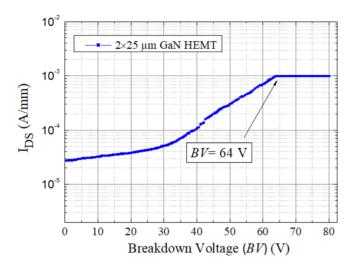

The device off-state breakdown voltage is measured as shown in Fig. 10. The three terminal breakdown voltage measurement were done on a 2-step photolithography HEMT device with  $2\times25~\mu m$  gate width,  $L_{SD}{=}2.25~\mu m$ . The device shows a breakdown voltage at  $I_{DS}{=}1~mA/mm$  of 64 V at off-state ( $V_{GS}{=}-5~V$ ), which demonstrates the potential of GaN HEMT device for high power Ka-band applications.

To investigate the RF characteristics of the AlGaN/GaN HEMTs with the 2-Step Photolithography Process,

FIGURE 3. (a)  $I_{DS}$ -V $_{GS}$ , (b)  $I_{DS}$ -V $_{DS}$  and pulsed  $I_{DS}$ -V $_{DS}$  curves, and (c) the transfer characteristics in semi-log scale at V $_{DS}$ =10 V and 1 V of the 2×25  $\mu$ m AlGaN/GaN HEMT.

S parameter results of the AlGaN/GaN HEMT and large signal characteristics of a the AlGaN/GaN HEMT at 28GHz were examined.

S-parameters results were measured on-wafer using the N5227B PNA Microwave Network Analyzer and shown in Fig. 8 after de-embedding. The system was calibrated with a

VOLUME 11, 2023 313

FIGURE 4. TLM results of the AlGaN/GaN HEMT for the 2-Step Photolithography Process.

short-open load-through calibration standard. The calibration accuracy was verified by insuring that both  $S_{21}$  and  $S_{12}$  of the through standard are less than  $\pm 0.01$  dB and that both  $S_{11}$  and  $S_{22}$  are less than -45 dB within the measured frequency range after calibration [30].

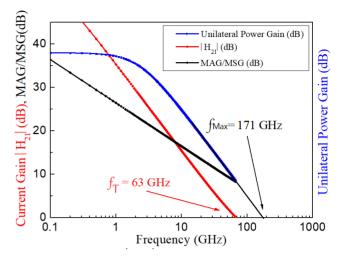

The current gain cut-off frequency ( $f_t$ ) of 63 GHz, the unilateral power gain (U) curve, and the maximum oscillation frequency ( $f_{max}$ ) of 171 GHz for the 2×50  $\mu$ m AlGaN/GaN HEMT with L<sub>SD</sub>=2.5  $\mu$ m using the 2-Step Photolithography Process are shown in Fig. 8.

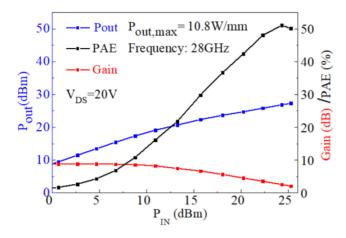

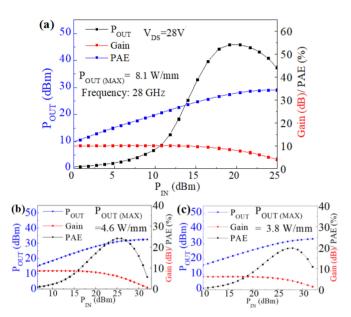

For large signal characteristics, the 3dB compression point power density ( $P_{OUT(P3dB)}$ ) of 4.3 W/mm, maximum power density ( $P_{OUT}$  ( $P_{max}$ )) of 10.8 W/mm, and maximum PAE of 51.1% of the 2×25  $\mu$ m device with  $L_{SD}$ =2.25  $\mu$ m were measured at  $V_{DS}$  = 20 V and  $V_{GS}$ =-1.58 V ( $I_{DS}$ =460 mA/mm) in Continuous Wave (CW) mode Load Pull measurement, as shown in Fig. 6.

28 GHz CW mode Load-pull measurement tests have also been performed on the 2×50  $\mu$ m, 8×50  $\mu$ m, and 8×75  $\mu$ m devices, as shown in Fig. 7 (a), (b), and (c). The 2×50  $\mu$ m device with L<sub>SD</sub>=2.5  $\mu$ m measured at a bias of V<sub>DS</sub>=28 V and V<sub>GS</sub>=-1.66 V (I<sub>DS</sub>=41.1 mA/mm) exhibits an output power density of 8.1 W/mm. The 8×50  $\mu$ m device with L<sub>SD</sub>=2.5  $\mu$ m measured at a set bias of V<sub>DS</sub>=28 V and V<sub>GS</sub>=-2.5 V (I<sub>DS</sub>=252.5 mA/mm) exhibits an output power of 1.85 W. Moreover, to further increase the output power performances of the 2-Step Process devices, the 8×75  $\mu$ m device with L<sub>SD</sub>=3.0  $\mu$ m and with the increased gate width of 25  $\mu$ m compared to the 8×50  $\mu$ m devices have been fabricated and has demonstrated an output power of 2.25 W under 28 GHz load pull measurements with V<sub>DS</sub>=28 V and V<sub>GS</sub>=-2.6 V (I<sub>DS</sub>=233.3 mA/mm).

The RF performance of these devices shows the capability of the 2-Step Photolithography Process to be applied on larger gate periphery devices, while maintaining high wafer yield through a high uniformity analyzation. The decrease of the output power density of the 2-Step devices

FIGURE 5. The 4-inch wafer uniformity of a 2×25  $\mu$ m device on (a) I<sub>DSS</sub> value, (b)  $G_{\rm m}$  value and (c)  $V_{\rm th}$  value.

with increased device single gate width may result from the increased gate resistance ( $R_g$ ). The effect of gate width concerning the  $R_g$  has been done in detail by Palacios et al. [31]. Palacios et al. shows that for AlGaN/GaN HEMT devices, the  $R_g$  scales linearly with the gate width for a device with gate lengths of around 150 nm, and has an important effect on the device RF performances, such as  $f_{max}$ .

FIGURE 6. Large signal results of a 2×25  $\mu$ m AlGaN/GaN HEMT for the 2-Step Photolithography Process.

FIGURE 7. Large signal results of the (a)  $2\times50~\mu$ m, (b)  $8\times50~\mu$ m, (c)  $8\times75~\mu$ m AlGaN/GaN HEMTs for the 2-Step Photolithography Process.

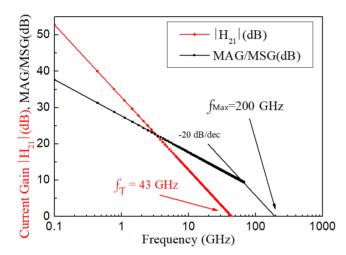

The effects of gate width on  $f_t$  and  $f_{max}$  are also discussed with the small signal of the 2×50  $\mu$ m and 8×50  $\mu$ m devices. The  $f_t$  and  $f_{max}$  values of 43 GHz and 200GHz, respectively, for the 8×50  $\mu$ m AlGaN/GaN HEMT are shown in Fig. 11.

Compared to the  $2\times50~\mu\mathrm{m}$  device in Fig. 8, the  $8\times50~\mu\mathrm{m}$  device exhibits a lower  $f_t$  value, which may be due to increased gate capacitance from the larger gate width. However, the  $8\times50~\mu\mathrm{m}$  device has a higher  $f_{max}$  value, which is mainly due to the reduced  $R_g$  from increased gate fingers [34].

The decrease of output power density of the devices with more gate fingers in this study may be due to the increase of self-heating effect [32], showing that the increase of self-heating effects with gate fingers during on-wafer measurement reduces the output power density of the SiC

FIGURE 8. Current-gain  $|H_{21}|$ , unilateral power gain (U), and MAG/MSG vs. Frequency plot for the  $2\times50~\mu m$  AlGaN/GaN HEMT with the 2-Step Photolithography Process.

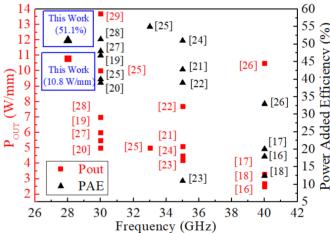

FIGURE 9. Benchmark of the 2-Step device and published results.

MESFET devices, despite the high thermal conductivity of SiC substrates.

The RF power performance of the device with a highest output power density in this study is compared with other published results, as shown in Fig. 9. At Ka-Band, the RF results of a  $2\times25~\mu m$  using the 2-Step Photolithography Process exhibited an outstanding POUT (MAX) among representative published papers. The RF power characteristic shown in this work exhibits over 50% PAE, and a record high output power density of 10.8 W/mm for devices fabricated using only the stepper phtolithography system for  $L_{\rm G}$ definition. Within published Ka band frequency devices [16], [17], [18], [19], [20], [21], [22], [23], [24], [25], [26], [27], [28], [29], the output power density of this work not only standout among state-of-the-art results, but also shows potential for the mass production of high output power density GaN HEMT wafers without using the conventional E-beam lithography system.

VOLUME 11, 2023 315

FIGURE 10. Breakdown Voltage measurement result of the 2×25  $\mu m$  HEMT device at VGS =-5 V.

FIGURE 11. Current-gain  $|H_{21}|$  and MAG/MSG vs. Frequency plot for the  $8\times50~\mu m$  AlGaN/GaN HEMT with the 2-Step Photolithography Process.

# IV. CONCLUSION

We have demonstrated AlGaN/GaN HEMTs fabricated by the Stepper Lithography, and with the 2-Step Photolithography Process, we have achieved small gate lengths and achieved high wafer uniformity on the 4-inch wafer with high  $I_{DSS}$ ,  $G_m$  and  $V_{th}$  values. At  $V_{DS}=20$  V, the AlGaN/GaN HEMT exhibits an  $I_{DSS}$  of 1004.2 mA/mm, a  $G_m$  value of 363.6 mS/mm, a maximum output power density ( $P_{OUT\ (MAX)}$ ) of 10.8 W/mm, and a power gain of 8.8 dB with a maximum Power-added efficiency (PAE) of 51.1% at 28 GHz in CW mode. Overall, the high wafer uniformity and the outstanding RF power performance together makes the process applicable for Ka-band device fabrication, and has the potential to mass production on 6- and 8-inch wafers.

## **REFERENCES**

[1] A. Lidow, M. de Rooji, J. Strydom, D. Reusch, and J. Glaser, GaN Transistors for Efficient Power Conversion (1.3 GaN and SiC Compared with Silicon), 3rd ed. Hoboken, NJ, USA: Wiley, 2020, p. 2.

- [2] U. K. Mishra, L. Shen, T. E. Kazior, and Y.-F. Wu, "GaN-based RF power devices and amplifiers," *Proc. IEEE*, vol. 96, no. 2, pp. 287–305, Feb. 2008, doi: 10.1109/JPROC.2007.911060.

- [3] Y. C. Lin et al., "Enhancement-mode GaN MIS-HEMTs with LaHfOx gate insulator for power application," *IEEE Electron Device Lett.*, vol. 38, no. 8, pp. 1101–1104, Aug. 2017, doi: 10.1109/LED.2017.2722002.

- [4] Y.-C. Lin, C.-H. Chang, F.-M. Li, L.-H. Hsu, and E. Y. Chang, "Evaluation of TiN/Cu gate metal scheme for AlGaN/GaN highelectron-mobility transistor application," *Appl. Phys. Exp.*, vol. 6, Sep. 2013, Art. no. 91003, doi: 10.7567/APEX.6.091003.

- [5] J.-N. Yao et al., "Evaluation of a 100-nm gate length E-mode InAs high electron mobility transistor with Ti/Pt/Au ohmic contacts and mesa sidewall channel etch for high-speed and low-power logic applications," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 797–802, 2018, doi: 10.1109/JEDS.2018.2853547.

- [6] S.-J. Yeon, M. Park, and K.-S. Seo, "Novel sloped etch process for 15nm InAlAs/InGaAs metamorphic HEMTs," in *Proc. 7th IEEE Conf. Nanotechnol. (IEEE NANO)*, 2007, pp. 1152–1155, doi: 10.1109/NANO.2007.4601387.

- [7] Y.-C. Lin et al., "Study of the mesa etched tri-gate InAs HEMTs with extremely low SS for low-power logic applications," in *Proc. China Semicond. Technol. Int. Conf. (CSTIC)*, 2018, pp. 1–3, doi: 10.1109/CSTIC.2018.8369315.

- [8] S. Arulkumaran, G. I. Ng, and S. Vicknesh, "Enhanced breakdown voltage with high Johnson's figure-of-merit in 0.3-\$\mu{\rm m}\$ T-gate AlGaN/GaN HEMTs on silicon by \$({\rm NH}\_{4})\_{2}{\rm S}\_{x}\$ treatment," *IEEE Electron Device Lett.*, vol. 34, no. 11, pp. 1364–1366, Nov. 2013, doi: 10.1109/LED.2013.2279882.

- [9] J. Xu, S. Zhang, P. Zheng, R. Wang, and X. Tong, "Non-ebeam AlGaN/GaN HEMTs with \$f\_{\max}\$ of 206 GHz for mass production," in *Proc. Int. Conf. Microw. Millimeter Wave Technol. (ICMMT)*, 2019, pp. 1–3, doi: 10.1109/ICMMT45702.2019.8992212.

- [10] S. V. Sreenivasan, "Nanoimprint lithography steppers for volume fabrication of leading-edge semiconductor integrated circuits," *Microsyst. Nanoeng.*, vol. 3, Sep. 2017, Art. no. 17075, doi: 10.1038/micronano.2017.75.

- [11] J.-E. Muller et al., "A GaAs HEMT MMIC chip set for automotive radar systems fabricated by optical stepper lithography," *IEEE J. Solid-State Circuits*, vol. 32, no. 9, pp. 1342–1349, Sep. 1997, doi: 10.1109/4.628737.

- [12] R. Chu et al., "Impact of \$\hbox{CF}\_{4}\$ plasma treatment on GaN," IEEE Electron Device Lett., vol. 28, no. 9, pp. 781–783, Sep. 2007, doi: 10.1109/LED.2007.902849.

- [13] A. Ouacha, M. Willander, B. Hammarlund, and R. A. Logan, "Effect of surface passivation with SiN on the electrical properties of InP/InGaAs heterojunction bipolar transistors," *J. Appl. Phys.*, vol. 74, no. 9, pp. 5602–5605, 1993, doi: 10.1063/1.354221.

- [15] I. W. Rangelow, "Critical tasks in high aspect ratio silicon dry etching for microelectromechanical systems," J. Vac. Sci. Technol. A, Vac. Surf. Films, vol. 21, no. 4, pp. 1550–1562, Jul. 2003, doi: 10.1116/1.1580488.

- [16] F. Medjdoub, M. Zegaoui, B. Grimbert, D. Ducatteau, N. Rolland, and P. A. Rolland, "First demonstration of high-power GaN-on-silicon transistors at 40 GHz," *IEEE Electron Device Lett.*, vol. 33, no. 8, pp. 1168–1170, Aug. 2012, doi: 10.1109/LED.2012.2198192.

- [17] A. Soltani et al., "Power performance of AlGaN/GaN high-electron-mobility transistors on (110) silicon substrate at 40 GHz," *IEEE Electron Device Lett.*, vol. 34, no. 4, pp. 490–492, Apr. 2013, doi: 10.1109/LED.2013.2244841.

- [18] P. Altuntas et al., "Power performance at 40 GHz of AlGaN/GaN high-electron mobility transistors grown by molecular beam epitaxy on Si(111) substrate," *IEEE Electron Device Lett.*, vol. 36, no. 4, pp. 303–305, Apr. 2015, doi: 10.1109/LED.2015.2404358.

- [19] M. Mi et al., "Millimeter-wave power AlGaN/GaN HEMT using surface plasma treatment of access region," *IEEE Trans. Electron Devices*, vol. 64, no. 12, pp. 4875–4881, Dec. 2017, doi: 10.1109/TED.2017.2761766.

- [20] R. Aubry et al., "ICP-CVD SiN passivation for highpower RF InAlGaN/GaN/SiC HEMT," IEEEElectron Lett., vol. 37, no. 5, pp. 629–632, May 2016. doi: 10.1109/LED.2016.2540164.

- [21] Y. Zhang et al., "High-temperature-recessed millimeter-wave AlGaN/GaN HEMTs with 42.8% power-added-efficiency at 35 GHz," IEEE Electron Device Lett., vol. 39, no. 5, pp. 727-730, May 2018, doi: 10.1109/LED.2018.2822259.

- [22] R. C. Fitch et al., "Implementation of high-powerdensity X-band AlGaN/GaN high electron mobility transistors in a millimeterwave monolithic microwave integrated circuit process," IEEE Electron Device Lett., vol. 36, no. 10, pp. 1004-1007, Oct. 2015, doi: 10.1109/LED.2015.2474265.

- [23] H. Zhou et al., "DC and RF performance of AlGaN/GaN/SiC MOSHEMTs with deep sub-micron T-gates and atomic layer epitaxy MgCaO as gate dielectric," IEEE Electron vol. 38, no. 10, pp. 1409–1412, Oct. Device Lett., doi: 10.1109/LED.2017.2746338.

- [24] M.-Y. Kao, C. Lee, R. Hajji, P. Saunier, and H.-Q. Tserng, "AlGaN/GaN HEMTs with PAE of 53% at 35 GHz for HPA and multi-function MMIC applications," in IEEE/MTT-Dig., 2007, pp. 627–629, S Int. Microw. Symp. Tech. doi: 10.1109/MWSYM.2007.379979.

- [25] J. S. Moon et al., "55% PAE and high power Ka-band GaN HEMTs with linearized transconductance via \$\hbox{n}+\$ GaN source contact ledge," IEEE Electron Device Lett., vol. 29, no. 8, pp. 834-837, Aug. 2008, doi: 10.1109/LED.2008.2000792.

- [26] T. Palacios et al., "High-power AlGaN/GaN HEMTs for Ka-band applications," IEEE Electron Device Lett., vol. 26, no. 11, pp. 781-783, Nov. 2005, doi: 10.1109/LED.2005.857701.

- [27] J.-S. Moon et al., "Power scaling of graded-channel GaN HEMTs with mini-field-plate T-gate and 156 GHz f<sub>T</sub>," IEEE Electron Device Lett., vol. 42, no. 6, pp. 796-799, Jun. 2021, doi: 10.1109/LED.2021.3075926.

- [28] S. Zhang et al., "7.05 W/mm power density millimeter-wave GaN MIS-HEMT with plasma enhanced atomic layer deposition SiN dielectric layer," IEEE Electron Device Lett., vol. 42, no. 10, pp. 1436-1439, Oct. 2021, doi: 10.1109/LED.2021.3105817.

- [29] Y.-F. Wu et al., "High-voltage millimeter-wave GaN HEMTs with 13.7 W/mm power density," in Proc. IEEE Int. Electron Devices Meeting, 2007, pp. 405-407, doi: 10.1109/IEDM.2007.4418958.

- [30] D.-H. Kim and J. A. del Alamo, "30-nm InAs pseudomorphic HEMTs on an InP substrate with a current-gain cutoff frequency of 628 GHz," IEEE Electron Device Lett., vol. 29, no. 8, pp. 830-833, Aug. 2008, doi: 10.1109/LED.2008.2000794.

- [31] T. Palacios et al., "Optimization of AlGaN/GaN HEMTs for high frequency operation," Physica Status Solidi, vol. 203, pp. 1845-1850, May 2006. [Online]. Available: https://doi.org/10. 1002/pssa.200565384

- [32] W. Liu, C. M. Zetterling, and M. Ostling, "Thermal-issues for design of high power SiC MESFETs," in Proc. 6th IEEE CPMT Conf. High Density Microsyst. Des. Packag. Compon. Failure Anal. (HDP), Shanghai, China, 2004, pp. 331-335, doi: 10.1109/HPD.2004.1346722.

- [33] Y.-W. Lien et al., "GaN technologies for applications from L- to Ka-band," in Proc. IEEE Int. Conf. Microw. Antennas Commun. Electron. Syst. (COMCAS), Tel-Aviv, Israel, 2017, pp. 1-5, doi: 10.1109/COMCAS.2017.8244831.

- [34] G. Crupi, A. Raffo, V. Vadalà, G. Vannini, D. M. M.-P. Schreurs, and A. Caddemi, "Scalability of multifinger HEMT performance," IEEE Microw. Wireless Compon. Lett., vol. 30, no. 9, pp. 869-872, Sep. 2020, doi: 10.1109/LMWC.2020.3012181.

- [35] K. Ranjan, S. Arulkumaran, G. I. Ng, and S. Vicknesh, "High Johnson's figure of merit (8.32 THz·V) in 0.15-μm conventional Tgate AlGaN/GaN HEMTs on silicon," Appl. Phys. Exp., vol. 7, no. 4, 2014, Art. no. 44102, doi: 10.7567/APEX.7.044102.

- [36] F. Medjdoub, D. Ducatteau, M. Zegaoui, B. Grimbert, N. Rolland, and P.-A. Rolland, "Trapping effects dependence on electron confinement in ultrashort GaN-on-Si high-electron-mobility transistors," Appl. Phys. Exp., vol. 5, no. 3, Mar. 2012, Art. no. 34103, doi: 10.1143/APEX.5.034103.

MING-WEN LEE (Graduate Student Member, IEEE) was born in Taipei City, Taiwan. He received the B.S. degree in material science and engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2017. He is currently pursuing the Ph.D. degree with the International College of Semiconductor Technology, National Yang Ming Chiao Tung University, Hsinchu, Taiwan, and the Ph.D. degree in doctorate programme in information and communication technologies with the University of Granada, Spain, and enrolled in

the Cotutelle Agreement signed between both Universities.

His research interest includes small gate length and high RF linearity AlGaN/GaN HEMT device design and fabrication for Ka Band wireless communication and GaN HEMT TCAD simulation.

YUEH-CHIN LIN was born in Taipei City, Taiwan. He received the B.S. degree in nuclear engineering and engineering physics and the M.S. degree in electrical engineering from Tsing Hua University, Hsinchu, Taiwan, in 1996 and 2000, respectively, and the Ph.D. degree from materials science and engineering, National Chiao Tung University, Hsinchu, in 2006.

From 2004 to 2006, he was with NTT Basic Research Laboratories, where he investigated the growth of AlGaSb/InAs HEMT on Si substrate

by molecular beam epitaxy. He is currently a Postdoctoral Fellow with the Department of Materials Science and Engineering and Microelectronics and Information Systems Research Center, NYCU. His research interests include MBE material growth and HEMT device design and fabrication for wireless communication.

PO-SHENG CHANG was born in Kaohsiung, Taiwan. He received the B.S. degree in electronics and electrical engineering and the M.S. degree in lighting and energy photonics from National Chiao Tung University, Hsinchu, Taiwan, in 2013 and 2019, respectively.

His research interest includes HEMT device design and fabrication for wireless communication.

YI-FAN TSAO (Member, IEEE) received the B.S. degree in electro-physics from National Chiao Tung University, Hsinchu, Taiwan, in 2016, the M.S. degree in electrical engineering from the University of California at Los Angeles, Los Angeles, CA, USA, in 2018, and the Ph.D. degree in electrical and computer engineering from Technische Üniversität Berlin, Berlin, Germany, in 2022. He is currently with the International College of Semiconductor Technology, National Yang Ming Chiao Tung University, Hsinchu.

transceiver design.

His research interests include millimeter-wave circuit and RF front-end

**HENG-TUNG HSU** (Senior Member, IEEE) received the B.S. and M.S. degrees in electronics engineering from the National Chiao Tung University, Hsinchu, Taiwan, in 1993 and 1995, respectively, and the Ph.D. degree in electrical and computer engineering from the University of Maryland at College Park, MD, USA, in 2002.

From 2002 to 2005, he was appointed as the Director of Engineering, AMCOM Communications, USA, mainly in charge of the design and development of monolithic microwave

integrated circuits for wireless communication systems. From 2006 to 2015, he was with the Department of Communication Engineering, Yuan Ze University, Taiwan. In 2015, he joined the International College of Semiconductor Technology in National Chiao Tung University, Taiwan, where he is currently a Professor and the Deputy Dean. He has authored or coauthored more than 90 journal papers and held three U.S. patents. His research interest includes the design and implementation of RF front-ends, antennas, active and passive microwave components, and RF packaging.

Dr. Hsu was the recipient of the 2012 Y. Z. Hsu's Outstanding Professor Award and received the Silver Medal Award for 2014 Taipei International Invention Show and Technomart.

**CHANG-FU DEE** received the B.Sc. and M.Sc. degrees in physics from the University of Malaya and the Ph.D. degree in electronic engineering from the Institute of Microengineering and Nanoelectroics (IMEN), Universiti Kebangsaan Malaysia.

He joined the Institute of Microengineering and Nanoelectronics, Universiti Kebangsaan Malaysia in 2004, as a Research Officer and a Research Fellow in 2006. He has been actively involved in the Nanostructures growth Si, ZnO, CuO and

SnO2, Molecular Beam Epitaxy, Compound semiconductor, GaAs, PHEMT, HEMT Crystal growth simulation, and Monte Carlo simulation of crystal growth in the IMEN. His research focus is in the area of microelectronics and nanoelectronics materials and devices design for electronics, functional sensor, and actuator applications. These includes the synthesis, fabrication, and characterization of nano-structured metal oxide and epitaxial growth of high-speed compound semiconductor layers. He is a Principal Investigator for FEWS Research Projects mainly in the areas of nano materials.

EDWARD YI CHANG (Life Fellow, IEEE) received the Ph.D. degree from the University of Minnesota, Minneapolis, in 1985. He worked with Unisys Corporation and Comsat Labs, USA from 1985 to 1992. In 1992, he joined National Chiao Tung University, Hsinchu, Taiwan. He is currently the Chair Professor with the Department of Material Science and Engineering, the International College of Semiconductor Technology, and the Department of Electronics Engineering, National Yang Ming Chiao Tung

University, Taiwan. He is also a Professor with the Institute of Microengineering and Nanoelectronics, Universiti Kebangsaan Malaysia. He holds more than 40 patents worldwide and has been authored or co-authored of more than 250 journal papers in the related research areas. His current research interests include III-V and GaN based devices for logic, high frequency and power applications. He is a JSAP Fellow International, a TMRS Fellow, and a Distinguished Lecturer of the IEEE Electron Devices Society.